Electronics and Computer Science Versatile HighLevel Synthesis of

- Slides: 20

Electronics and Computer Science Versatile High-Level Synthesis of Self-Checking Datapaths Using an On-line Testability Metric Petros Oikonomakos Bashir M. Al-Hashimi Mark Zwolinski Electronic Systems Design Group University of Southampton, UK

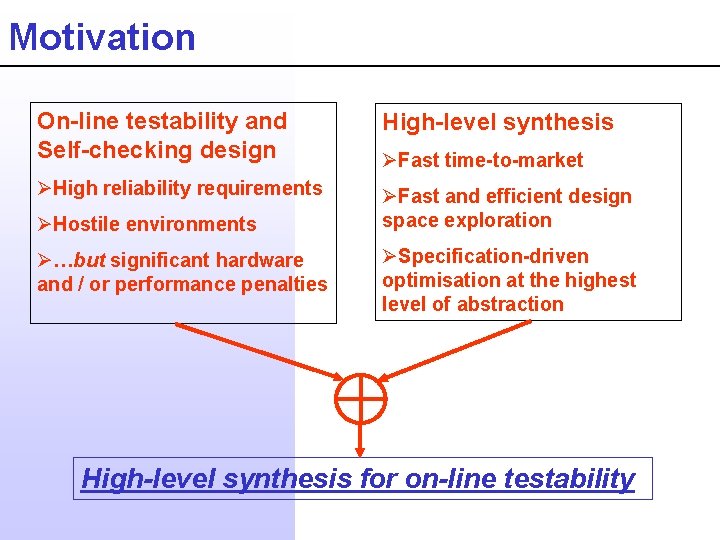

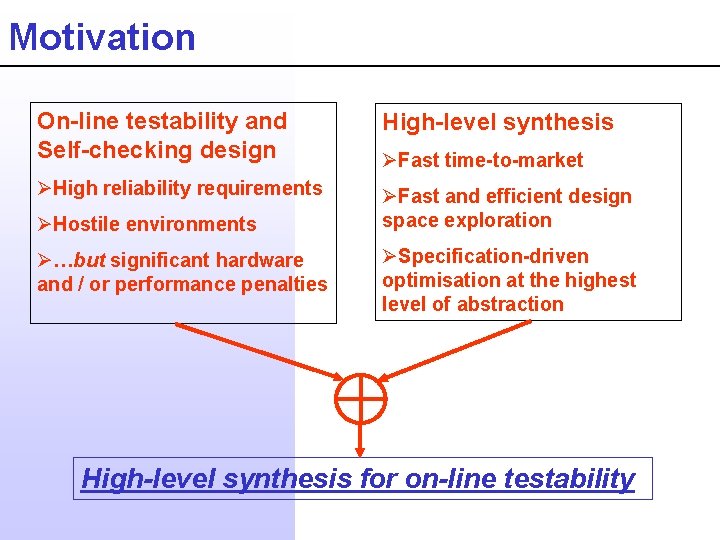

Motivation On-line testability and Self-checking design High-level synthesis ØHigh reliability requirements ØFast and efficient design space exploration ØHostile environments Ø…but significant hardware and / or performance penalties ØFast time-to-market ØSpecification-driven optimisation at the highest level of abstraction High-level synthesis for on-line testability

Outline ØIntroduction ØPhysical and Algorithmic Duplication and Inversion-based Self-checking Design ØHigh-level Synthesis Background ØImplementation : Transforms, Metric, Algorithm ØSynthesis and Simulation Results ØConclusion

Introduction ØSelf-checking design at the RTL : typical in industry ØSelf-checking design before high-level synthesis ØSelf-checking design after high-level synthesis üOur approach : self-checking design within high-level synthesis!!!

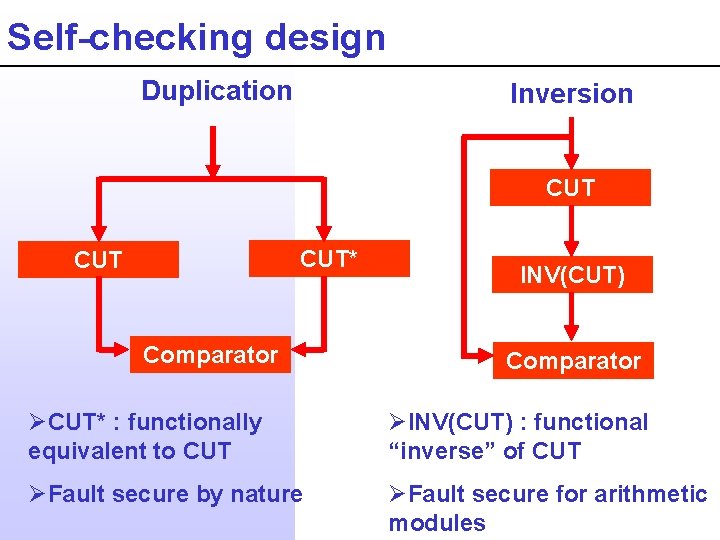

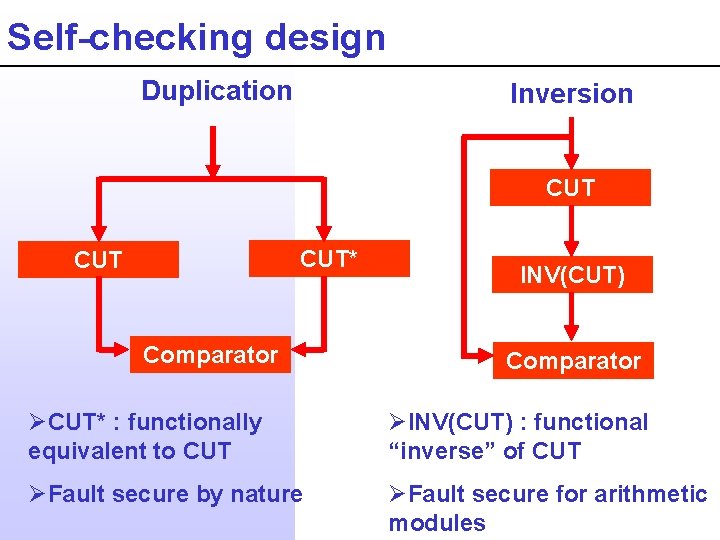

Self-checking design Duplication Inversion CUT* CUT Comparator INV(CUT) Comparator ØCUT* : functionally equivalent to CUT ØINV(CUT) : functional “inverse” of CUT ØFault secure by nature ØFault secure for arithmetic modules

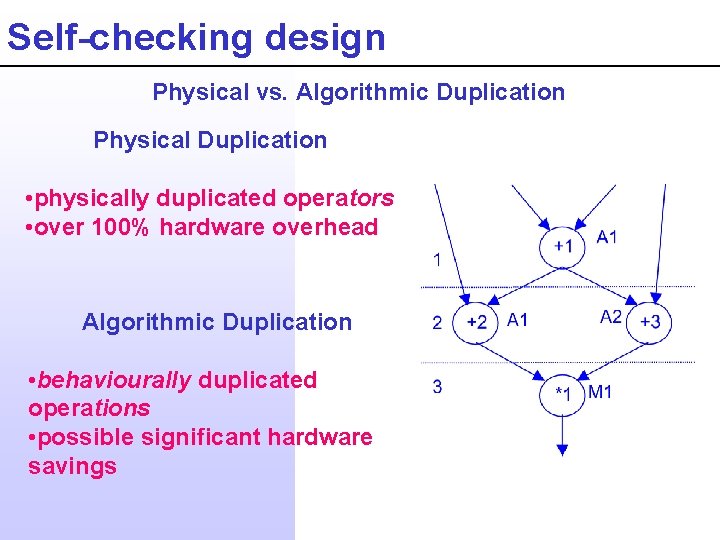

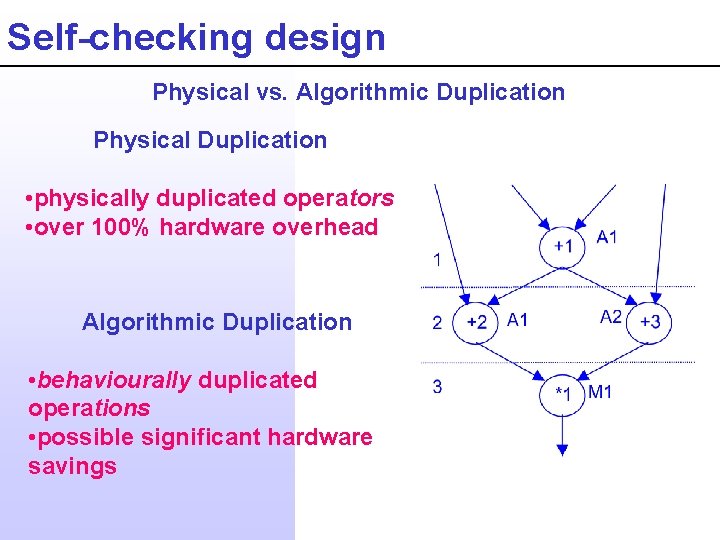

Self-checking design Physical vs. Algorithmic Duplication Physical Duplication • physically duplicated operators • over 100% hardware overhead Algorithmic Duplication • behaviourally duplicated operations • possible significant hardware savings

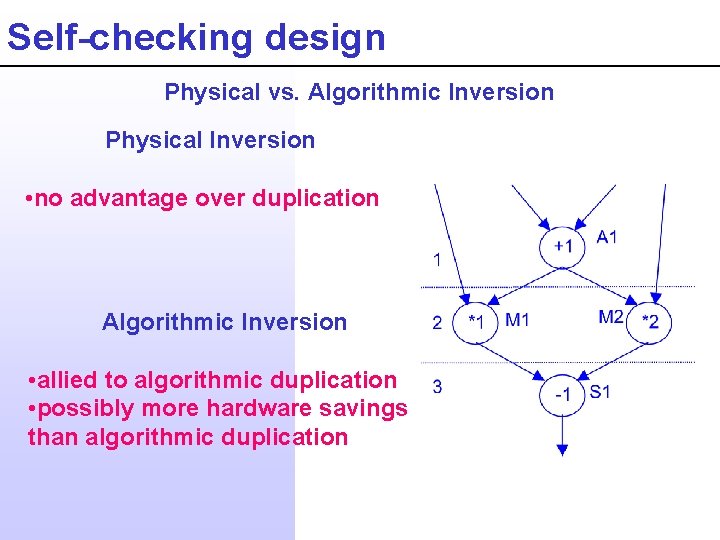

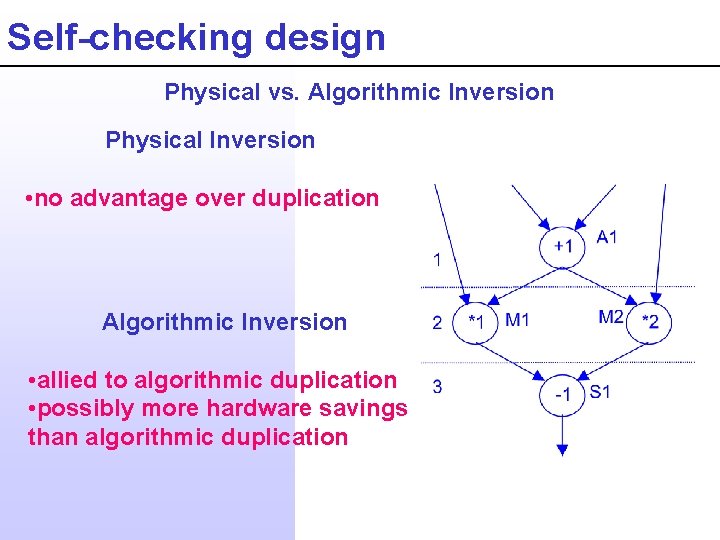

Self-checking design Physical vs. Algorithmic Inversion Physical Inversion • no advantage over duplication Algorithmic Inversion • allied to algorithmic duplication • possibly more hardware savings than algorithmic duplication

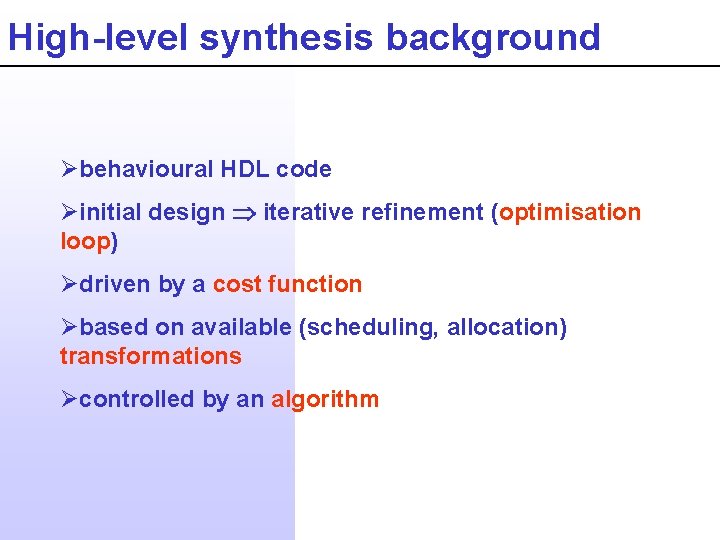

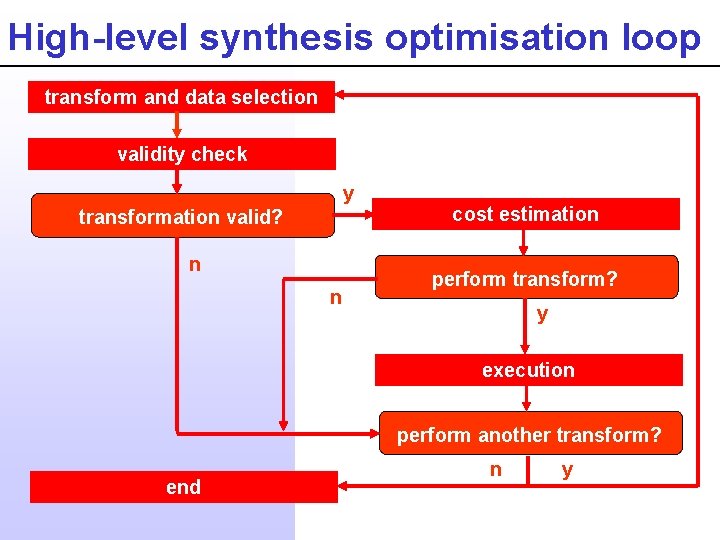

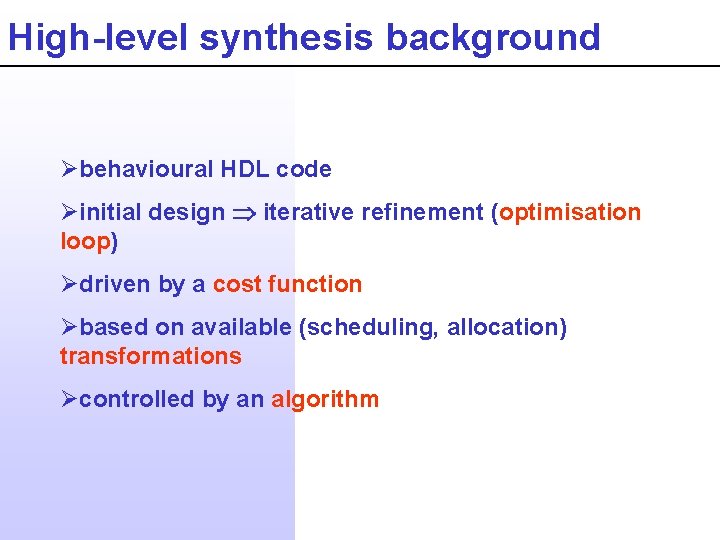

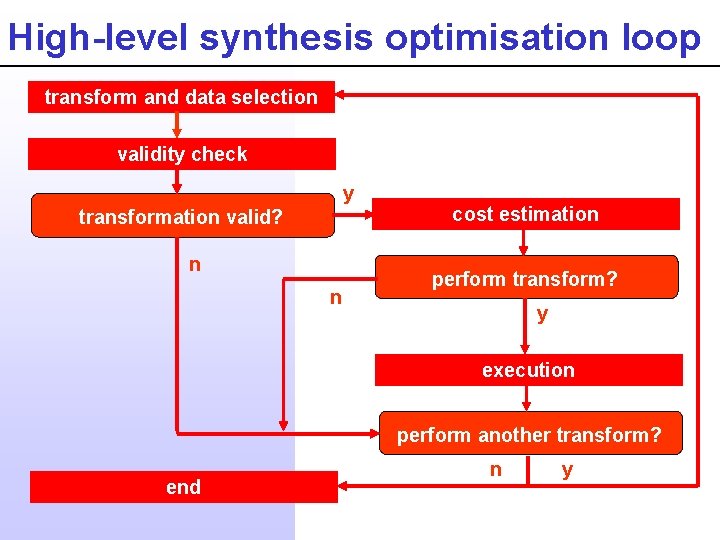

High-level synthesis background Øbehavioural HDL code Øinitial design iterative refinement (optimisation loop) Ødriven by a cost function Øbased on available (scheduling, allocation) transformations Øcontrolled by an algorithm

High-level synthesis optimisation loop transform and data selection validity check y transformation valid? n n cost estimation perform transform? y execution perform another transform? end n y

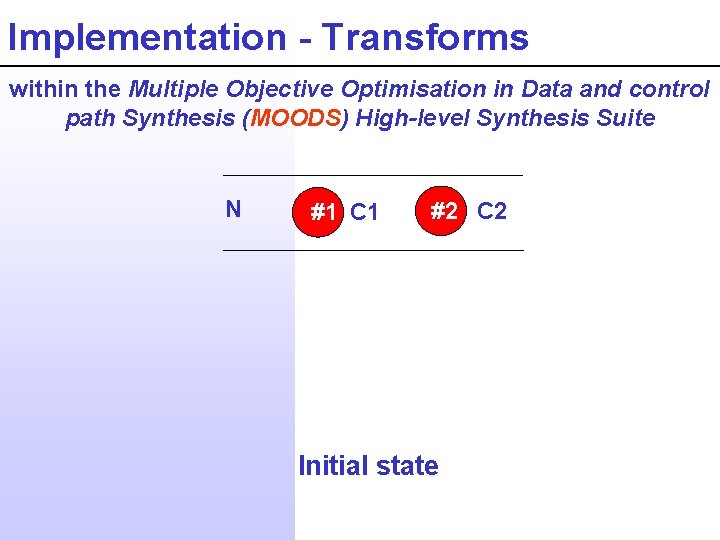

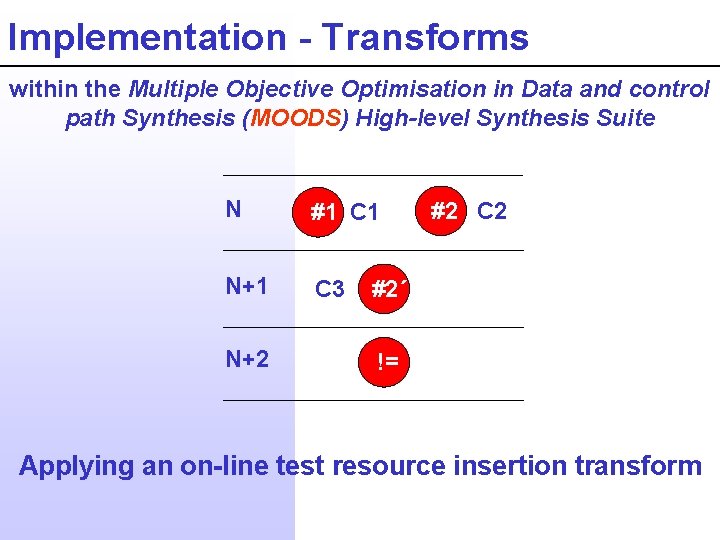

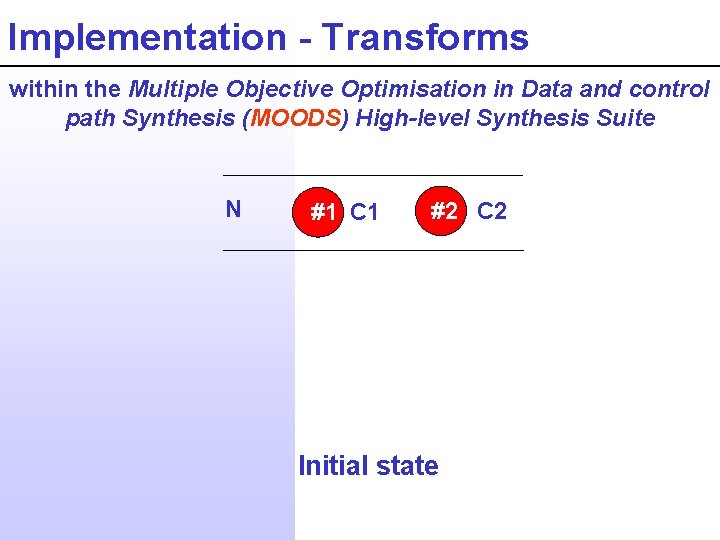

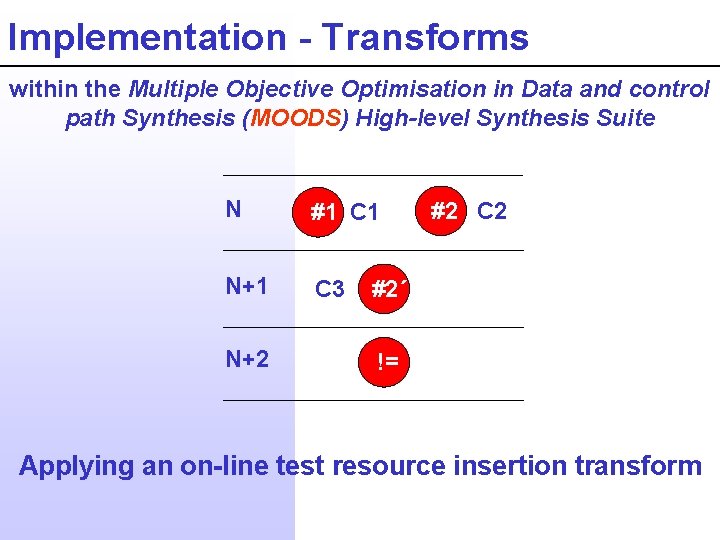

Implementation - Transforms within the Multiple Objective Optimisation in Data and control path Synthesis (MOODS) High-level Synthesis Suite N #1 C 1 #2 C 2 Initial state

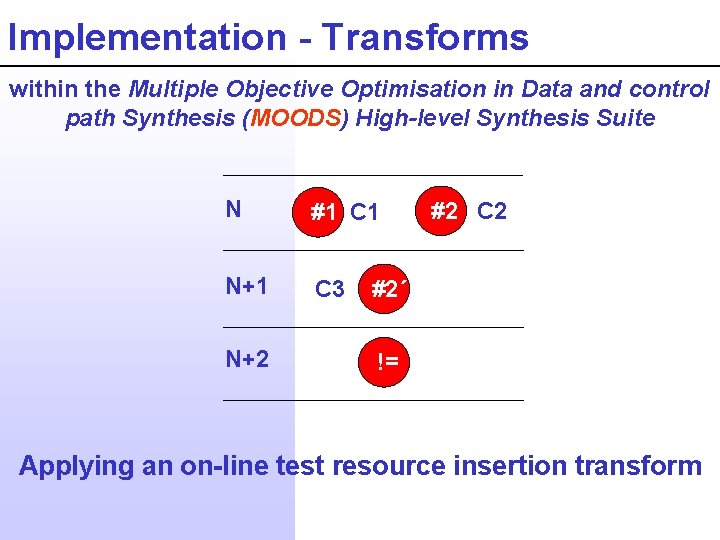

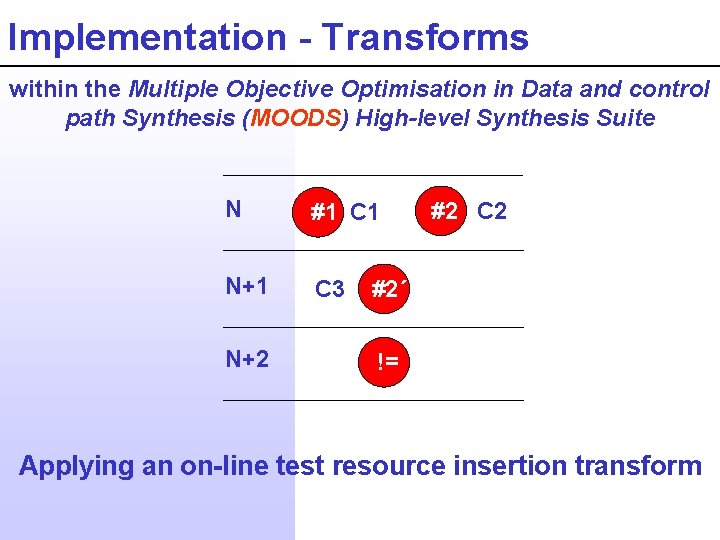

Implementation - Transforms within the Multiple Objective Optimisation in Data and control path Synthesis (MOODS) High-level Synthesis Suite N #1 C 1 N+1 C 3 N+2 #2 C 2 #2´ != Applying an on-line test resource insertion transform

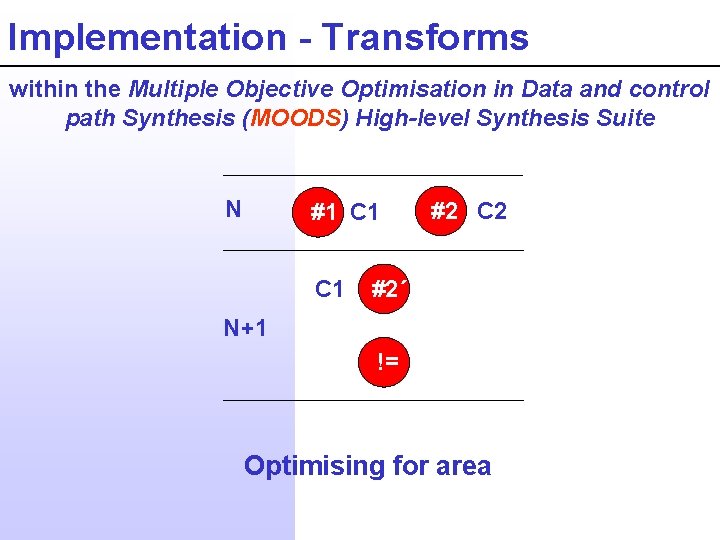

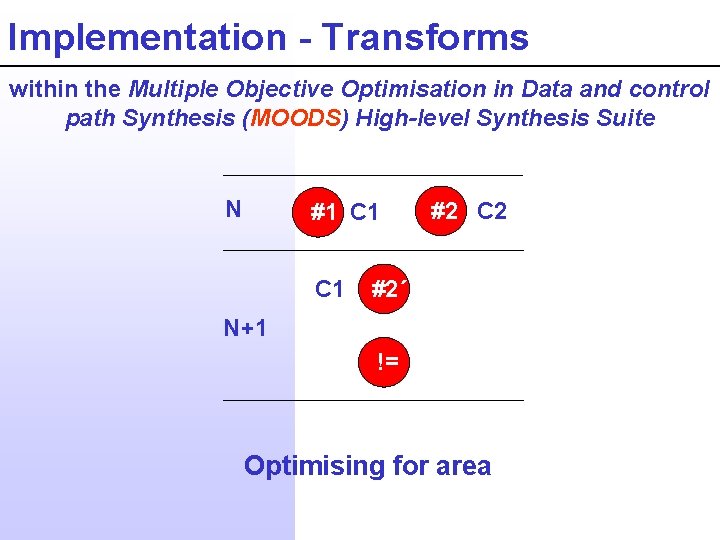

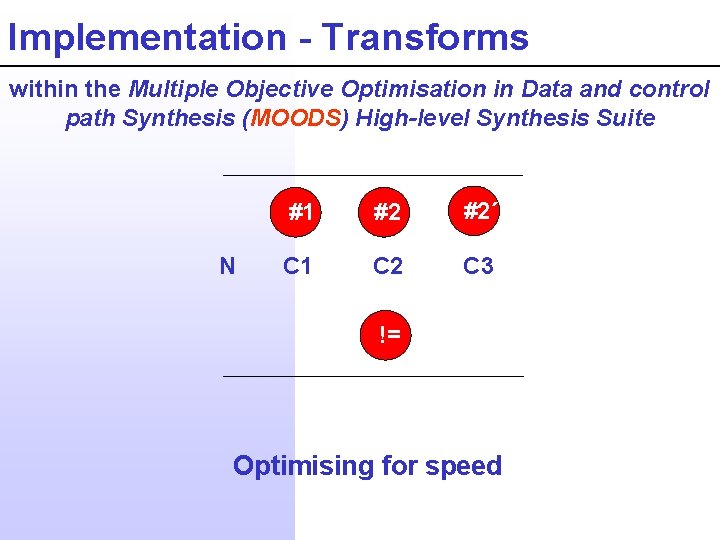

Implementation - Transforms within the Multiple Objective Optimisation in Data and control path Synthesis (MOODS) High-level Synthesis Suite N #1 C 1 #2 C 2 #2´ N+1 != Optimising for area

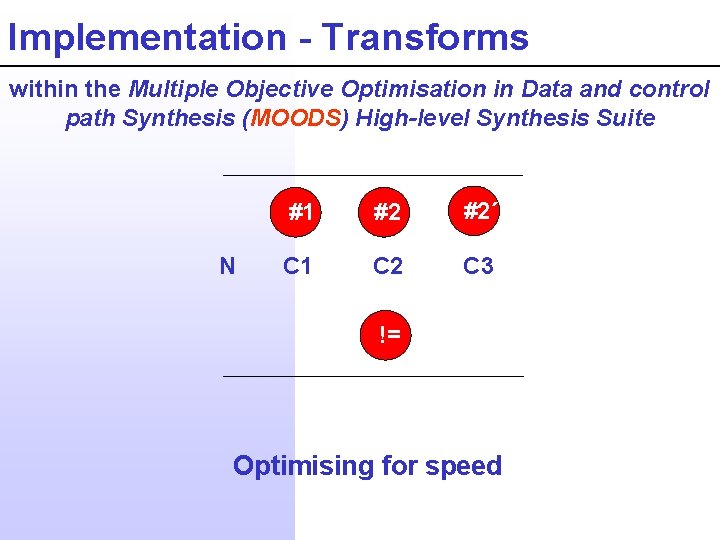

Implementation - Transforms within the Multiple Objective Optimisation in Data and control path Synthesis (MOODS) High-level Synthesis Suite N #1 C 1 N+1 C 3 N+2 #2 C 2 #2´ != Applying an on-line test resource insertion transform

Implementation - Transforms within the Multiple Objective Optimisation in Data and control path Synthesis (MOODS) High-level Synthesis Suite N #1 #2 #2´ C 1 C 2 C 3 != Optimising for speed

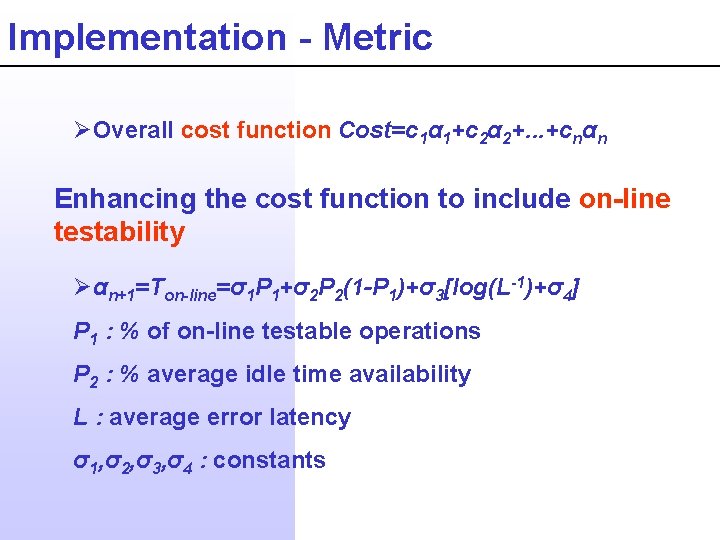

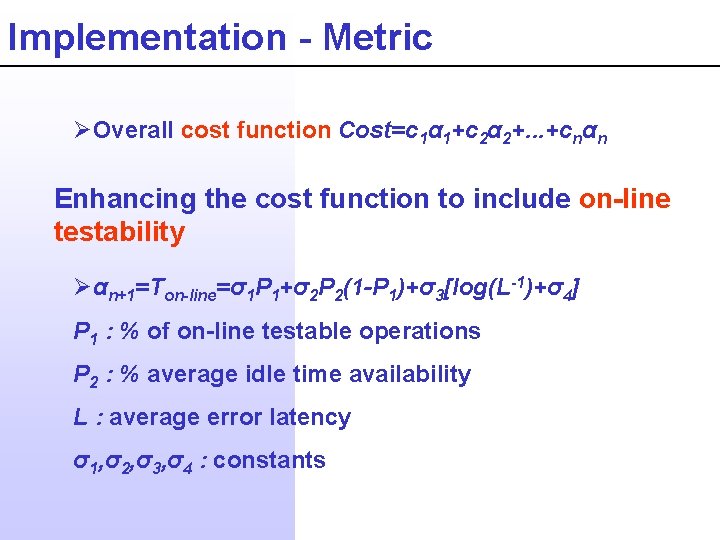

Implementation - Metric ØOverall cost function Cost=c 1α 1+c 2α 2+. . . +cnαn Enhancing the cost function to include on-line testability Øαn+1=Ton-line=σ1 P 1+σ2 P 2(1 -P 1)+σ3[log(L-1)+σ4] P 1 : % of on-line testable operations P 2 : % average idle time availability L : average error latency σ1, σ2, σ3, σ4 : constants

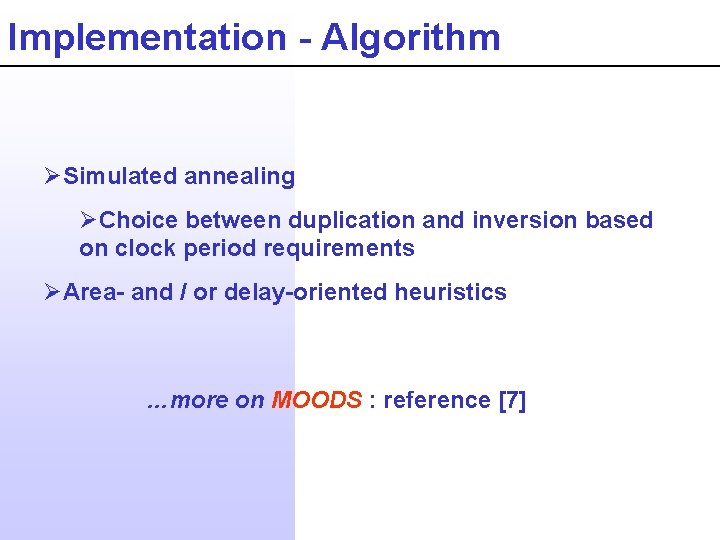

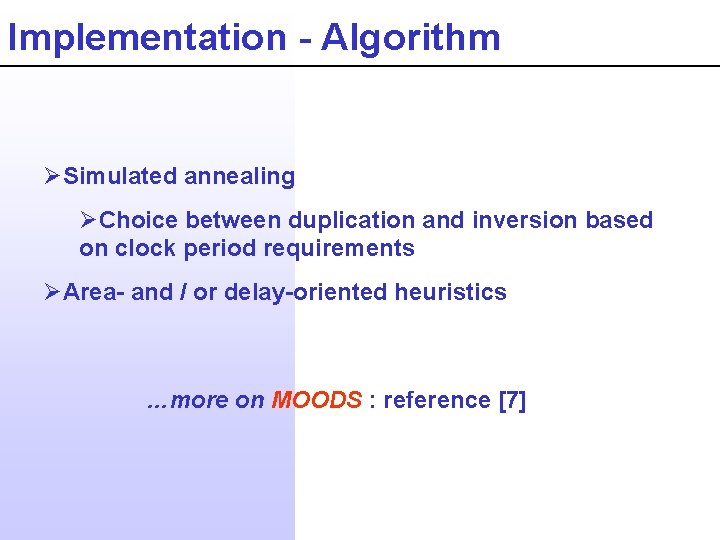

Implementation - Algorithm ØSimulated annealing ØChoice between duplication and inversion based on clock period requirements ØArea- and / or delay-oriented heuristics …more on MOODS : reference [7]

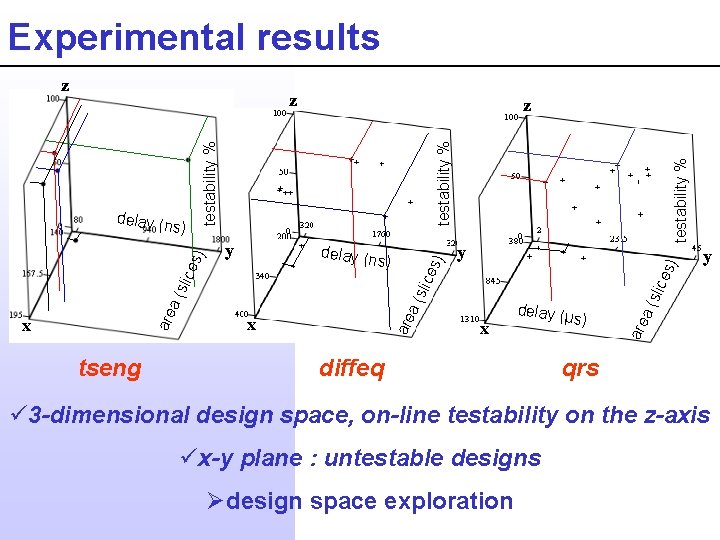

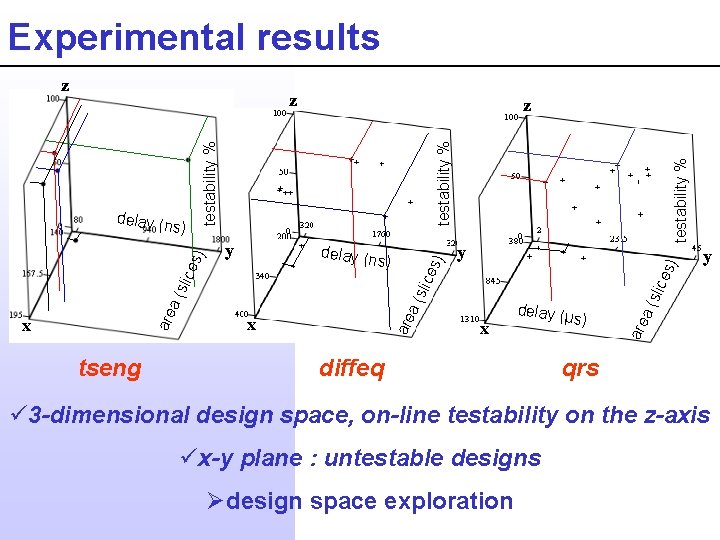

Experimental results z z tseng es) are x x delay (μ diffeq y slic a( a( are x y slic s) s) a( delay (n are y testability % s) es) delay (n z qrs ü 3 -dimensional design space, on-line testability on the z-axis üx-y plane : untestable designs Ødesign space exploration

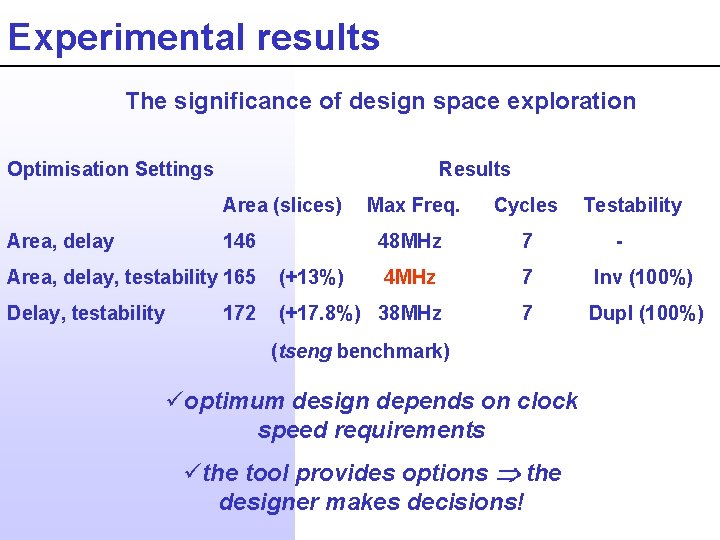

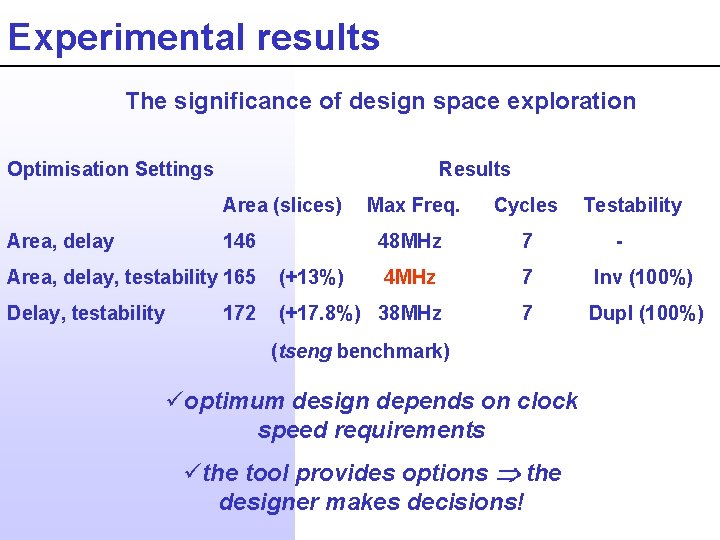

Experimental results The significance of design space exploration Optimisation Settings Results Area (slices) Area, delay 146 Max Freq. Cycles 48 MHz 7 Testability - Area, delay, testability 165 (+13%) 4 MHz 7 Inv (100%) Delay, testability (+17. 8%) 38 MHz 7 Dupl (100%) 172 (tseng benchmark) üoptimum design depends on clock speed requirements üthe tool provides options the designer makes decisions!

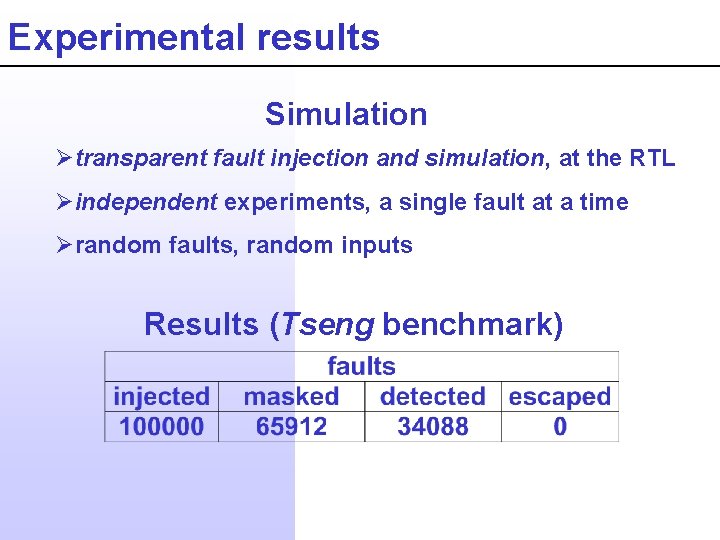

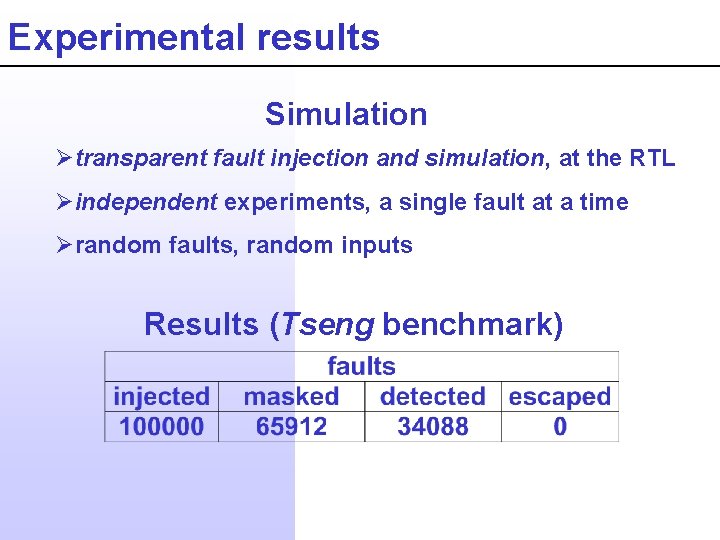

Experimental results Simulation Øtransparent fault injection and simulation, at the RTL Øindependent experiments, a single fault at a time Ørandom faults, random inputs Results (Tseng benchmark)

Conclusion ØIntegral, cost function-driven on-line test synthesis framework ØProperties and contributions: • Versatility : hardware- or time-redundancy according to designer’s requirements • Fully automatic insertion of self-checking resources • Quantification of on-line testability • Utilisation of the inversion testing idea