ELECTRONIC II Notie de curs Cursul nr 13

- Slides: 22

ELECTRONICĂ II Notiţe de curs Cursul nr. 13 Conf. Dr. Ing. Gheorghe PANĂ pana@vega. unitbv. ro

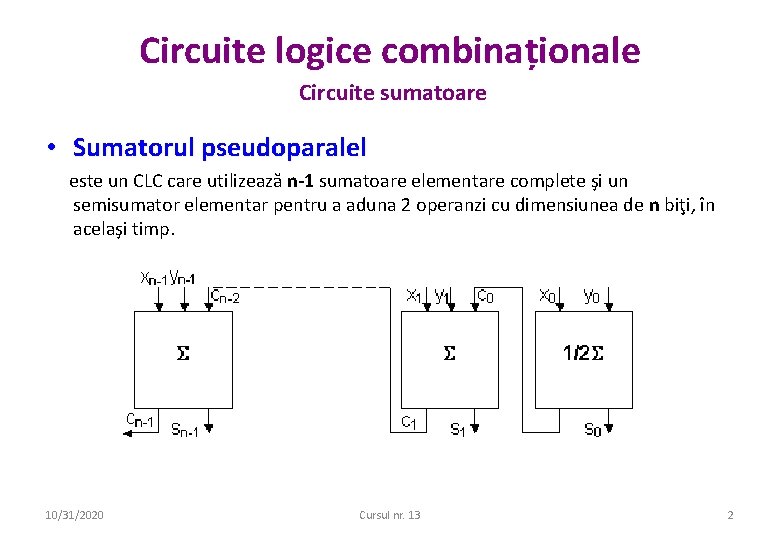

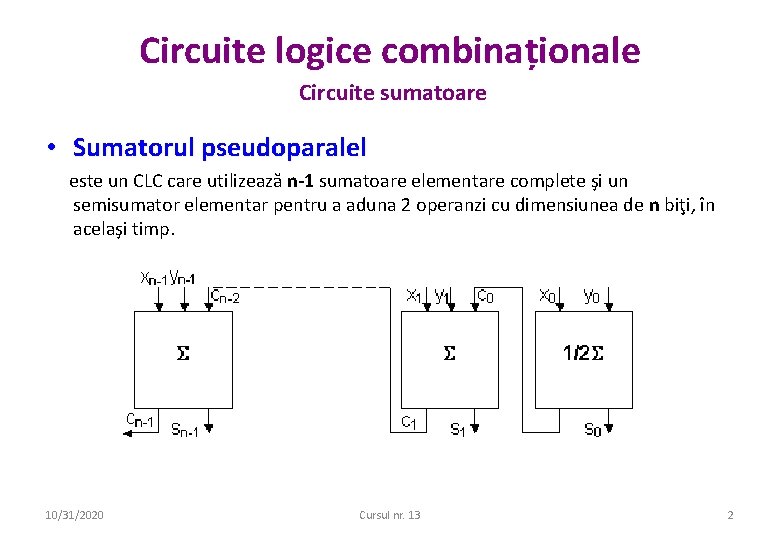

Circuite logice combinaționale Circuite sumatoare • Sumatorul pseudoparalel este un CLC care utilizează n-1 sumatoare elementare complete şi un semisumator elementar pentru a aduna 2 operanzi cu dimensiunea de n biţi, în acelaşi timp. 10/31/2020 Cursul nr. 13 2

Circuite logice combinaționale Circuite sumatoare Observații: ții • Circuitul se numeşte pseudoparalel deoarece, deşi cei doi biţi de date se adună simultan, transportul trebuie să se propage de la rangul cel mai mic spre cel mai mare. • Se mai numeşte şi sumator cu transport propagat şi este un sumator lent. 10/31/2020 Cursul nr. 13 3

Circuite logice combinaționale Circuite sumatoare • Sumatoare de mare viteză • • S-a impus realizarea unor astfel de sumatoare pentru a creşte viteza de procesare a sistemelor. La aceste sumatoare, pe lângă utilizarea porţilor cu timpi de propagare mari, sau utilizat şi structuri adecvate acestui scop. Tipuri: Sumatorul paralel complet este proiectat să adune strict în paralel şi este cel mai rapid sumator. La intrări se aduc simultan transportul şi biţii operanzilor. Sumatorul paralel cu transport anticipat, realizează un compromis între sumatorul pseudoparalel şi sumatorul paralel complet. El împarte sumatorul în module, calculează transportul pentru fiecare rang şi îl aduce apoi la intrarea corespunzătoare a sumatoarelor elementare în acelaşi timp. Sumatorul cu salvarea transportului este utilizat în cazul adunării unor şiruri de numere. La acest sumator se salvează transportul rezultat din însumarea a 2 operanzi într-un bistabil (celulă elementară de memorare) care se pune apoi la dispoziţia următoarei însumări, realizându-se astfel o adunare în manieră pseudoparalelă. 10/31/2020 Cursul nr. 13 4

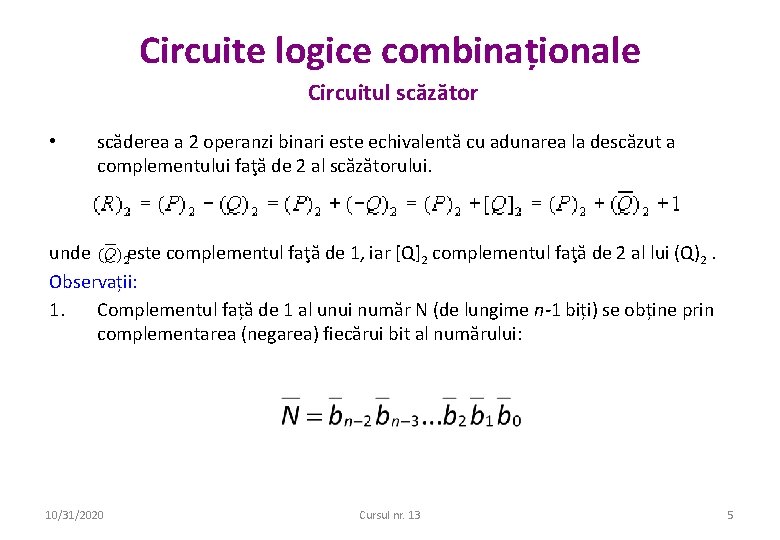

Circuite logice combinaționale Circuitul scăzător • scăderea a 2 operanzi binari este echivalentă cu adunarea la descăzut a complementului faţă de 2 al scăzătorului. unde este complementul faţă de 1, iar [Q]2 complementul faţă de 2 al lui (Q)2. Observații: 1. Complementul față de 1 al unui număr N (de lungime n-1 biți) se obține prin complementarea (negarea) fiecărui bit al numărului: 10/31/2020 Cursul nr. 13 5

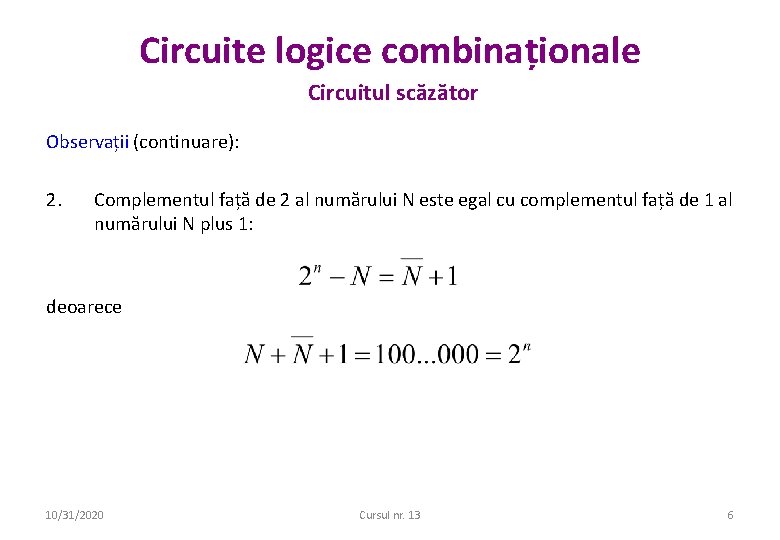

Circuite logice combinaționale Circuitul scăzător Observații (continuare): 2. Complementul față de 2 al numărului N este egal cu complementul față de 1 al numărului N plus 1: deoarece 10/31/2020 Cursul nr. 13 6

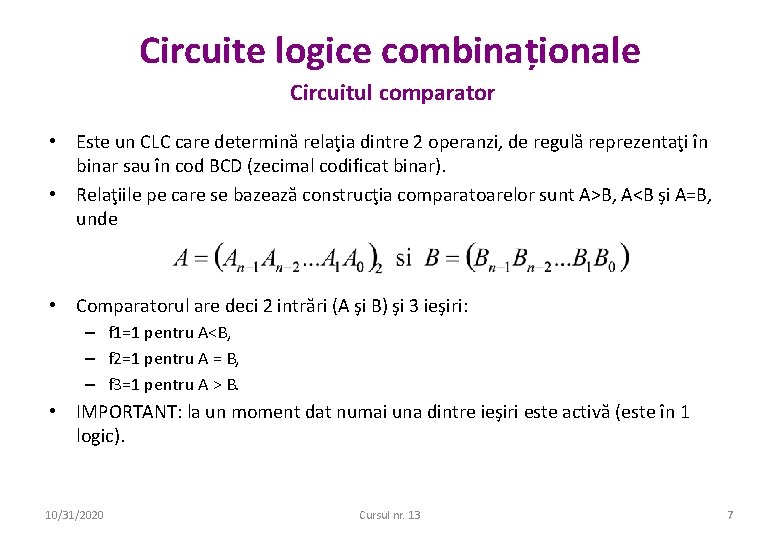

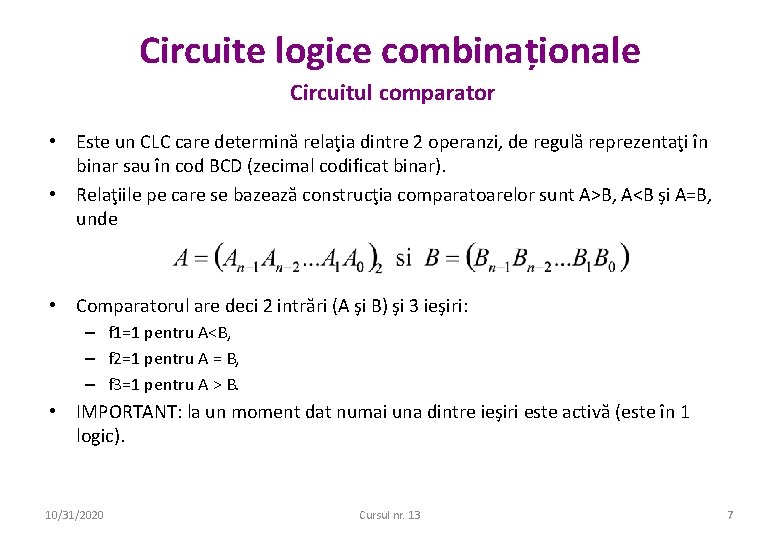

Circuite logice combinaționale Circuitul comparator • Este un CLC care determină relaţia dintre 2 operanzi, de regulă reprezentaţi în binar sau în cod BCD (zecimal codificat binar). • Relaţiile pe care se bazează construcţia comparatoarelor sunt A>B, A<B şi A=B, unde • Comparatorul are deci 2 intrări (A şi B) şi 3 ieşiri: – f 1=1 pentru A<B, – f 2=1 pentru A = B, – f 3=1 pentru A > B. • IMPORTANT: la un moment dat numai una dintre ieşiri este activă (este în 1 logic). 10/31/2020 Cursul nr. 13 7

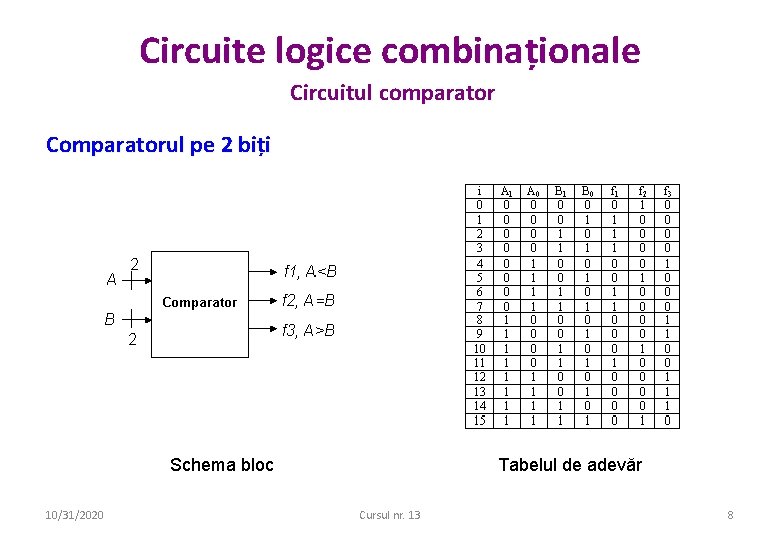

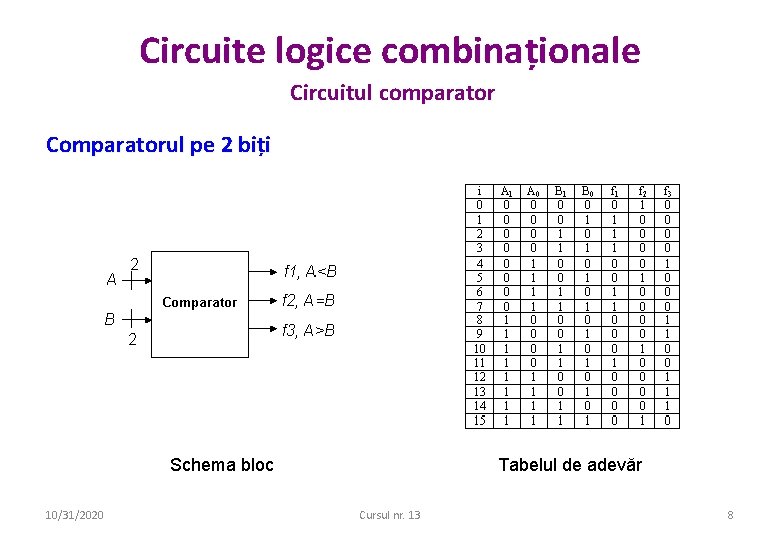

Circuite logice combinaționale Circuitul comparator Comparatorul pe 2 biți Schema bloc 10/31/2020 Tabelul de adevăr Cursul nr. 13 8

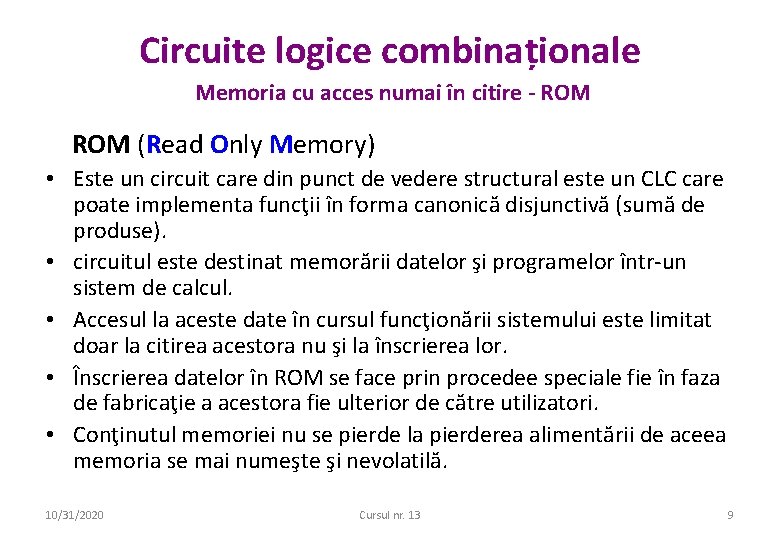

Circuite logice combinaționale Memoria cu acces numai în citire - ROM (Read Only Memory) • Este un circuit care din punct de vedere structural este un CLC care poate implementa funcţii în forma canonică disjunctivă (sumă de produse). • circuitul este destinat memorării datelor şi programelor într-un sistem de calcul. • Accesul la aceste date în cursul funcţionării sistemului este limitat doar la citirea acestora nu şi la înscrierea lor. • Înscrierea datelor în ROM se face prin procedee speciale fie în faza de fabricaţie a acestora fie ulterior de către utilizatori. • Conţinutul memoriei nu se pierde la pierderea alimentării de aceea memoria se mai numeşte şi nevolatilă. 10/31/2020 Cursul nr. 13 9

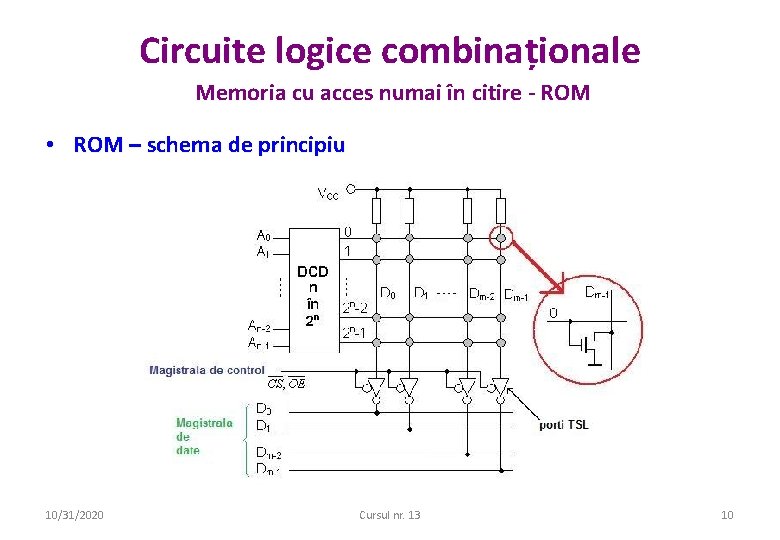

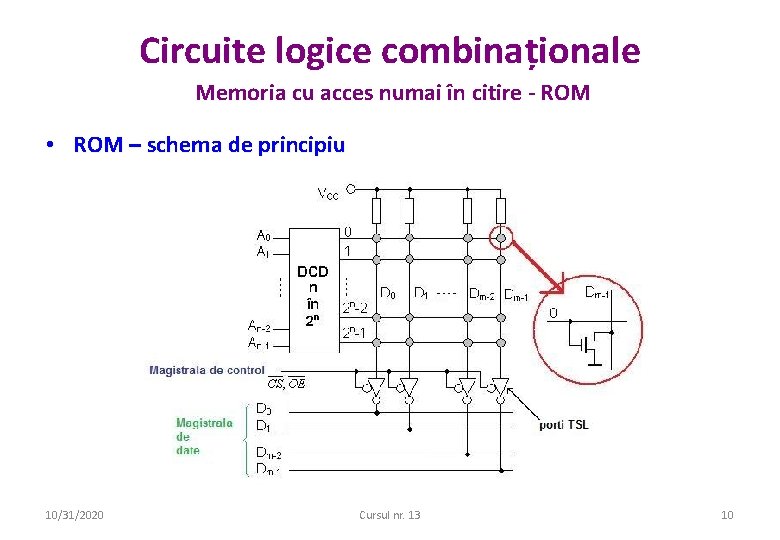

Circuite logice combinaționale Memoria cu acces numai în citire - ROM • ROM – schema de principiu 10/31/2020 Cursul nr. 13 10

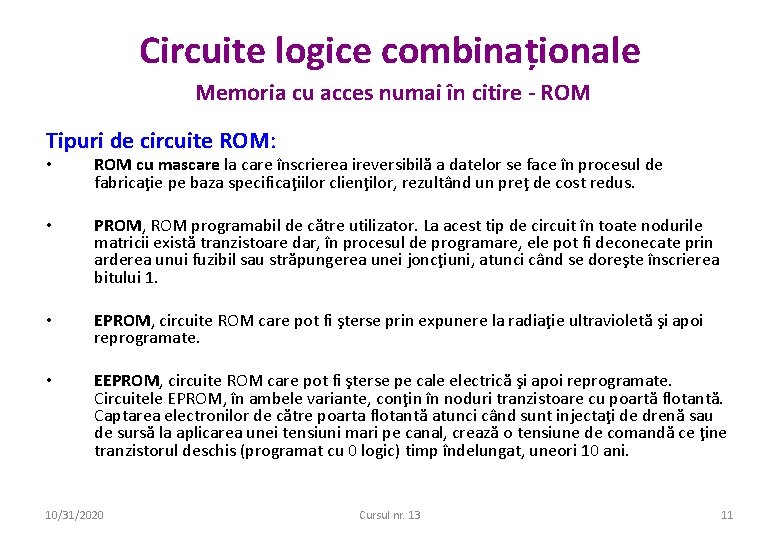

Circuite logice combinaționale Memoria cu acces numai în citire - ROM Tipuri de circuite ROM: • ROM cu mascare la care înscrierea ireversibilă a datelor se face în procesul de fabricaţie pe baza specificaţiilor clienţilor, rezultând un preţ de cost redus. • PROM, ROM programabil de către utilizator. La acest tip de circuit în toate nodurile matricii există tranzistoare dar, în procesul de programare, ele pot fi deconecate prin arderea unui fuzibil sau străpungerea unei joncţiuni, atunci când se doreşte înscrierea bitului 1. • EPROM, circuite ROM care pot fi şterse prin expunere la radiaţie ultravioletă şi apoi reprogramate. • EEPROM, circuite ROM care pot fi şterse pe cale electrică şi apoi reprogramate. Circuitele EPROM, în ambele variante, conţin în noduri tranzistoare cu poartă flotantă. Captarea electronilor de către poarta flotantă atunci când sunt injectaţi de drenă sau de sursă la aplicarea unei tensiuni mari pe canal, crează o tensiune de comandă ce ţine tranzistorul deschis (programat cu 0 logic) timp îndelungat, uneori 10 ani. 10/31/2020 Cursul nr. 13 11

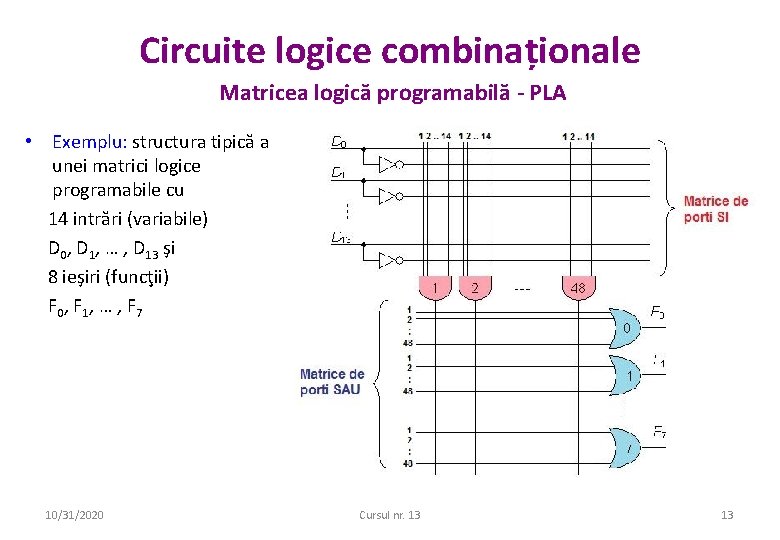

Circuite logice combinaționale Matricea logică programabilă - PLA (Programmable Logic Array) • Matricea logică programabilă spre deosebire de ROM prezintă pe lângă nivelul SAU programabil şi nivelul ŞI programabil. • Programarea celor două nivele utilizează aceleaşi tehnici ca la ROM şi poate fi realizată din fabricaţie sau de către utilizator în cazul FPLA (Field PLA). 10/31/2020 Cursul nr. 13 12

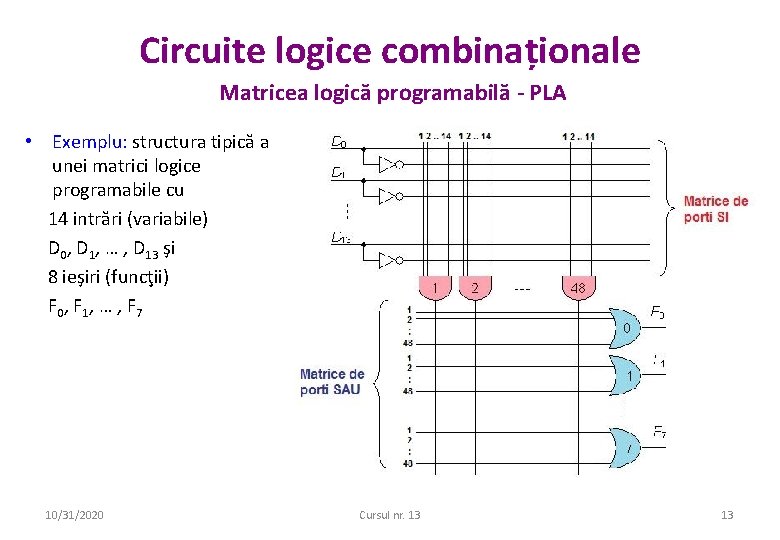

Circuite logice combinaționale Matricea logică programabilă - PLA • Exemplu: structura tipică a unei matrici logice programabile cu 14 intrări (variabile) D 0, D 1, … , D 13 şi 8 ieşiri (funcţii) F 0 , F 1 , … , F 7 10/31/2020 Cursul nr. 13 13

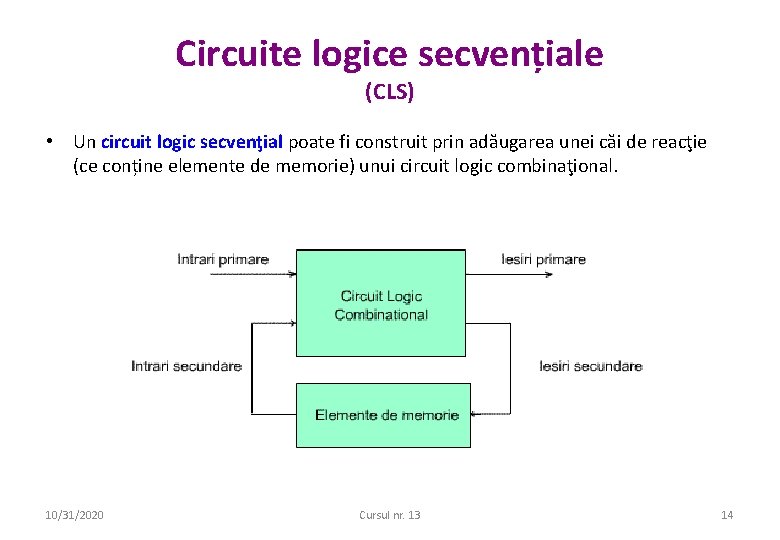

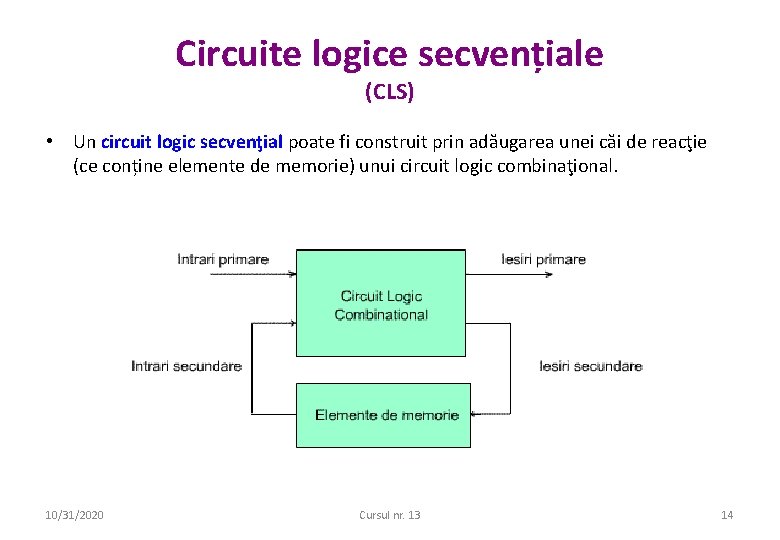

Circuite logice secvențiale (CLS) • Un circuit logic secvenţial poate fi construit prin adăugarea unei căi de reacţie (ce conține elemente de memorie) unui circuit logic combinaţional. 10/31/2020 Cursul nr. 13 14

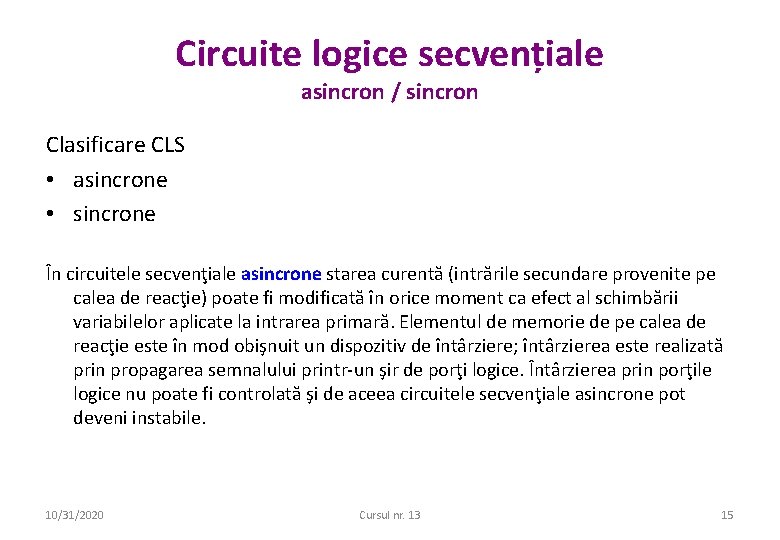

Circuite logice secvențiale asincron / sincron Clasificare CLS • asincrone • sincrone În circuitele secvenţiale asincrone starea curentă (intrările secundare provenite pe calea de reacţie) poate fi modificată în orice moment ca efect al schimbării variabilelor aplicate la intrarea primară. Elementul de memorie de pe calea de reacţie este în mod obişnuit un dispozitiv de întârziere; întârzierea este realizată prin propagarea semnalului printr-un şir de porţi logice. Întârzierea prin porţile logice nu poate fi controlată şi de aceea circuitele secvenţiale asincrone pot deveni instabile. 10/31/2020 Cursul nr. 13 15

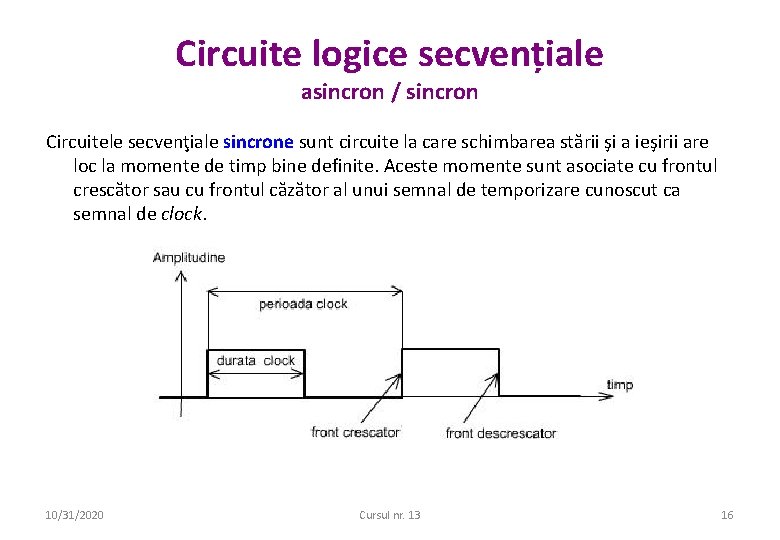

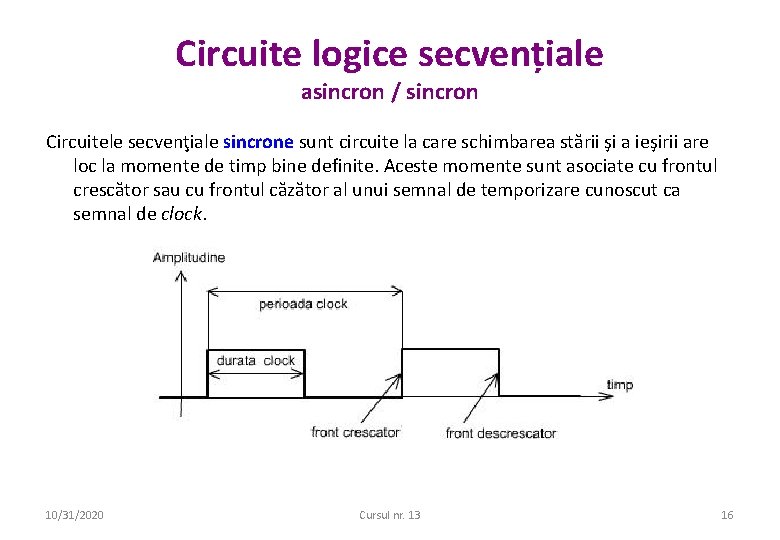

Circuite logice secvențiale asincron / sincron Circuitele secvenţiale sincrone sunt circuite la care schimbarea stării şi a ieşirii are loc la momente de timp bine definite. Aceste momente sunt asociate cu frontul crescător sau cu frontul căzător al unui semnal de temporizare cunoscut ca semnal de clock. 10/31/2020 Cursul nr. 13 16

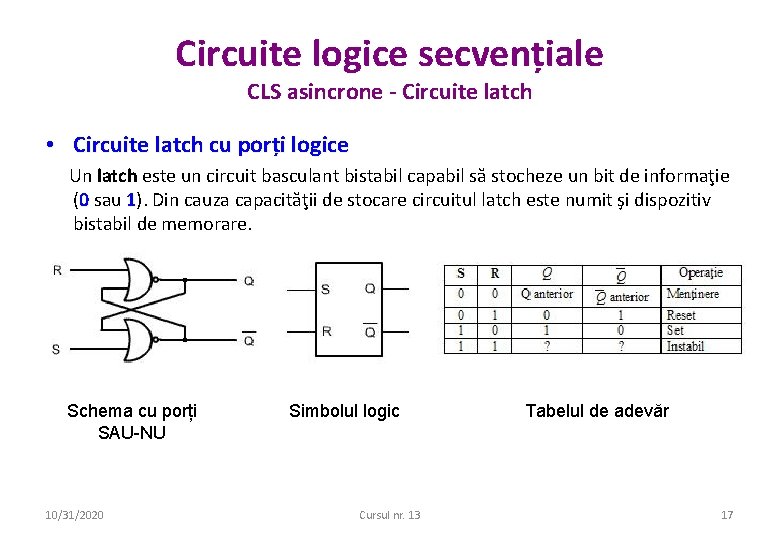

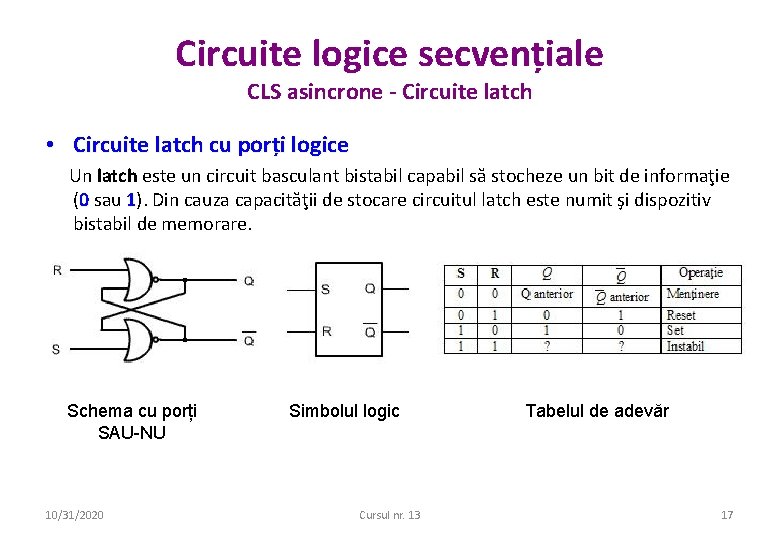

Circuite logice secvențiale CLS asincrone - Circuite latch • Circuite latch cu porți logice Un latch este un circuit basculant bistabil capabil să stocheze un bit de informaţie (0 sau 1). Din cauza capacităţii de stocare circuitul latch este numit şi dispozitiv bistabil de memorare. Schema cu porți SAU-NU 10/31/2020 Simbolul logic Cursul nr. 13 Tabelul de adevăr 17

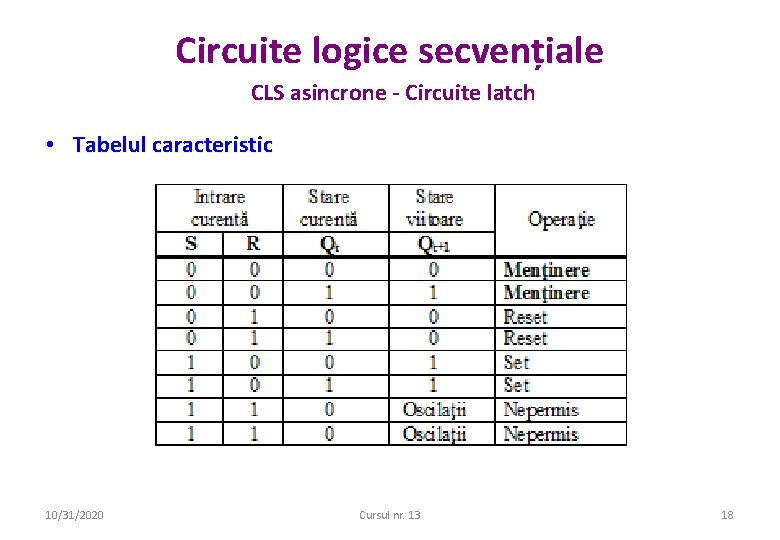

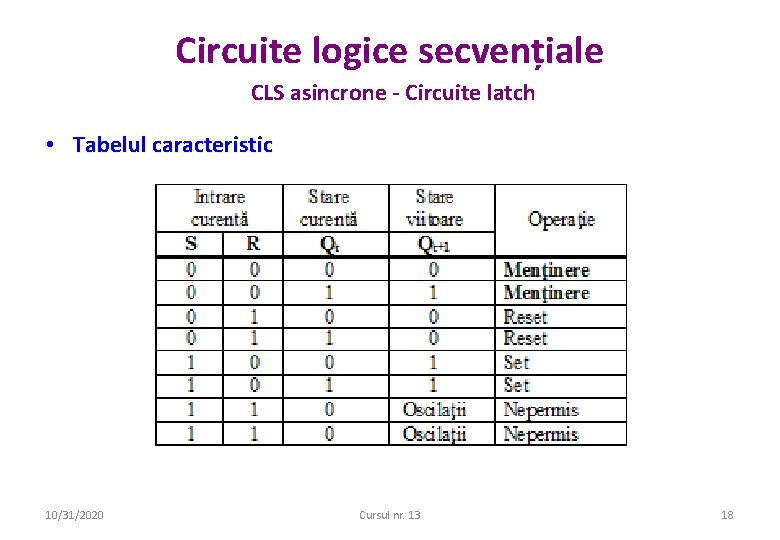

Circuite logice secvențiale CLS asincrone - Circuite latch • Tabelul caracteristic 10/31/2020 Cursul nr. 13 18

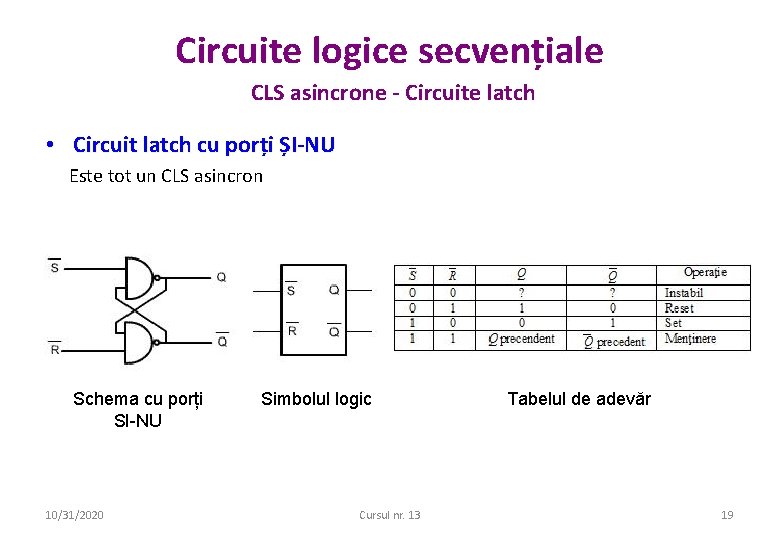

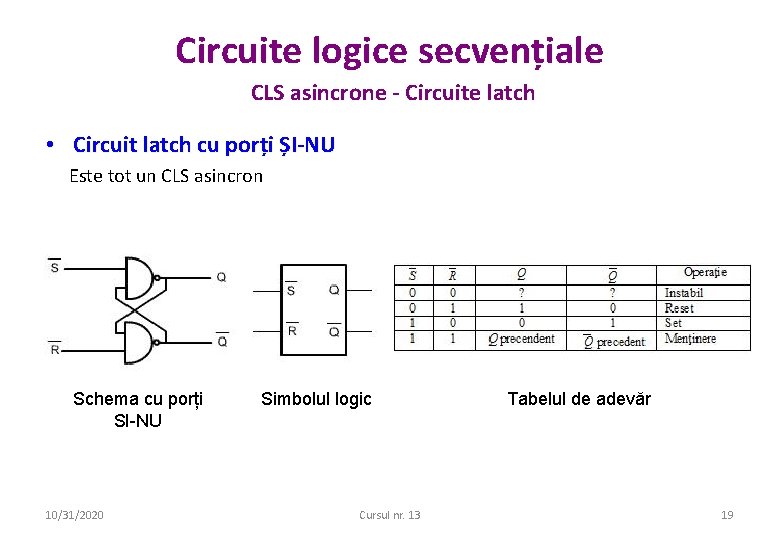

Circuite logice secvențiale CLS asincrone - Circuite latch • Circuit latch cu porți ȘI-NU Este tot un CLS asincron Schema cu porți SI-NU 10/31/2020 Simbolul logic Cursul nr. 13 Tabelul de adevăr 19

Circuite logice secvențiale CLS sincrone • Există 2 tipuri: 1. Circuitele latch sunt active pe palier; ieşirile circuitului sunt sensibile la nivel de tensiune (palier) şi nu la o tranziţie de semnal. 2. Circuitele flip-flop sunt active pe front; ieşirile circuitului sunt sensibile la tranziţia semnalului, fie din 1 în 0 (front negativ) fie din 0 în 1 (front pozitiv). 10/31/2020 Cursul nr. 13 20

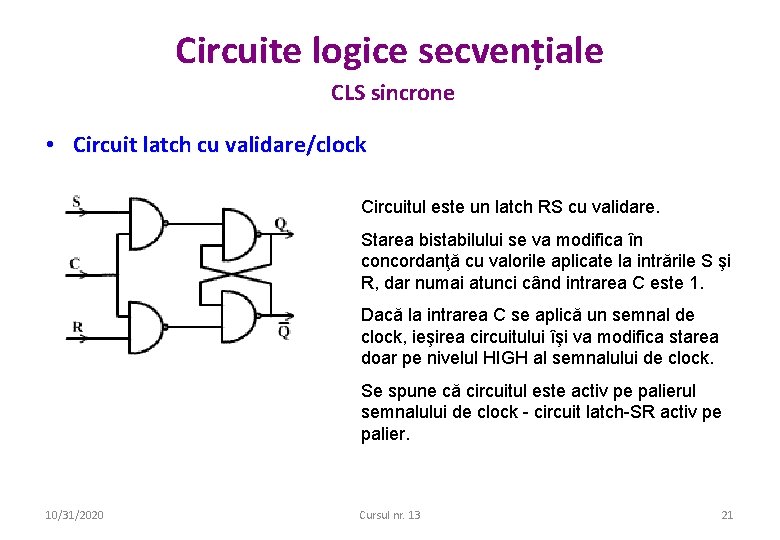

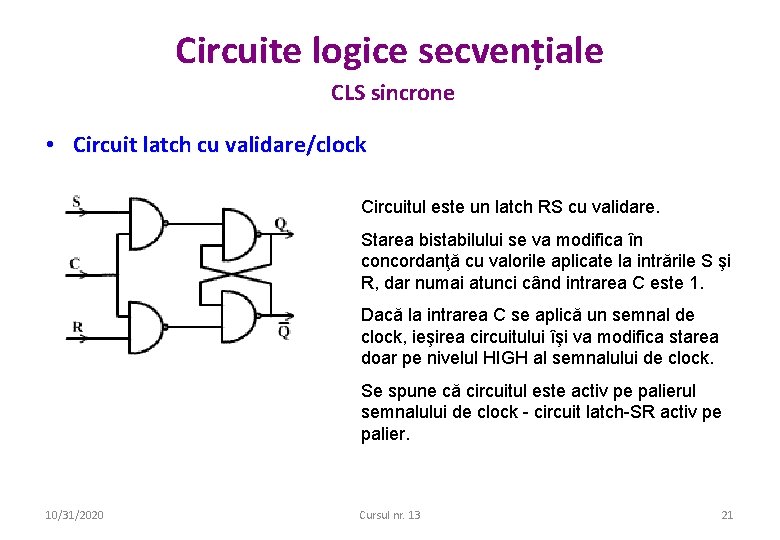

Circuite logice secvențiale CLS sincrone • Circuit latch cu validare/clock Circuitul este un latch RS cu validare. Starea bistabilului se va modifica în concordanţă cu valorile aplicate la intrările S şi R, dar numai atunci când intrarea C este 1. Dacă la intrarea C se aplică un semnal de clock, ieşirea circuitului îşi va modifica starea doar pe nivelul HIGH al semnalului de clock. Se spune că circuitul este activ pe palierul semnalului de clock - circuit latch-SR activ pe palier. 10/31/2020 Cursul nr. 13 21

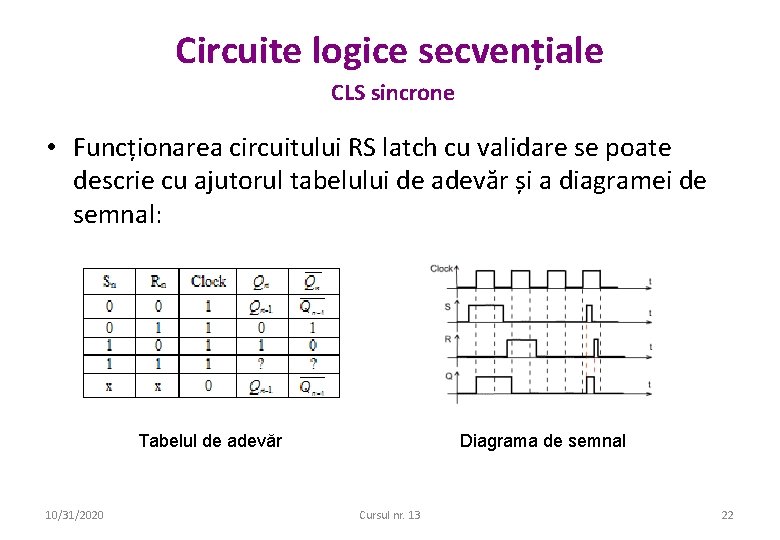

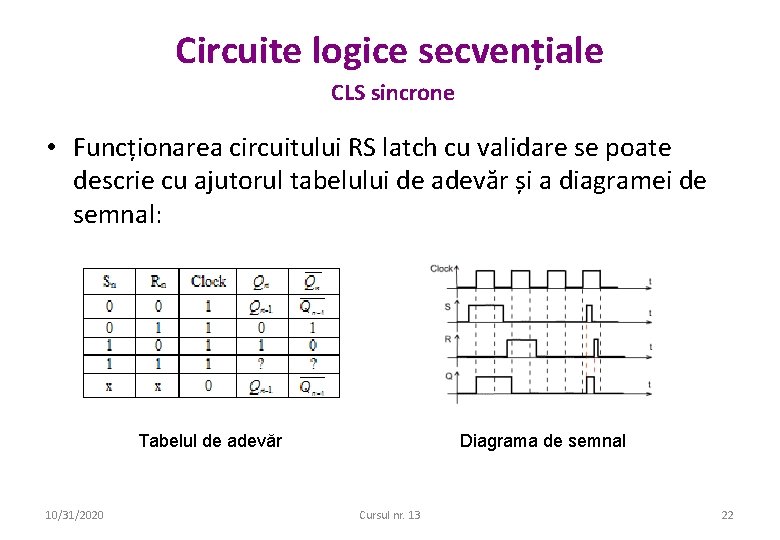

Circuite logice secvențiale CLS sincrone • Funcționarea circuitului RS latch cu validare se poate descrie cu ajutorul tabelului de adevăr și a diagramei de semnal: Tabelul de adevăr 10/31/2020 Diagrama de semnal Cursul nr. 13 22