ELECTRICAL ENGINEERING 4 Flip Flop 1 SetReset FlipFlop

![Crossed NAND Set-Reset Flip-Flop [1] 8 Crossed NAND Set-Reset Flip-Flop [1] 8](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-7.jpg)

![Crossed NAND Set-Reset Flip-Flop [2] 0 1 1 0 1 0 1 1 1 Crossed NAND Set-Reset Flip-Flop [2] 0 1 1 0 1 0 1 1 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-8.jpg)

![Crossed NAND Set-Reset Flip-Flop [3] 1 1 0 1 0 0 1 1 1 Crossed NAND Set-Reset Flip-Flop [3] 1 1 0 1 0 0 1 1 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-9.jpg)

![Crossed NAND Set-Reset Flip-Flop [4] 0 0 ? ? 1 1 0 0 1 Crossed NAND Set-Reset Flip-Flop [4] 0 0 ? ? 1 1 0 0 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-10.jpg)

![Crossed NAND Set-Reset Flip-Flop [5] 1 1 0 0 1 1 Unused State 1 Crossed NAND Set-Reset Flip-Flop [5] 1 1 0 0 1 1 Unused State 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-11.jpg)

![Crossed NAND Set-Reset Flip-Flop [6] 0 1 0 0 13 Crossed NAND Set-Reset Flip-Flop [6] 0 1 0 0 13](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-12.jpg)

![Crossed NOR Set-Reset Flip-Flop [1] 14 Crossed NOR Set-Reset Flip-Flop [1] 14](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-13.jpg)

![Crossed NOR Set-Reset Flip-Flop [2] 0 1 1 0 1 0 0 1 1 Crossed NOR Set-Reset Flip-Flop [2] 0 1 1 0 1 0 0 1 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-14.jpg)

![Crossed NOR Set-Reset Flip-Flop [3] 0 0 0 1 1 0 0 0 1 Crossed NOR Set-Reset Flip-Flop [3] 0 0 0 1 1 0 0 0 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-15.jpg)

![Crossed NOR Set-Reset Flip-Flop [4] 1 1 ? ? 0 0 1 0 1 Crossed NOR Set-Reset Flip-Flop [4] 1 1 ? ? 0 0 1 0 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-16.jpg)

![Crossed NOR Set-Reset Flip-Flop [5] 1 1 0 0 Unused State 1 0 0 Crossed NOR Set-Reset Flip-Flop [5] 1 1 0 0 Unused State 1 0 0](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-17.jpg)

![Crossed NOR Set-Reset Flip-Flop [6] 0 1 0 0 19 Crossed NOR Set-Reset Flip-Flop [6] 0 1 0 0 19](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-18.jpg)

![Using A Set-Reset Flip-Flop as a Debounce Switch [1] 21 Using A Set-Reset Flip-Flop as a Debounce Switch [1] 21](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-20.jpg)

![Using A Set-Reset Flip-Flop as a Debounce Switch [2] 22 Using A Set-Reset Flip-Flop as a Debounce Switch [2] 22](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-21.jpg)

![Using A Set-Reset Flip-Flop as a Debounce Switch [3] 23 Using A Set-Reset Flip-Flop as a Debounce Switch [3] 23](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-22.jpg)

![Gated Set-Reset Flip-Flop [1] 1 0 1 26 Gated Set-Reset Flip-Flop [1] 1 0 1 26](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-24.jpg)

![Gated Set-Reset Flip-Flop [2] 1 27 Gated Set-Reset Flip-Flop [2] 1 27](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-25.jpg)

![Gated Set-Reset Flip-Flop [3] 28 Gated Set-Reset Flip-Flop [3] 28](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-26.jpg)

![Gated Set-Reset Flip-Flop [4] 0 0 1 1 0 1 0 1 0 1 Gated Set-Reset Flip-Flop [4] 0 0 1 1 0 1 0 1 0 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-27.jpg)

![D Flip-Flop [1] 31 D Flip-Flop [1] 31](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-28.jpg)

![D Flip-Flop [2] 32 D Flip-Flop [2] 32](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-29.jpg)

![D Flip-Flop [3] 33 D Flip-Flop [3] 33](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-30.jpg)

![D Flip-Flop [4] D Clock 0 0 1 1 1 Unchanged State 0 1 D Flip-Flop [4] D Clock 0 0 1 1 1 Unchanged State 0 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-31.jpg)

![JK Flip-Flop [1] 36 JK Flip-Flop [1] 36](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-32.jpg)

![JK Flip-Flop [2] 37 JK Flip-Flop [2] 37](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-33.jpg)

![JK Flip-Flop [3] x 0 0 1 1 x 0 1 0 1 1 JK Flip-Flop [3] x 0 0 1 1 x 0 1 0 1 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-34.jpg)

- Slides: 47

ELECTRICAL ENGINEERING ครงท 4 ฟลปฟลอป (Flip – Flop) 1

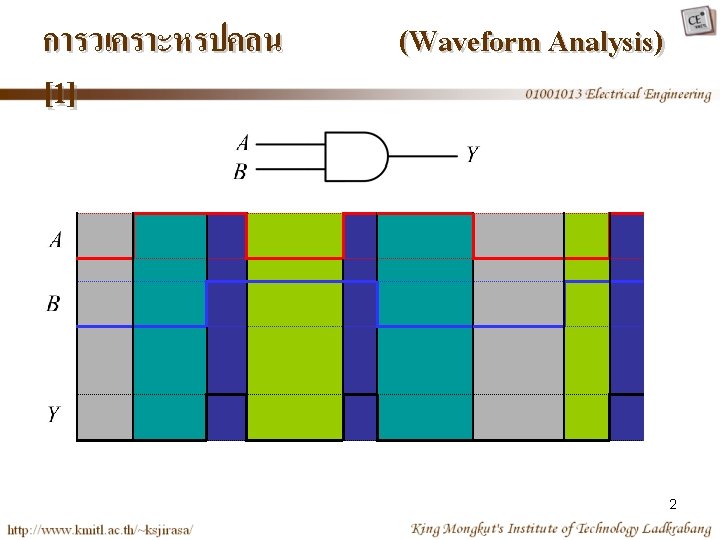

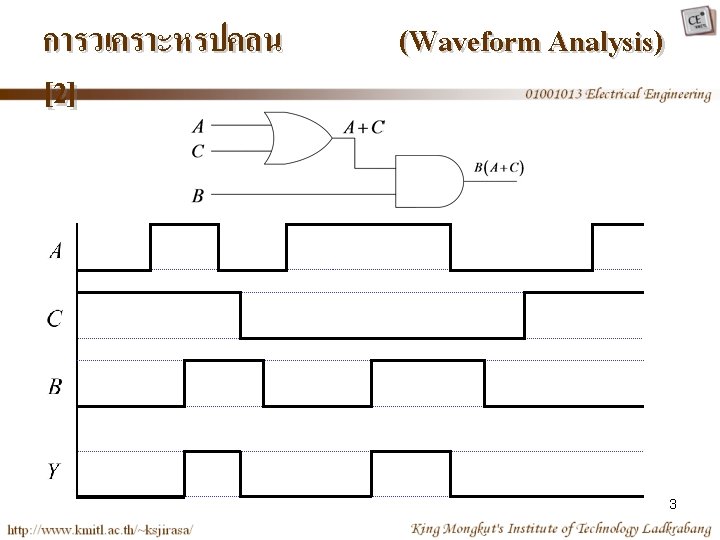

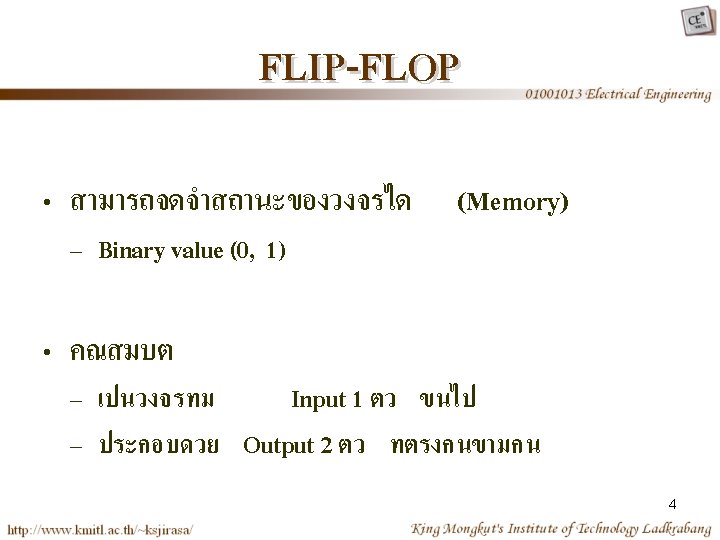

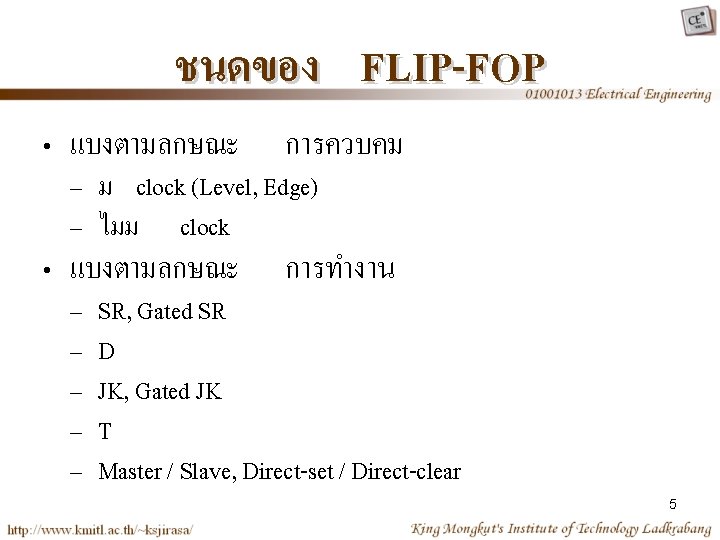

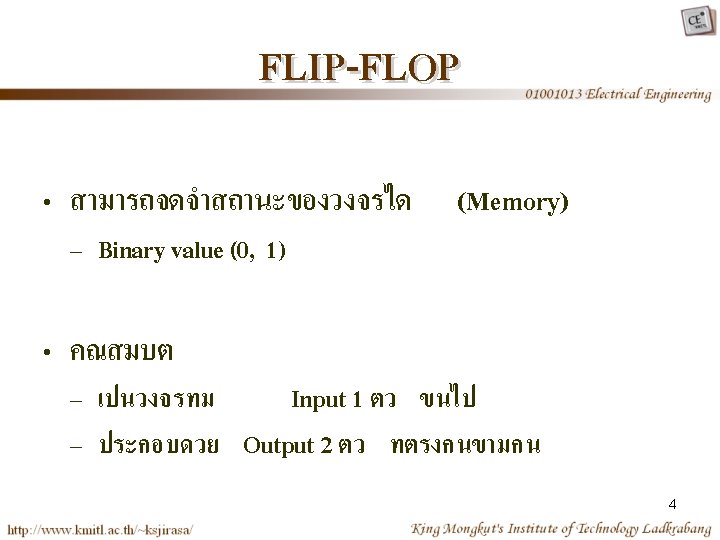

Set-Reset Flip-Flop Input Output 0 0 0 1 Reset State 1 0 Set State 1 1 Unchangeed State Unused State 7

![Crossed NAND SetReset FlipFlop 1 8 Crossed NAND Set-Reset Flip-Flop [1] 8](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-7.jpg)

Crossed NAND Set-Reset Flip-Flop [1] 8

![Crossed NAND SetReset FlipFlop 2 0 1 1 0 1 0 1 1 1 Crossed NAND Set-Reset Flip-Flop [2] 0 1 1 0 1 0 1 1 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-8.jpg)

Crossed NAND Set-Reset Flip-Flop [2] 0 1 1 0 1 0 1 1 1 0 9

![Crossed NAND SetReset FlipFlop 3 1 1 0 1 0 0 1 1 1 Crossed NAND Set-Reset Flip-Flop [3] 1 1 0 1 0 0 1 1 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-9.jpg)

Crossed NAND Set-Reset Flip-Flop [3] 1 1 0 1 0 0 1 1 1 0 10

![Crossed NAND SetReset FlipFlop 4 0 0 1 1 0 0 1 Crossed NAND Set-Reset Flip-Flop [4] 0 0 ? ? 1 1 0 0 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-10.jpg)

Crossed NAND Set-Reset Flip-Flop [4] 0 0 ? ? 1 1 0 0 1 1 1 0 11

![Crossed NAND SetReset FlipFlop 5 1 1 0 0 1 1 Unused State 1 Crossed NAND Set-Reset Flip-Flop [5] 1 1 0 0 1 1 Unused State 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-11.jpg)

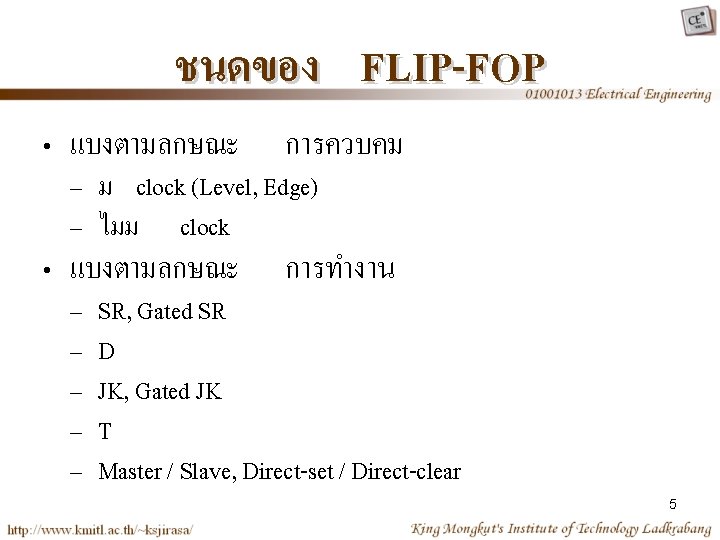

Crossed NAND Set-Reset Flip-Flop [5] 1 1 0 0 1 1 Unused State 1 0 0 1 1 0 Set State 0 1 1 0 0 1 Reset State 0 0 1 1 Unchangeed State 12

![Crossed NAND SetReset FlipFlop 6 0 1 0 0 13 Crossed NAND Set-Reset Flip-Flop [6] 0 1 0 0 13](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-12.jpg)

Crossed NAND Set-Reset Flip-Flop [6] 0 1 0 0 13

![Crossed NOR SetReset FlipFlop 1 14 Crossed NOR Set-Reset Flip-Flop [1] 14](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-13.jpg)

Crossed NOR Set-Reset Flip-Flop [1] 14

![Crossed NOR SetReset FlipFlop 2 0 1 1 0 1 0 0 1 1 Crossed NOR Set-Reset Flip-Flop [2] 0 1 1 0 1 0 0 1 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-14.jpg)

Crossed NOR Set-Reset Flip-Flop [2] 0 1 1 0 1 0 0 1 1 0 15

![Crossed NOR SetReset FlipFlop 3 0 0 0 1 1 0 0 0 1 Crossed NOR Set-Reset Flip-Flop [3] 0 0 0 1 1 0 0 0 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-15.jpg)

Crossed NOR Set-Reset Flip-Flop [3] 0 0 0 1 1 0 0 0 1 0 1 0 0 1 1 0 16

![Crossed NOR SetReset FlipFlop 4 1 1 0 0 1 0 1 Crossed NOR Set-Reset Flip-Flop [4] 1 1 ? ? 0 0 1 0 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-16.jpg)

Crossed NOR Set-Reset Flip-Flop [4] 1 1 ? ? 0 0 1 0 1 0 0 1 1 0 17

![Crossed NOR SetReset FlipFlop 5 1 1 0 0 Unused State 1 0 0 Crossed NOR Set-Reset Flip-Flop [5] 1 1 0 0 Unused State 1 0 0](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-17.jpg)

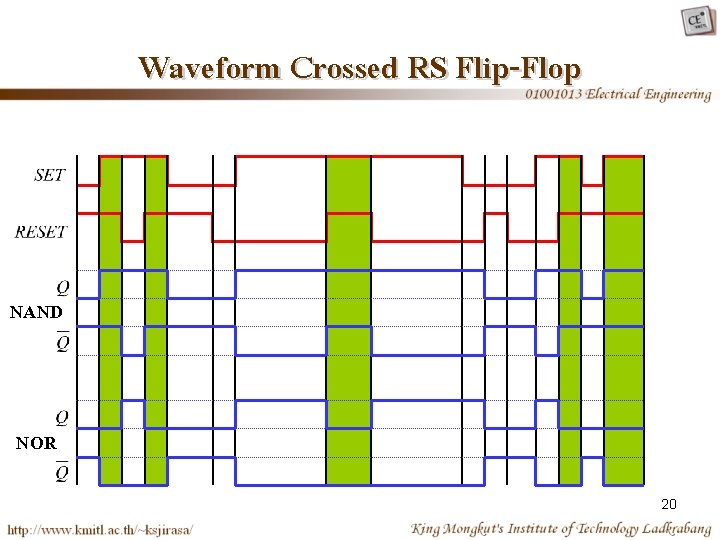

Crossed NOR Set-Reset Flip-Flop [5] 1 1 0 0 Unused State 1 0 0 1 1 0 Set State 0 1 1 0 0 1 Reset State 0 0 1 1 Unchanged State 18

![Crossed NOR SetReset FlipFlop 6 0 1 0 0 19 Crossed NOR Set-Reset Flip-Flop [6] 0 1 0 0 19](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-18.jpg)

Crossed NOR Set-Reset Flip-Flop [6] 0 1 0 0 19

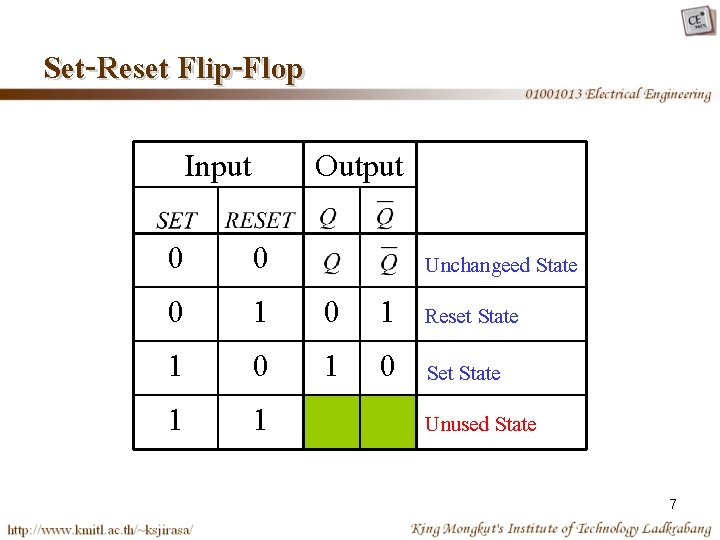

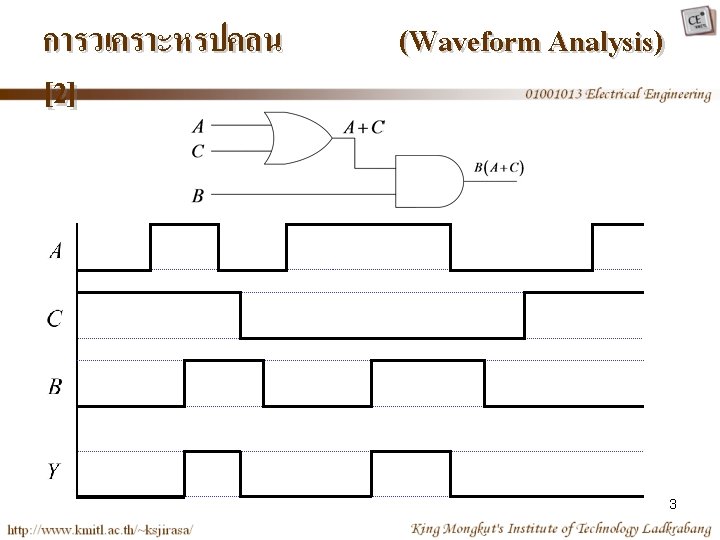

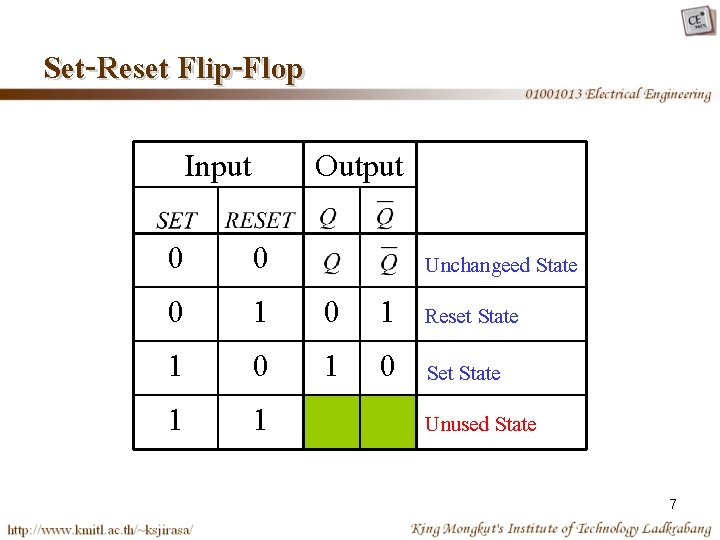

Waveform Crossed RS Flip-Flop NAND NOR 20

![Using A SetReset FlipFlop as a Debounce Switch 1 21 Using A Set-Reset Flip-Flop as a Debounce Switch [1] 21](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-20.jpg)

Using A Set-Reset Flip-Flop as a Debounce Switch [1] 21

![Using A SetReset FlipFlop as a Debounce Switch 2 22 Using A Set-Reset Flip-Flop as a Debounce Switch [2] 22](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-21.jpg)

Using A Set-Reset Flip-Flop as a Debounce Switch [2] 22

![Using A SetReset FlipFlop as a Debounce Switch 3 23 Using A Set-Reset Flip-Flop as a Debounce Switch [3] 23](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-22.jpg)

Using A Set-Reset Flip-Flop as a Debounce Switch [3] 23

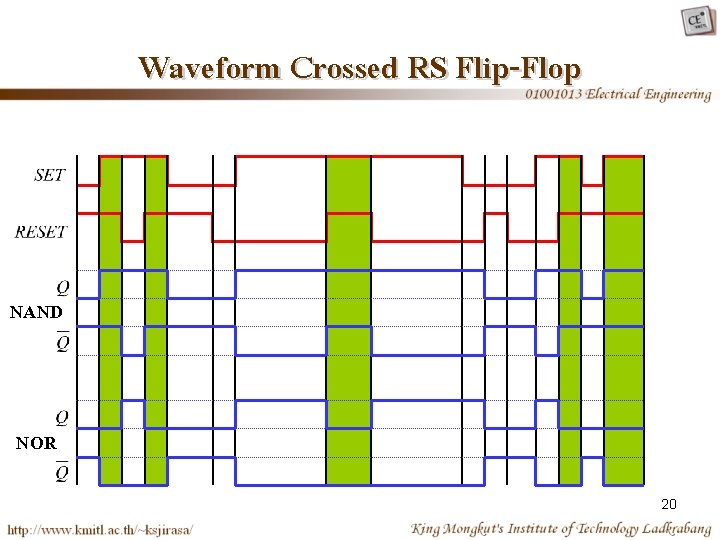

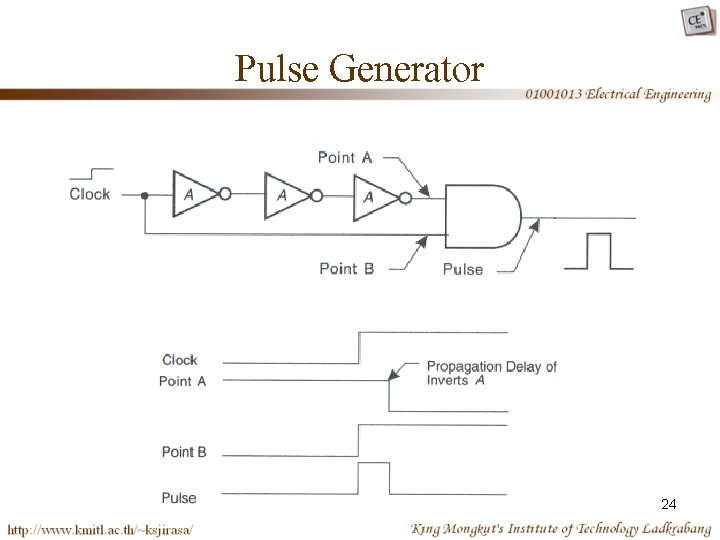

Pulse Generator 24

![Gated SetReset FlipFlop 1 1 0 1 26 Gated Set-Reset Flip-Flop [1] 1 0 1 26](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-24.jpg)

Gated Set-Reset Flip-Flop [1] 1 0 1 26

![Gated SetReset FlipFlop 2 1 27 Gated Set-Reset Flip-Flop [2] 1 27](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-25.jpg)

Gated Set-Reset Flip-Flop [2] 1 27

![Gated SetReset FlipFlop 3 28 Gated Set-Reset Flip-Flop [3] 28](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-26.jpg)

Gated Set-Reset Flip-Flop [3] 28

![Gated SetReset FlipFlop 4 0 0 1 1 0 1 0 1 0 1 Gated Set-Reset Flip-Flop [4] 0 0 1 1 0 1 0 1 0 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-27.jpg)

Gated Set-Reset Flip-Flop [4] 0 0 1 1 0 1 0 1 0 1 1 1 0 1 Unchangeed State Reset State Set State Unused State 29

![D FlipFlop 1 31 D Flip-Flop [1] 31](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-28.jpg)

D Flip-Flop [1] 31

![D FlipFlop 2 32 D Flip-Flop [2] 32](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-29.jpg)

D Flip-Flop [2] 32

![D FlipFlop 3 33 D Flip-Flop [3] 33](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-30.jpg)

D Flip-Flop [3] 33

![D FlipFlop 4 D Clock 0 0 1 1 1 Unchanged State 0 1 D Flip-Flop [4] D Clock 0 0 1 1 1 Unchanged State 0 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-31.jpg)

D Flip-Flop [4] D Clock 0 0 1 1 1 Unchanged State 0 1 1 0 34

![JK FlipFlop 1 36 JK Flip-Flop [1] 36](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-32.jpg)

JK Flip-Flop [1] 36

![JK FlipFlop 2 37 JK Flip-Flop [2] 37](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-33.jpg)

JK Flip-Flop [2] 37

![JK FlipFlop 3 x 0 0 1 1 x 0 1 0 1 1 JK Flip-Flop [3] x 0 0 1 1 x 0 1 0 1 1](https://slidetodoc.com/presentation_image/c18fc3bd27a39b444175b554c3661989/image-34.jpg)

JK Flip-Flop [3] x 0 0 1 1 x 0 1 0 1 1 0 38

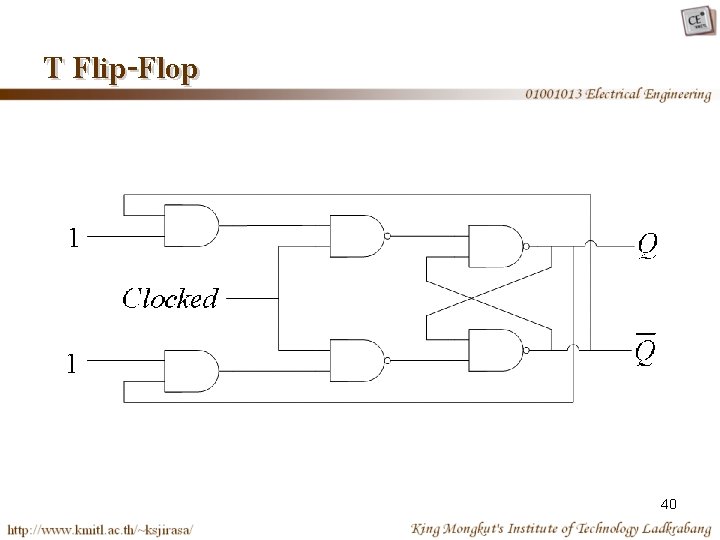

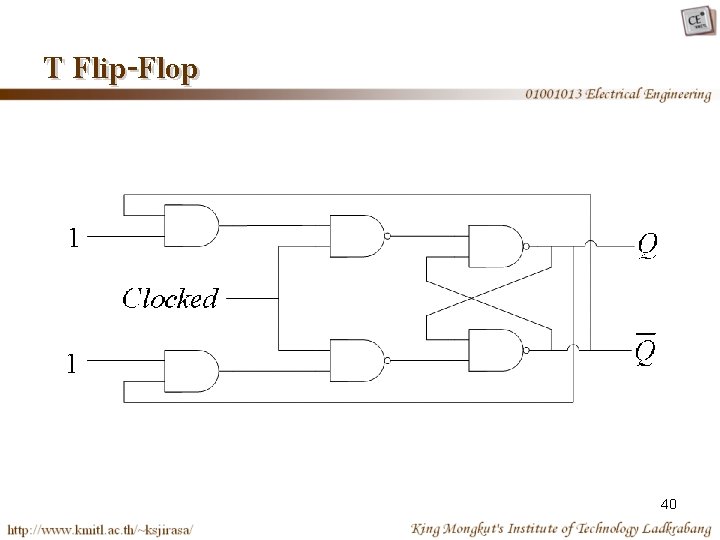

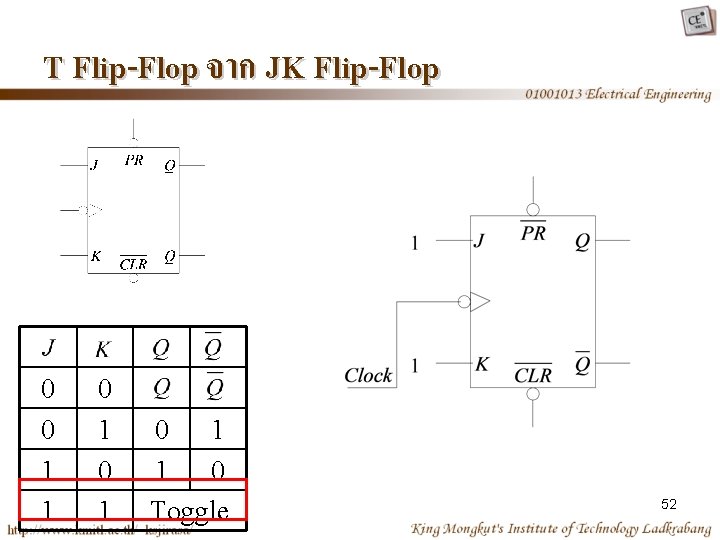

T Flip-Flop 40

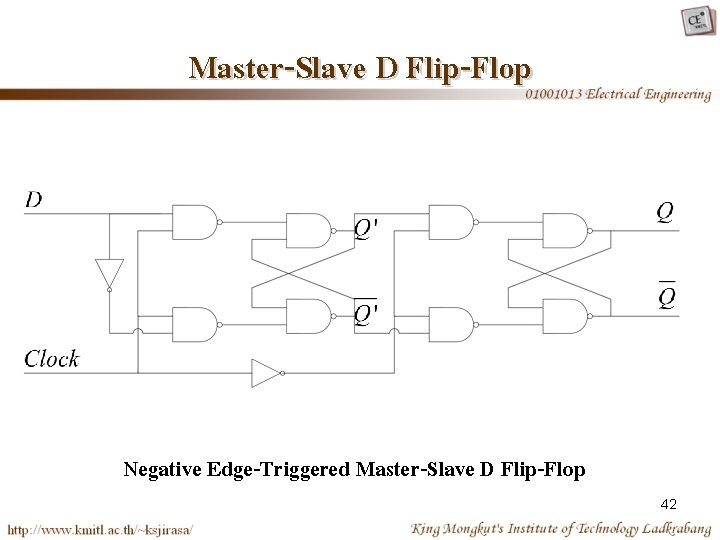

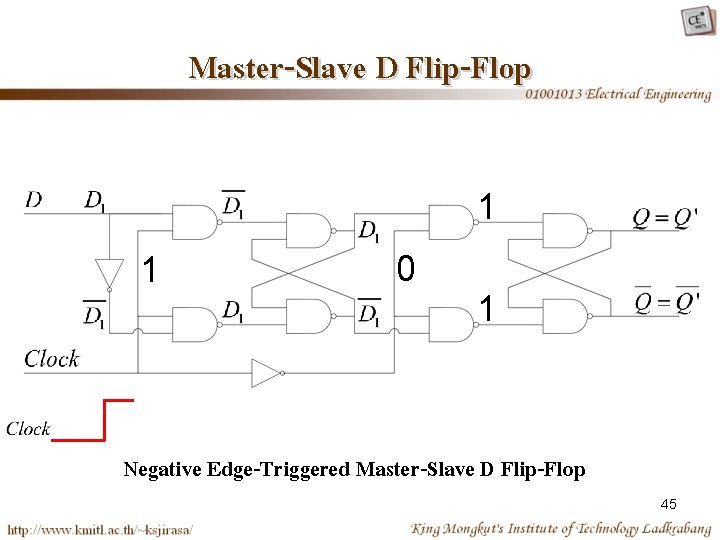

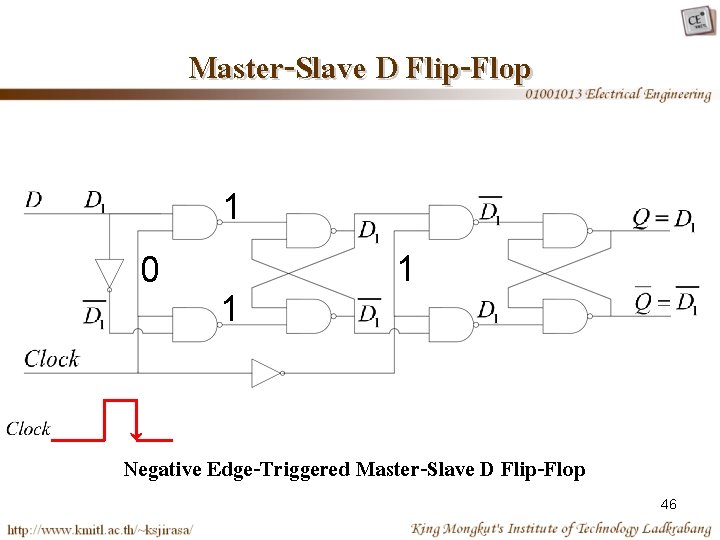

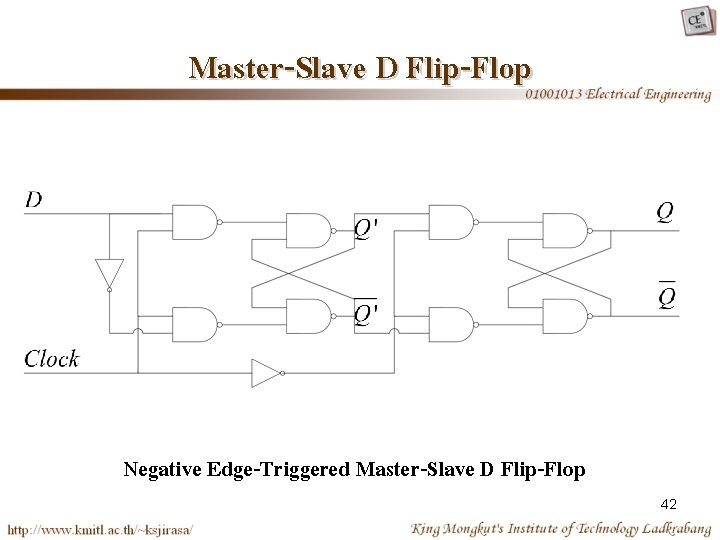

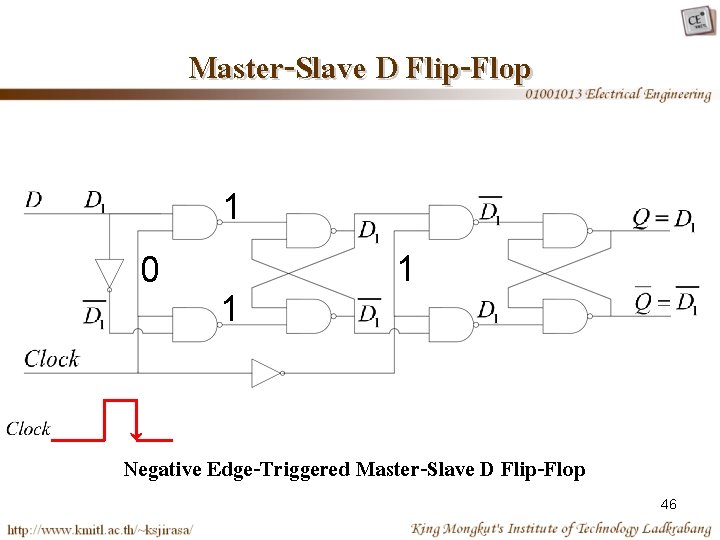

Master-Slave D Flip-Flop Negative Edge-Triggered Master-Slave D Flip-Flop 42

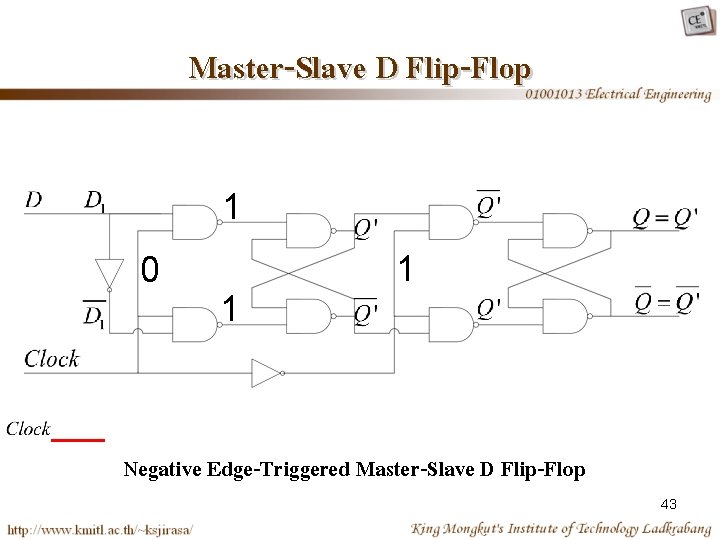

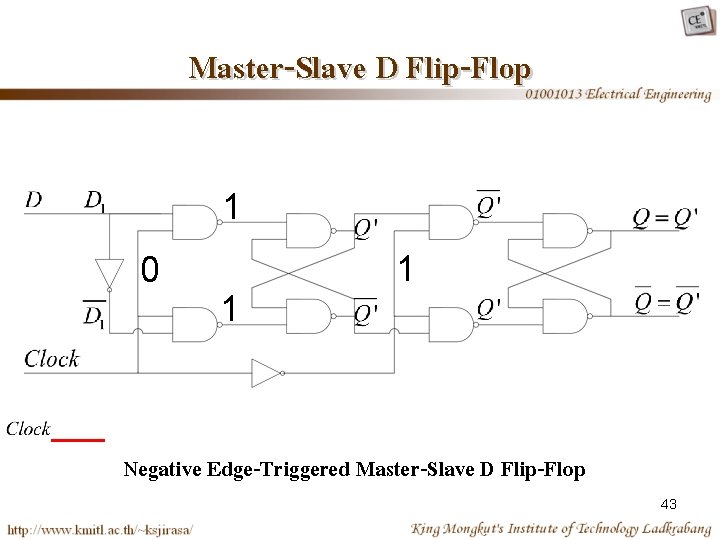

Master-Slave D Flip-Flop 1 0 1 1 Negative Edge-Triggered Master-Slave D Flip-Flop 43

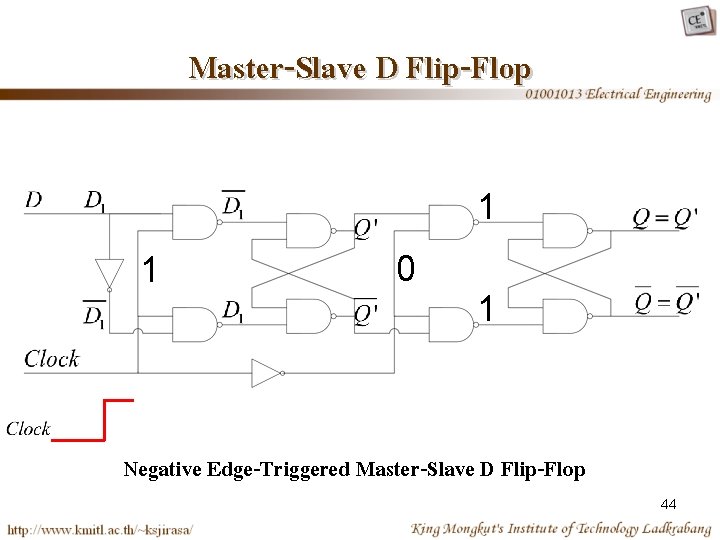

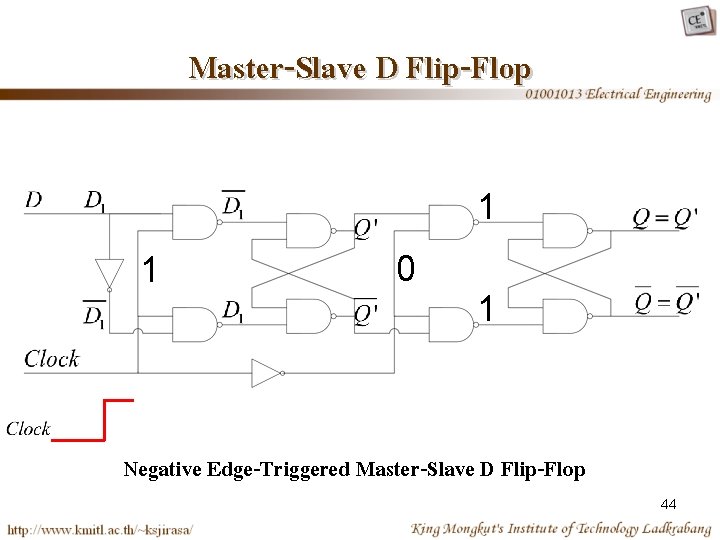

Master-Slave D Flip-Flop 1 1 0 1 Negative Edge-Triggered Master-Slave D Flip-Flop 44

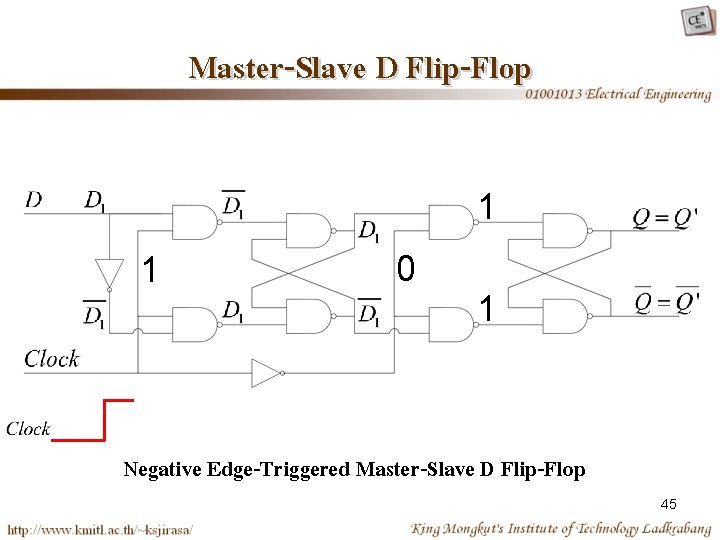

Master-Slave D Flip-Flop 1 1 0 1 Negative Edge-Triggered Master-Slave D Flip-Flop 45

Master-Slave D Flip-Flop 1 0 1 1 Negative Edge-Triggered Master-Slave D Flip-Flop 46

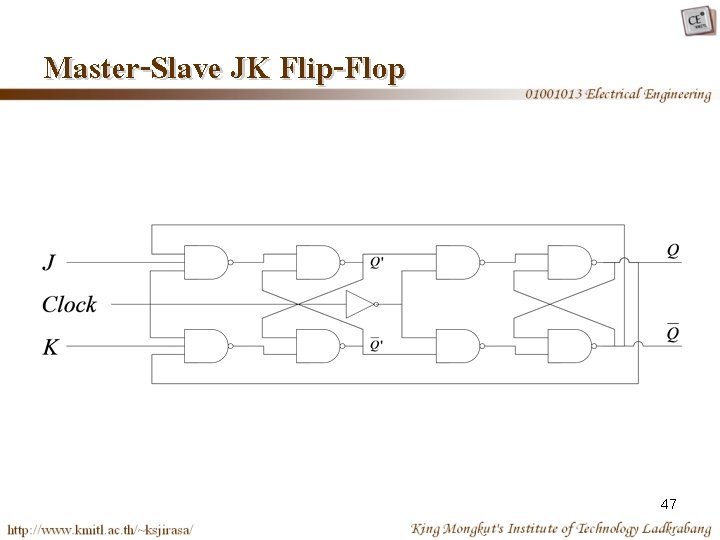

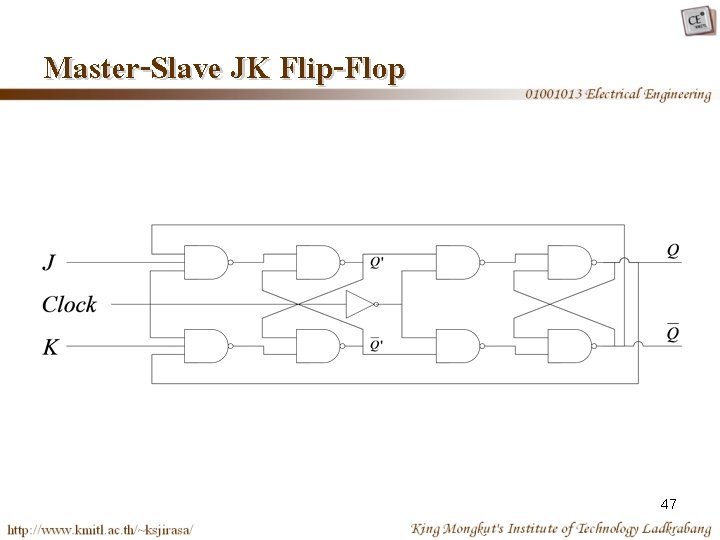

Master-Slave JK Flip-Flop 47

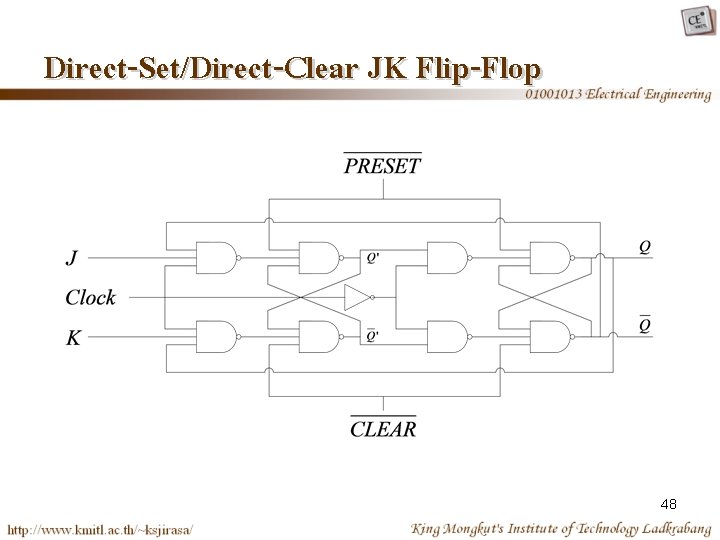

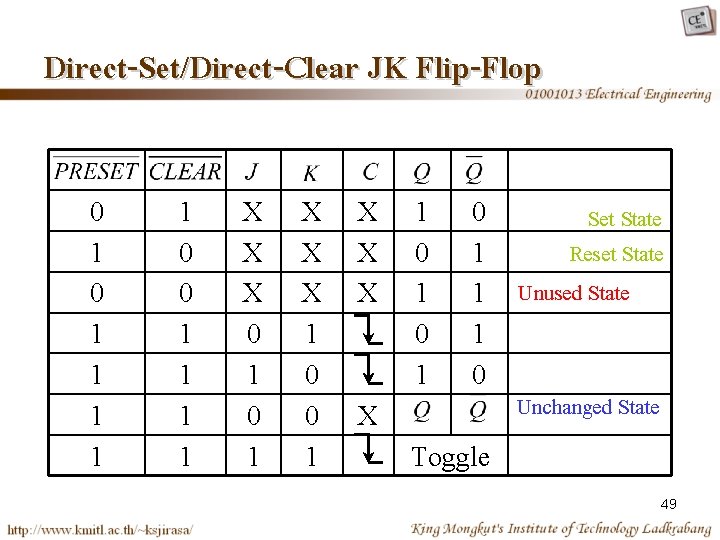

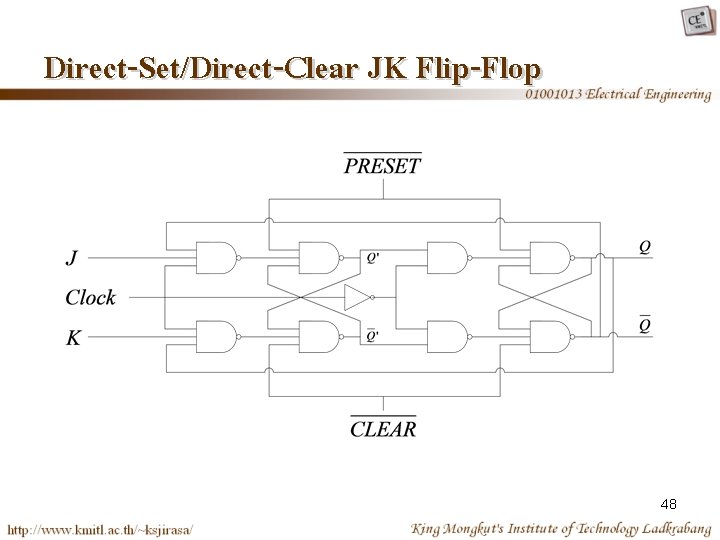

Direct-Set/Direct-Clear JK Flip-Flop 48

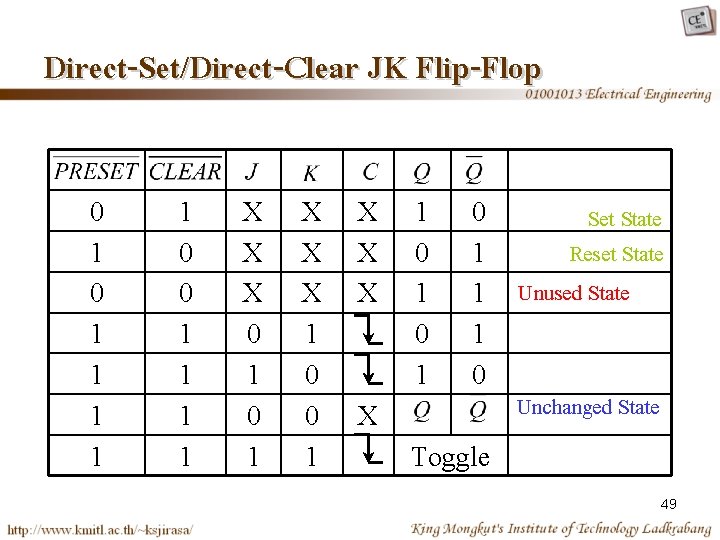

Direct-Set/Direct-Clear JK Flip-Flop 0 1 1 1 0 0 1 1 X X X 0 1 X X X 1 0 1 0 1 1 1 0 X Set State Reset State Unused State Unchanged State Toggle 49

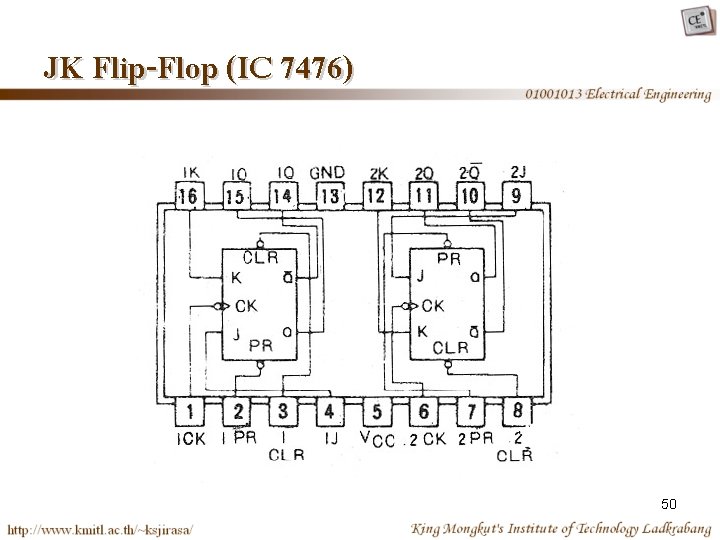

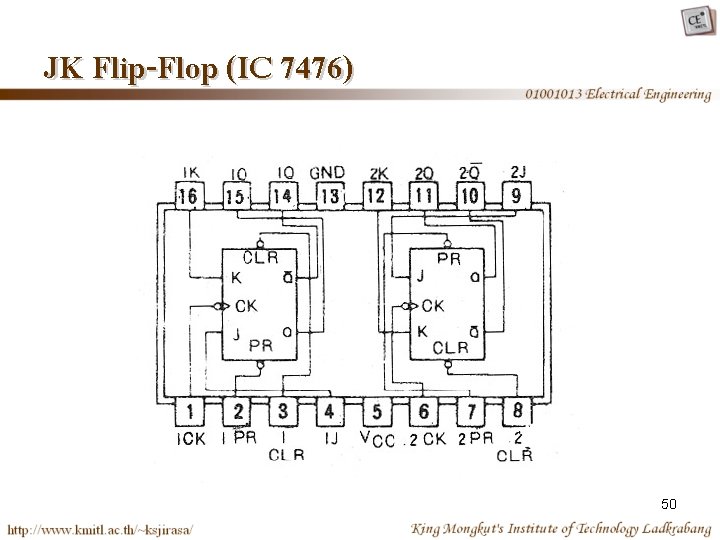

JK Flip-Flop (IC 7476) 50

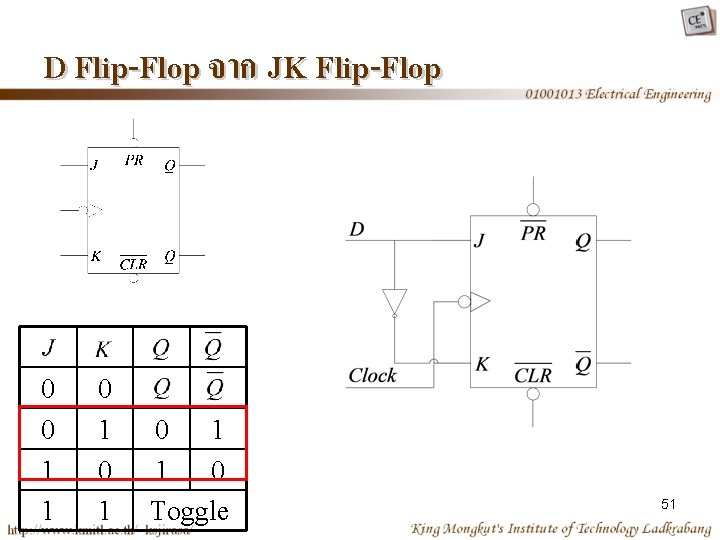

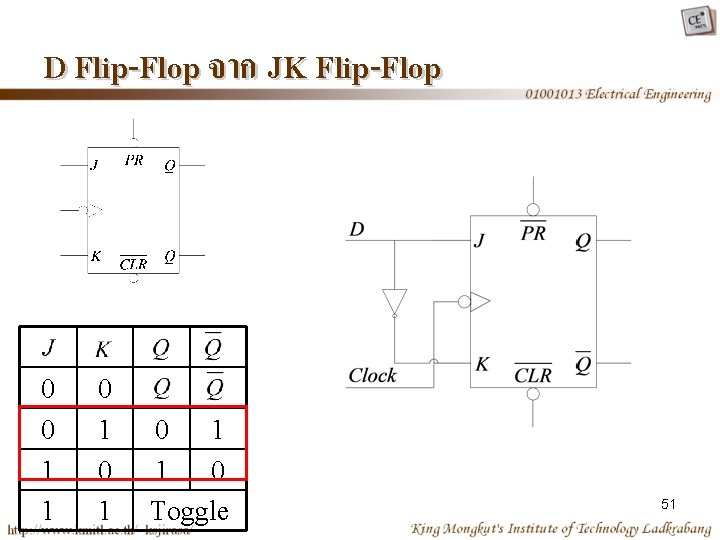

D Flip-Flop จาก JK Flip-Flop 0 0 1 1 0 1 0 1 1 0 Toggle 51

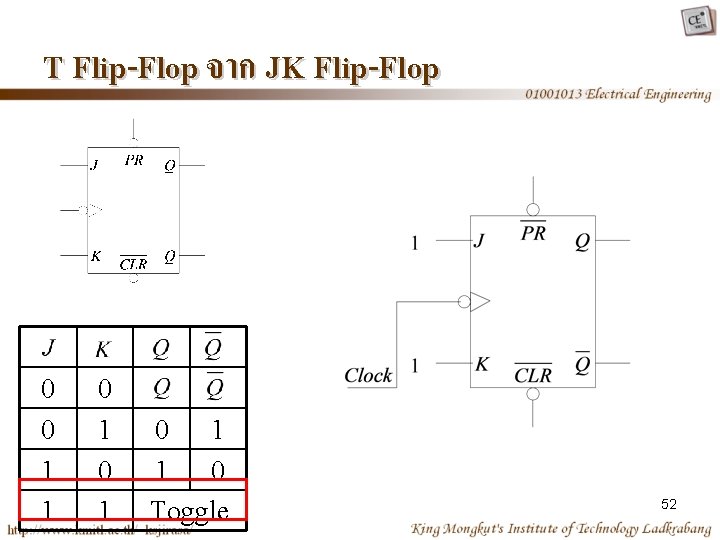

T Flip-Flop จาก JK Flip-Flop 0 0 1 1 0 1 0 1 1 0 Toggle 52

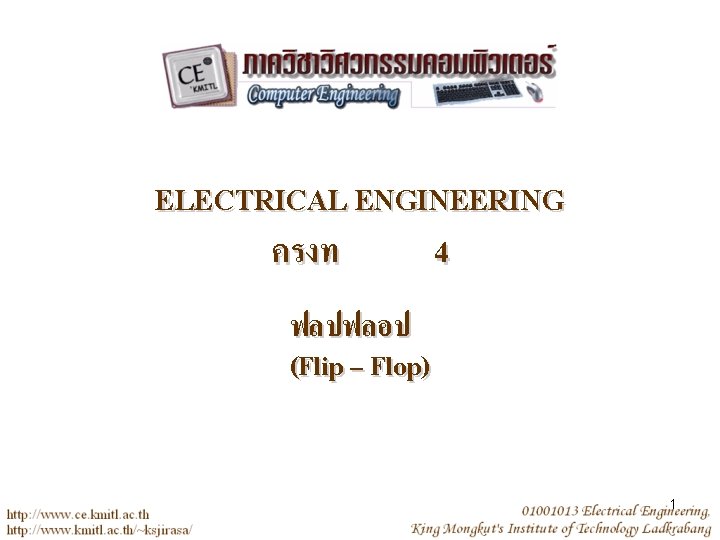

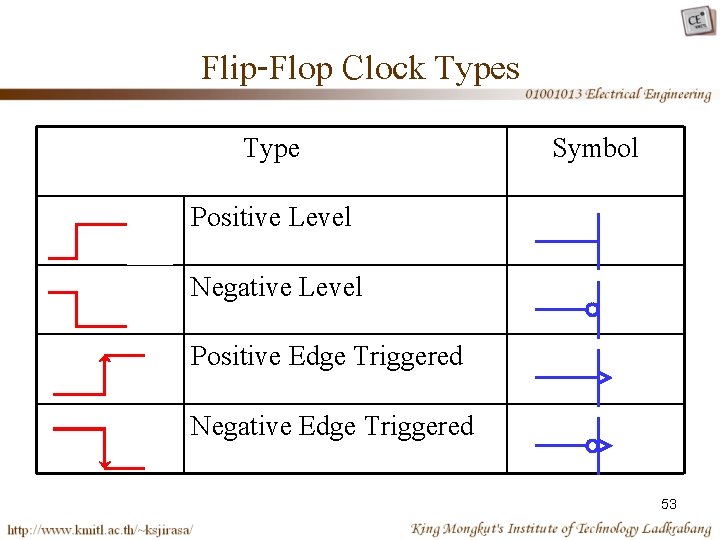

Flip-Flop Clock Types Type Symbol Positive Level Negative Level Positive Edge Triggered Negative Edge Triggered 53