ELEC 7250 VLSI Testing Spring 2004 Experimental Analysis

- Slides: 9

ELEC 7250: VLSI Testing Spring 2004 Experimental Analysis of Fault Collapsing Methods Dixit, Ayoush M

Testing Why? - Processing defects due to fabrication technology need to be addressed - Defects in devices cause faults to exist. How do we go about testing devices? Fault Models Structural testing allows designers to develop algorithms to detect faults present in the system with the help of Fault Models. How? -Collapsing is done based on different criteria. -Possible ways to collapse faults are dominance collapsing, equivalent collapsing, functional collapsing, etc.

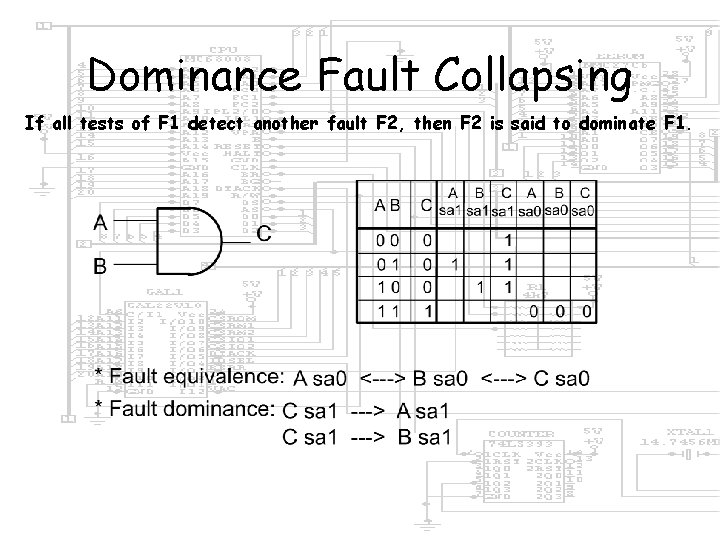

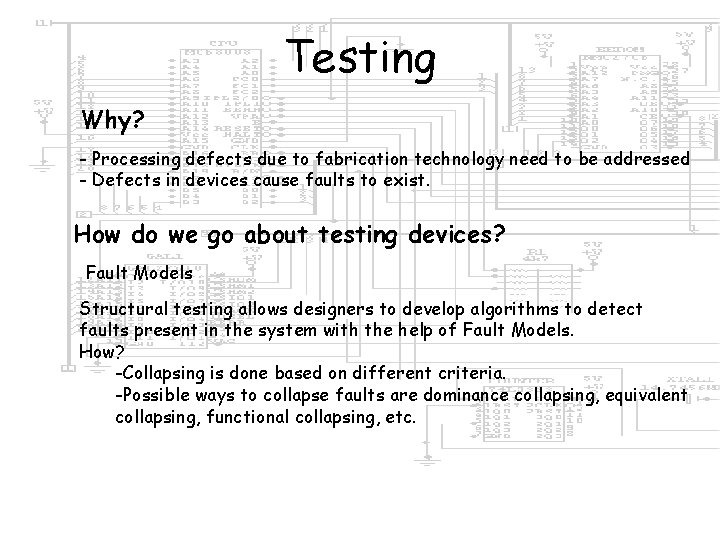

Dominance Fault Collapsing If all tests of F 1 detect another fault F 2, then F 2 is said to dominate F 1.

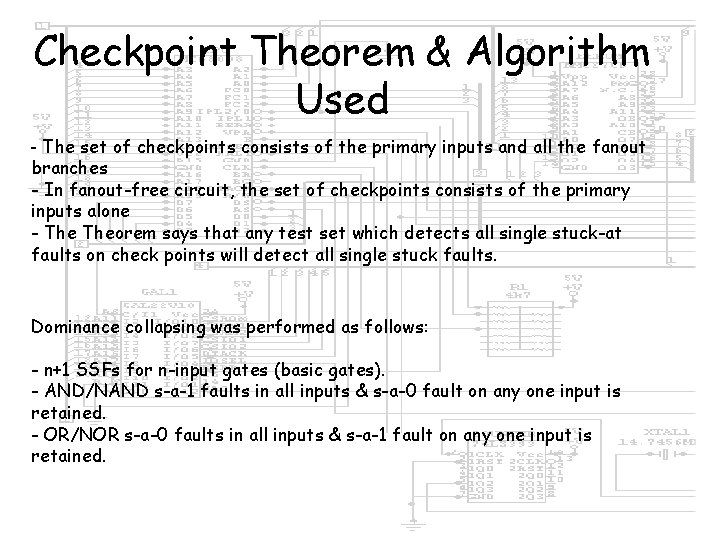

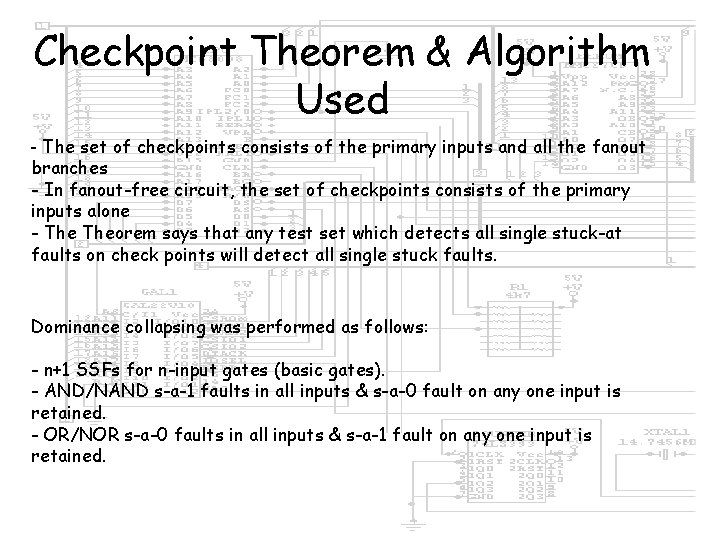

Checkpoint Theorem & Algorithm Used - The set of checkpoints consists of the primary inputs and all the fanout branches - In fanout-free circuit, the set of checkpoints consists of the primary inputs alone - Theorem says that any test set which detects all single stuck-at faults on check points will detect all single stuck faults. Dominance collapsing was performed as follows: - n+1 SSFs for n-input gates (basic gates). - AND/NAND s-a-1 faults in all inputs & s-a-0 fault on any one input is retained. - OR/NOR s-a-0 faults in all inputs & s-a-1 fault on any one input is retained.

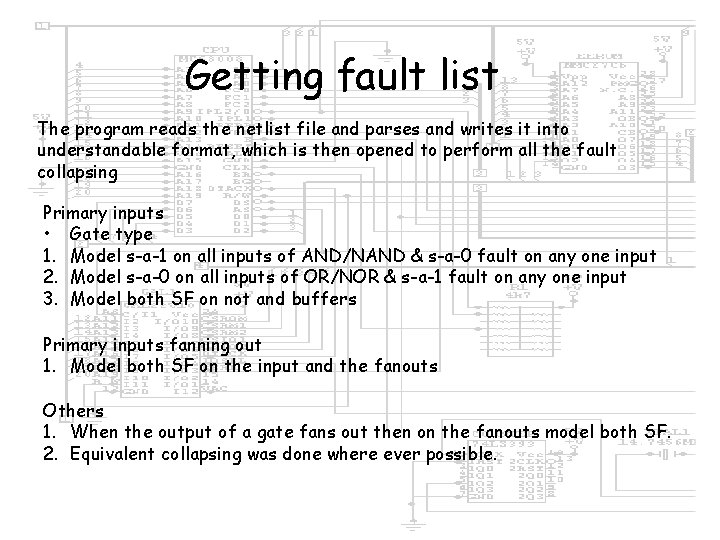

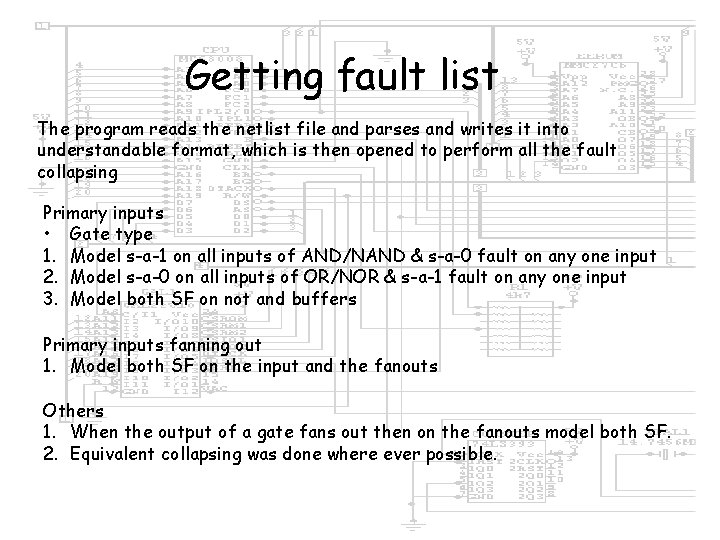

Getting fault list The program reads the netlist file and parses and writes it into understandable format, which is then opened to perform all the fault collapsing Primary inputs • Gate type 1. Model s-a-1 on all inputs of AND/NAND & s-a-0 fault on any one input 2. Model s-a-0 on all inputs of OR/NOR & s-a-1 fault on any one input 3. Model both SF on not and buffers Primary inputs fanning out 1. Model both SF on the input and the fanouts Others 1. When the output of a gate fans out then on the fanouts model both SF. 2. Equivalent collapsing was done where ever possible.

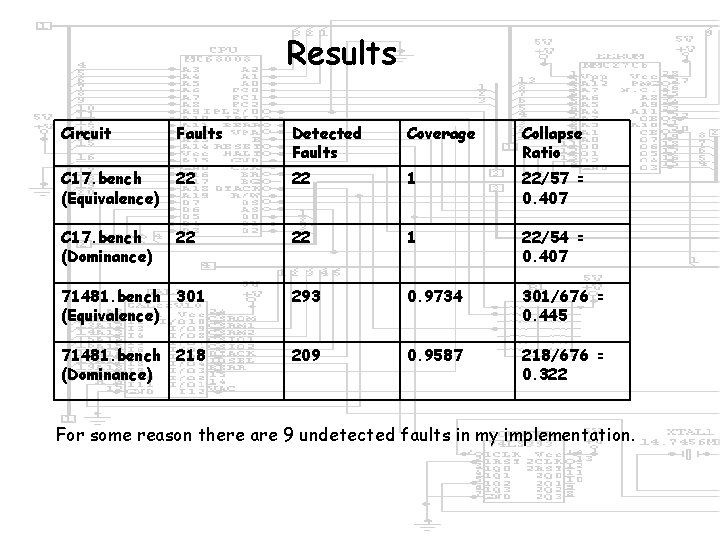

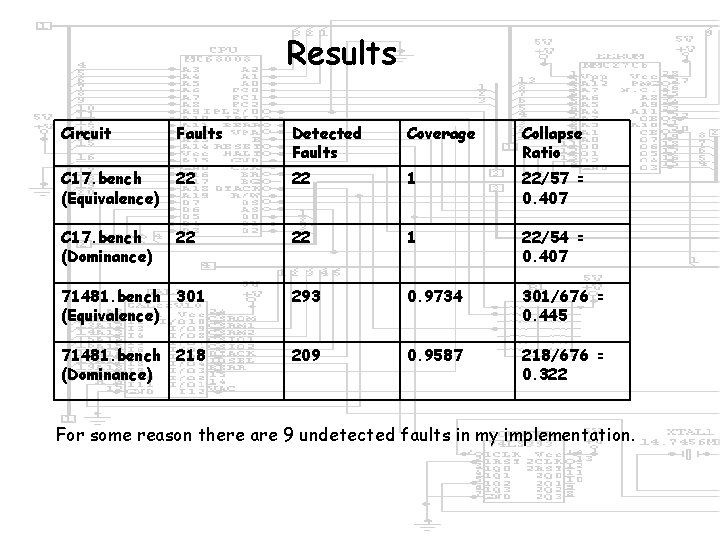

Results and Conclusion Circuit Faults Detected Faults Coverage Collapse Ratio C 17. bench (Equivalence) 22 22 1 22/57 = 0. 407 C 17. bench (Dominance) 22 22 1 22/54 = 0. 407 71481. bench 301 (Equivalence) 293 0. 9734 301/676 = 0. 445 71481. bench 218 (Dominance) 209 0. 9587 218/676 = 0. 322 For some reason there are 9 undetected faults in my implementation.

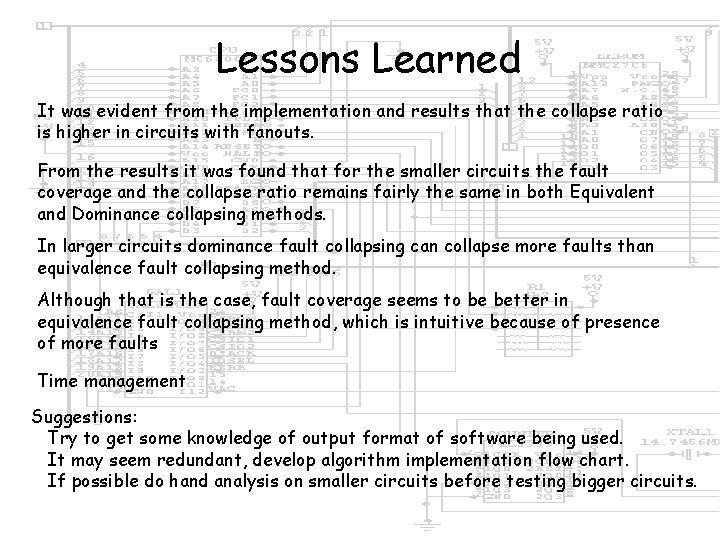

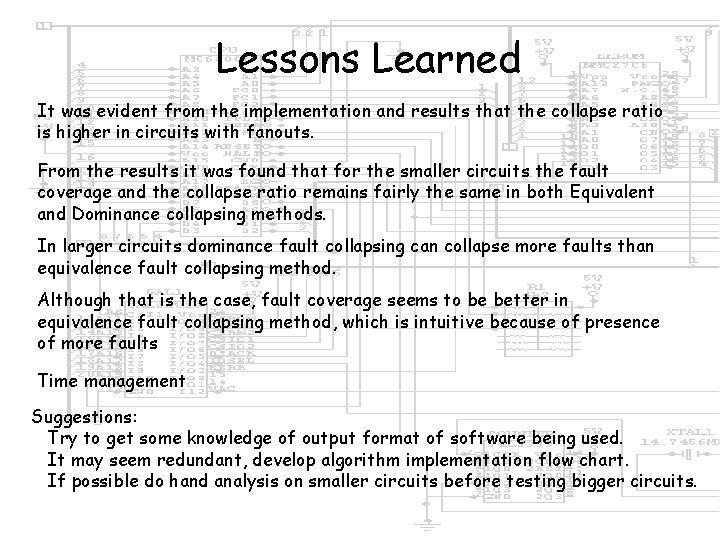

Results and Conclusion Lessons Learned It was evident from the implementation and results that the collapse ratio is higher in circuits with fanouts. From the results it was found that for the smaller circuits the fault coverage and the collapse ratio remains fairly the same in both Equivalent and Dominance collapsing methods. In larger circuits dominance fault collapsing can collapse more faults than equivalence fault collapsing method. Although that is the case, fault coverage seems to be better in equivalence fault collapsing method, which is intuitive because of presence of more faults Time management Suggestions: Try to get some knowledge of output format of software being used. It may seem redundant, develop algorithm implementation flow chart. If possible do hand analysis on smaller circuits before testing bigger circuits.

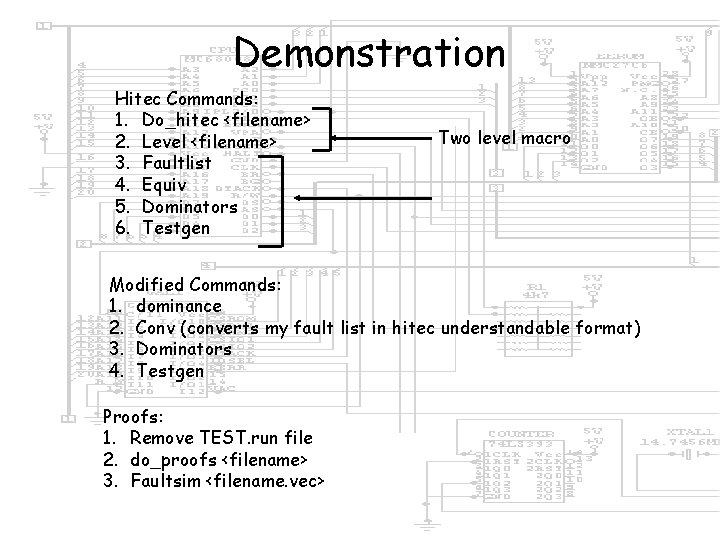

Results and Conclusion Demonstration Hitec Commands: 1. Do_hitec <filename> 2. Level <filename> 3. Faultlist 4. Equiv 5. Dominators 6. Testgen Two level macro Modified Commands: 1. dominance 2. Conv (converts my fault list in hitec understandable format) 3. Dominators 4. Testgen Proofs: 1. Remove TEST. run file 2. do_proofs <filename> 3. Faultsim <filename. vec>

Results and Conclusion Discussions C is buggy while reading a file. If the end of line is found right after the end of the token read strtok puts that with the last read token. This creates problem when the comparison vector is not the last file token read from another file. Even though the strings are equal, strcmp cannot do anything. So, since I knew that the naming file ends right after the second vector, add in "n" to the vector read from the fault file. Comments and questions can also be directed to dixitam@auburn. edu Thank you for your time.