ELEC 5970 0016970 001Fall 2005 Special Topics in

- Slides: 16

ELEC 5970 -001/6970 -001(Fall 2005) Special Topics in Electrical Engineering Low-Power Design of Electronic Circuits Dynamic Power Vishwani D. Agrawal James J. Danaher Professor Department of Electrical and Computer Engineering Auburn University http: //www. eng. auburn. edu/~vagrawal@eng. auburn. edu 9/13/05 ELEC 5970 -001/6970 -001 Lecture 6 1

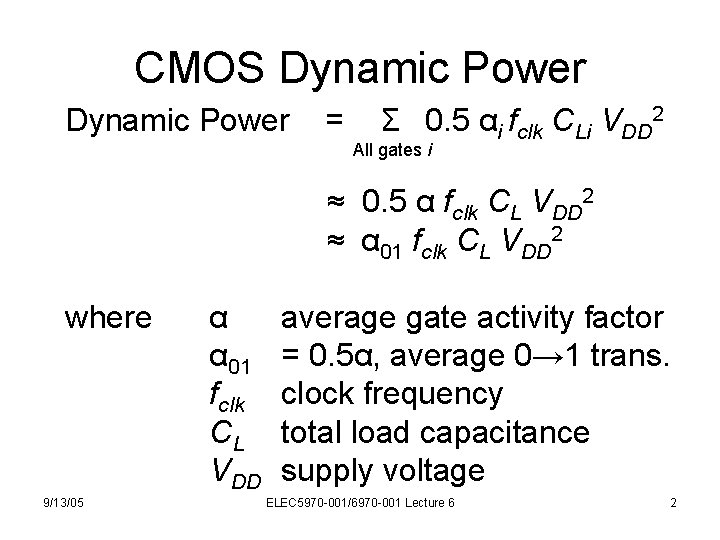

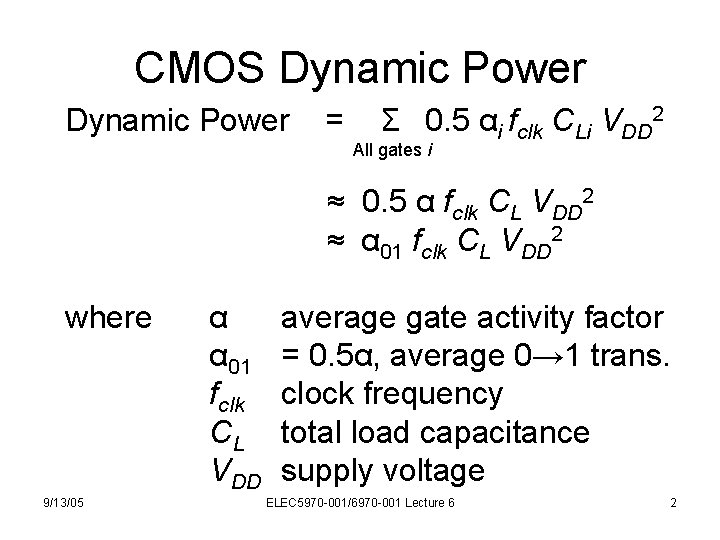

CMOS Dynamic Power = Σ 0. 5 αi fclk CLi VDD 2 All gates i ≈ 0. 5 α fclk CL VDD 2 ≈ α 01 fclk CL VDD 2 where 9/13/05 α α 01 fclk CL VDD average gate activity factor = 0. 5α, average 0→ 1 trans. clock frequency total load capacitance supply voltage ELEC 5970 -001/6970 -001 Lecture 6 2

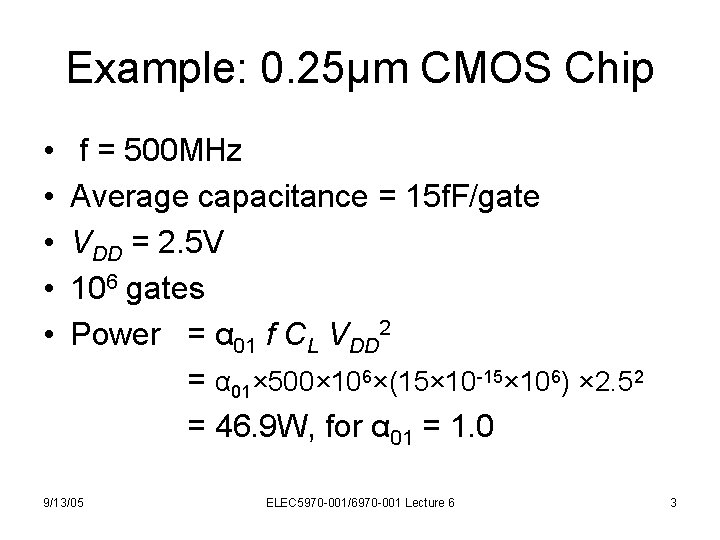

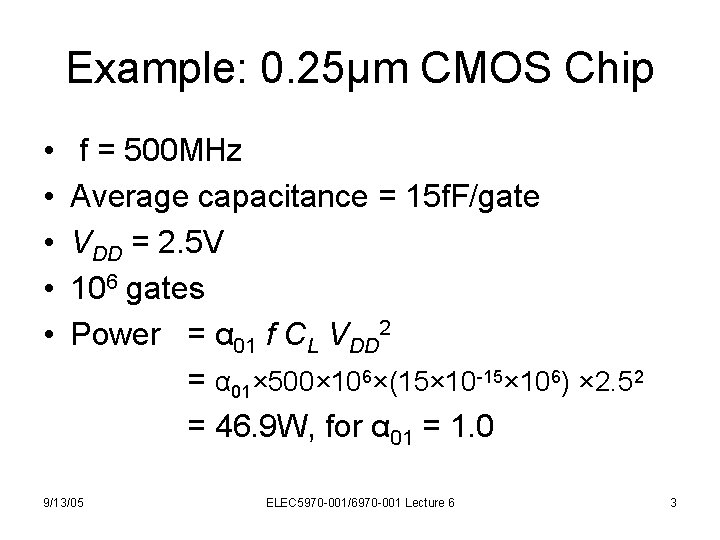

Example: 0. 25μm CMOS Chip • • • f = 500 MHz Average capacitance = 15 f. F/gate VDD = 2. 5 V 106 gates Power = α 01 f CL VDD 2 = α 01× 500× 106×(15× 10 -15× 106) × 2. 52 = 46. 9 W, for α 01 = 1. 0 9/13/05 ELEC 5970 -001/6970 -001 Lecture 6 3

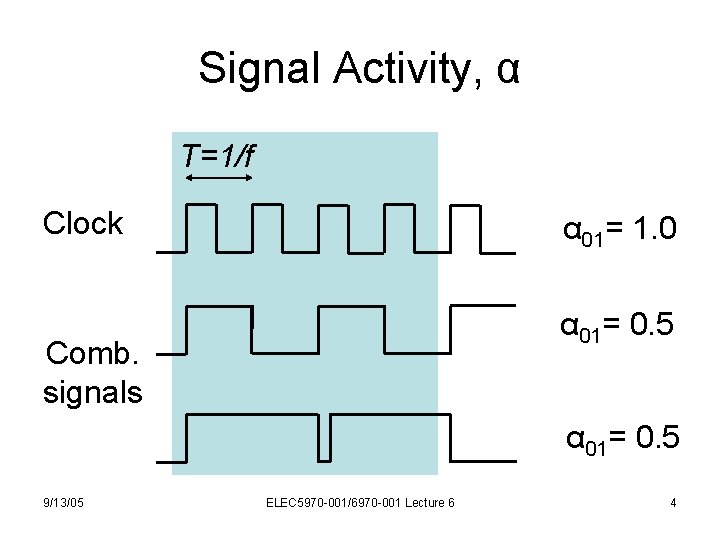

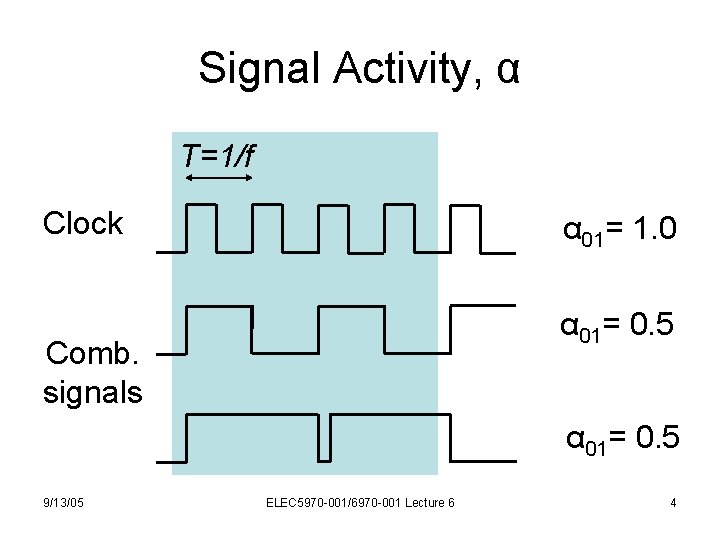

Signal Activity, α T=1/f Clock α 01= 1. 0 α 01= 0. 5 Comb. signals α 01= 0. 5 9/13/05 ELEC 5970 -001/6970 -001 Lecture 6 4

Reducing Dynamic Power • Dynamic power reduction is – Quadratic with reduction of supply voltage – Linear with reduction of capacitance 9/13/05 ELEC 5970 -001/6970 -001 Lecture 6 5

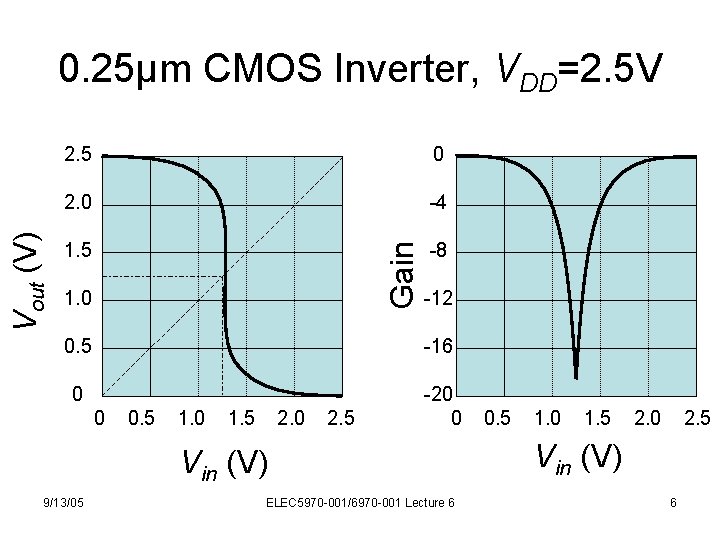

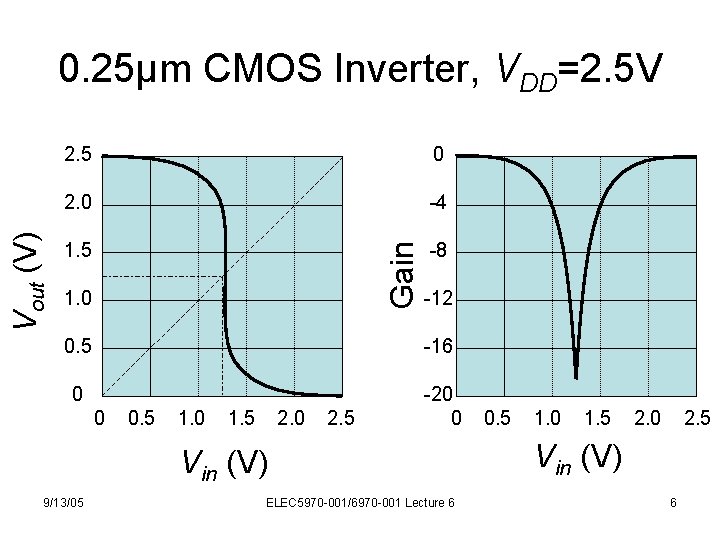

2. 5 0 2. 0 -4 1. 5 -8 Gain Vout (V) 0. 25μm CMOS Inverter, VDD=2. 5 V 1. 0 -12 0. 5 -16 0 -20 0 0 0. 5 1. 0 1. 5 2. 0 2. 5 Vin (V) 9/13/05 ELEC 5970 -001/6970 -001 Lecture 6 0. 5 1. 0 1. 5 2. 0 2. 5 Vin (V) 6

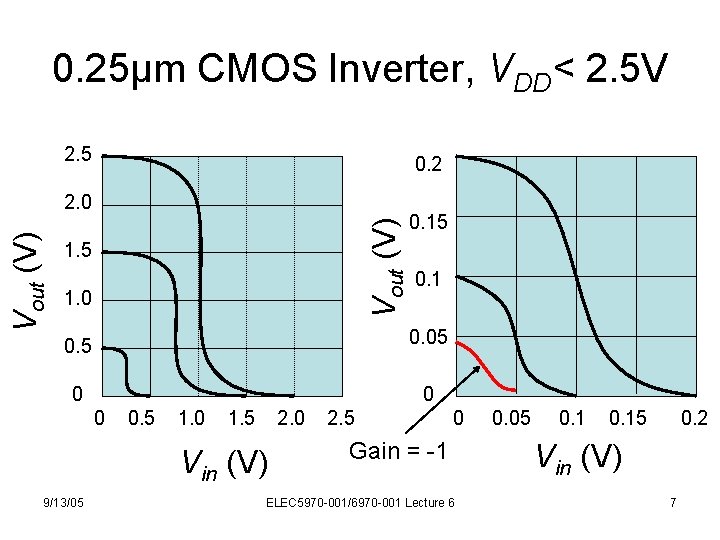

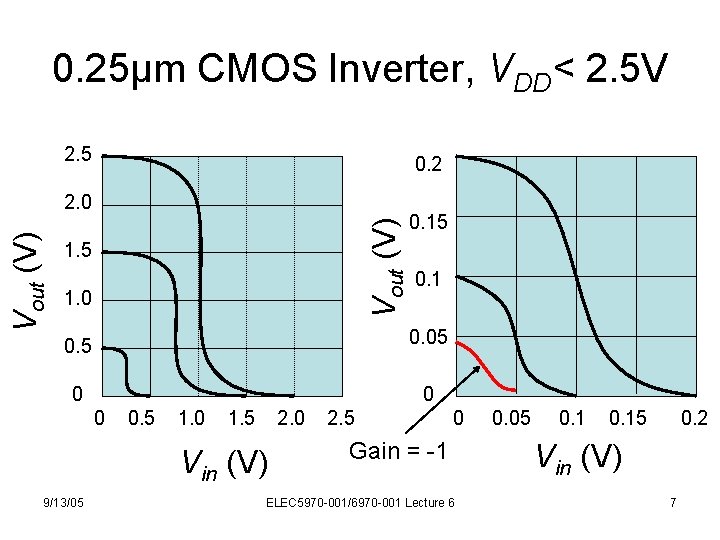

0. 25μm CMOS Inverter, VDD< 2. 5 V 2. 5 0. 2 Vout (V) 2. 0 1. 5 1. 0 0. 15 0. 1 0. 5 0. 05 0 0. 5 1. 0 1. 5 2. 0 Vin (V) 9/13/05 2. 5 0 Gain = -1 ELEC 5970 -001/6970 -001 Lecture 6 0. 05 0. 15 0. 2 Vin (V) 7

Lower Bound on VDD • For properation of gate, maximum gain (for Vin = VDD/2) should be greater than 1. • Gainmax = -(1/n)[exp(VDD /2ΦT) – 1] = -1 • n = 1. 5 • ΦT = k. T/q = 26 m. V • VDD = 48 V • VDDmin > 2 to 4 times k. T/q or ~100 m. V at room temperature (27 o. C) • Ref. : J. M. Rabaey, A. Chandrakasan and B. Nikolić, Digital Integrated Circuits, Upper Saddle River, New Jersey: Pearson Education, 2003. 9/13/05 ELEC 5970 -001/6970 -001 Lecture 6 8

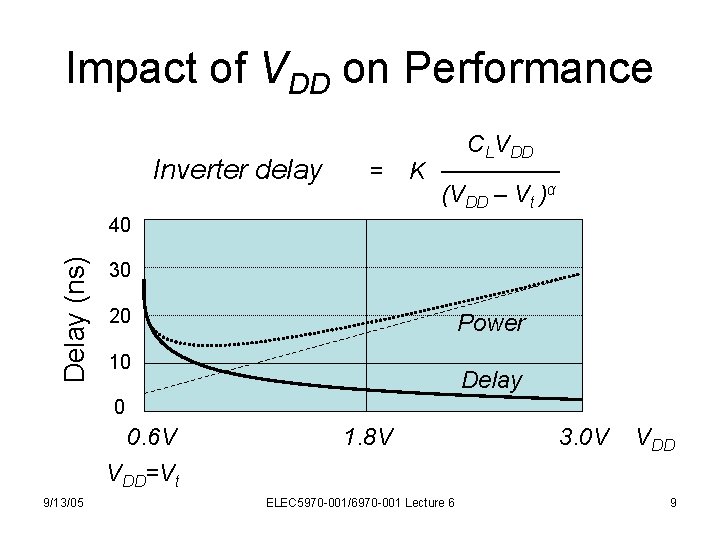

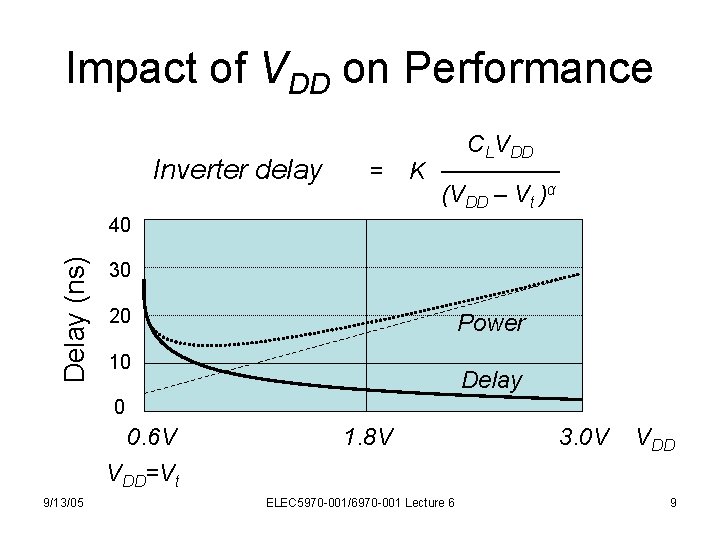

Impact of VDD on Performance Inverter delay = CLVDD K ─────── (VDD – Vt )α Delay (ns) 40 30 20 Power 10 Delay 0 0. 6 V VDD=Vt 9/13/05 1. 8 V ELEC 5970 -001/6970 -001 Lecture 6 3. 0 V VDD 9

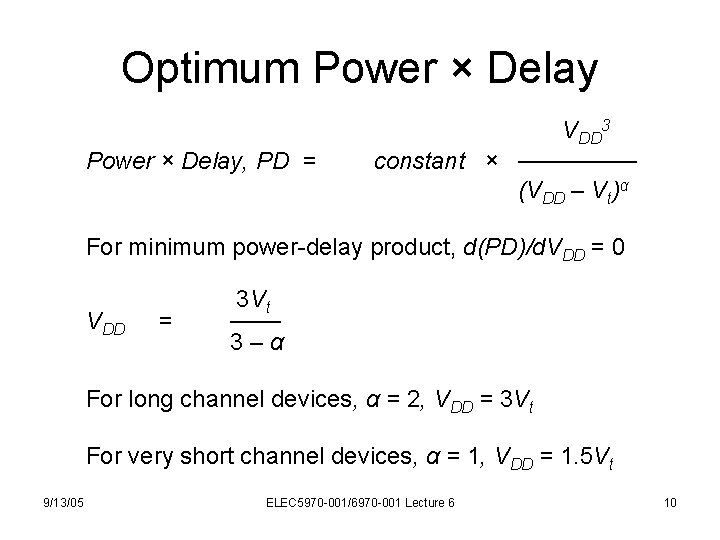

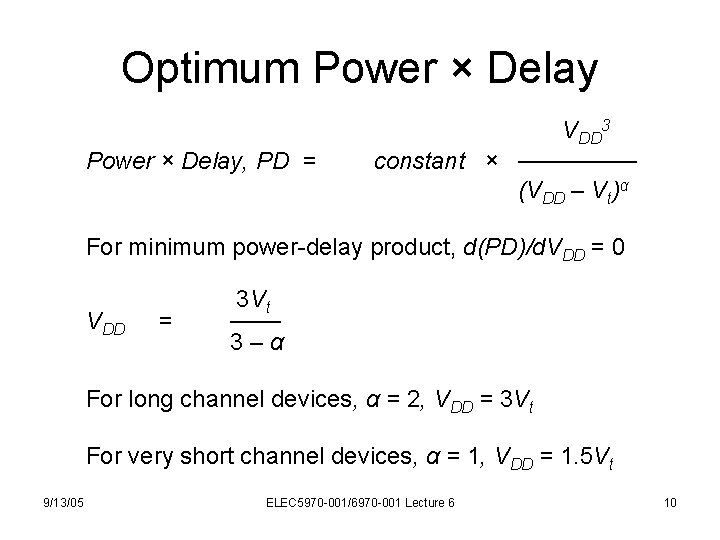

Optimum Power × Delay, PD = VDD 3 constant × ─────── (VDD – Vt)α For minimum power-delay product, d(PD)/d. VDD = 0 VDD = 3 Vt ─── 3–α For long channel devices, α = 2, VDD = 3 Vt For very short channel devices, α = 1, VDD = 1. 5 Vt 9/13/05 ELEC 5970 -001/6970 -001 Lecture 6 10

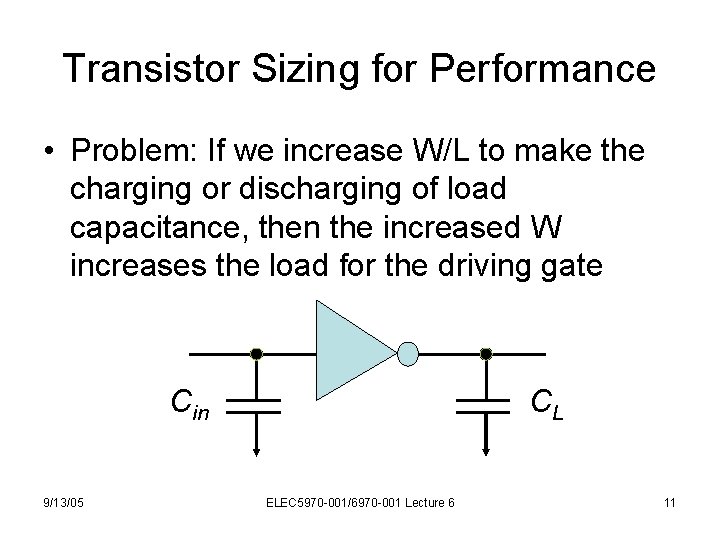

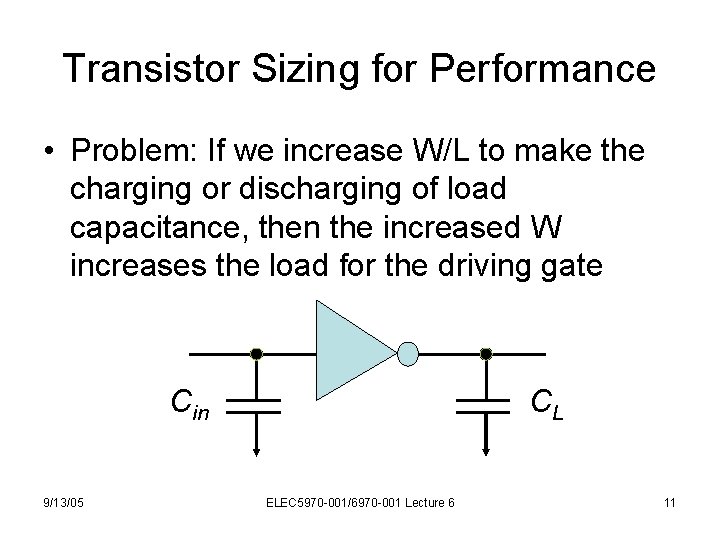

Transistor Sizing for Performance • Problem: If we increase W/L to make the charging or discharging of load capacitance, then the increased W increases the load for the driving gate Cin 9/13/05 CL ELEC 5970 -001/6970 -001 Lecture 6 11

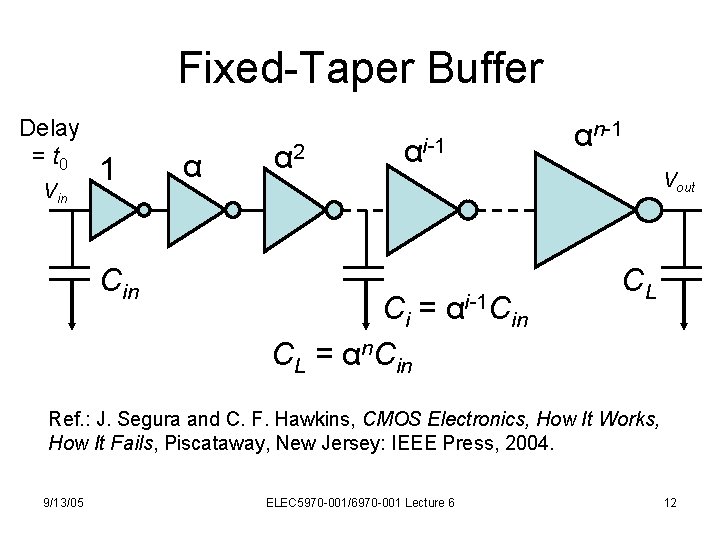

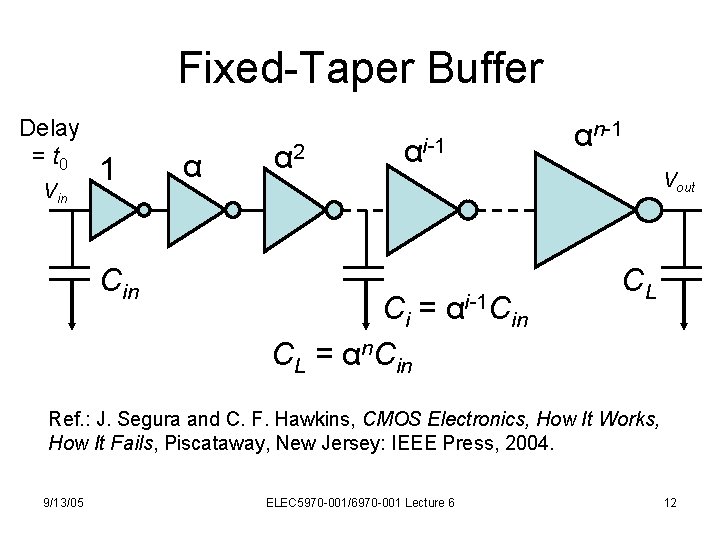

Fixed-Taper Buffer Delay = t 0 Vin 1 Cin α α 2 αi-1 Ci = αi-1 Cin CL = αn. Cin αn-1 Vout CL Ref. : J. Segura and C. F. Hawkins, CMOS Electronics, How It Works, How It Fails, Piscataway, New Jersey: IEEE Press, 2004. 9/13/05 ELEC 5970 -001/6970 -001 Lecture 6 12

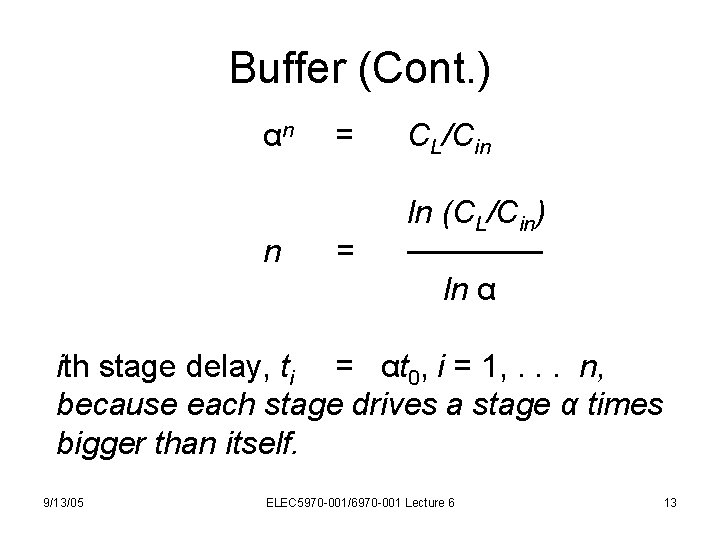

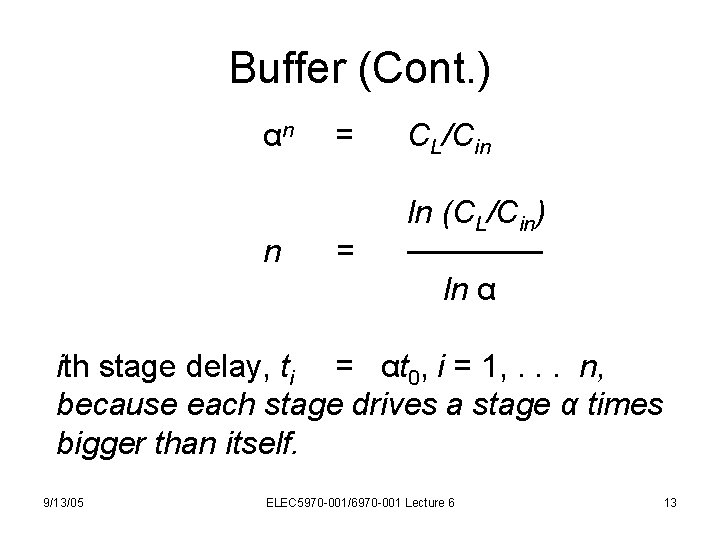

Buffer (Cont. ) αn n = CL/Cin = ln (CL/Cin) ────── ln α ith stage delay, ti = αt 0, i = 1, . . . n, because each stage drives a stage α times bigger than itself. 9/13/05 ELEC 5970 -001/6970 -001 Lecture 6 13

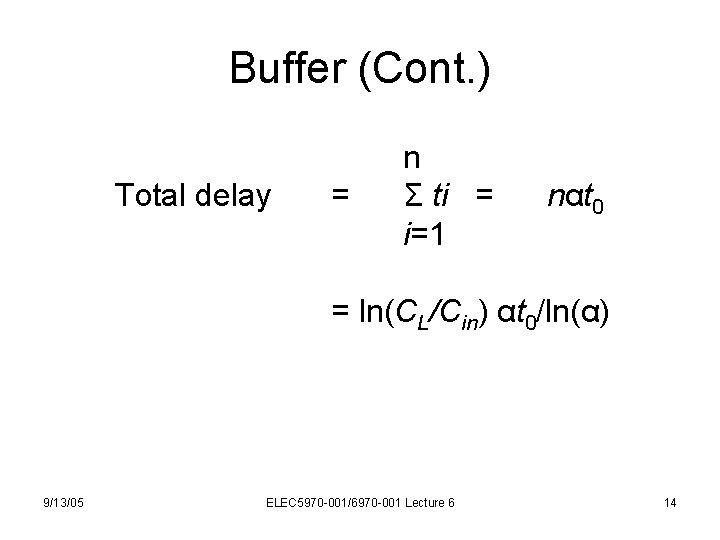

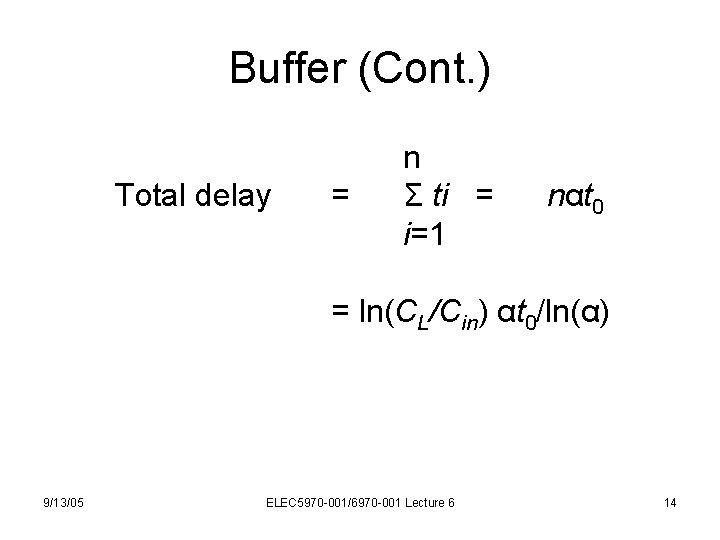

Buffer (Cont. ) Total delay = n Σ ti = i=1 nαt 0 = ln(CL/Cin) αt 0/ln(α) 9/13/05 ELEC 5970 -001/6970 -001 Lecture 6 14

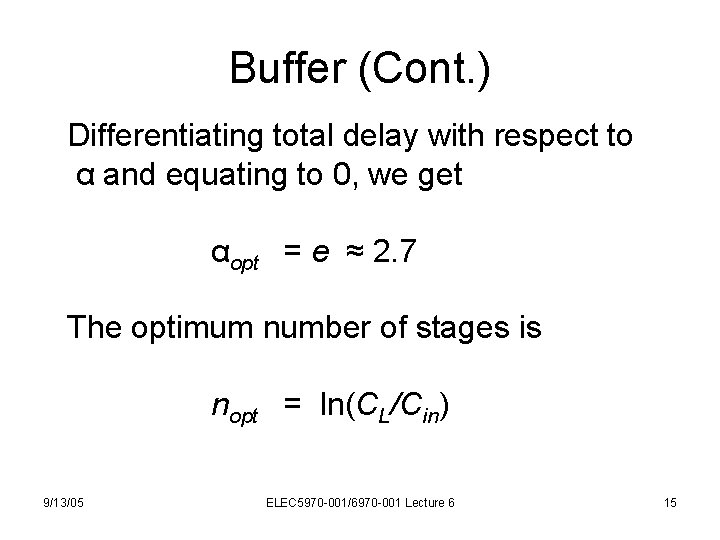

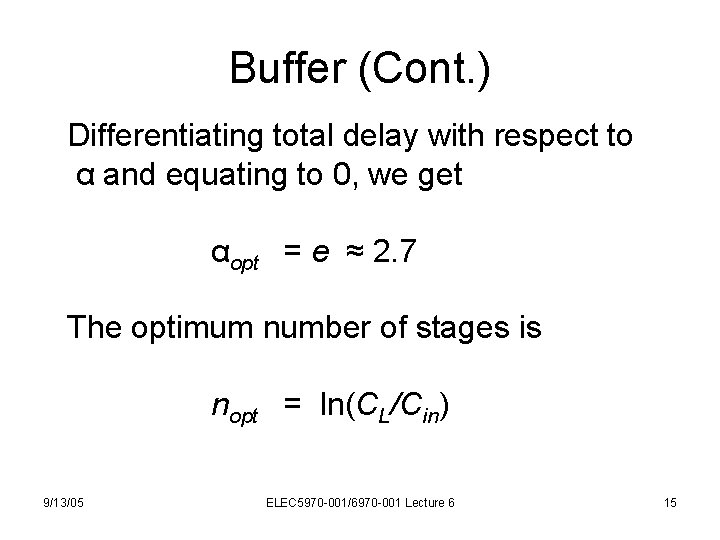

Buffer (Cont. ) Differentiating total delay with respect to α and equating to 0, we get αopt = e ≈ 2. 7 The optimum number of stages is nopt = ln(CL/Cin) 9/13/05 ELEC 5970 -001/6970 -001 Lecture 6 15

Further Reading B. S. Cherkauer and E. G. Friedman, “A Unified Design Methodology for CMOS Tapered Buffers, ” IEEE Trans. VLSI Systems, vol. 3, no. 1, pp. 99 -111, March 1995. 9/13/05 ELEC 5970 -001/6970 -001 Lecture 6 16