ELEC 5970 0016970 001Fall 2005 Special Topics in

![Threshold Voltage • Vt = Vt 0 + γ[(Φs+Vsb)½- Φs½] • Vt 0 is Threshold Voltage • Vt = Vt 0 + γ[(Φs+Vsb)½- Φs½] • Vt 0 is](https://slidetodoc.com/presentation_image/46aecabf3c021b565dd198c0ce3eb68f/image-5.jpg)

- Slides: 25

ELEC 5970 -001/6970 -001(Fall 2005) Special Topics in Electrical Engineering Low-Power Design of Electronic Circuits Dual-Threshold Low-Power Devices Vishwani D. Agrawal James J. Danaher Professor Department of Electrical and Computer Engineering Auburn University http: //www. eng. auburn. edu/~vagrawal@eng. auburn. edu 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 1

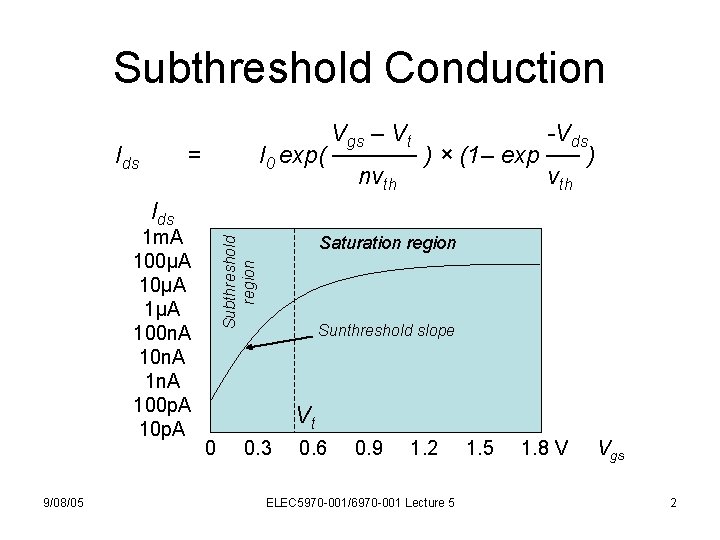

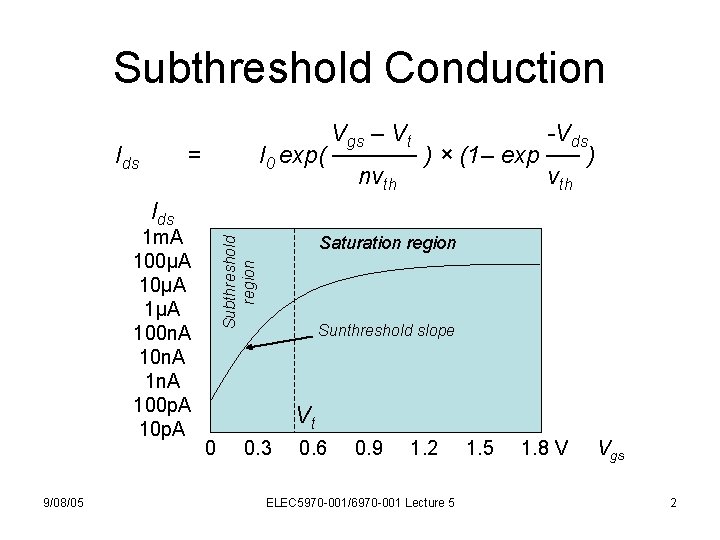

Subthreshold Conduction Ids Vgs – Vt -Vds I 0 exp( ───── ) × (1– exp ── ) nvth = Ids 9/08/05 Saturation region Subthreshold region 1 m. A 100μA 1μA 100 n. A 1 n. A 100 p. A 10 p. A Sunthreshold slope Vt 0 0. 3 0. 6 0. 9 1. 2 ELEC 5970 -001/6970 -001 Lecture 5 1. 8 V Vgs 2

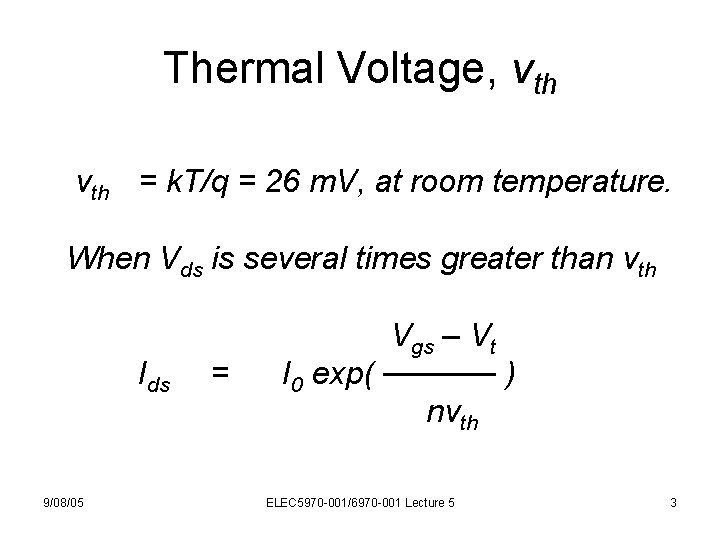

Thermal Voltage, vth = k. T/q = 26 m. V, at room temperature. When Vds is several times greater than vth Ids 9/08/05 = Vgs – Vt I 0 exp( ───── ) nvth ELEC 5970 -001/6970 -001 Lecture 5 3

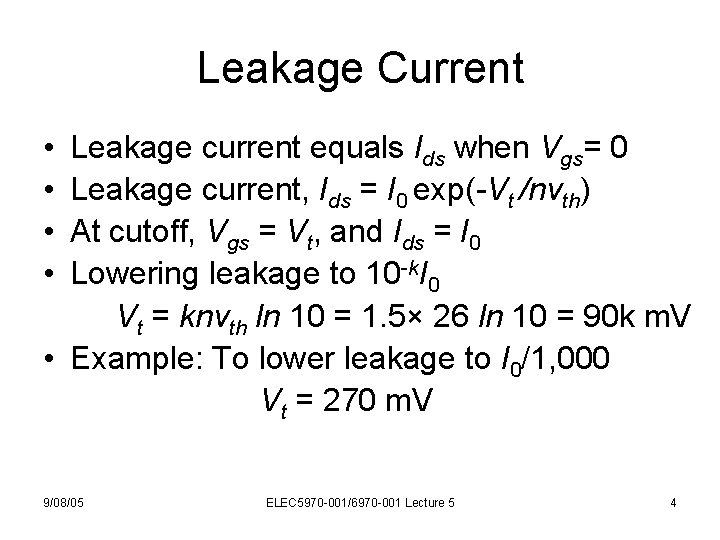

Leakage Current • • Leakage current equals Ids when Vgs= 0 Leakage current, Ids = I 0 exp(-Vt /nvth) At cutoff, Vgs = Vt, and Ids = I 0 Lowering leakage to 10 -k. I 0 Vt = knvth ln 10 = 1. 5× 26 ln 10 = 90 k m. V • Example: To lower leakage to I 0/1, 000 Vt = 270 m. V 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 4

![Threshold Voltage Vt Vt 0 γΦsVsb½ Φs½ Vt 0 is Threshold Voltage • Vt = Vt 0 + γ[(Φs+Vsb)½- Φs½] • Vt 0 is](https://slidetodoc.com/presentation_image/46aecabf3c021b565dd198c0ce3eb68f/image-5.jpg)

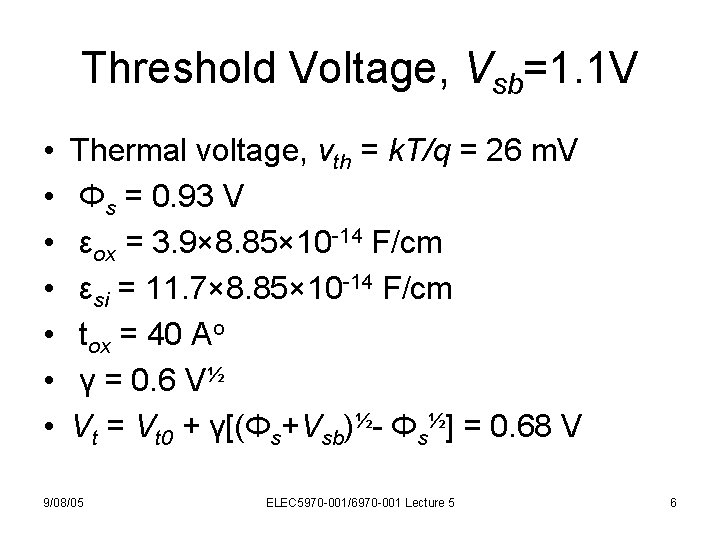

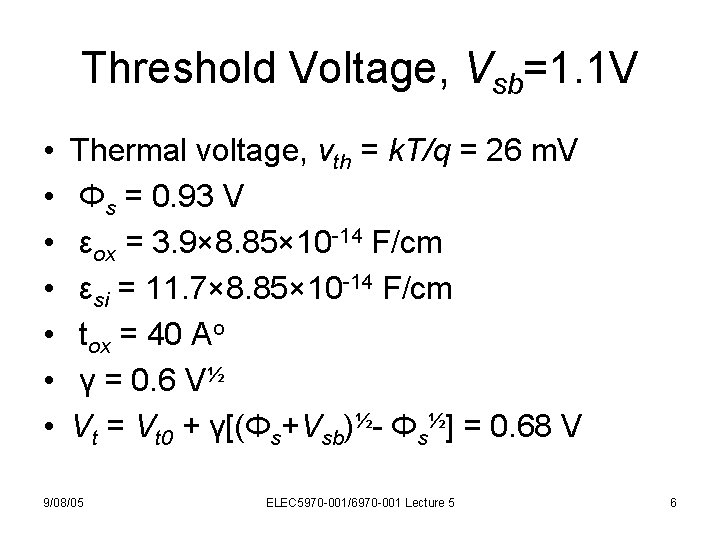

Threshold Voltage • Vt = Vt 0 + γ[(Φs+Vsb)½- Φs½] • Vt 0 is threshold voltage when source is at body potential (0. 4 V for 180 nm process) • Φs = 2 vth ln(NA/ni) is surface potential • γ = (2 qεsi. NA)½tox/εox is body effect coefficient (0. 4 to 1. 0) • NA is doping level = 8× 1017 cm-3 • ni = 1. 45× 1010 cm-3 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 5

Threshold Voltage, Vsb=1. 1 V • • Thermal voltage, vth = k. T/q = 26 m. V Φs = 0. 93 V εox = 3. 9× 8. 85× 10 -14 F/cm εsi = 11. 7× 8. 85× 10 -14 F/cm tox = 40 Ao γ = 0. 6 V½ Vt = Vt 0 + γ[(Φs+Vsb)½- Φs½] = 0. 68 V 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 6

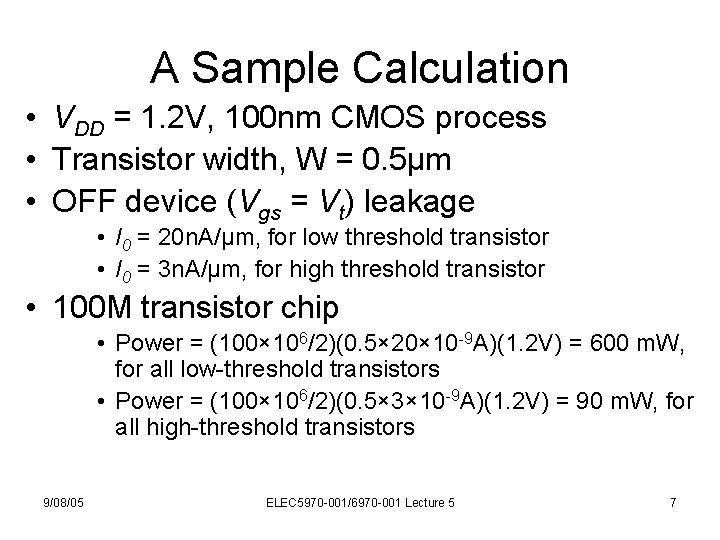

A Sample Calculation • VDD = 1. 2 V, 100 nm CMOS process • Transistor width, W = 0. 5μm • OFF device (Vgs = Vt) leakage • I 0 = 20 n. A/μm, for low threshold transistor • I 0 = 3 n. A/μm, for high threshold transistor • 100 M transistor chip • Power = (100× 106/2)(0. 5× 20× 10 -9 A)(1. 2 V) = 600 m. W, for all low-threshold transistors • Power = (100× 106/2)(0. 5× 3× 10 -9 A)(1. 2 V) = 90 m. W, for all high-threshold transistors 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 7

Dual-Threshold Chip • Low-threshold only for 20% transistors on critical path. • Leakage power = 600× 0. 2 + 90× 0. 8 = 120 + 72 = 192 m. W 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 8

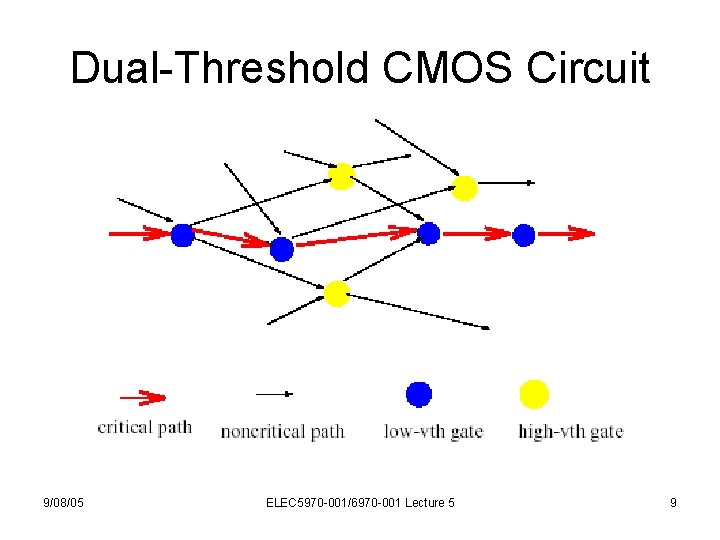

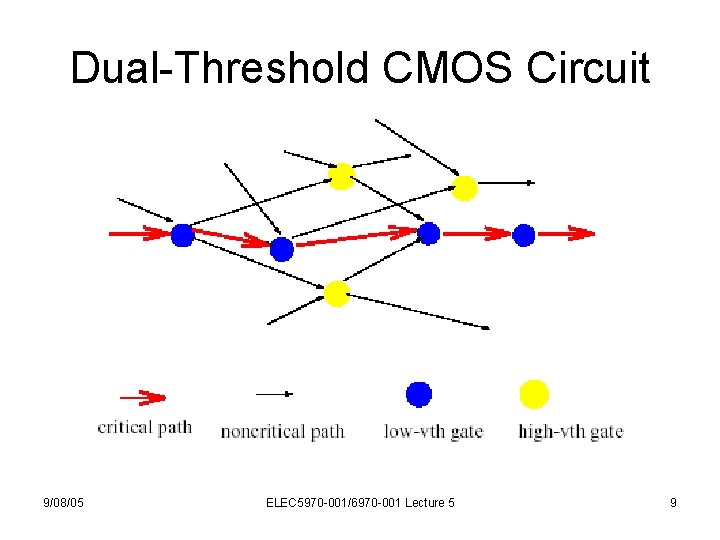

Dual-Threshold CMOS Circuit 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 9

Dual-Threshold Design • To maintain performance, all gates on the critical path are assigned low Vt. • Most of the other gates are assigned high Vt. But, • Some gates on non-critical paths may also be assigned low Vt to prevent those paths from becoming critical. 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 10

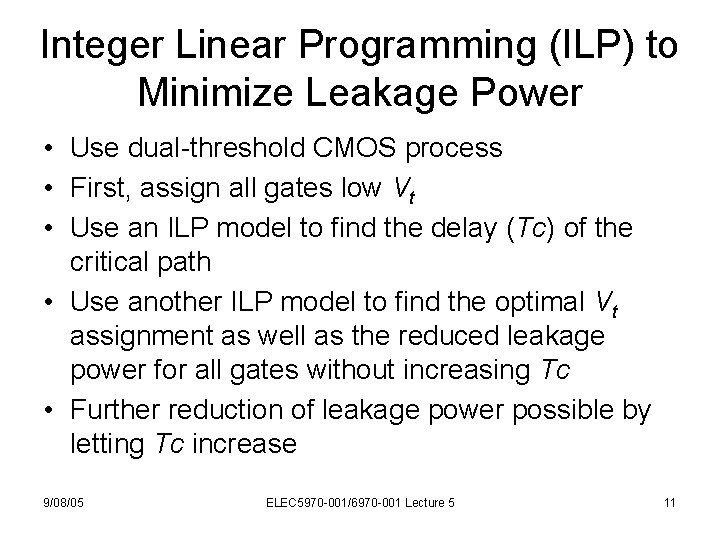

Integer Linear Programming (ILP) to Minimize Leakage Power • Use dual-threshold CMOS process • First, assign all gates low Vt • Use an ILP model to find the delay (Tc) of the critical path • Use another ILP model to find the optimal Vt assignment as well as the reduced leakage power for all gates without increasing Tc • Further reduction of leakage power possible by letting Tc increase 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 11

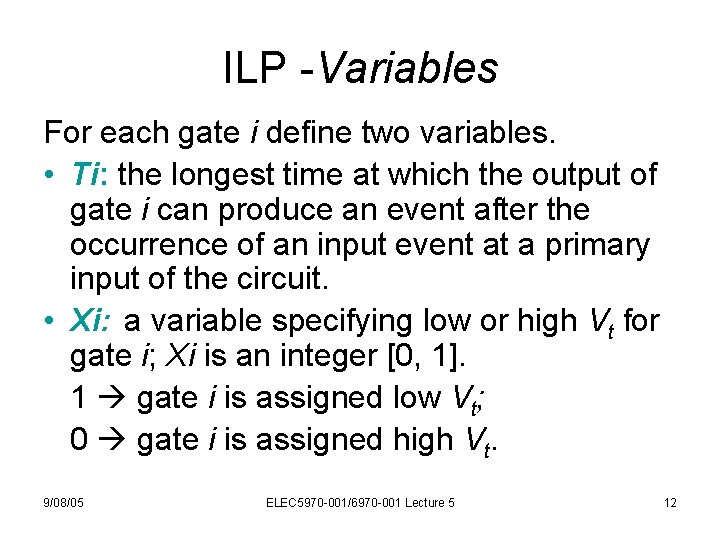

ILP -Variables For each gate i define two variables. • Ti: the longest time at which the output of gate i can produce an event after the occurrence of an input event at a primary input of the circuit. • Xi: a variable specifying low or high Vt for gate i; Xi is an integer [0, 1]. 1 gate i is assigned low Vt; 0 gate i is assigned high Vt. 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 12

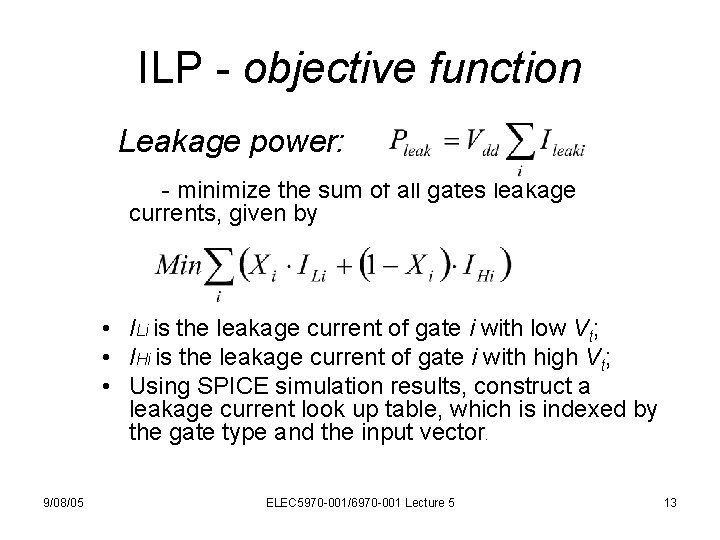

ILP - objective function Leakage power: - minimize the sum of all gates leakage currents, given by • ILi is the leakage current of gate i with low Vt; • IHi is the leakage current of gate i with high Vt; • Using SPICE simulation results, construct a leakage current look up table, which is indexed by the gate type and the input vector. 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 13

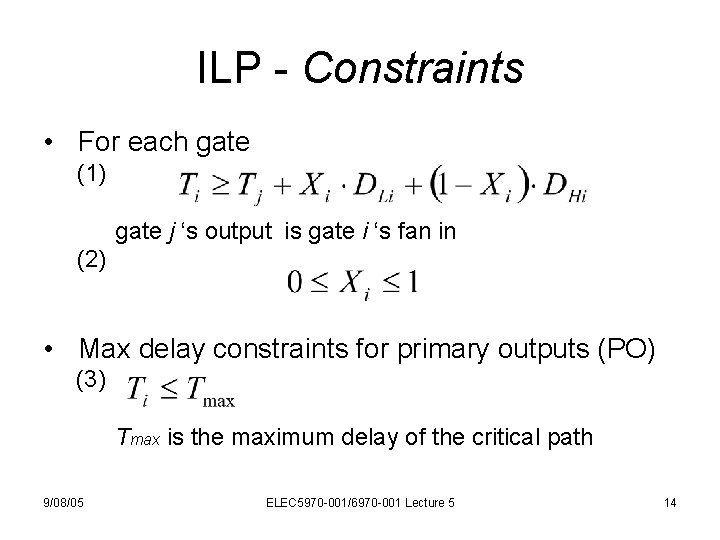

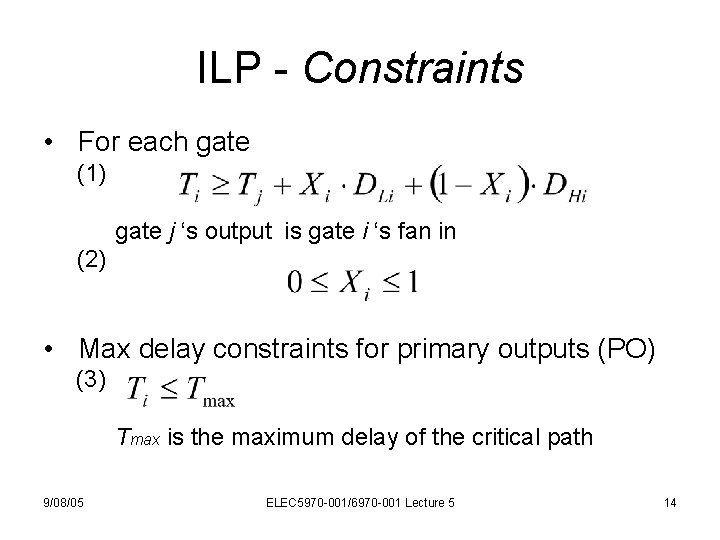

ILP - Constraints • For each gate (1) gate j ‘s output is gate i ‘s fan in (2) • Max delay constraints for primary outputs (PO) (3) Tmax is the maximum delay of the critical path 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 14

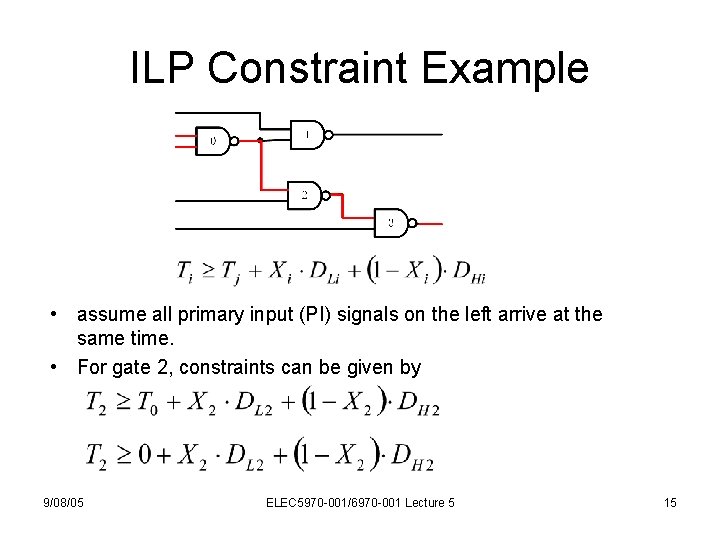

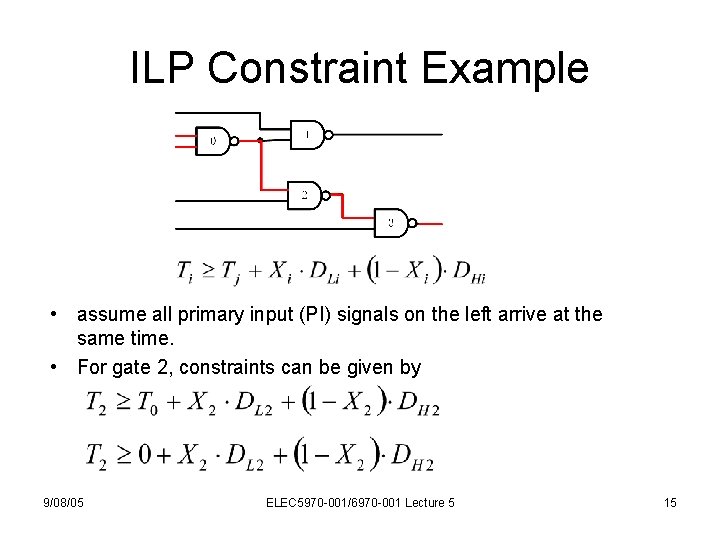

ILP Constraint Example • assume all primary input (PI) signals on the left arrive at the same time. • For gate 2, constraints can be given by 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 15

ILP – Constraints (cont. ) • DHi is the delay of gate i with high Vt • DLi is the delay of gate i with low Vt • A second look-up table is constructed and specifies the delay for given gate type and fanout number. 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 16

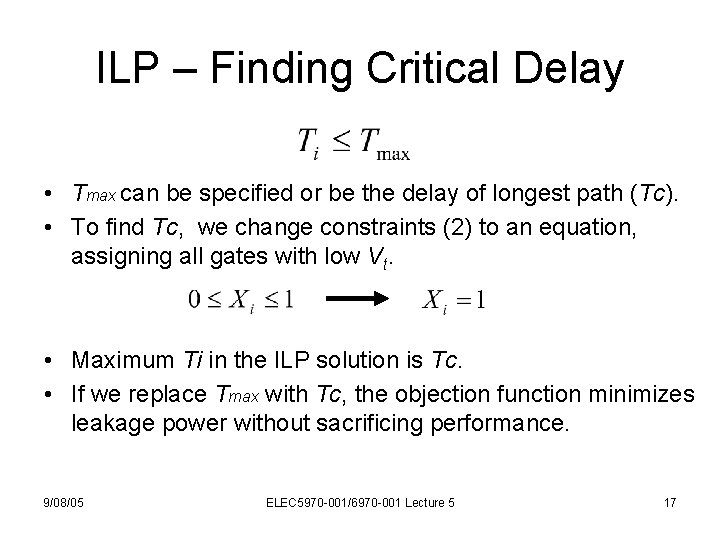

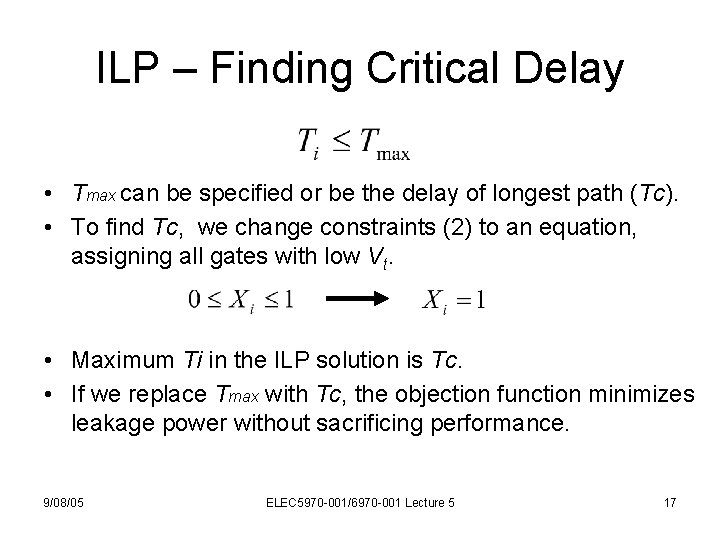

ILP – Finding Critical Delay • Tmax can be specified or be the delay of longest path (Tc). • To find Tc, we change constraints (2) to an equation, assigning all gates with low Vt. • Maximum Ti in the ILP solution is Tc. • If we replace Tmax with Tc, the objection function minimizes leakage power without sacrificing performance. 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 17

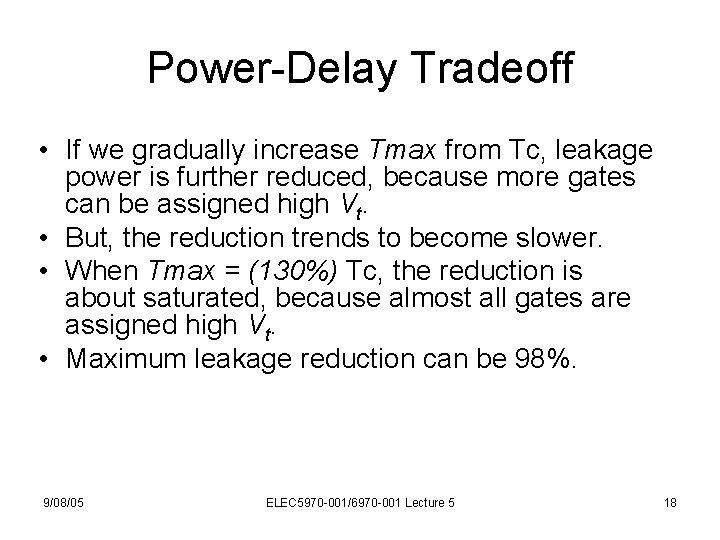

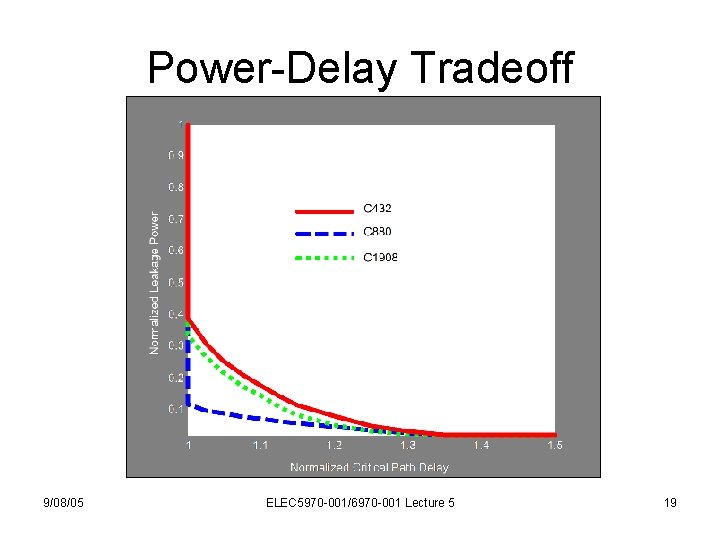

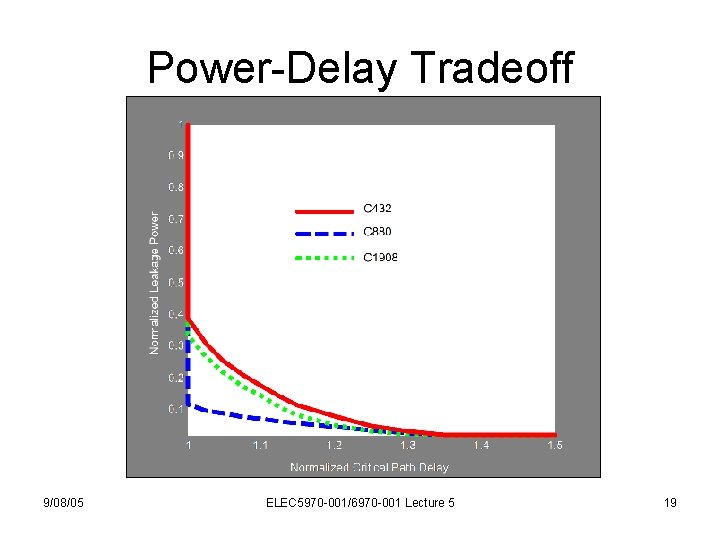

Power-Delay Tradeoff • If we gradually increase Tmax from Tc, leakage power is further reduced, because more gates can be assigned high Vt. • But, the reduction trends to become slower. • When Tmax = (130%) Tc, the reduction is about saturated, because almost all gates are assigned high Vt. • Maximum leakage reduction can be 98%. 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 18

Power-Delay Tradeoff 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 19

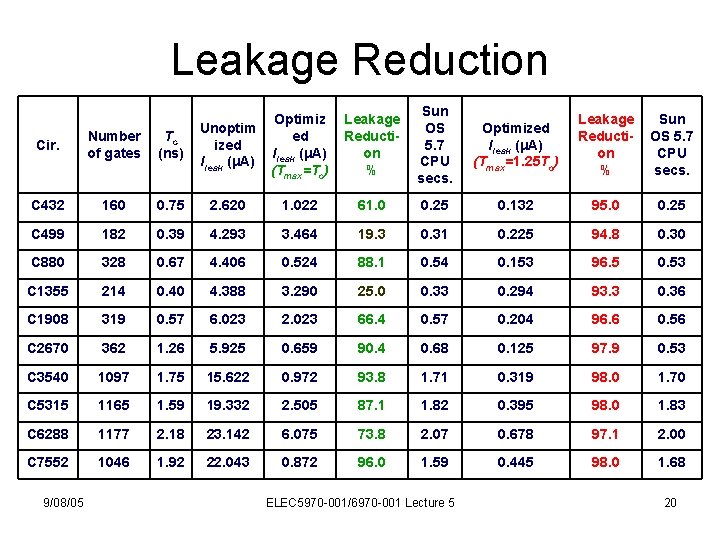

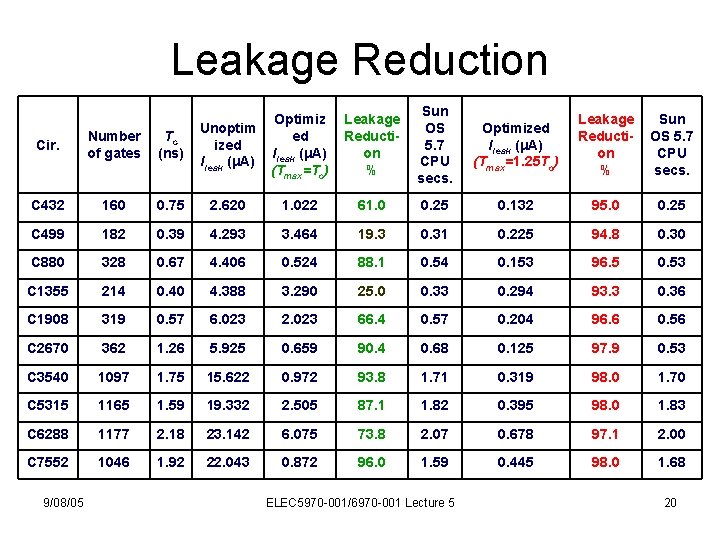

Leakage Reduction Optimiz ed Ileak (μA) (Tmax=Tc) Leakage Reduction % Sun OS 5. 7 CPU secs. Optimized Ileak (μA) (Tmax=1. 25 Tc) Leakage Reduction % Sun OS 5. 7 CPU secs. Cir. Number of gates Tc (ns) Unoptim ized Ileak (μA) C 432 160 0. 75 2. 620 1. 022 61. 0 0. 25 0. 132 95. 0 0. 25 C 499 182 0. 39 4. 293 3. 464 19. 3 0. 31 0. 225 94. 8 0. 30 C 880 328 0. 67 4. 406 0. 524 88. 1 0. 54 0. 153 96. 5 0. 53 C 1355 214 0. 40 4. 388 3. 290 25. 0 0. 33 0. 294 93. 3 0. 36 C 1908 319 0. 57 6. 023 2. 023 66. 4 0. 57 0. 204 96. 6 0. 56 C 2670 362 1. 26 5. 925 0. 659 90. 4 0. 68 0. 125 97. 9 0. 53 C 3540 1097 1. 75 15. 622 0. 972 93. 8 1. 71 0. 319 98. 0 1. 70 C 5315 1165 1. 59 19. 332 2. 505 87. 1 1. 82 0. 395 98. 0 1. 83 C 6288 1177 2. 18 23. 142 6. 075 73. 8 2. 07 0. 678 97. 1 2. 00 C 7552 1046 1. 92 22. 043 0. 872 96. 0 1. 59 0. 445 98. 0 1. 68 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 20

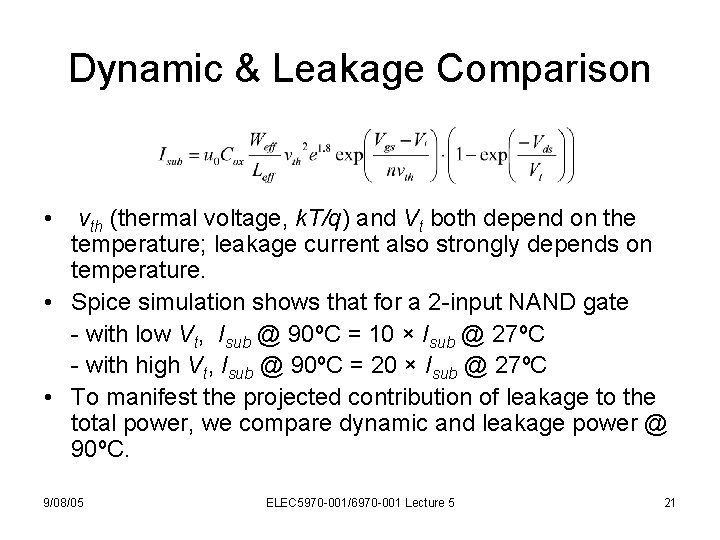

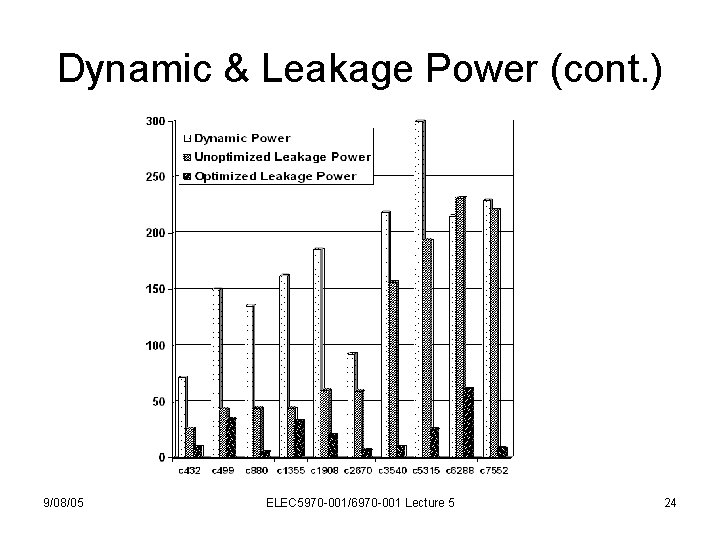

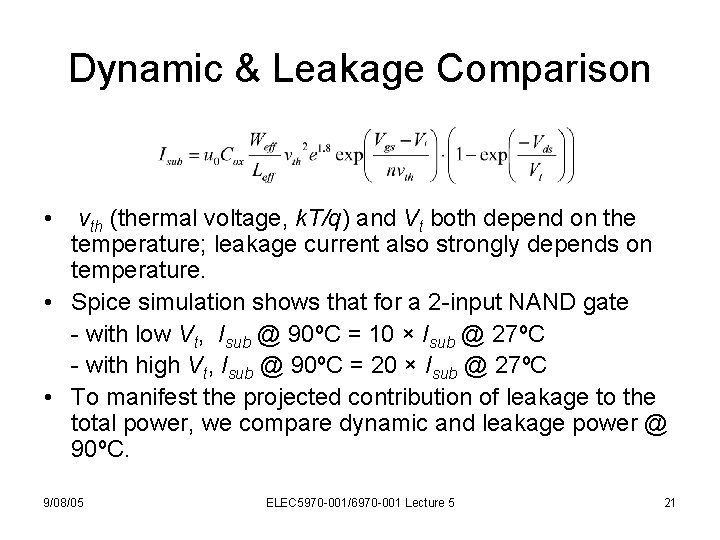

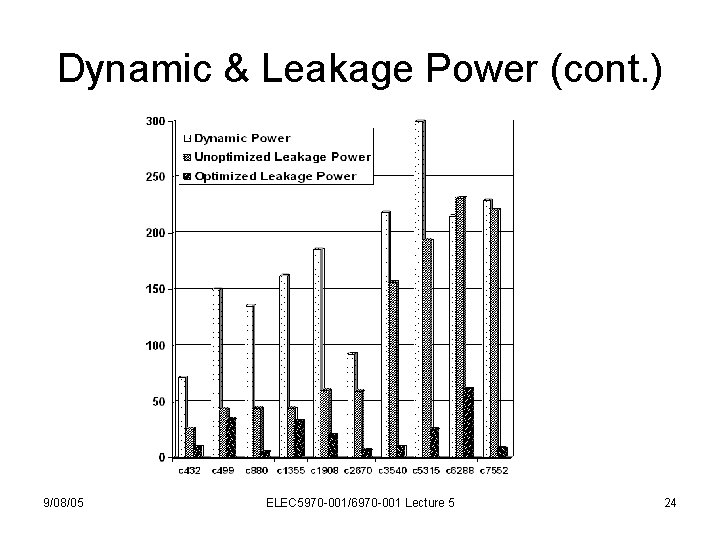

Dynamic & Leakage Comparison • vth (thermal voltage, k. T/q) and Vt both depend on the temperature; leakage current also strongly depends on temperature. • Spice simulation shows that for a 2 -input NAND gate - with low Vt, Isub @ 90ºC = 10 × Isub @ 27ºC - with high Vt, Isub @ 90ºC = 20 × Isub @ 27ºC • To manifest the projected contribution of leakage to the total power, we compare dynamic and leakage power @ 90ºC. 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 21

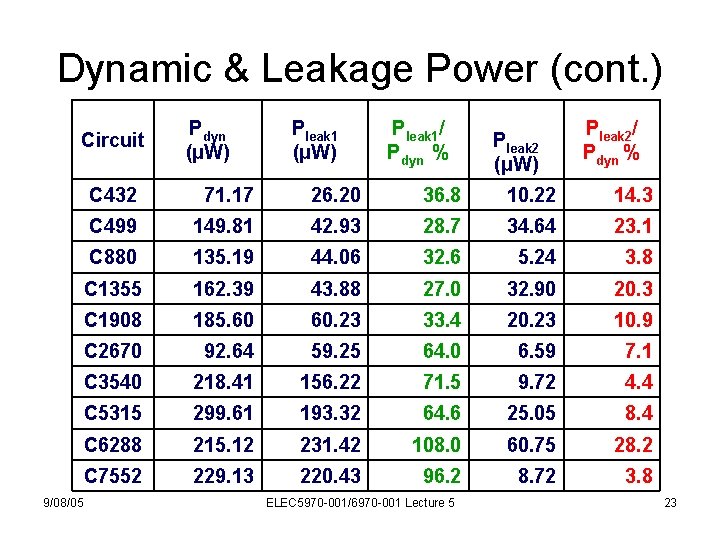

Results-Dynamic & Leakage Comparison (cont. ) • Without considering glitches, the dynamic power is estimated by an event driven simulator, and is given by • We apply 1000 random test vectors at PIs with a vector period of 120% Tc, and calculate the total number of weighted (by node capacitance) transitions in the circuit. 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 22

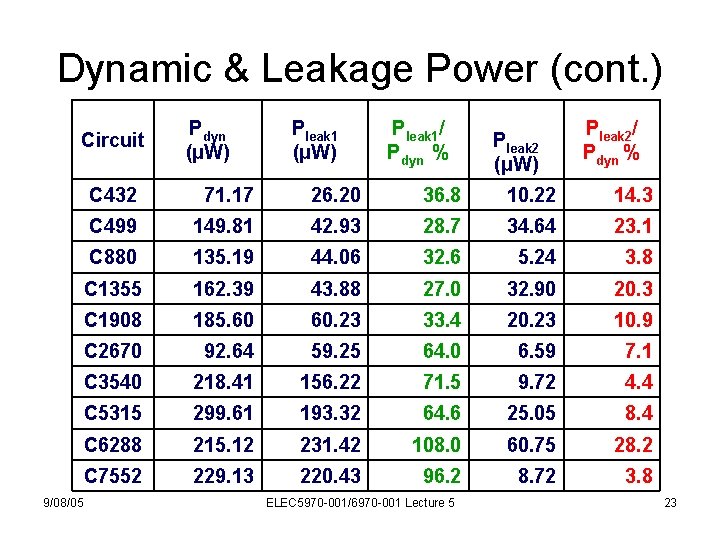

Dynamic & Leakage Power (cont. ) Circuit 9/08/05 Pdyn (μW) Pleak 1/ Pdyn % Pleak 2 (μW) Pleak 2/ Pdyn % C 432 71. 17 26. 20 36. 8 10. 22 14. 3 C 499 149. 81 42. 93 28. 7 34. 64 23. 1 C 880 135. 19 44. 06 32. 6 5. 24 3. 8 C 1355 162. 39 43. 88 27. 0 32. 90 20. 3 C 1908 185. 60 60. 23 33. 4 20. 23 10. 9 C 2670 92. 64 59. 25 64. 0 6. 59 7. 1 C 3540 218. 41 156. 22 71. 5 9. 72 4. 4 C 5315 299. 61 193. 32 64. 6 25. 05 8. 4 C 6288 215. 12 231. 42 108. 0 60. 75 28. 2 C 7552 229. 13 220. 43 96. 2 8. 72 3. 8 ELEC 5970 -001/6970 -001 Lecture 5 23

Dynamic & Leakage Power (cont. ) 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 24

Leakage and Dynamic Glitch Power Minimization Using Integer Linear Programming for Vt Assignment and Path Balancing Yuanlin Lu VLSI Design and Test Seminar Broun 235 September 14, 2005, 3: 00 PM 9/08/05 ELEC 5970 -001/6970 -001 Lecture 5 25