ELEC 5970 0016970 001Fall 2005 Special Topics in

- Slides: 18

ELEC 5970 -001/6970 -001(Fall 2005) Special Topics in Electrical Engineering Low-Power Design of Electronic Circuits Power Analysis: Logic Level Vishwani D. Agrawal James J. Danaher Professor Department of Electrical and Computer Engineering Auburn University http: //www. eng. auburn. edu/~vagrawal@eng. auburn. edu 9/29/05 ELEC 5970 -001/6970 -001 Lecture 10 1

Power Analysis • Motivation: – Specification – Optimization – Reliability • Applications – Design analysis and optimization – Physical design – Packaging – Test 9/29/05 ELEC 5970 -001/6970 -001 Lecture 10 2

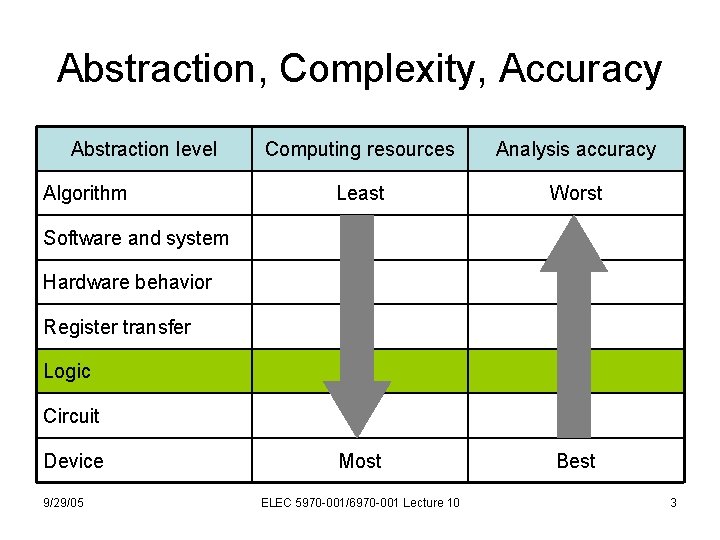

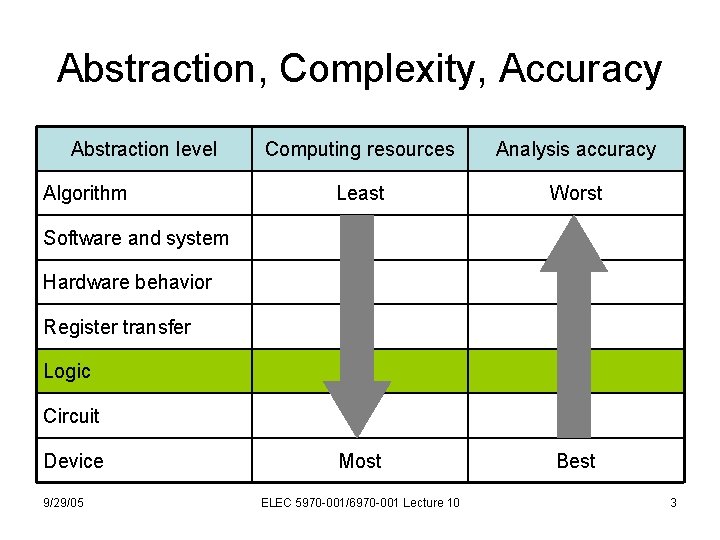

Abstraction, Complexity, Accuracy Abstraction level Algorithm Computing resources Analysis accuracy Least Worst Most Best Software and system Hardware behavior Register transfer Logic Circuit Device 9/29/05 ELEC 5970 -001/6970 -001 Lecture 10 3

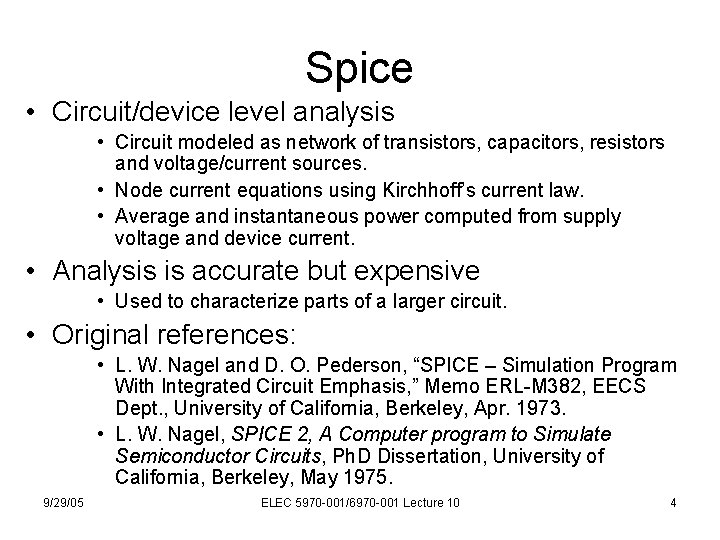

Spice • Circuit/device level analysis • Circuit modeled as network of transistors, capacitors, resistors and voltage/current sources. • Node current equations using Kirchhoff’s current law. • Average and instantaneous power computed from supply voltage and device current. • Analysis is accurate but expensive • Used to characterize parts of a larger circuit. • Original references: • L. W. Nagel and D. O. Pederson, “SPICE – Simulation Program With Integrated Circuit Emphasis, ” Memo ERL-M 382, EECS Dept. , University of California, Berkeley, Apr. 1973. • L. W. Nagel, SPICE 2, A Computer program to Simulate Semiconductor Circuits, Ph. D Dissertation, University of California, Berkeley, May 1975. 9/29/05 ELEC 5970 -001/6970 -001 Lecture 10 4

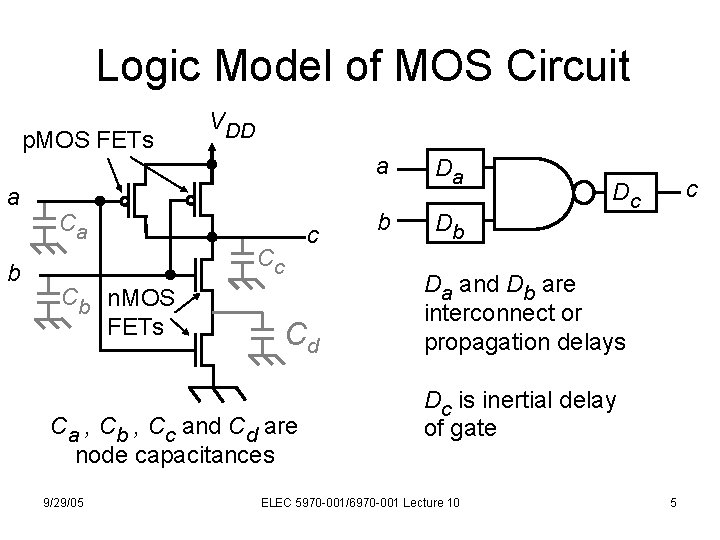

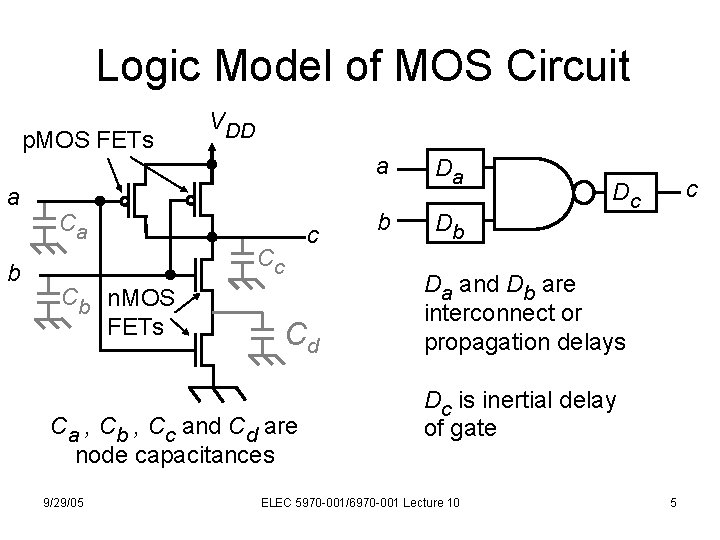

Logic Model of MOS Circuit p. MOS FETs a b VDD Ca Cc Cb n. MOS FETs Cd Ca , Cb , Cc and Cd are node capacitances 9/29/05 c a Da b Db c Dc Da and Db are interconnect or propagation delays Dc is inertial delay of gate ELEC 5970 -001/6970 -001 Lecture 10 5

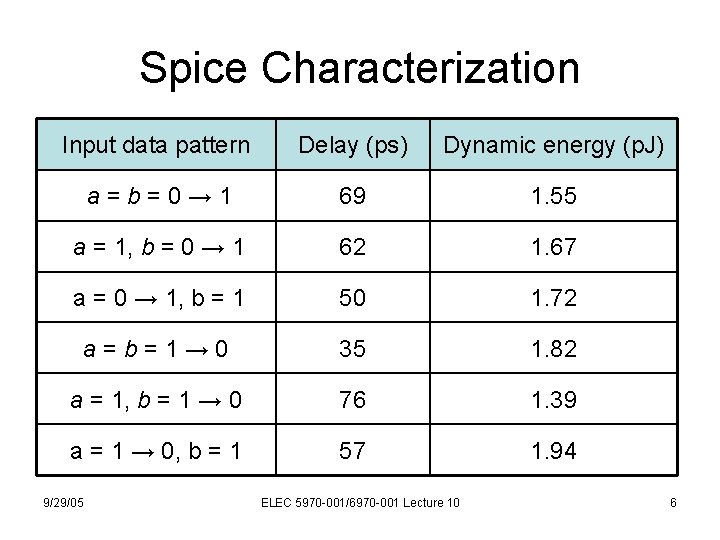

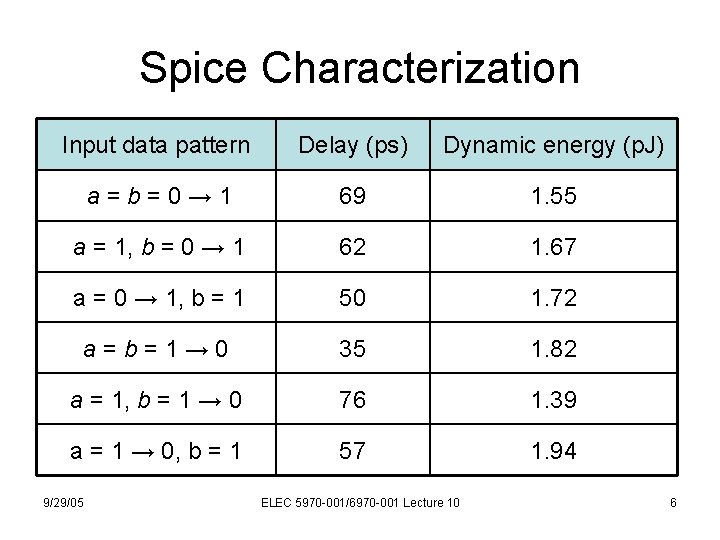

Spice Characterization Input data pattern Delay (ps) Dynamic energy (p. J) a=b=0→ 1 69 1. 55 a = 1, b = 0 → 1 62 1. 67 a = 0 → 1, b = 1 50 1. 72 a=b=1→ 0 35 1. 82 a = 1, b = 1 → 0 76 1. 39 a = 1 → 0, b = 1 57 1. 94 9/29/05 ELEC 5970 -001/6970 -001 Lecture 10 6

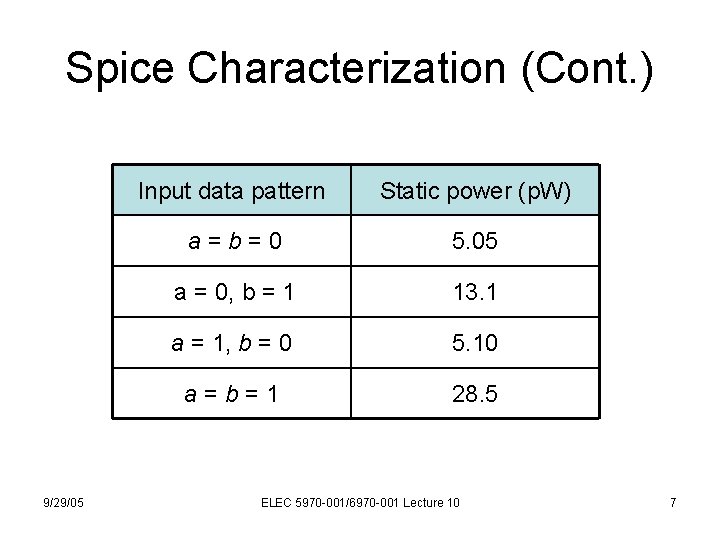

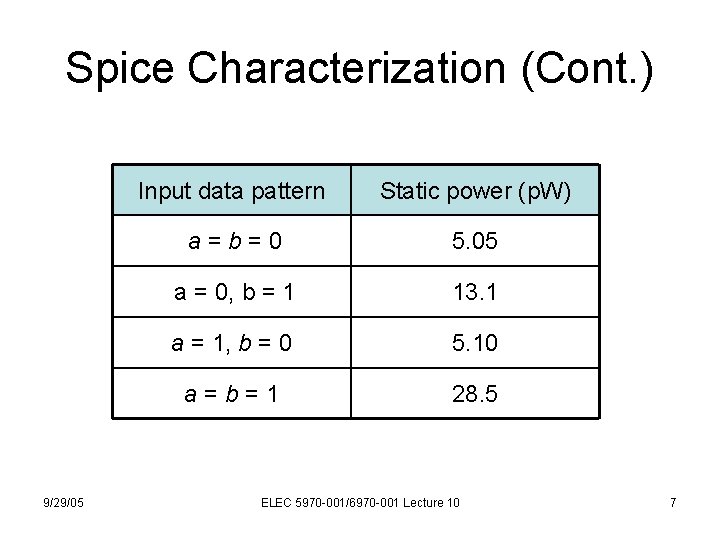

Spice Characterization (Cont. ) 9/29/05 Input data pattern Static power (p. W) a=b=0 5. 05 a = 0, b = 1 13. 1 a = 1, b = 0 5. 10 a=b=1 28. 5 ELEC 5970 -001/6970 -001 Lecture 10 7

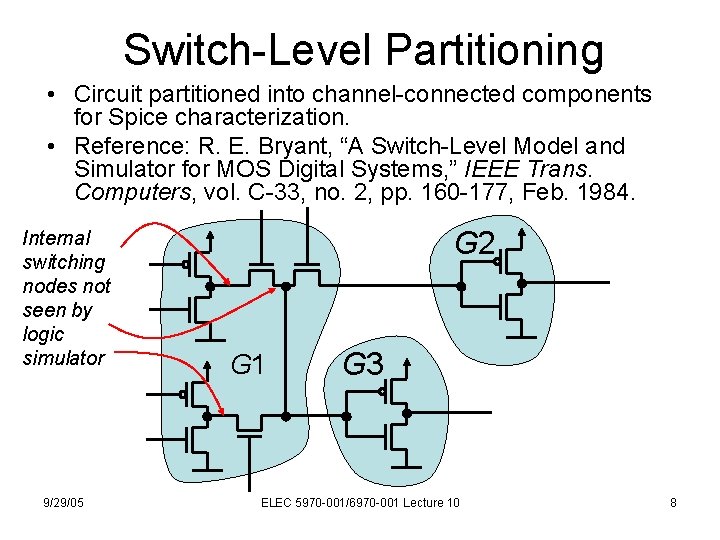

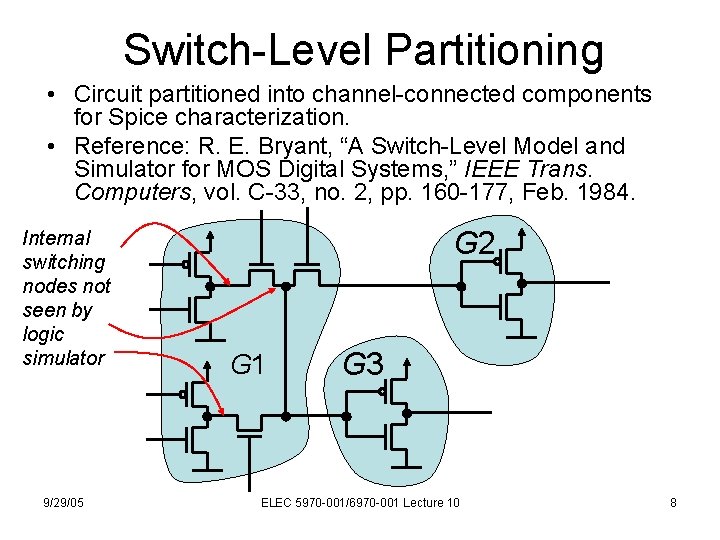

Switch-Level Partitioning • Circuit partitioned into channel-connected components for Spice characterization. • Reference: R. E. Bryant, “A Switch-Level Model and Simulator for MOS Digital Systems, ” IEEE Trans. Computers, vol. C-33, no. 2, pp. 160 -177, Feb. 1984. Internal switching nodes not seen by logic simulator 9/29/05 G 2 G 1 G 3 ELEC 5970 -001/6970 -001 Lecture 10 8

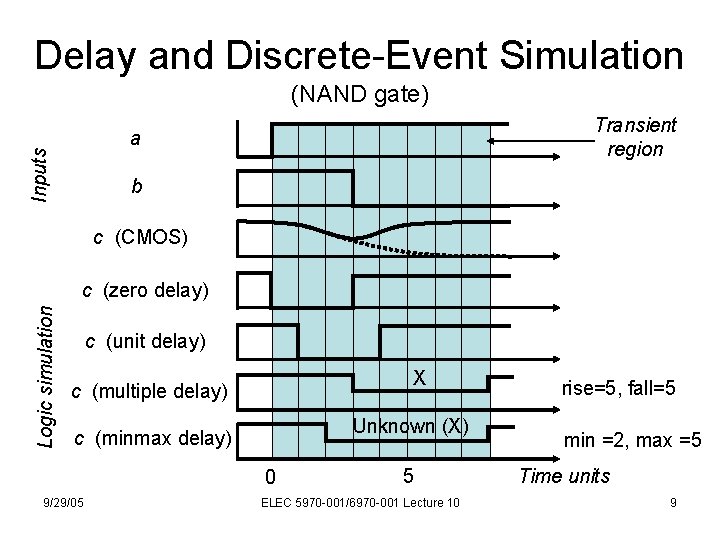

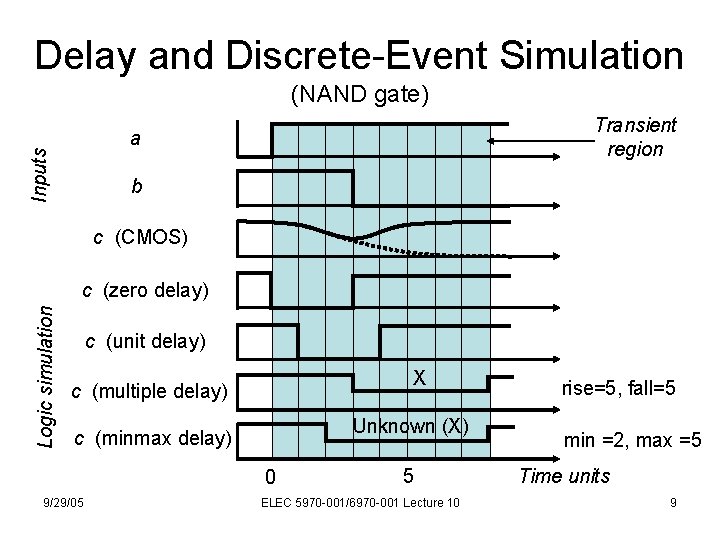

Delay and Discrete-Event Simulation (NAND gate) Transient region Inputs a b c (CMOS) Logic simulation c (zero delay) c (unit delay) X c (multiple delay) Unknown (X) c (minmax delay) 0 9/29/05 5 ELEC 5970 -001/6970 -001 Lecture 10 rise=5, fall=5 min =2, max =5 Time units 9

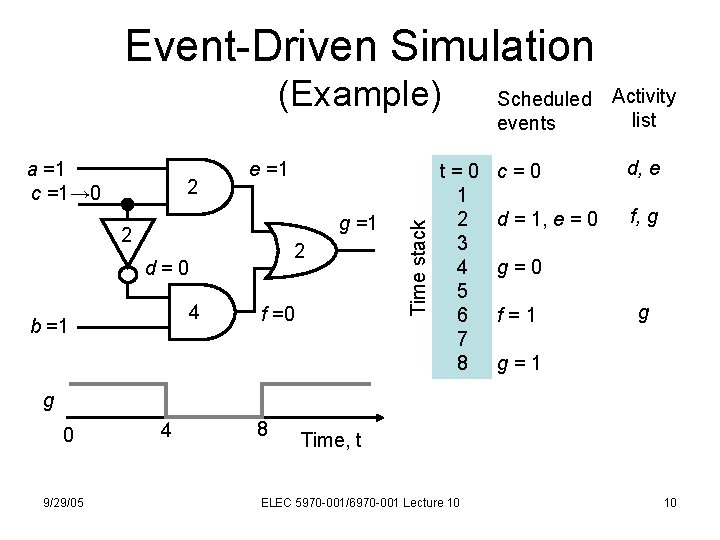

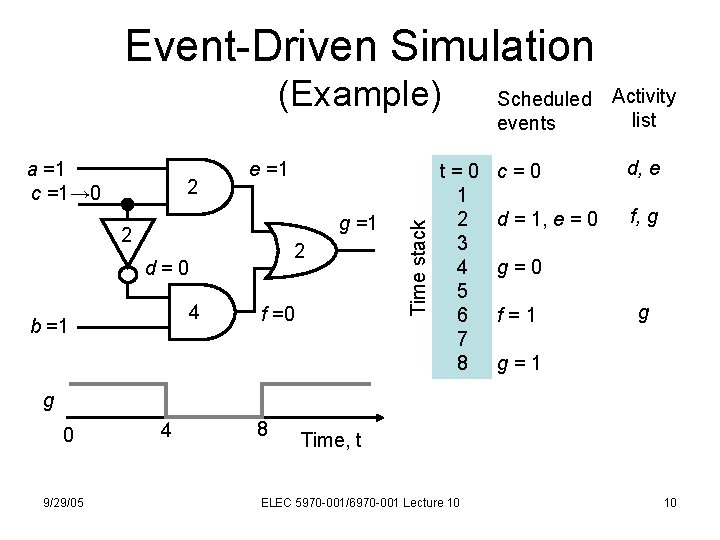

Event-Driven Simulation (Example) 2 e =1 g =1 2 2 d=0 4 b =1 f =0 Time stack a =1 c =1→ 0 t=0 1 2 3 4 5 6 7 8 Scheduled events Activity list c=0 d, e d = 1, e = 0 f, g g=0 f=1 g g=1 g 0 9/29/05 4 8 Time, t ELEC 5970 -001/6970 -001 Lecture 10 10

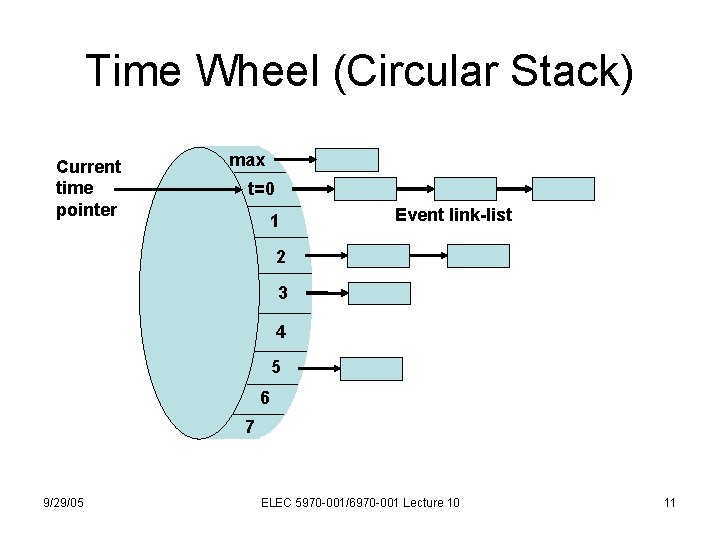

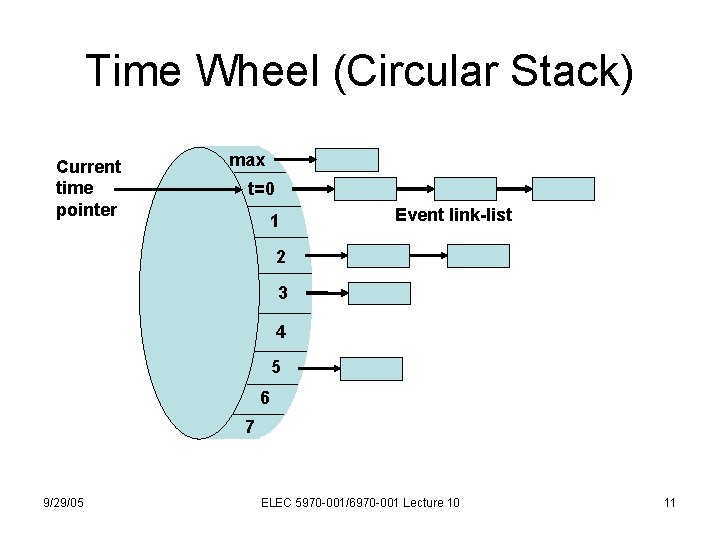

Time Wheel (Circular Stack) Current time pointer max t=0 1 Event link-list 2 3 4 5 6 7 9/29/05 ELEC 5970 -001/6970 -001 Lecture 10 11

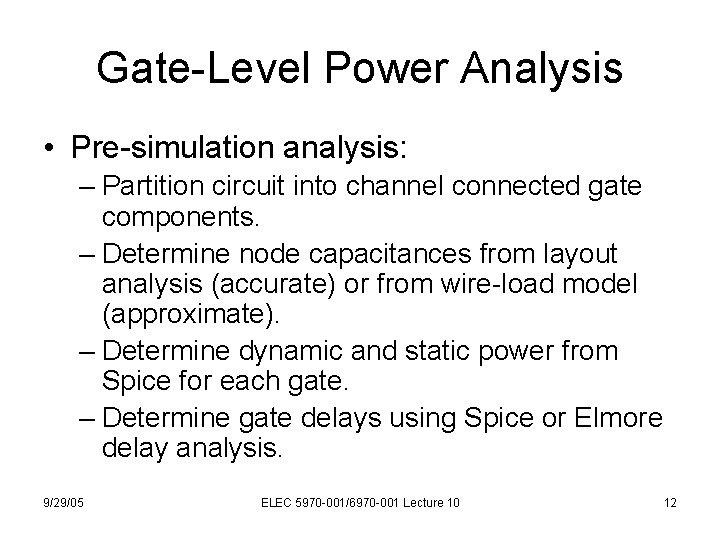

Gate-Level Power Analysis • Pre-simulation analysis: – Partition circuit into channel connected gate components. – Determine node capacitances from layout analysis (accurate) or from wire-load model (approximate). – Determine dynamic and static power from Spice for each gate. – Determine gate delays using Spice or Elmore delay analysis. 9/29/05 ELEC 5970 -001/6970 -001 Lecture 10 12

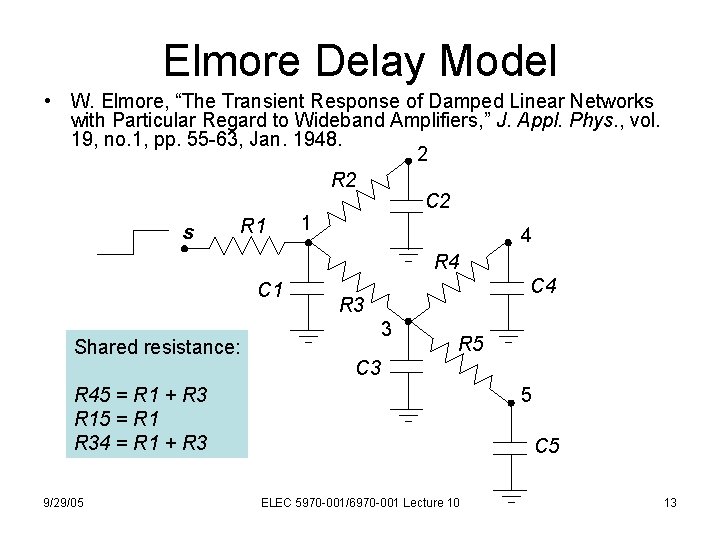

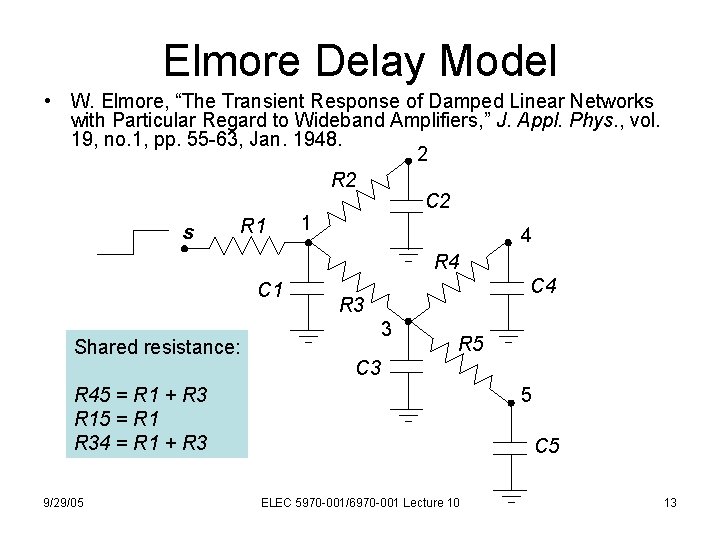

Elmore Delay Model • W. Elmore, “The Transient Response of Damped Linear Networks with Particular Regard to Wideband Amplifiers, ” J. Appl. Phys. , vol. 19, no. 1, pp. 55 -63, Jan. 1948. 2 R 2 C 2 1 R 1 s 4 R 4 C 1 R 3 3 R 5 Shared resistance: C 3 R 45 = R 1 + R 3 5 R 15 = R 1 R 34 = R 1 + R 3 C 5 9/29/05 ELEC 5970 -001/6970 -001 Lecture 10 13

Elmore Delay Formula N Delay at node k = 0. 69 Σ Cj × Rjk j=1 where N = number of capacitive nodes in the network Example: Delay at node 5 = 0. 69[R 1 C 1 + R 1 C 2 + (R 1+R 3)C 3 + (R 1+R 3)C 4 (R 1+R 3+R 5)C 5] 9/29/05 ELEC 5970 -001/6970 -001 Lecture 10 14

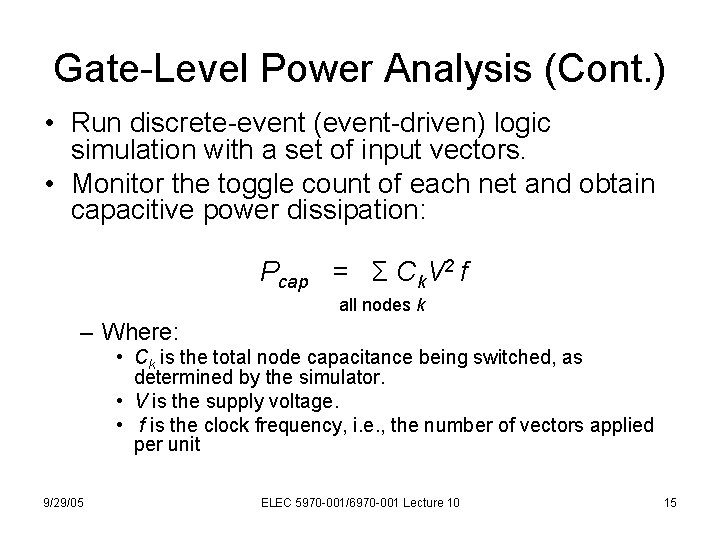

Gate-Level Power Analysis (Cont. ) • Run discrete-event (event-driven) logic simulation with a set of input vectors. • Monitor the toggle count of each net and obtain capacitive power dissipation: Pcap = Σ Ck. V 2 f all nodes k – Where: • Ck is the total node capacitance being switched, as determined by the simulator. • V is the supply voltage. • f is the clock frequency, i. e. , the number of vectors applied per unit 9/29/05 ELEC 5970 -001/6970 -001 Lecture 10 15

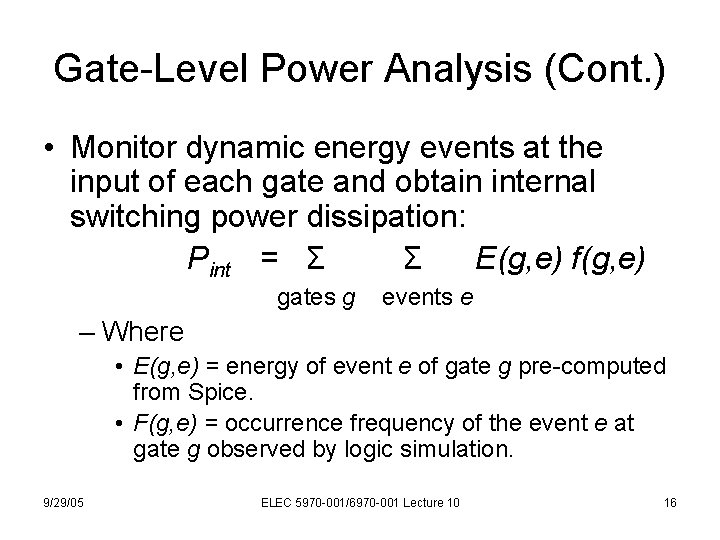

Gate-Level Power Analysis (Cont. ) • Monitor dynamic energy events at the input of each gate and obtain internal switching power dissipation: Pint = Σ Σ E(g, e) f(g, e) gates g events e – Where • E(g, e) = energy of event e of gate g pre-computed from Spice. • F(g, e) = occurrence frequency of the event e at gate g observed by logic simulation. 9/29/05 ELEC 5970 -001/6970 -001 Lecture 10 16

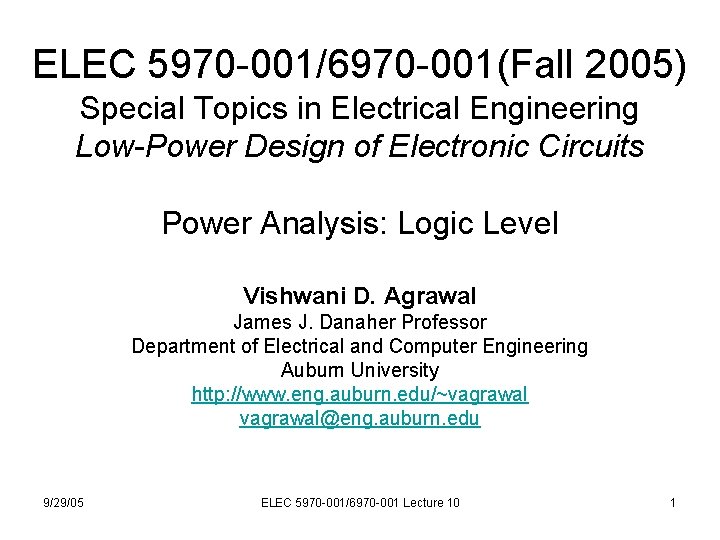

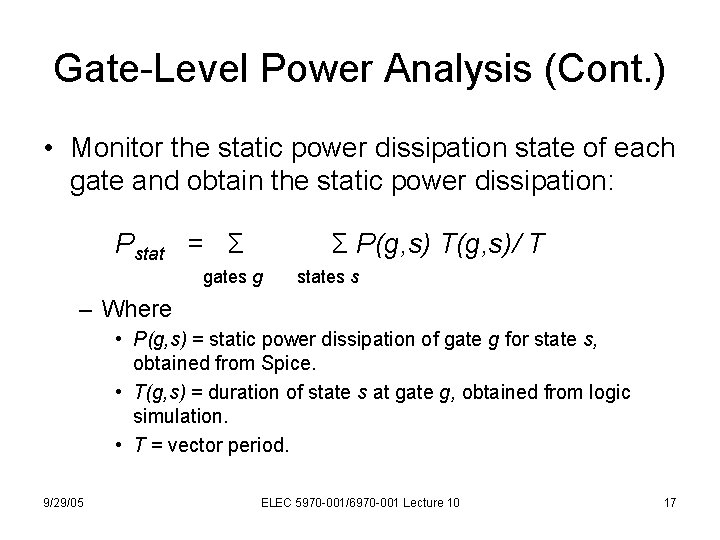

Gate-Level Power Analysis (Cont. ) • Monitor the static power dissipation state of each gate and obtain the static power dissipation: Pstat = Σ Σ P(g, s) T(g, s)/ T gates g states s – Where • P(g, s) = static power dissipation of gate g for state s, obtained from Spice. • T(g, s) = duration of state s at gate g, obtained from logic simulation. • T = vector period. 9/29/05 ELEC 5970 -001/6970 -001 Lecture 10 17

Gate-Level Power Analysis (Cont. ) • Sum up all three components of power: P = Pstat + Pint + Pstat • References: • A. Deng, “Power Analysis for CMOS/Bi. CMOS Circuits, ” Proc. International Workshop Low Power Design, 1994. • J. Benkoski, A. C. Deng, C. X. Huang, S. Napper and J. Tuan, “Simulation Algorithms, Power Estimation and Diagnostics in Power. Mill, ” Proc. PATMOS, 1995. • C. X. Huang, B. Zhang, A. C. Deng and B. Swirski, “The Design and Implementation of Power. Mill, ” Proc. International Symp. Low Power Design, 1995, pp. 105 -109. 9/29/05 ELEC 5970 -001/6970 -001 Lecture 10 18