ELEC 5270 0016270 001 Spring 09 Low Power

- Slides: 70

ELEC 5270 -001/6270 -001 Spring 09 Low Power Design of Electronic Circuits VLSI Synthesis and Simulation Tools Nitin Yogi 01/09/2009 Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 1

X-Win 32 o X-Win 32 is used to log into UNIX session o Use Windows Auburn login and password to log into X-Win 32 session. Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 2

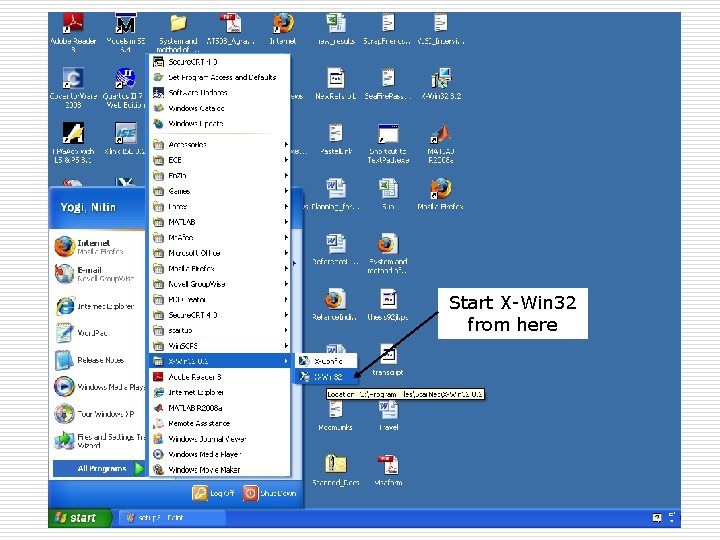

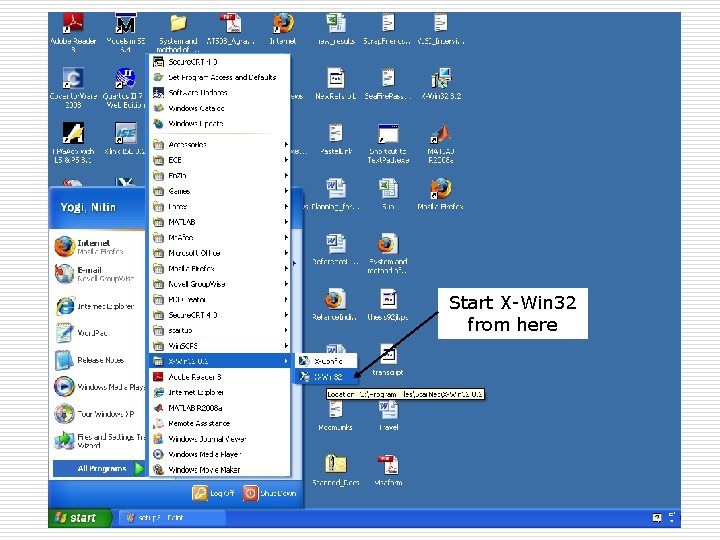

Start X-Win 32 from here Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 3

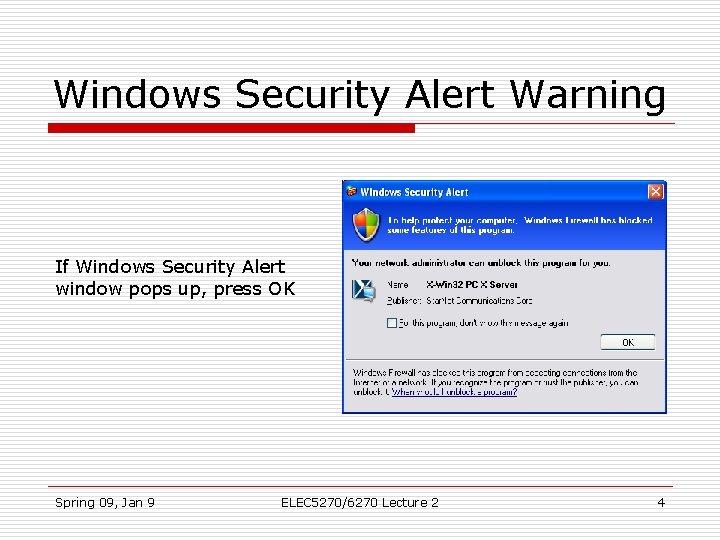

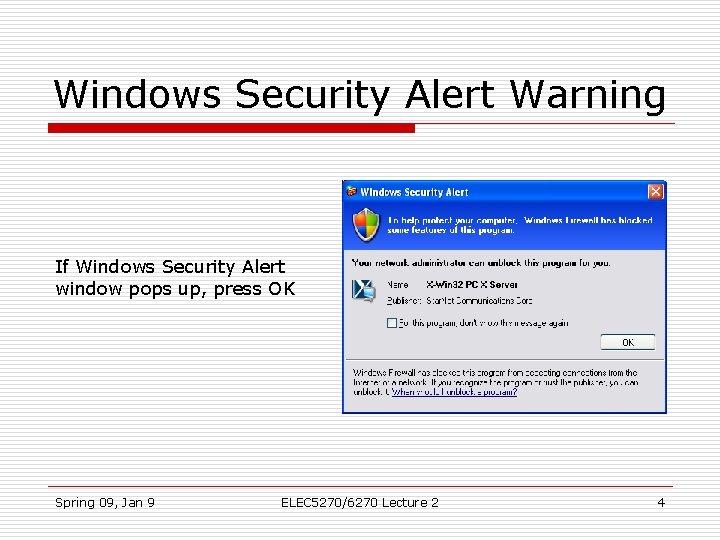

Windows Security Alert Warning If Windows Security Alert window pops up, press OK Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 4

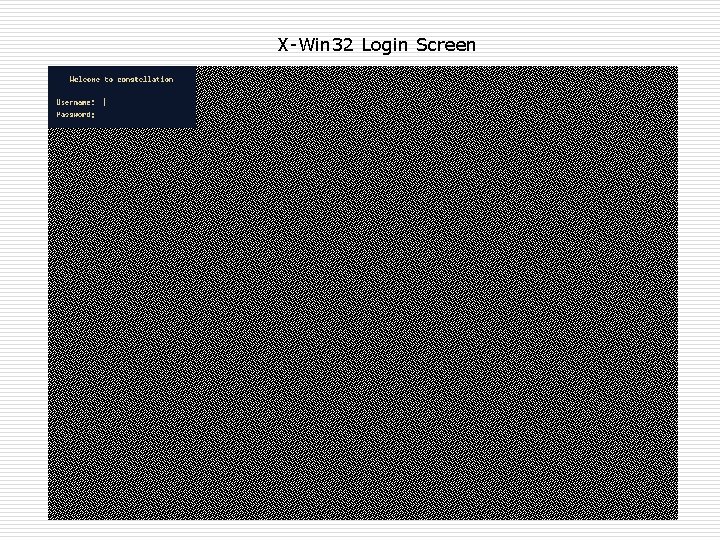

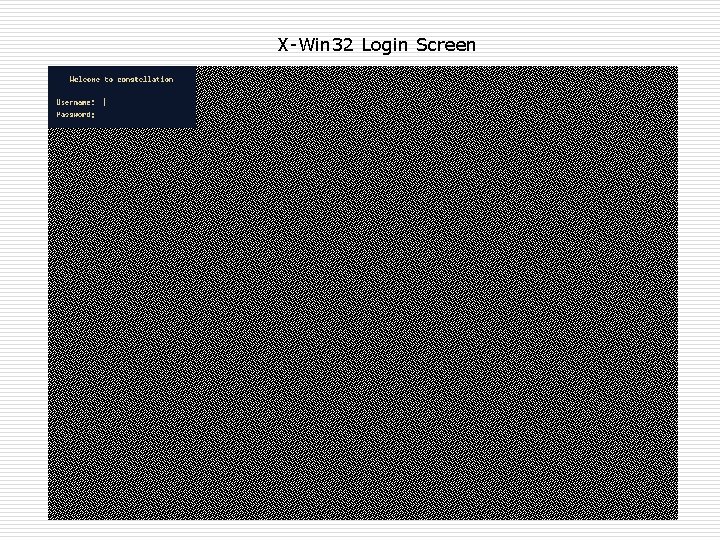

X-Win 32 Login Screen Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 5

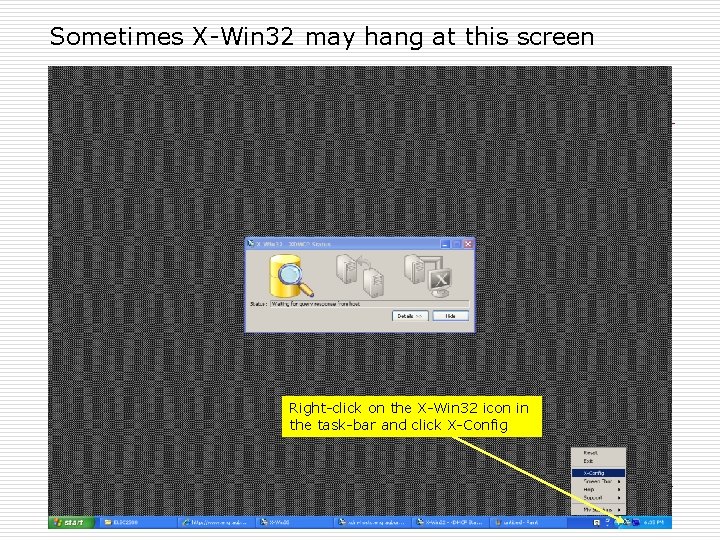

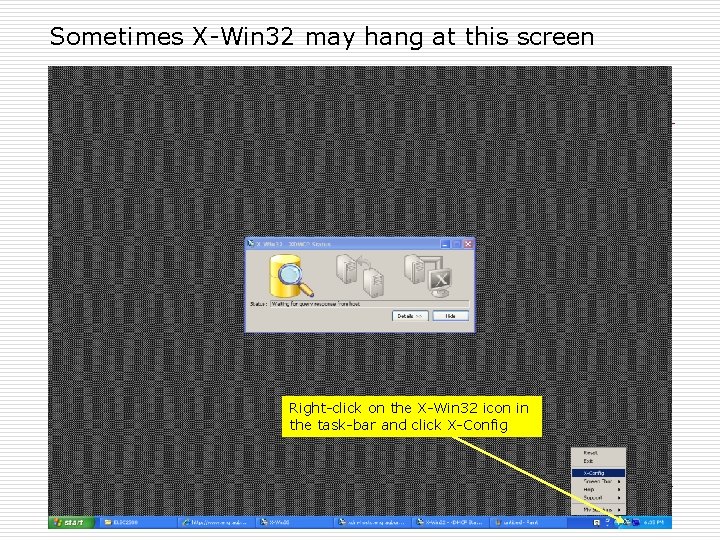

Sometimes X-Win 32 may hang at this screen Right-click on the X-Win 32 icon in the task-bar and click X-Config Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 6

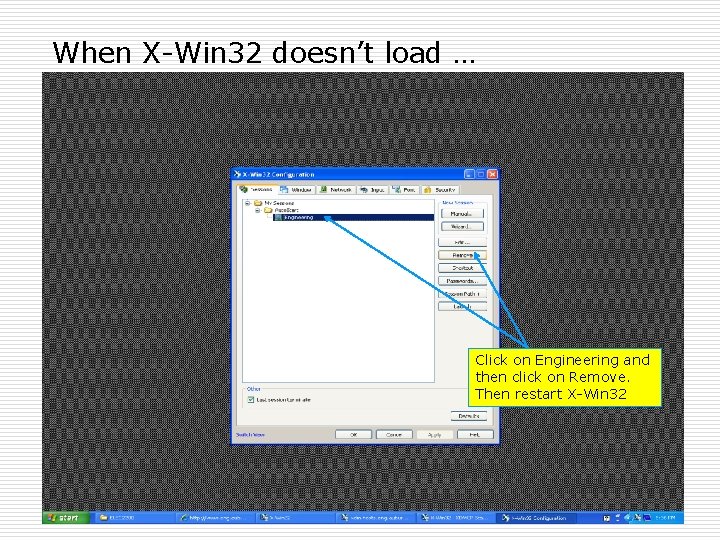

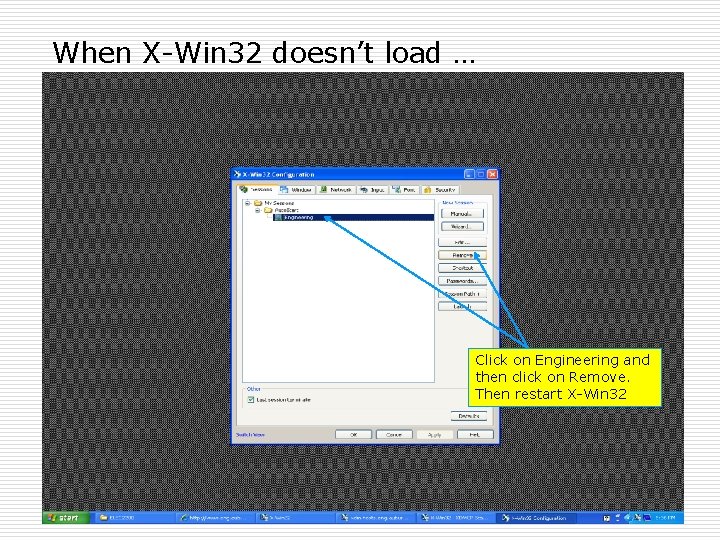

When X-Win 32 doesn’t load … Click on Engineering and then click on Remove. Then restart X-Win 32 Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 7

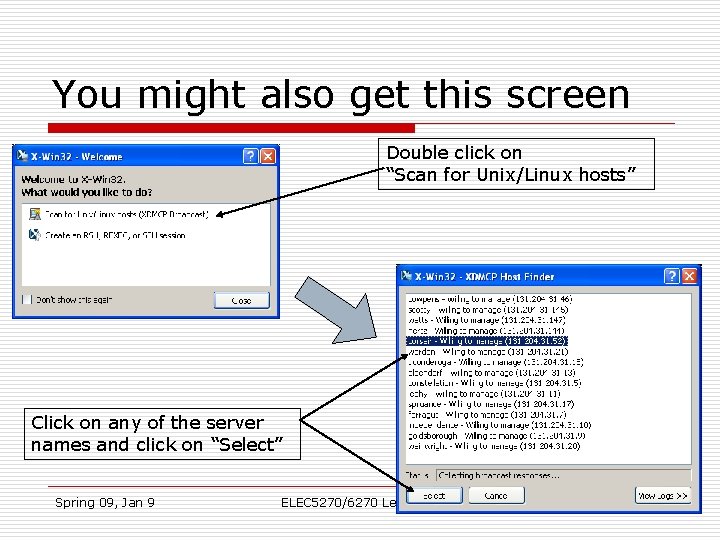

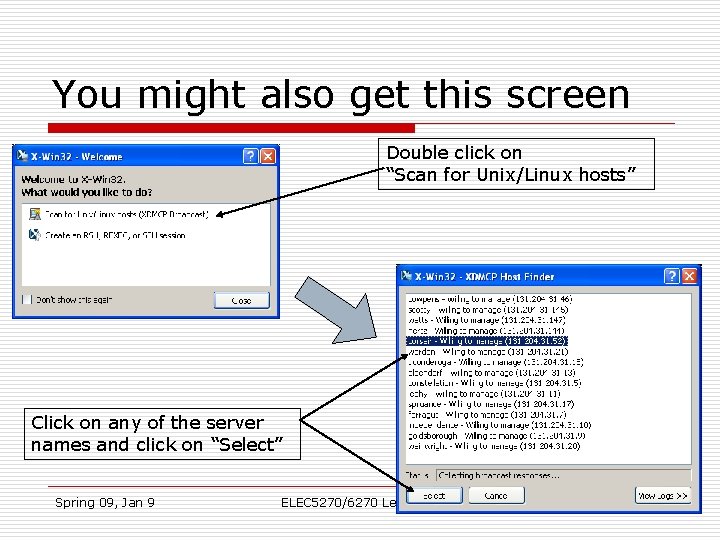

You might also get this screen Double click on “Scan for Unix/Linux hosts” Click on any of the server names and click on “Select” Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 8

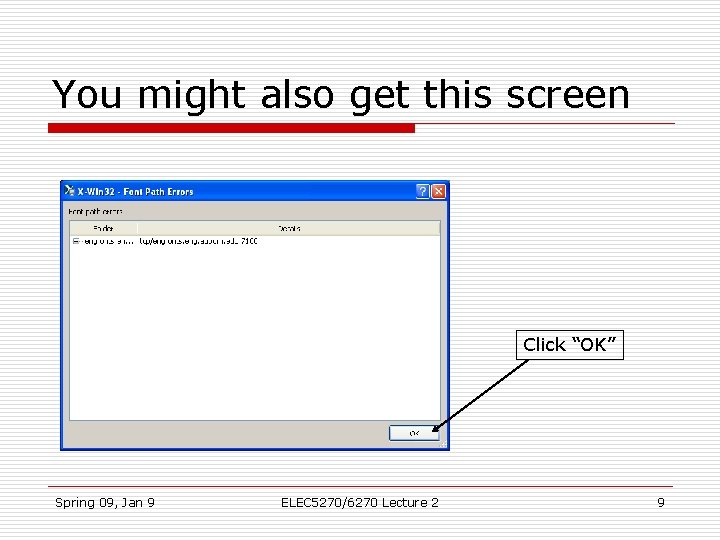

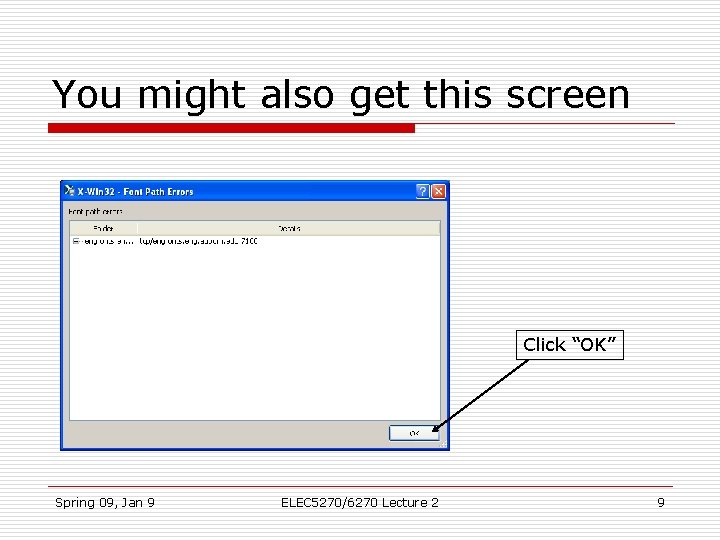

You might also get this screen Click “OK” Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 9

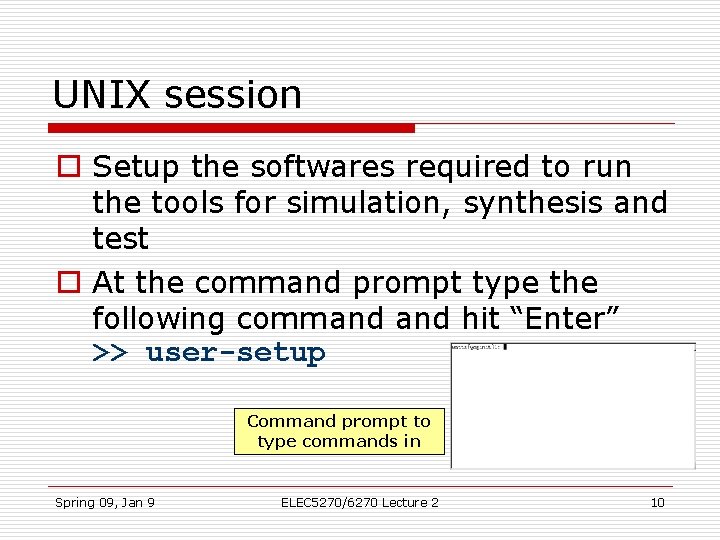

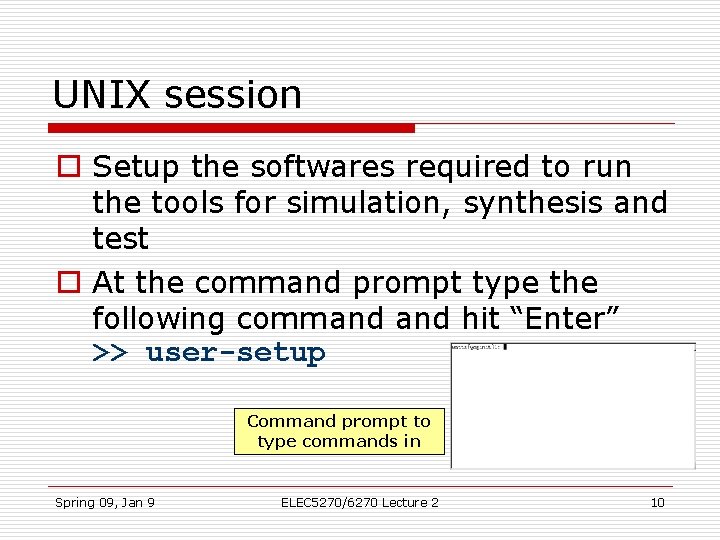

UNIX session o Setup the softwares required to run the tools for simulation, synthesis and test o At the command prompt type the following command hit “Enter” >> user-setup Command prompt to type commands in Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 10

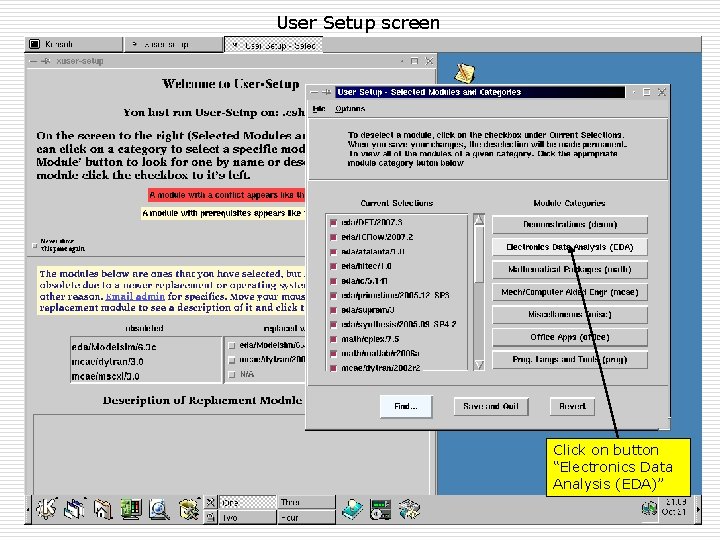

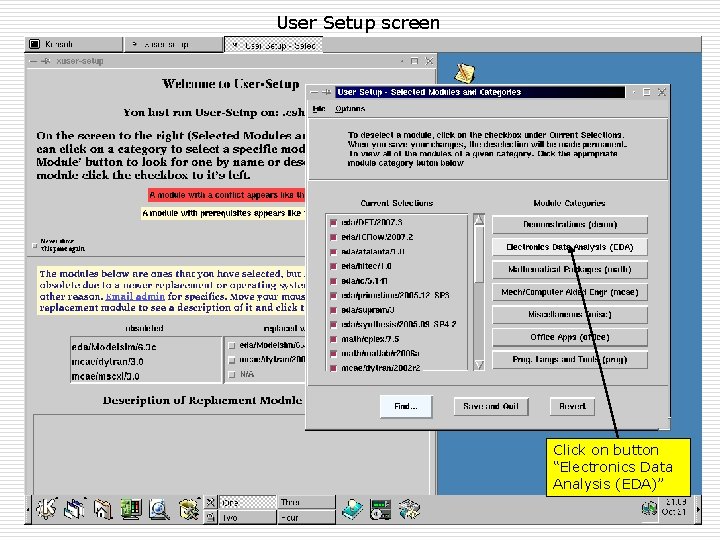

User Setup screen Click on button “Electronics Data Analysis (EDA)” Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 11

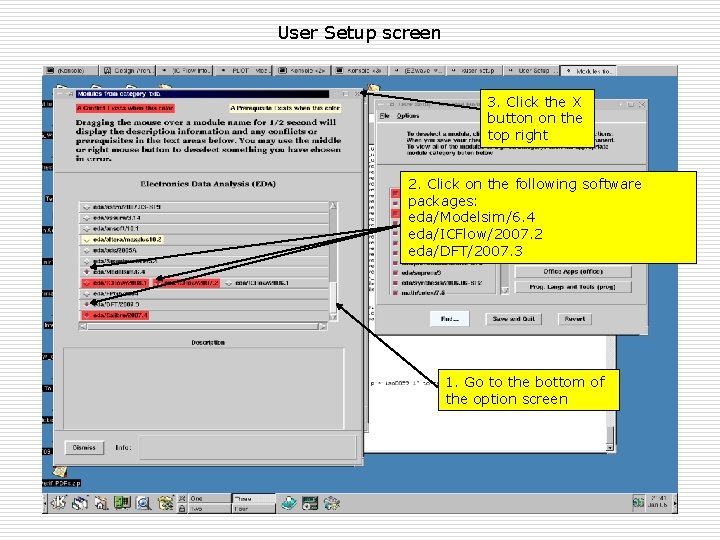

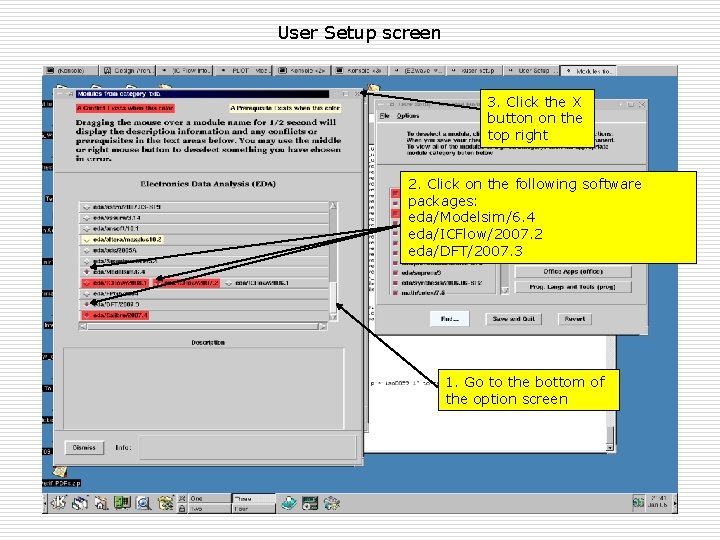

User Setup screen 3. Click the X button on the top right 2. Click on the following software packages: eda/Modelsim/6. 4 eda/ICFlow/2007. 2 eda/DFT/2007. 3 1. Go to the bottom of the option screen Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 12

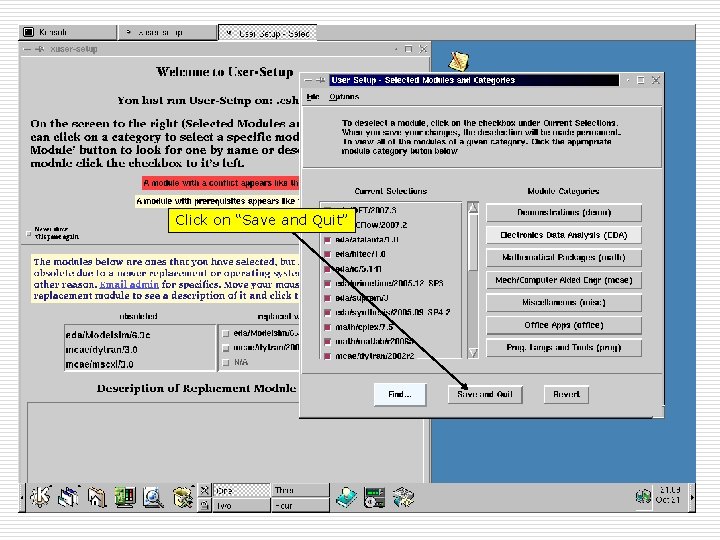

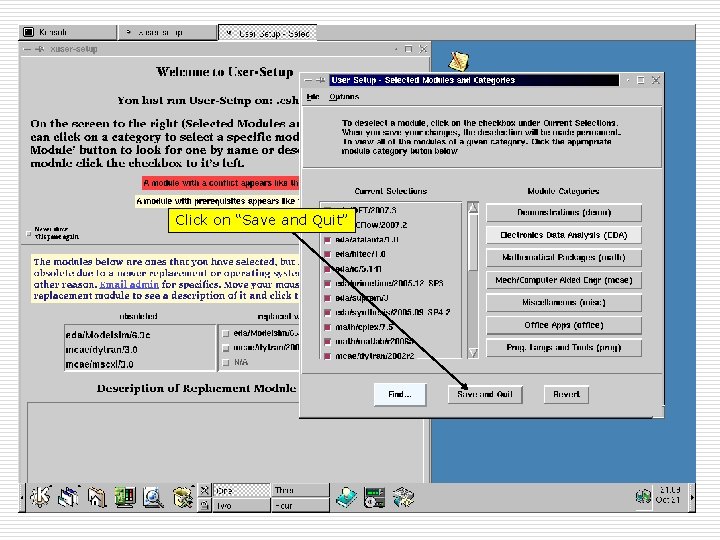

Click on “Save and Quit” Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 13

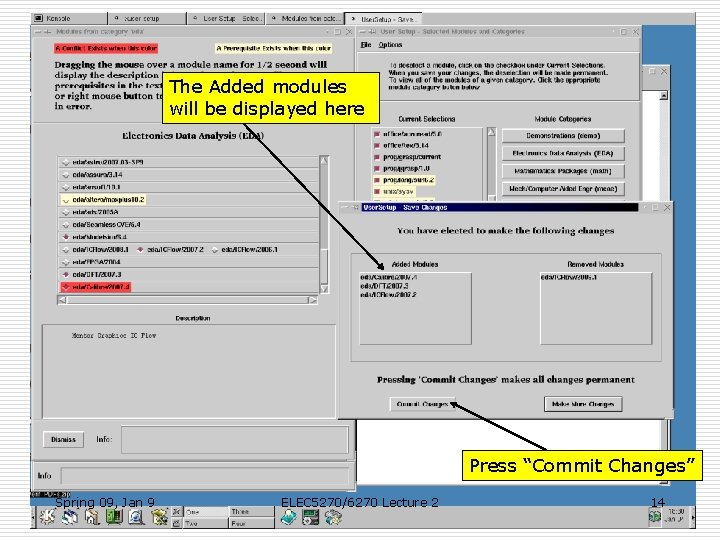

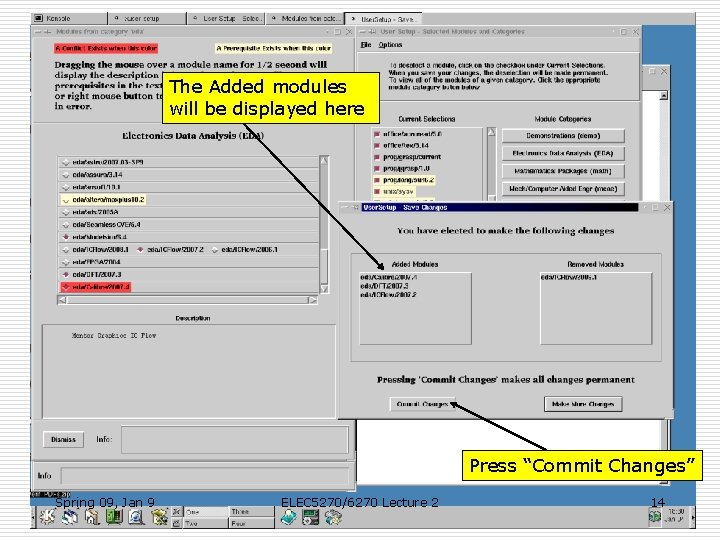

The Added modules will be displayed here Press “Commit Changes” Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 14

X-Win 32 reset o Exit X-Win 32 and restart the X-Win 32 session again as described earlier Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 15

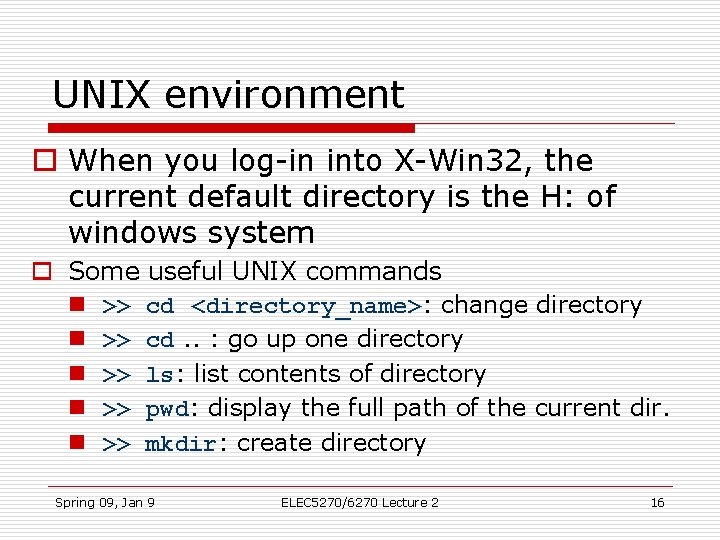

UNIX environment o When you log-in into X-Win 32, the current default directory is the H: of windows system o Some useful UNIX commands n >> cd <directory_name>: change directory n >> cd. . : go up one directory n >> ls: list contents of directory n >> pwd: display the full path of the current dir. n >> mkdir: create directory Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 16

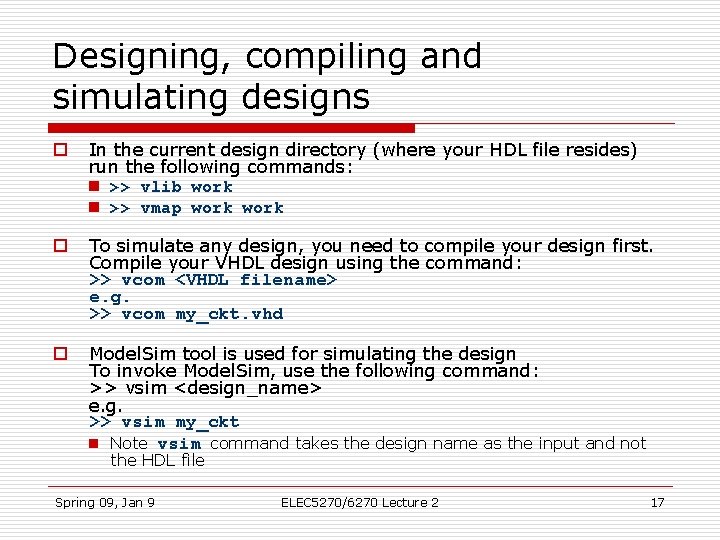

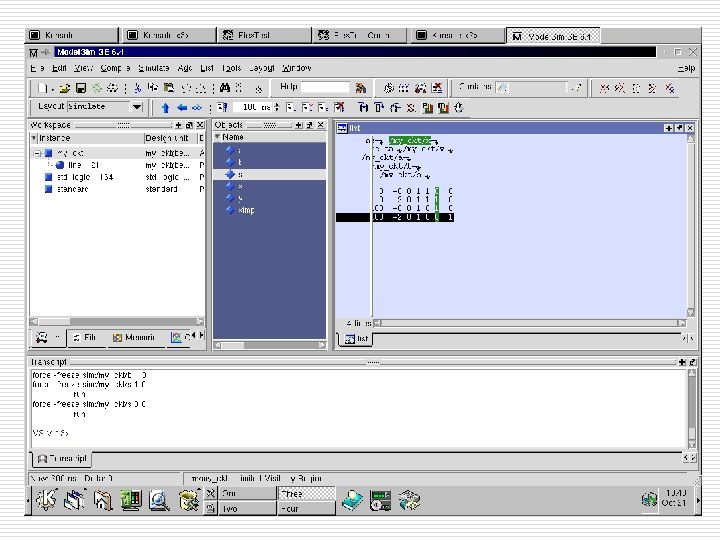

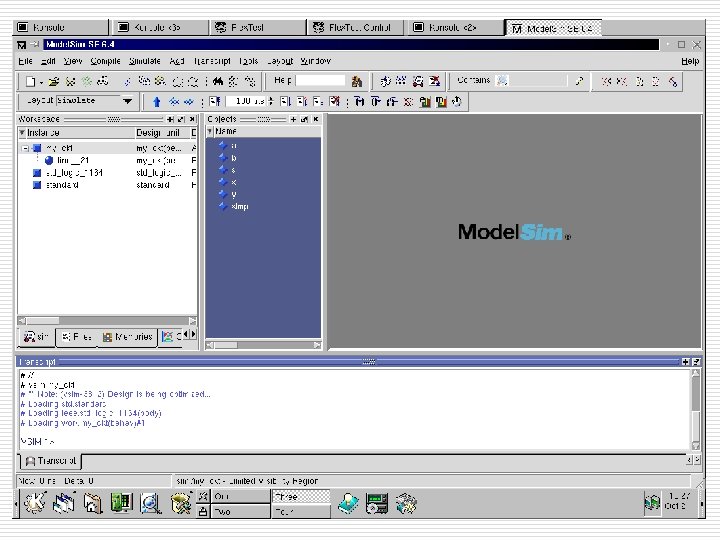

Designing, compiling and simulating designs o In the current design directory (where your HDL file resides) run the following commands: n >> vlib work n >> vmap work o To simulate any design, you need to compile your design first. Compile your VHDL design using the command: >> vcom <VHDL filename> e. g. >> vcom my_ckt. vhd o Model. Sim tool is used for simulating the design To invoke Model. Sim, use the following command: >> vsim <design_name> e. g. >> vsim my_ckt n Note vsim command takes the design name as the input and not the HDL file Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 17

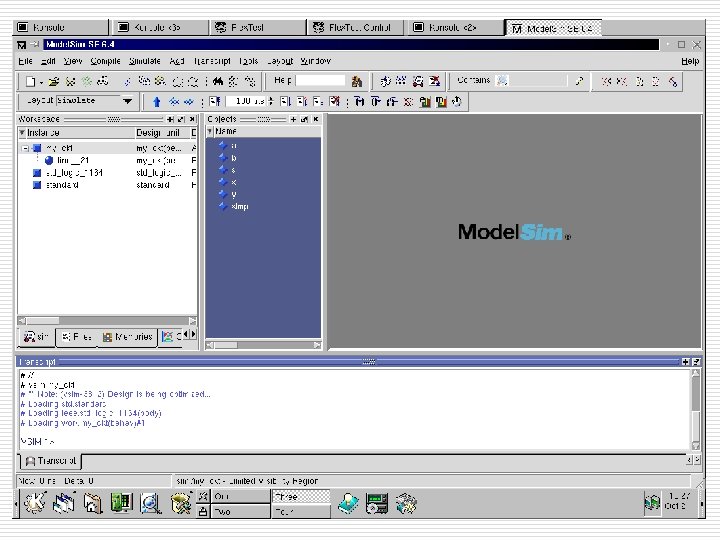

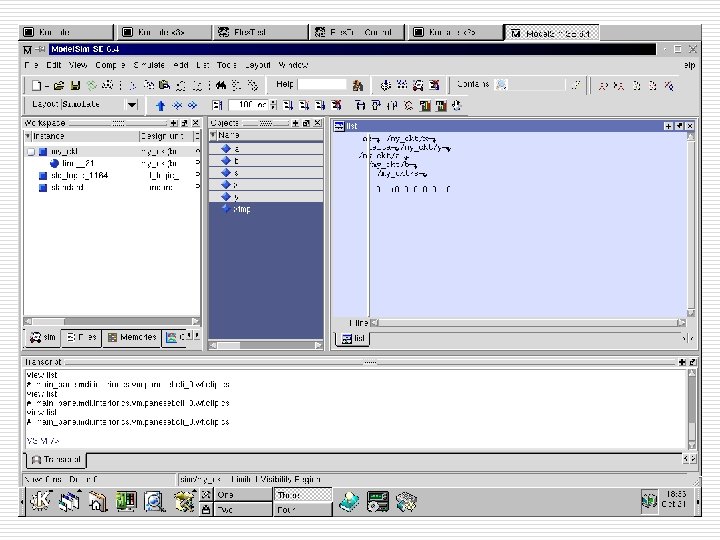

Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 18

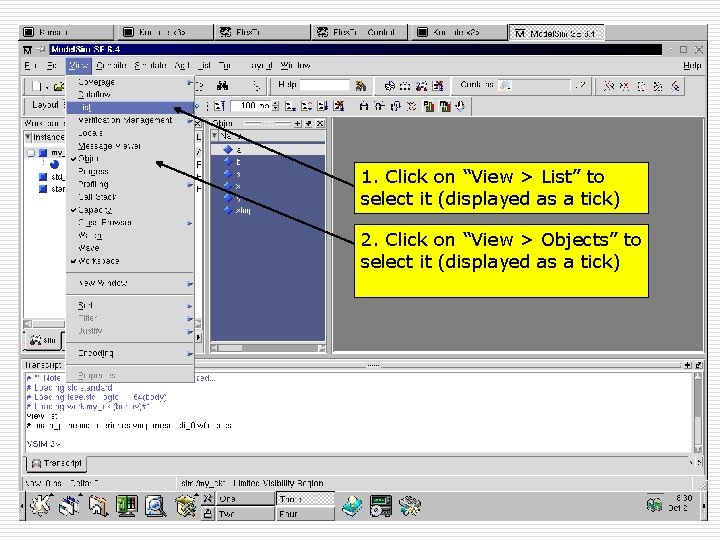

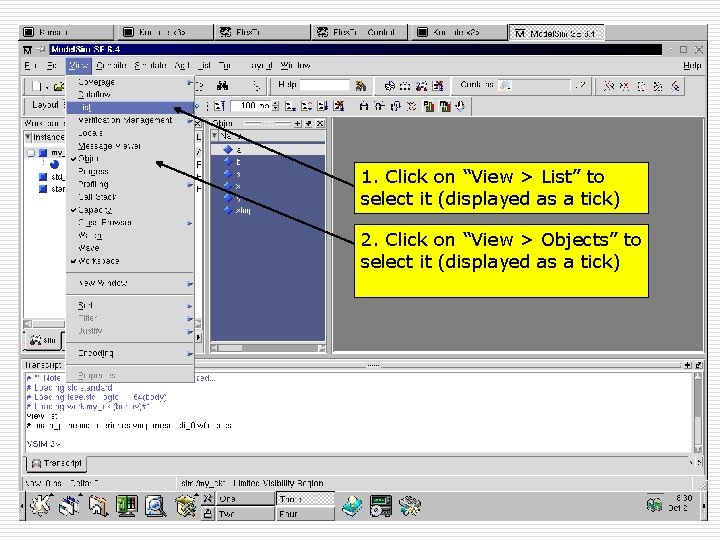

1. Click on “View > List” to select it (displayed as a tick) 2. Click on “View > Objects” to select it (displayed as a tick) Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 19

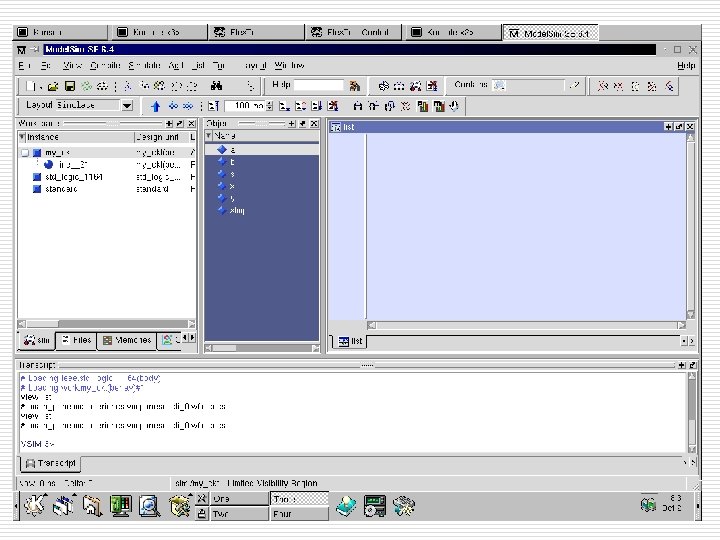

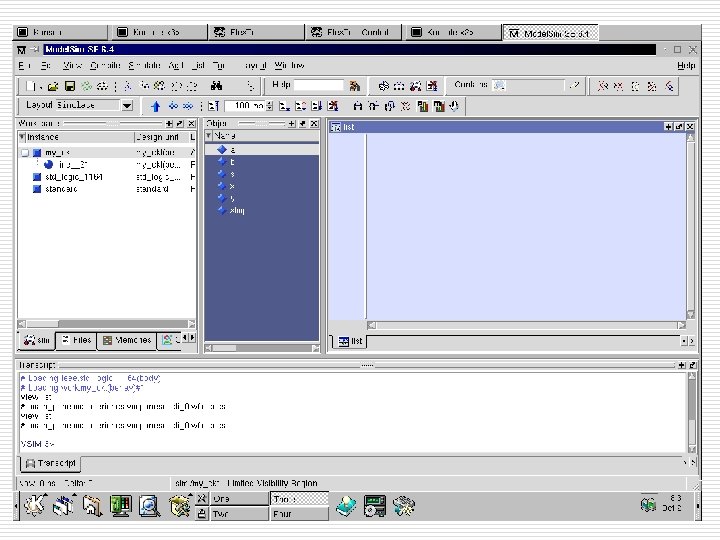

Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 20

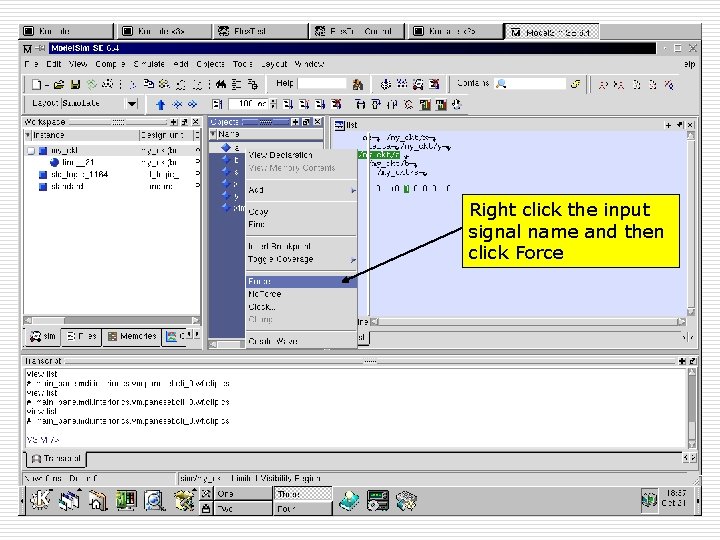

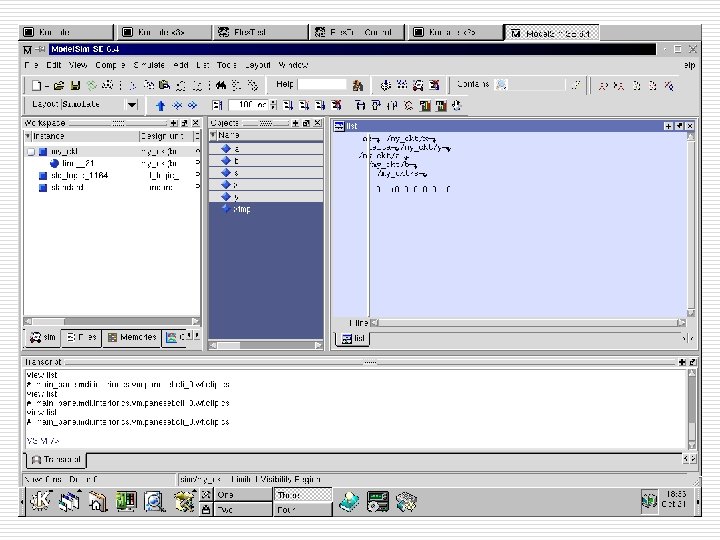

Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 21

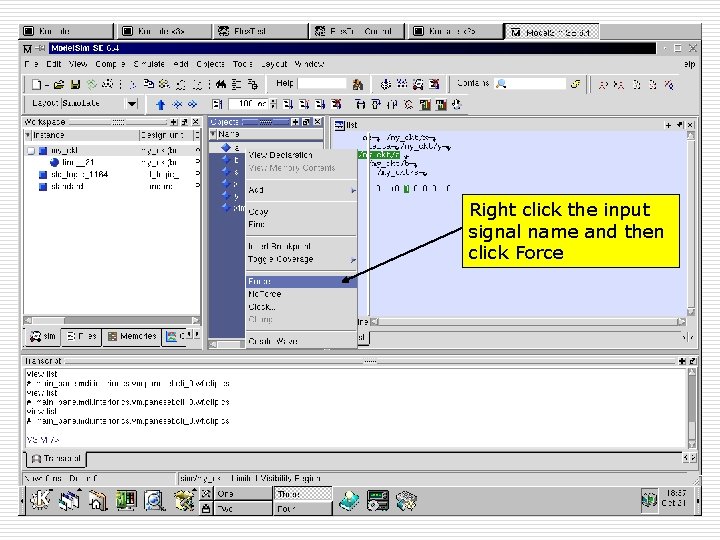

Right click the input signal name and then click Force Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 22

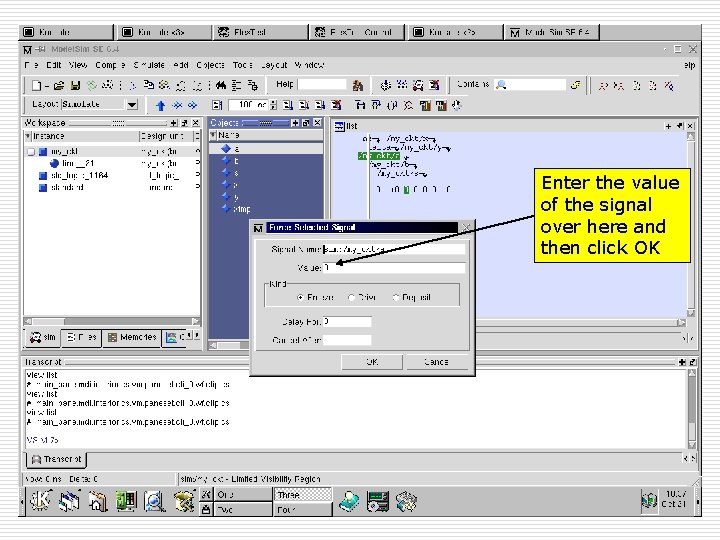

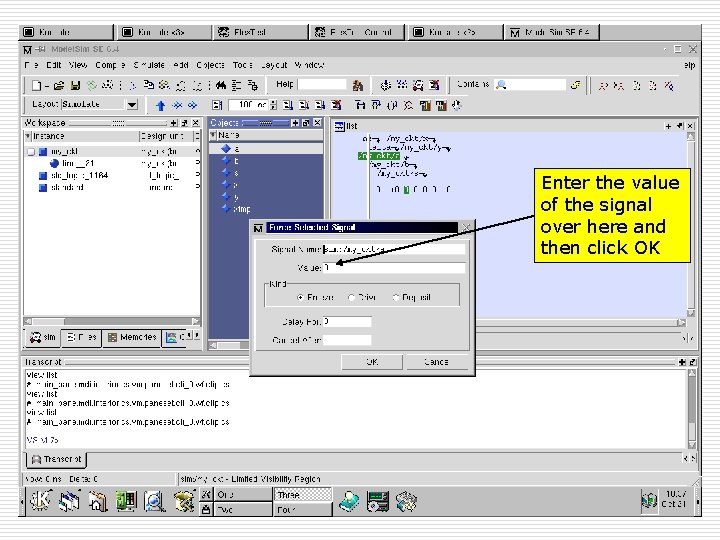

Enter the value of the signal over here and then click OK Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 23

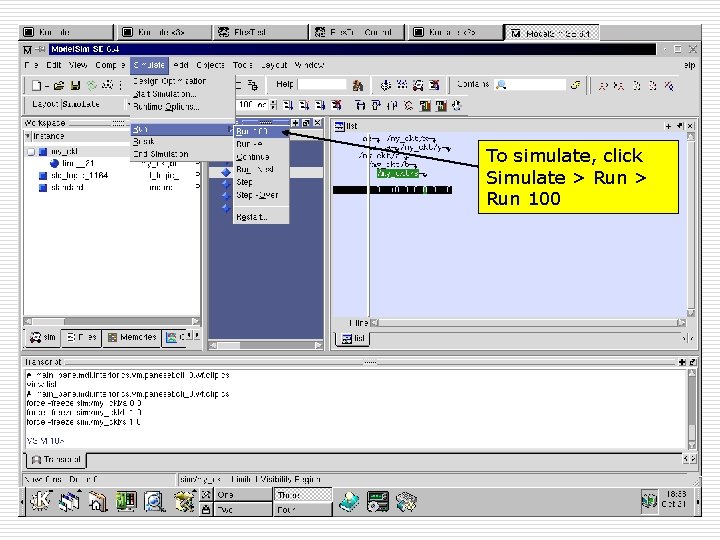

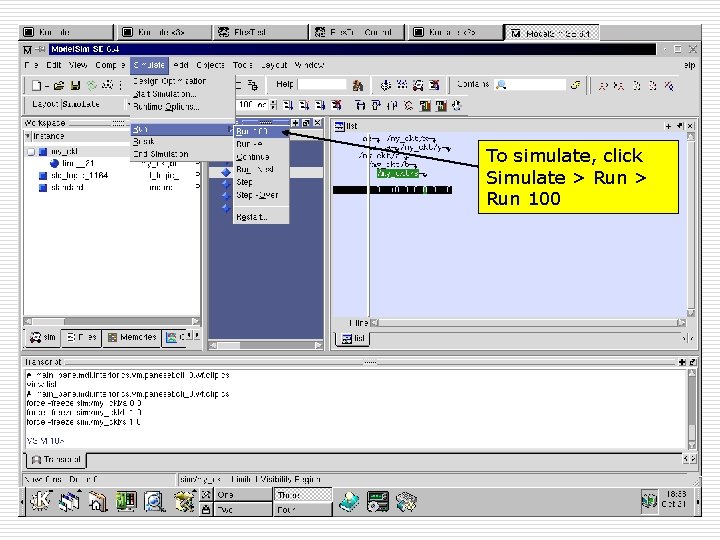

To simulate, click Simulate > Run 100 Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 24

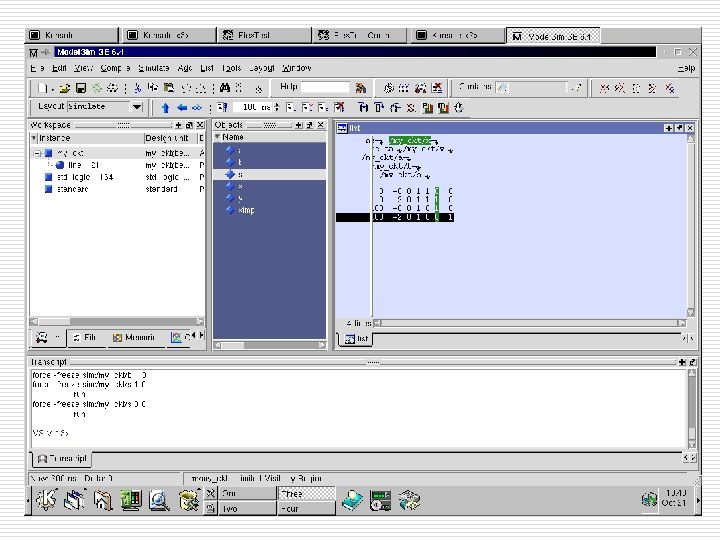

Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 25

Useful resource o “VHDL Design and Simulation using Model. Sim” on Prof. Nelson’s website n http: //www. eng. auburn. edu/department /ee/mgc/quickvhdl/modelsim. html Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 26

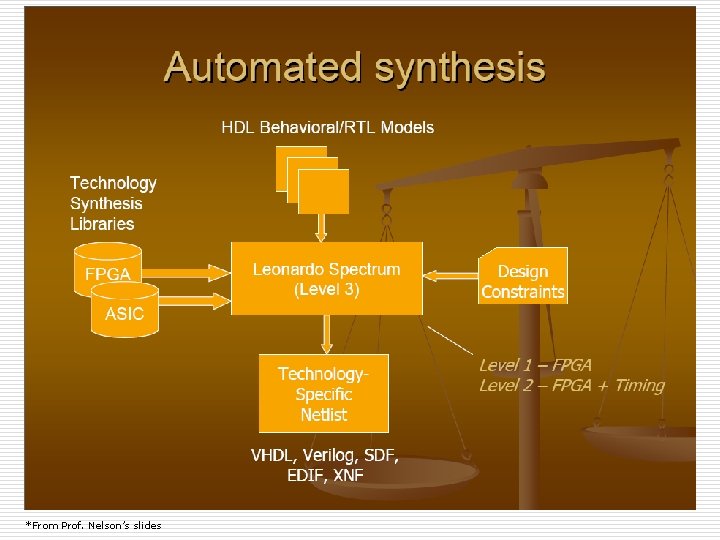

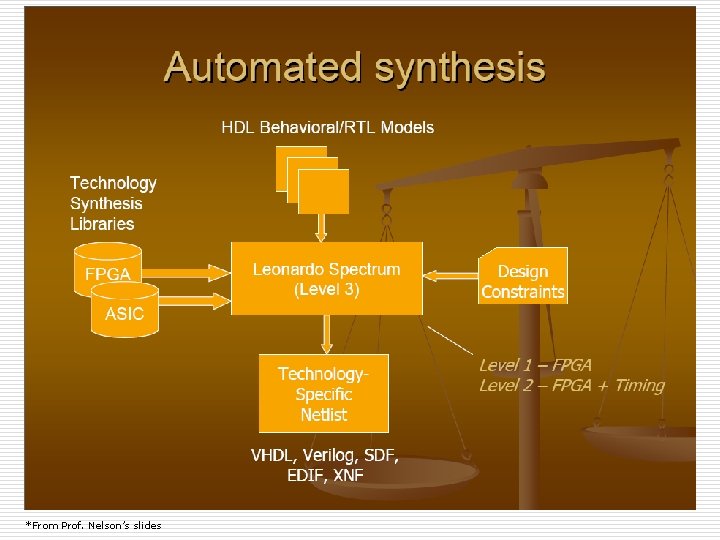

Spring 09, Jan 9 *From Prof. Nelson’s slides ELEC 5270/6270 Lecture 2 27

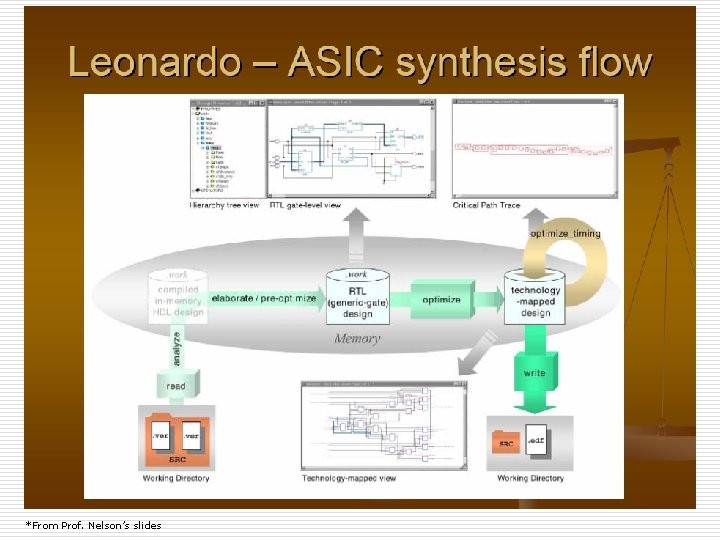

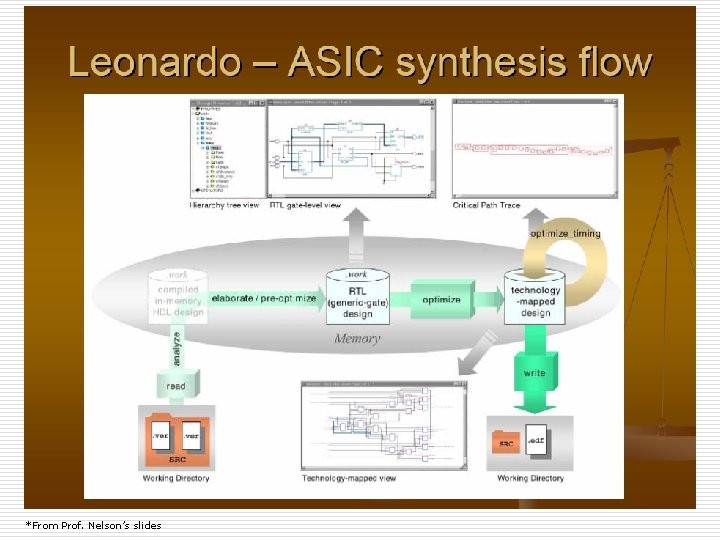

Spring 09, Jan 9 *From Prof. Nelson’s slides ELEC 5270/6270 Lecture 2 28

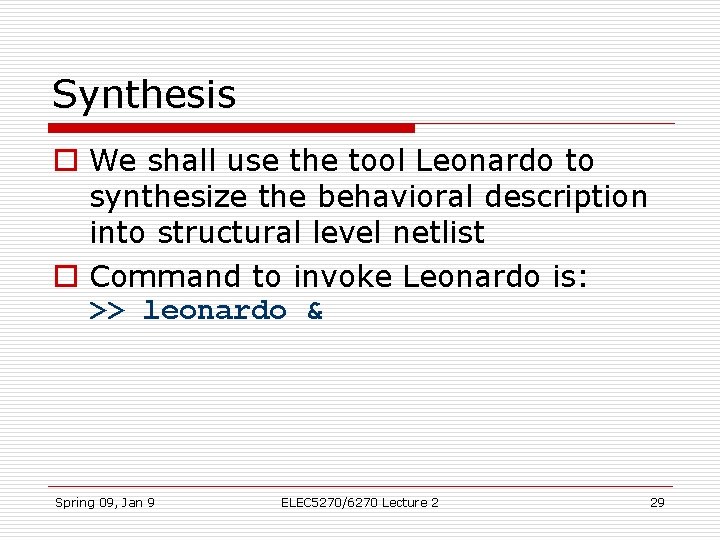

Synthesis o We shall use the tool Leonardo to synthesize the behavioral description into structural level netlist o Command to invoke Leonardo is: >> leonardo & Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 29

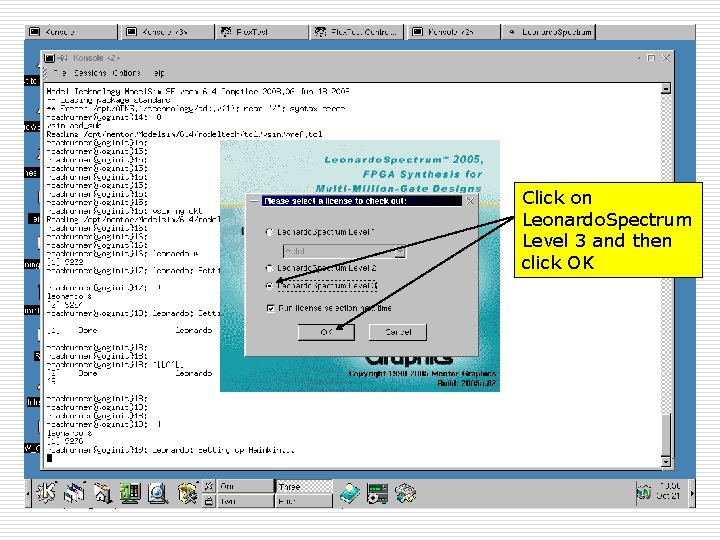

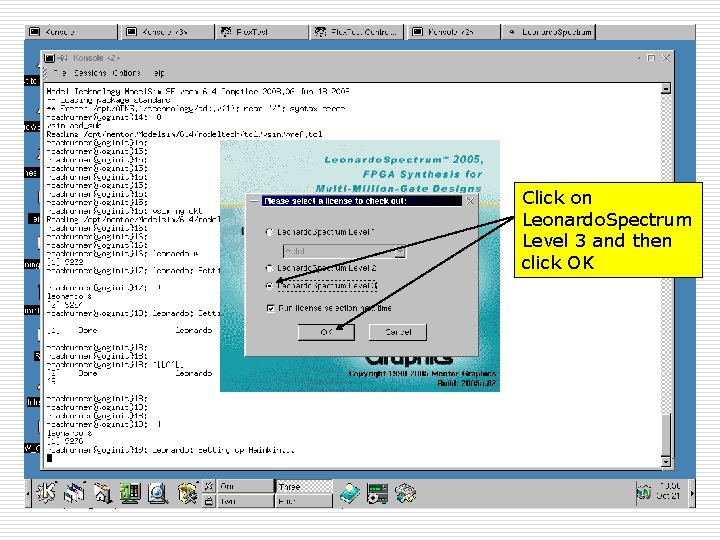

Click on Leonardo. Spectrum Level 3 and then click OK Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 30

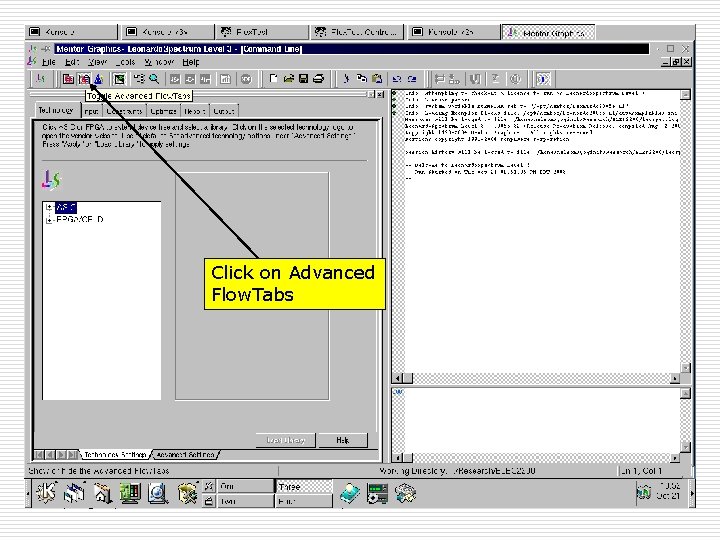

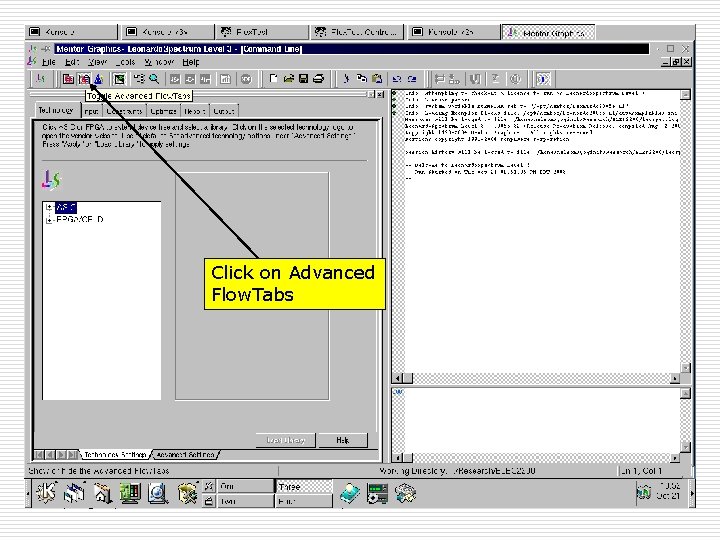

Click on Advanced Flow. Tabs Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 31

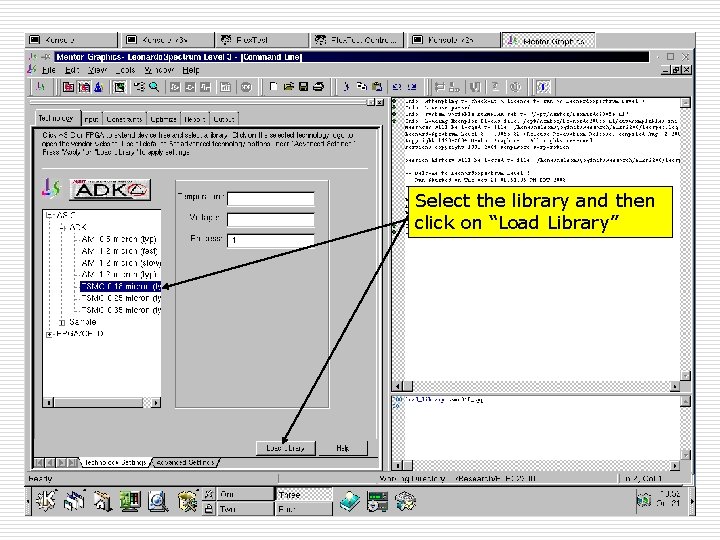

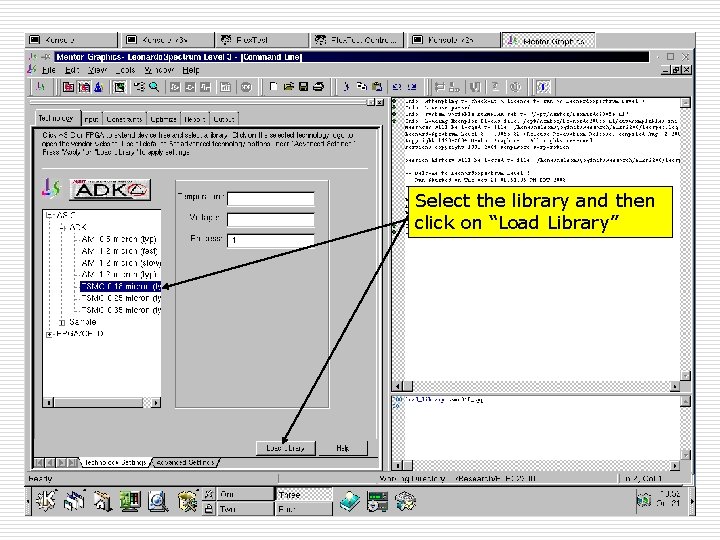

Select the library and then click on “Load Library” Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 32

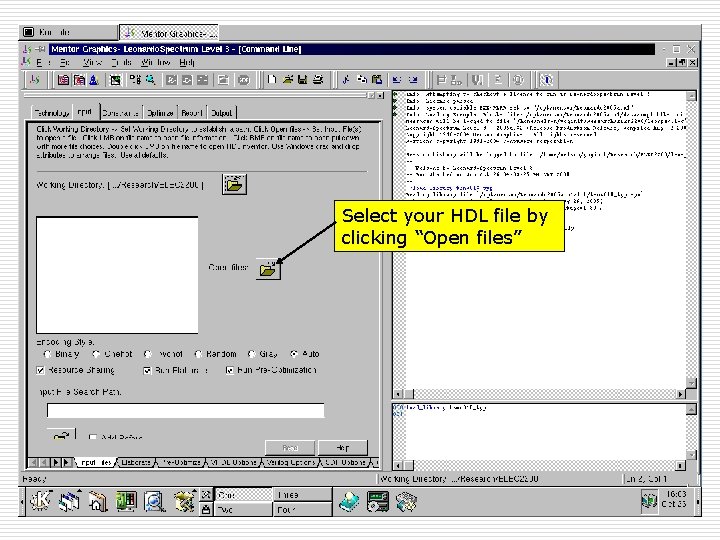

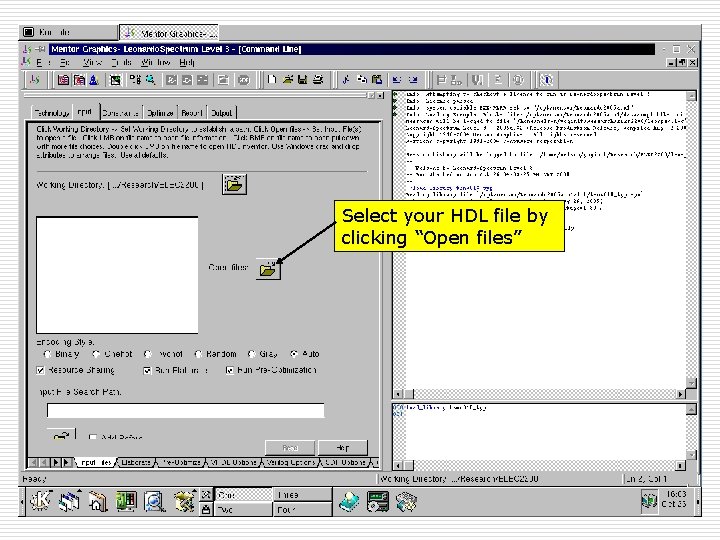

Select your HDL file by clicking “Open files” Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 33

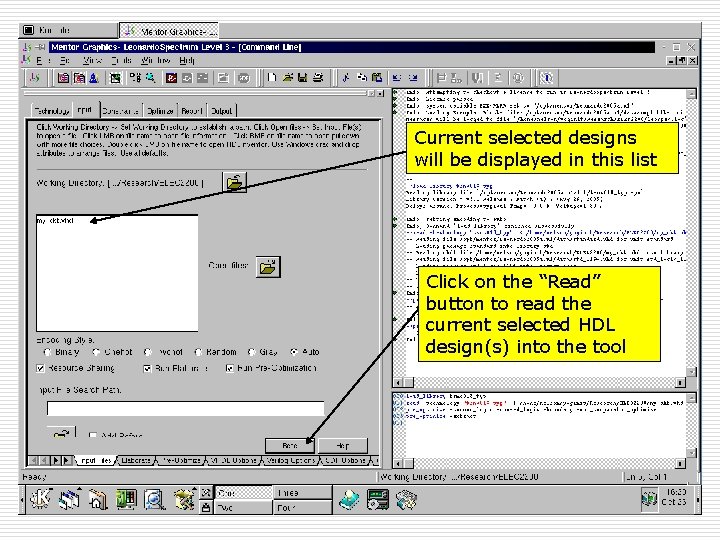

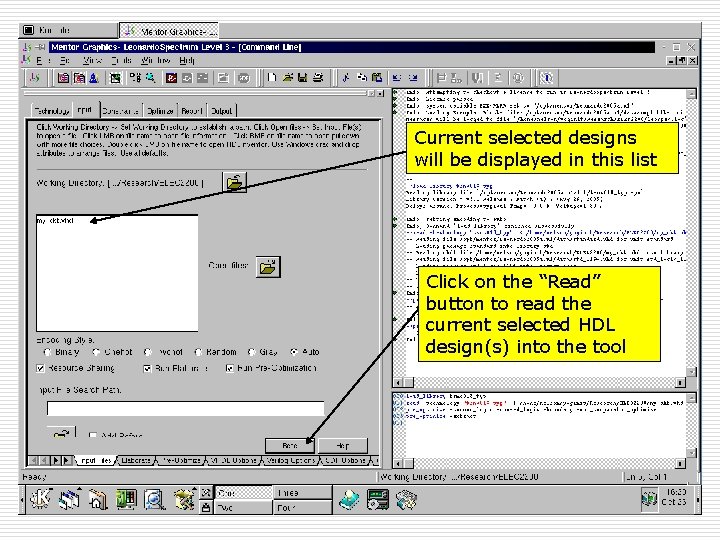

Current selected designs will be displayed in this list Click on the “Read” button to read the current selected HDL design(s) into the tool Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 34

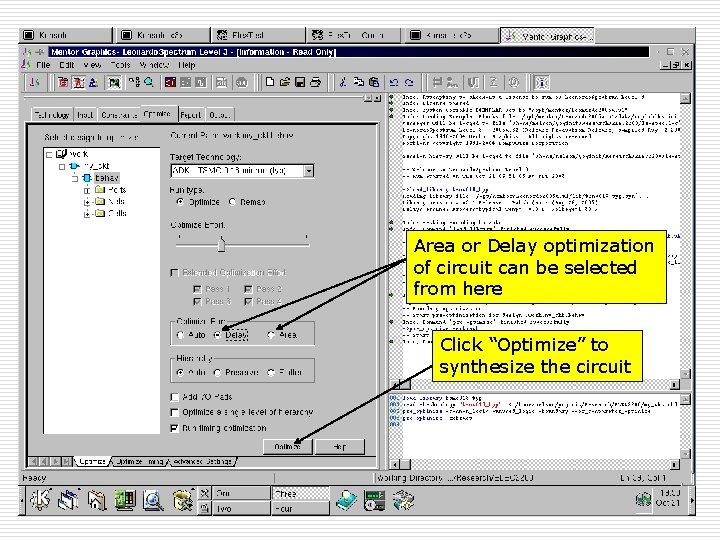

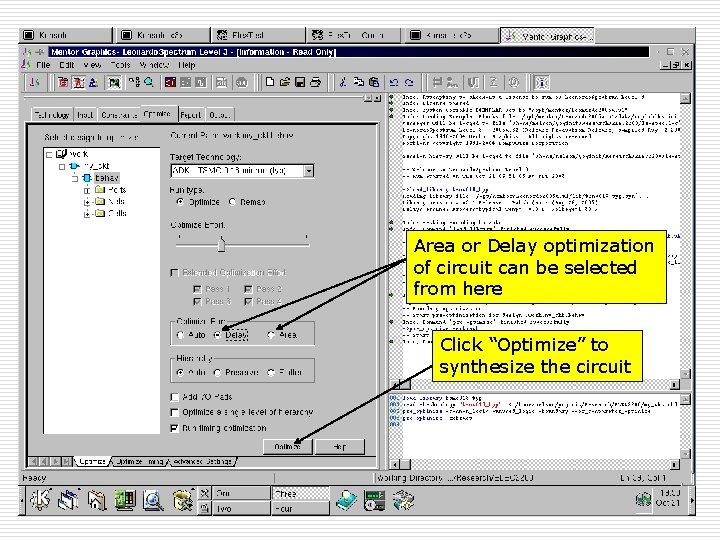

Area or Delay optimization of circuit can be selected from here Click “Optimize” to synthesize the circuit Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 35

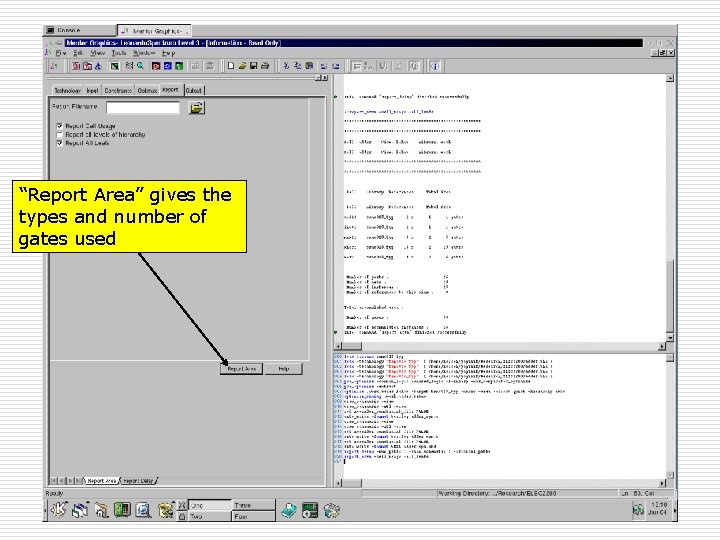

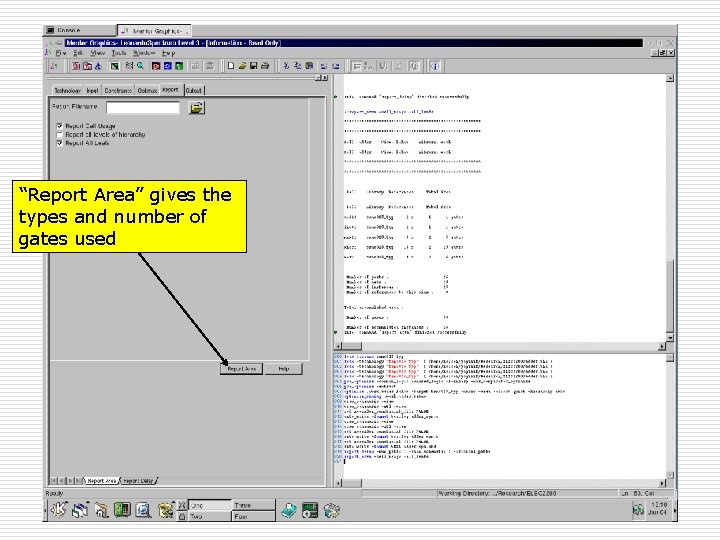

“Report Area” gives the types and number of gates used Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 36

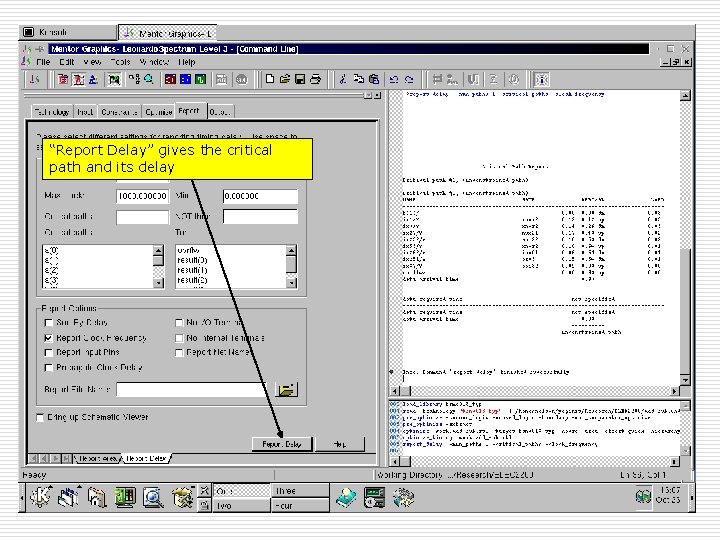

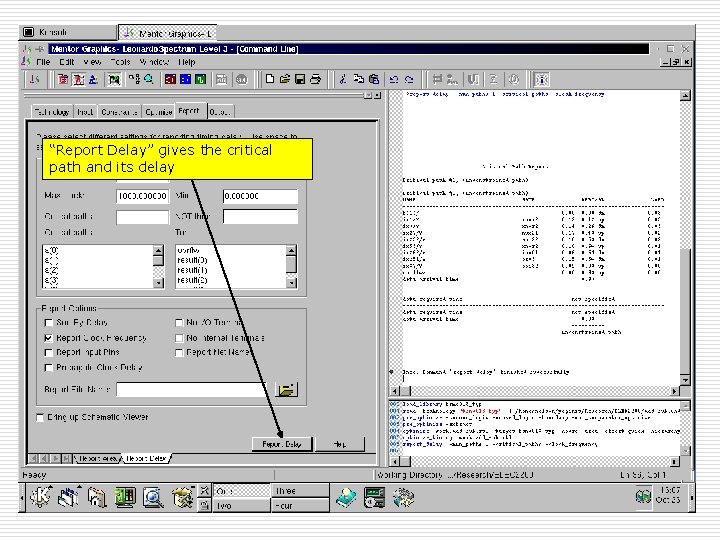

“Report Delay” gives the critical path and its delay Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 37

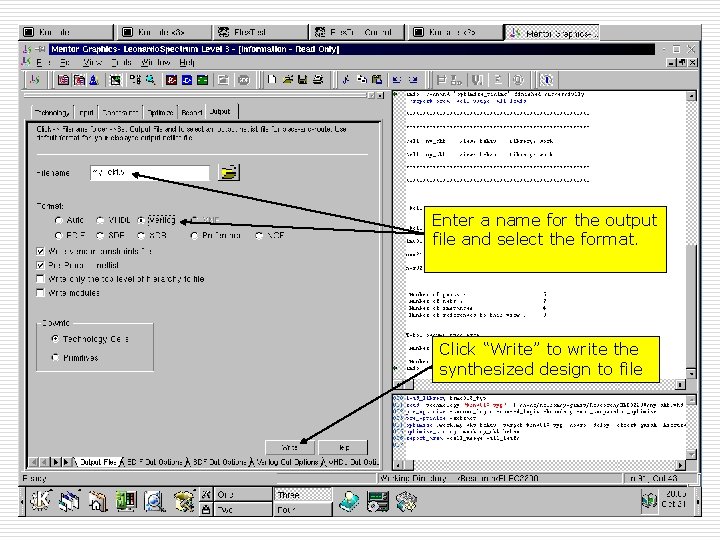

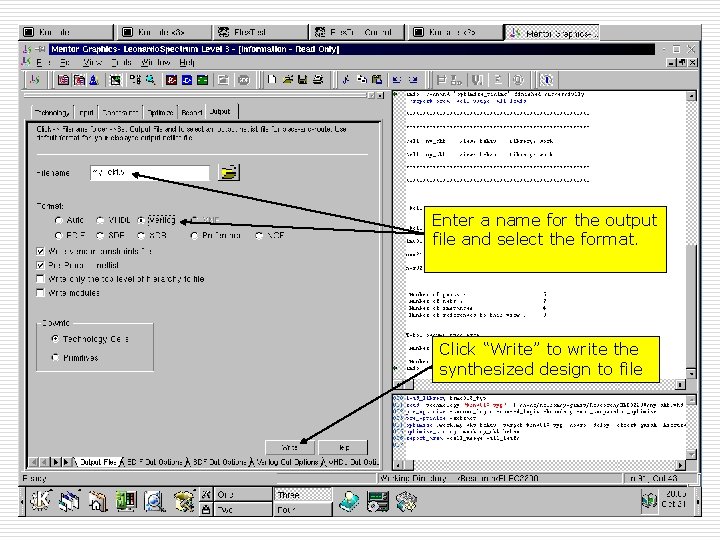

Enter a name for the output file and select the format. Click “Write” to write the synthesized design to file Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 38

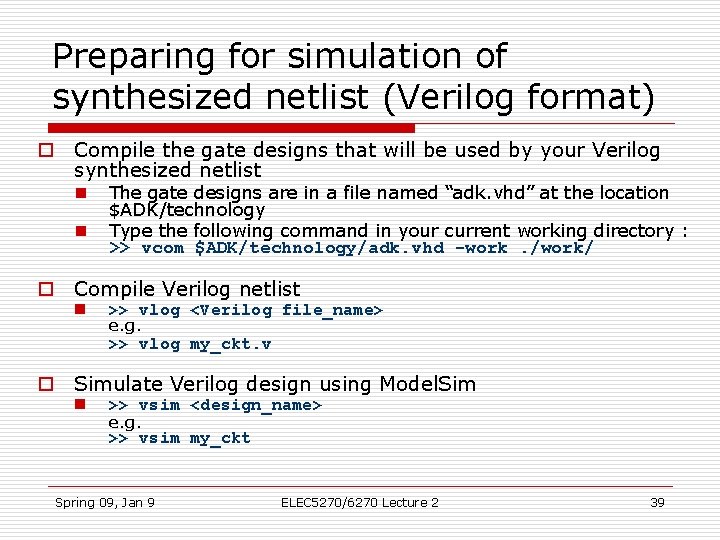

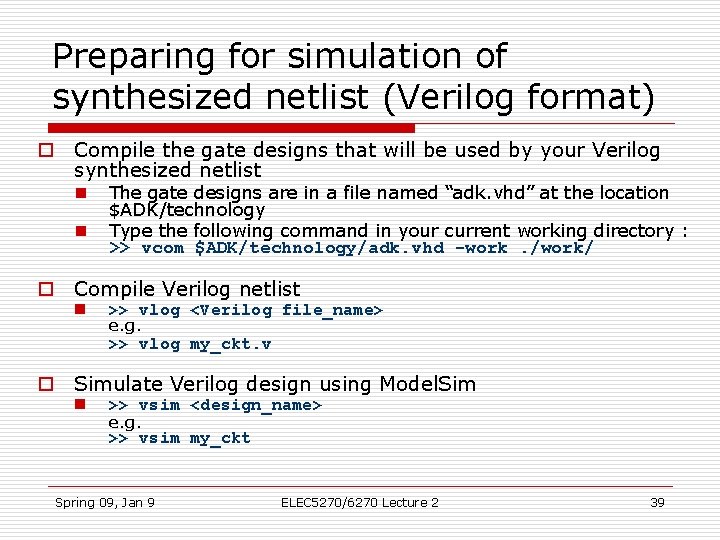

Preparing for simulation of synthesized netlist (Verilog format) o Compile the gate designs that will be used by your Verilog synthesized netlist n n The gate designs are in a file named “adk. vhd” at the location $ADK/technology Type the following command in your current working directory : >> vcom $ADK/technology/adk. vhd -work. /work/ o Compile Verilog netlist n >> vlog <Verilog file_name> e. g. >> vlog my_ckt. v o Simulate Verilog design using Model. Sim n >> vsim <design_name> e. g. >> vsim my_ckt Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 39

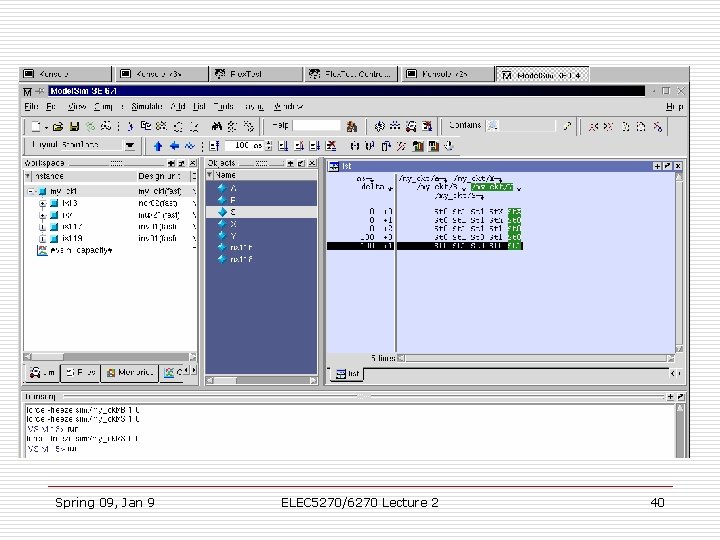

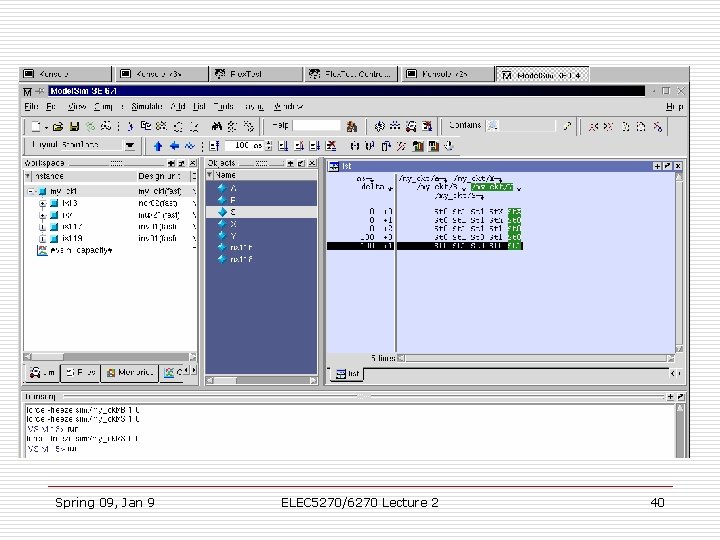

Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 40

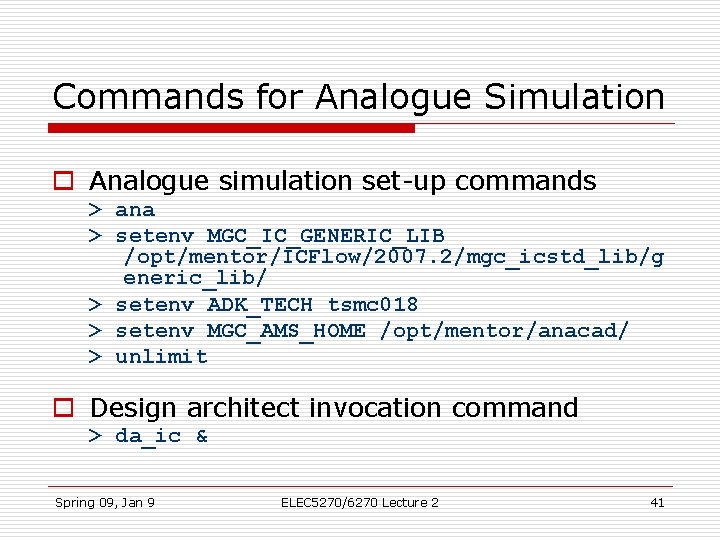

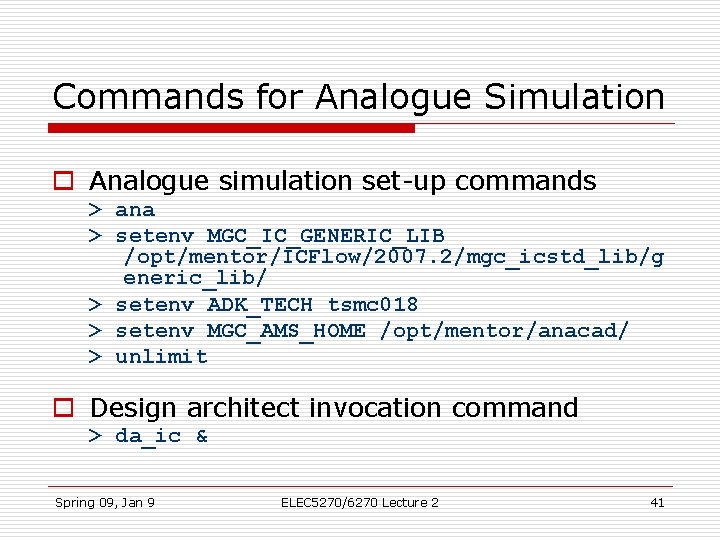

Commands for Analogue Simulation o Analogue simulation set-up commands > ana > setenv MGC_IC_GENERIC_LIB /opt/mentor/ICFlow/2007. 2/mgc_icstd_lib/g eneric_lib/ > setenv ADK_TECH tsmc 018 > setenv MGC_AMS_HOME /opt/mentor/anacad/ > unlimit o Design architect invocation command > da_ic & Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 41

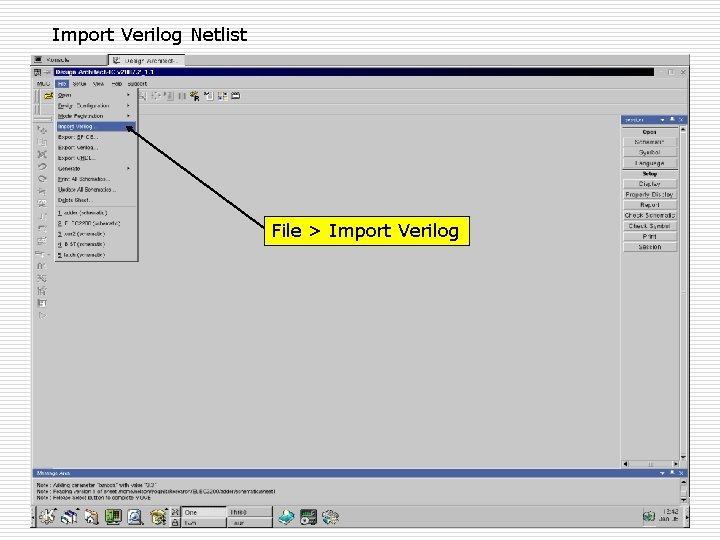

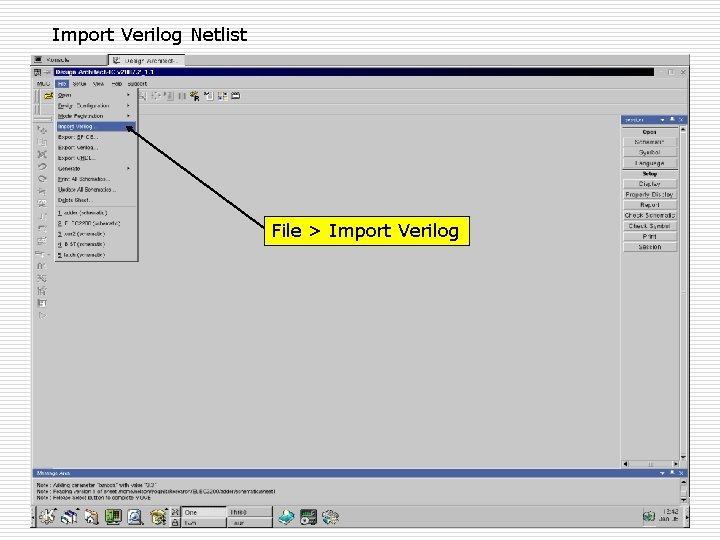

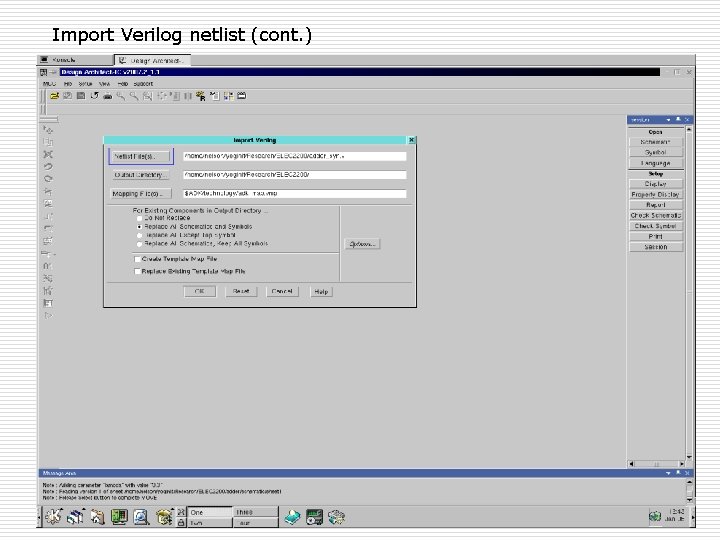

Import Verilog Netlist File > Import Verilog Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 42

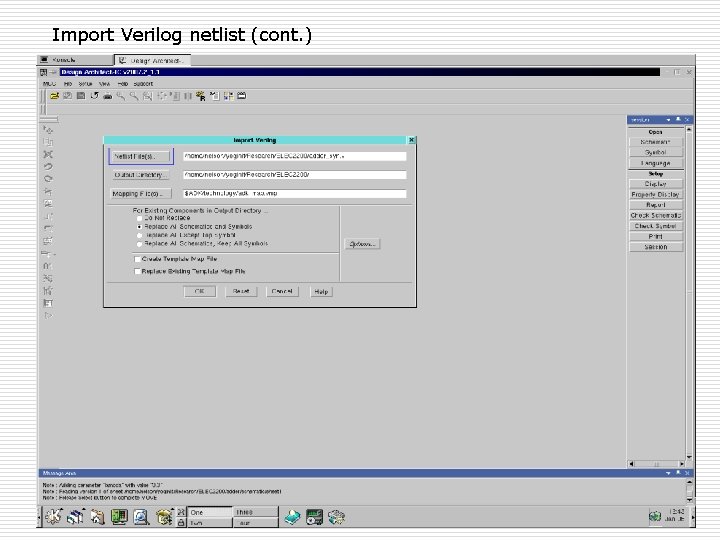

Import Verilog netlist (cont. ) Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 43

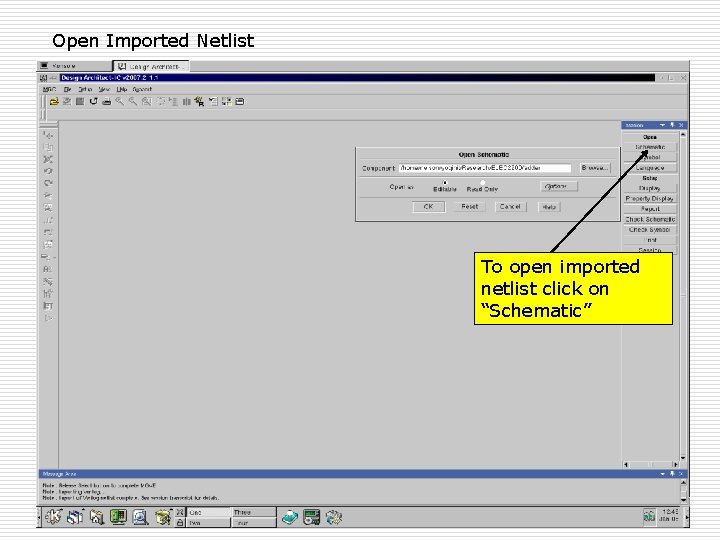

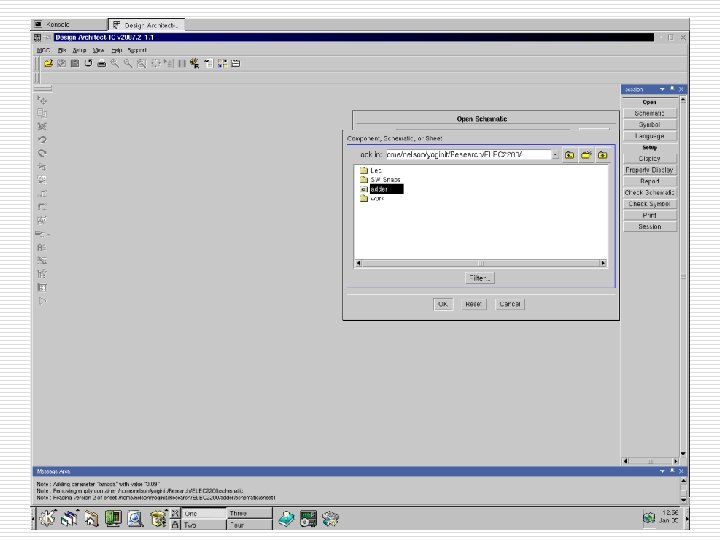

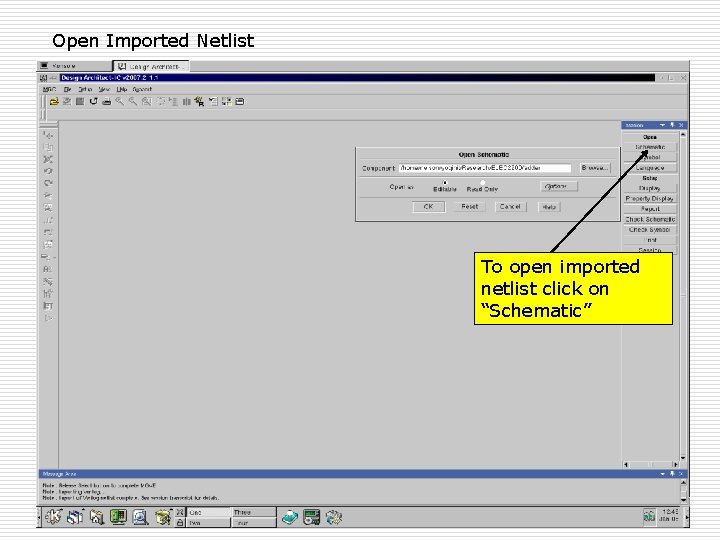

Open Imported Netlist To open imported netlist click on “Schematic” Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 44

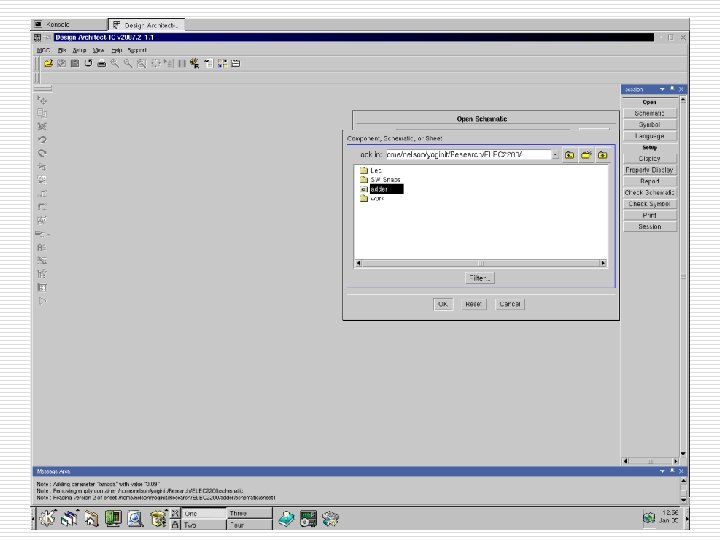

Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 45

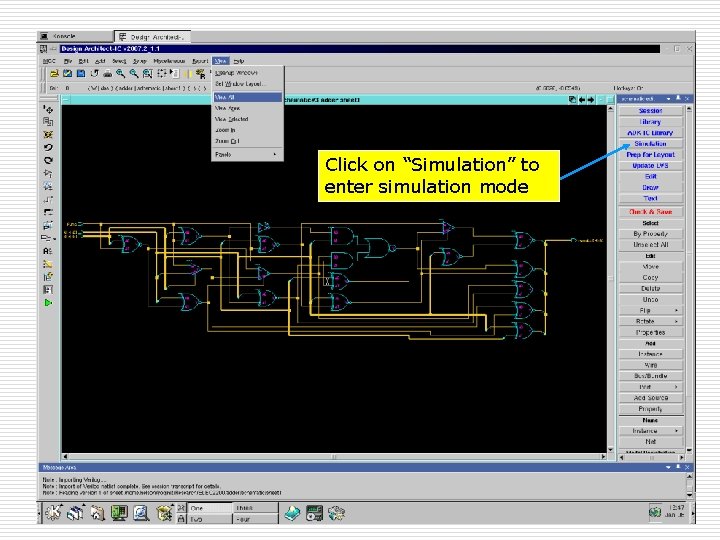

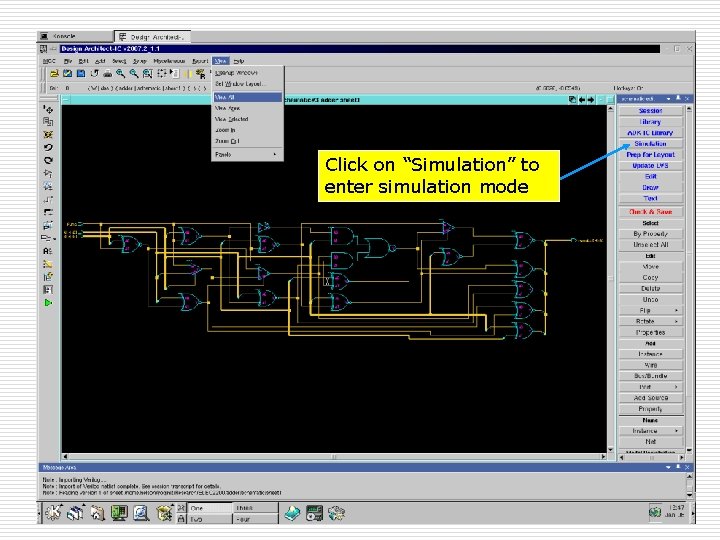

Click on “Simulation” to enter simulation mode Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 46

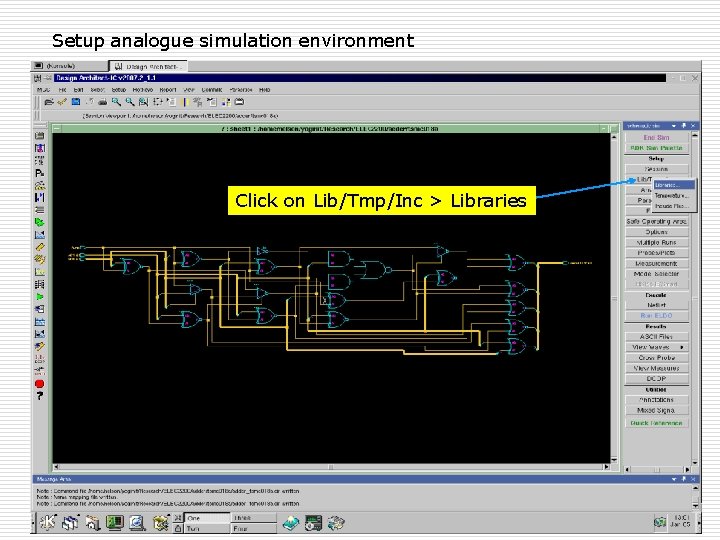

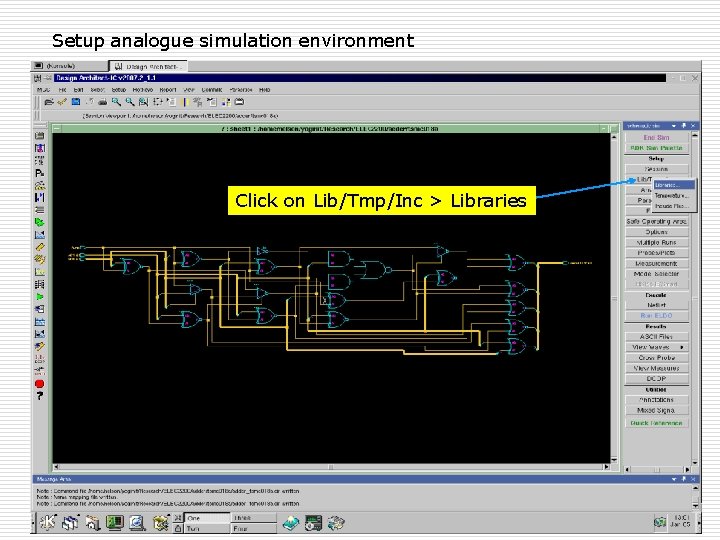

Setup analogue simulation environment Click on Lib/Tmp/Inc > Libraries Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 47

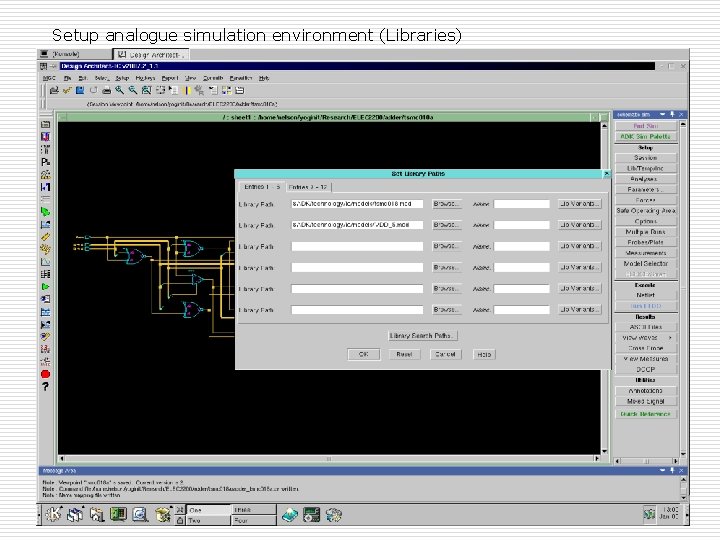

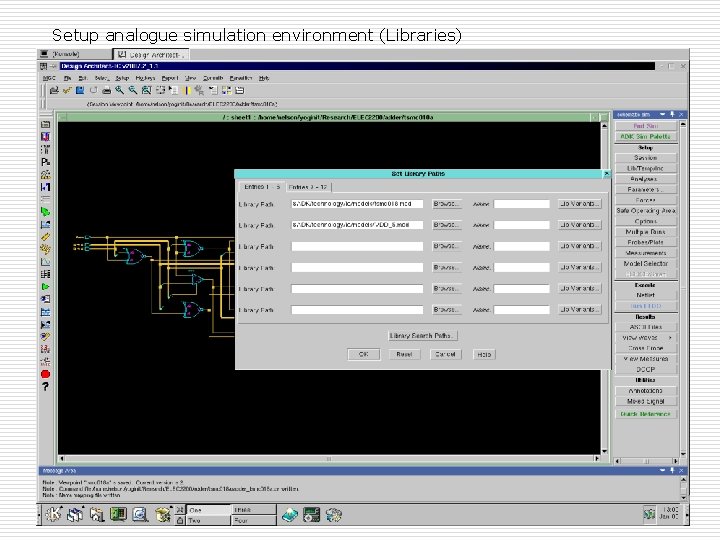

Setup analogue simulation environment (Libraries) Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 48

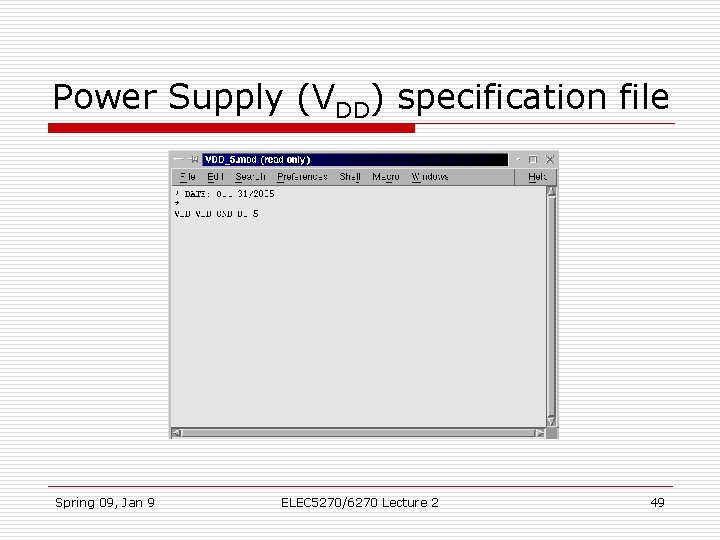

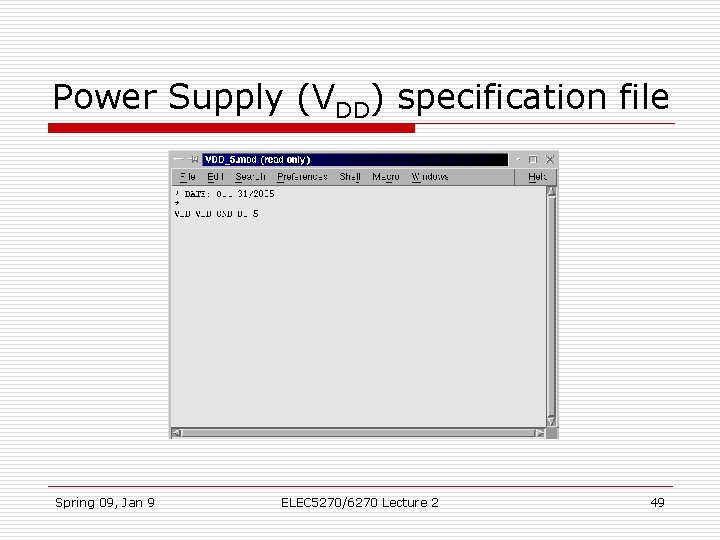

Power Supply (VDD) specification file Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 49

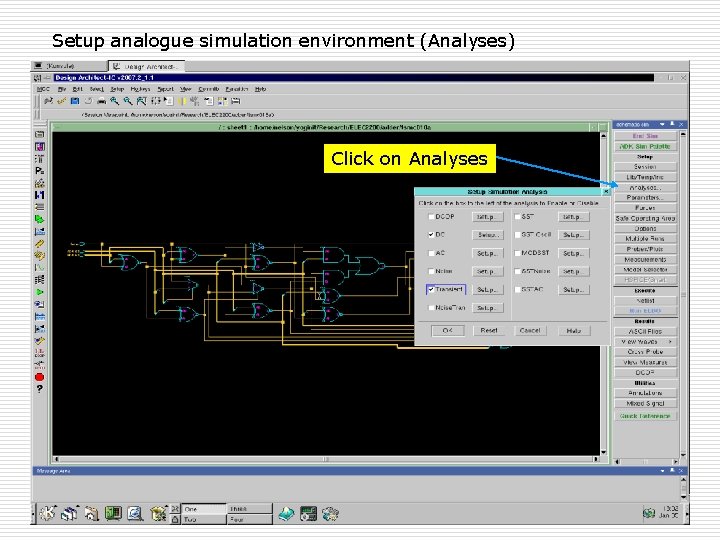

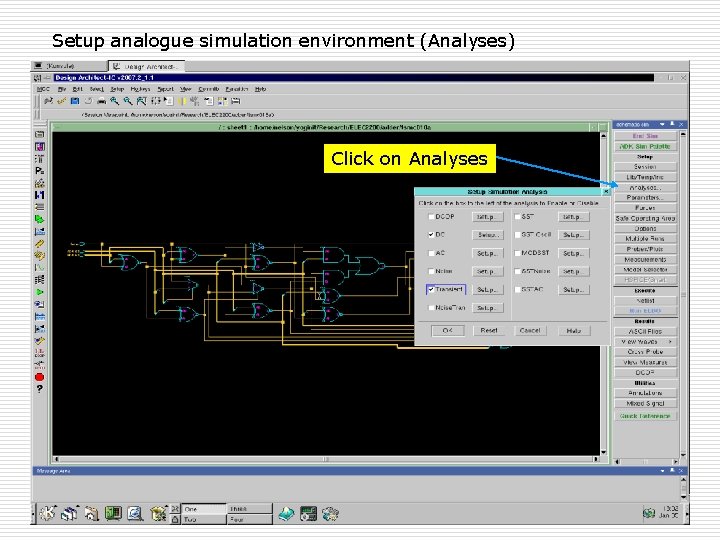

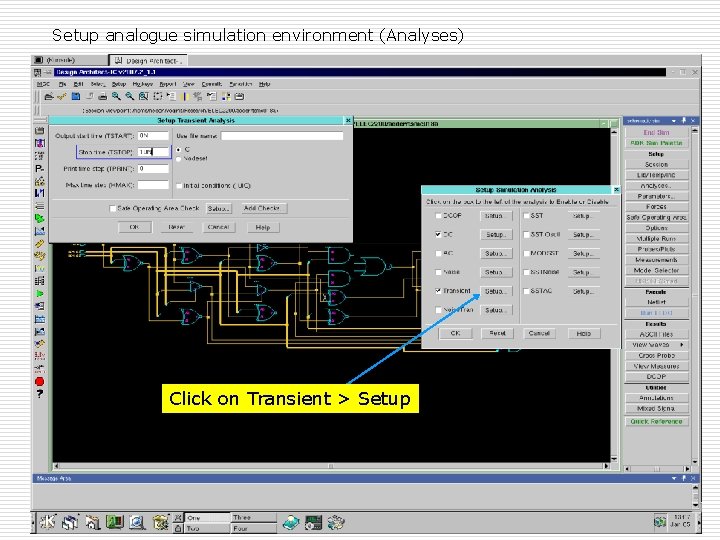

Setup analogue simulation environment (Analyses) Click on Analyses Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 50

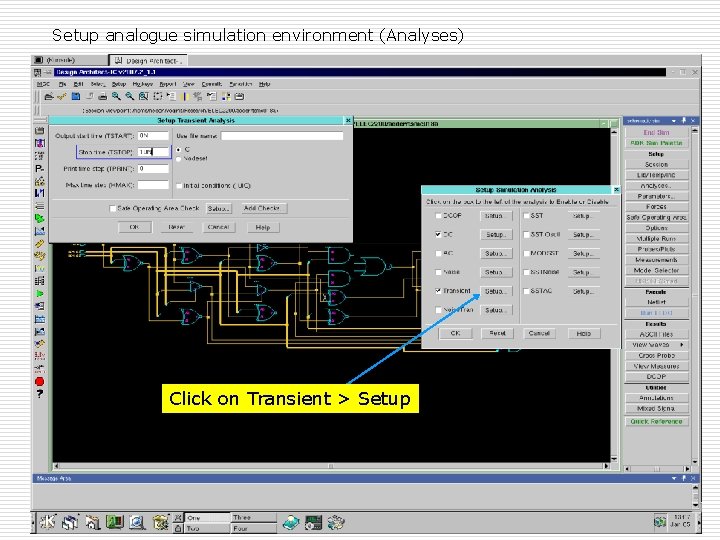

Setup analogue simulation environment (Analyses) Click on Transient > Setup Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 51

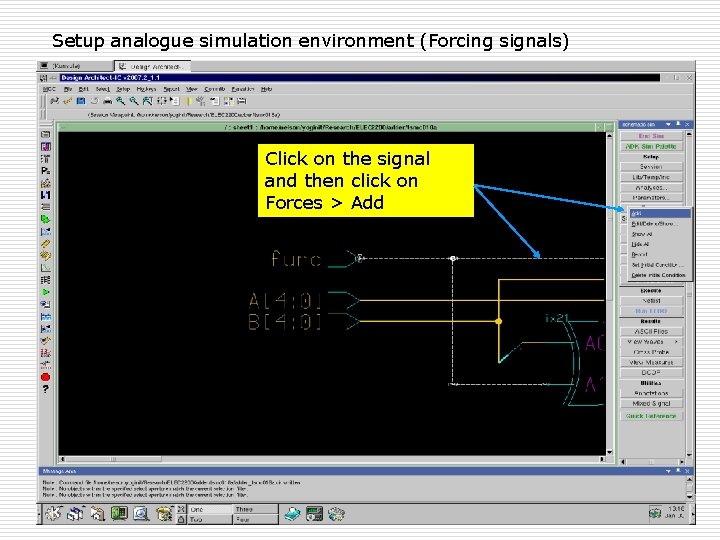

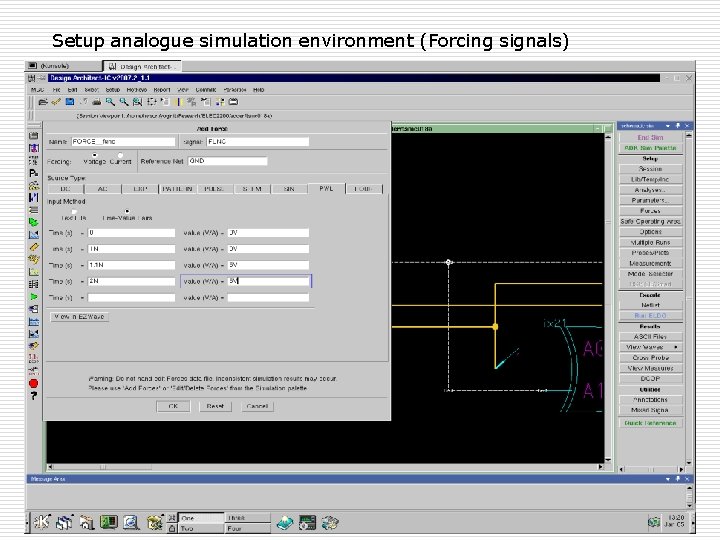

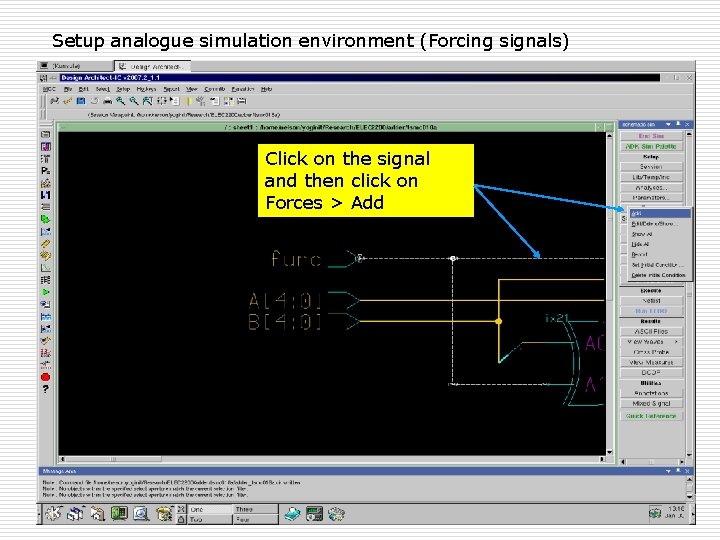

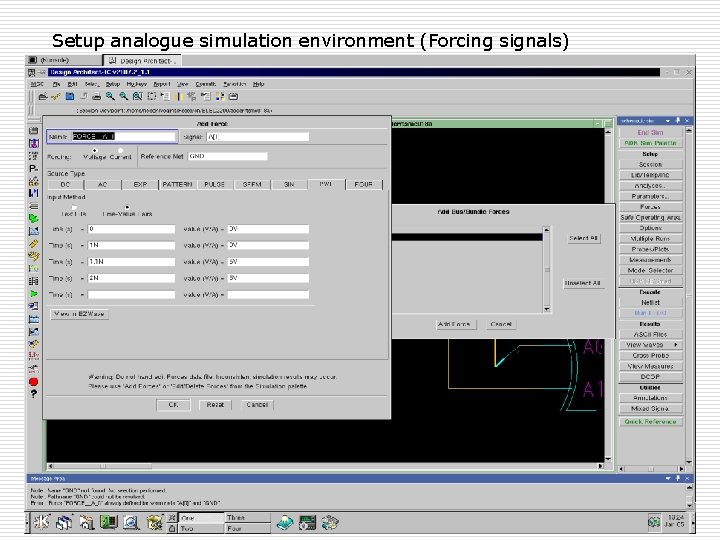

Setup analogue simulation environment (Forcing signals) Click on the signal and then click on Forces > Add Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 52

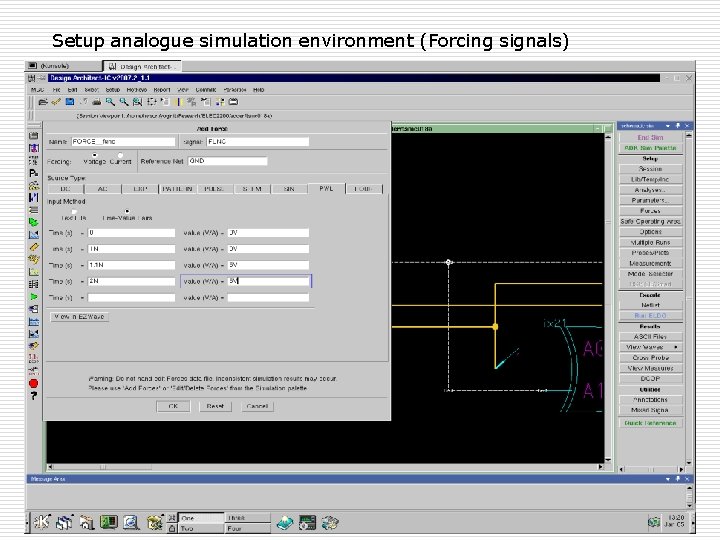

Setup analogue simulation environment (Forcing signals) Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 53

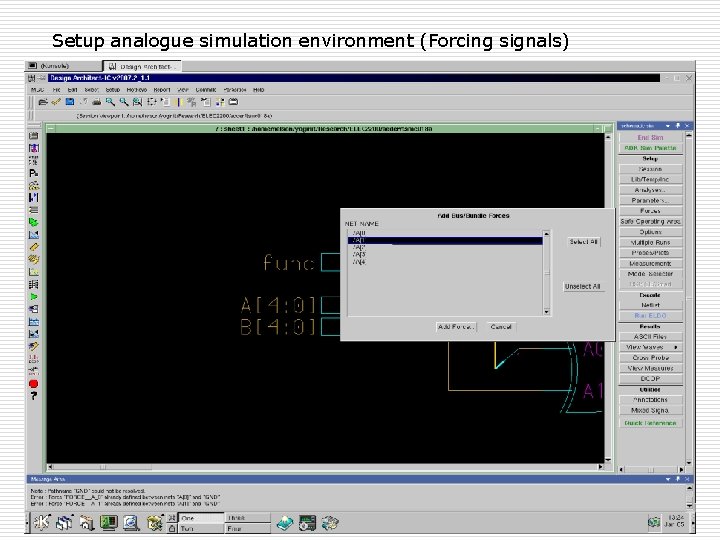

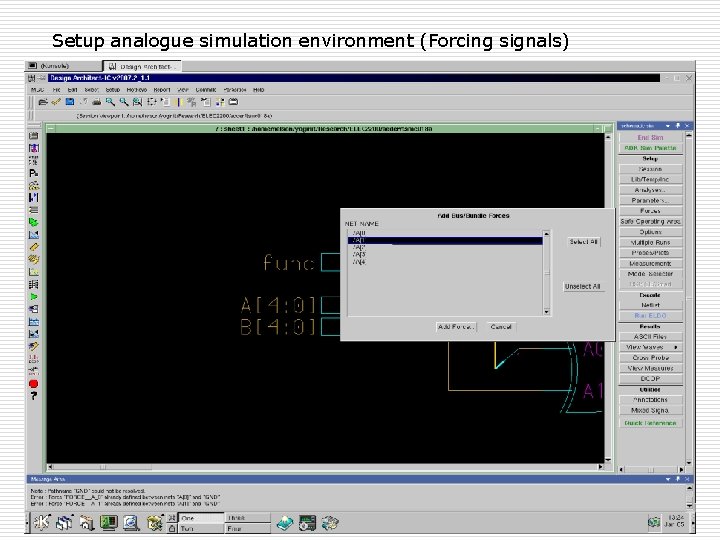

Setup analogue simulation environment (Forcing signals) Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 54

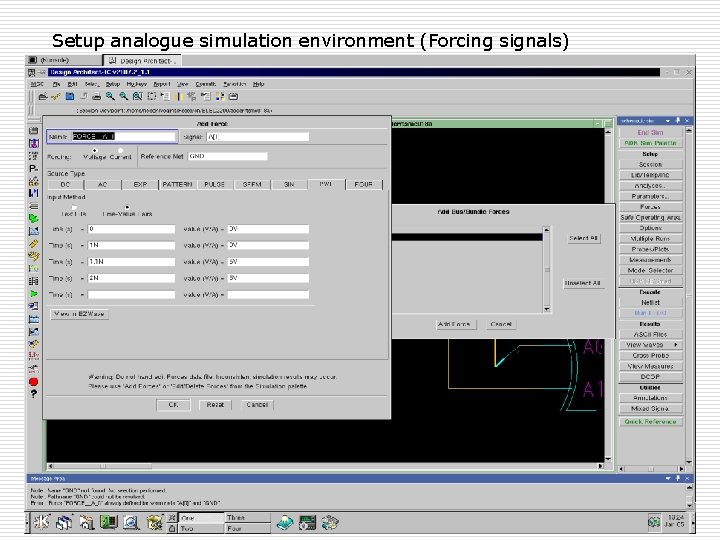

Setup analogue simulation environment (Forcing signals) Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 55

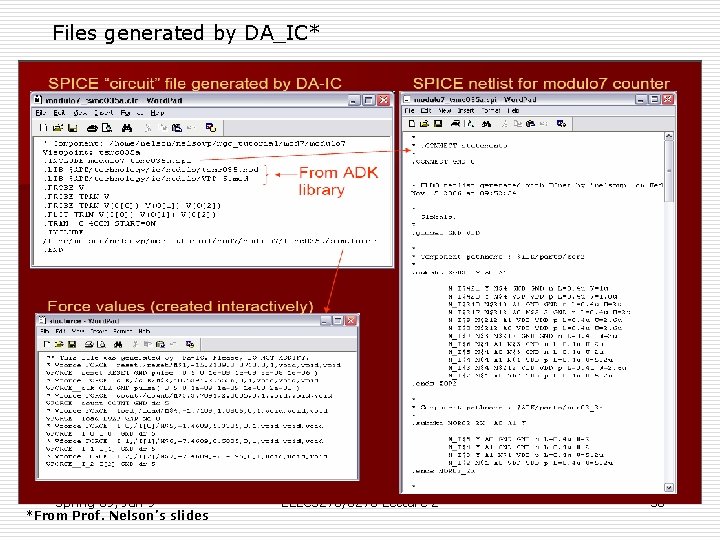

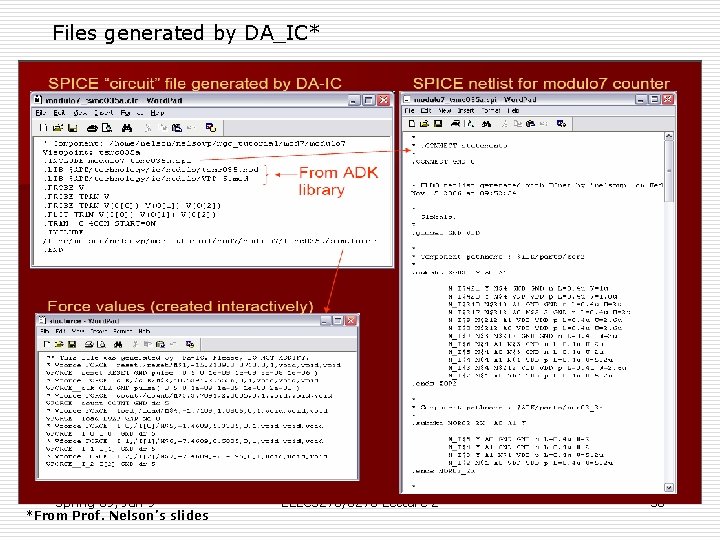

Files generated by DA_IC* Spring 09, Jan 9 *From Prof. Nelson’s slides ELEC 5270/6270 Lecture 2 56

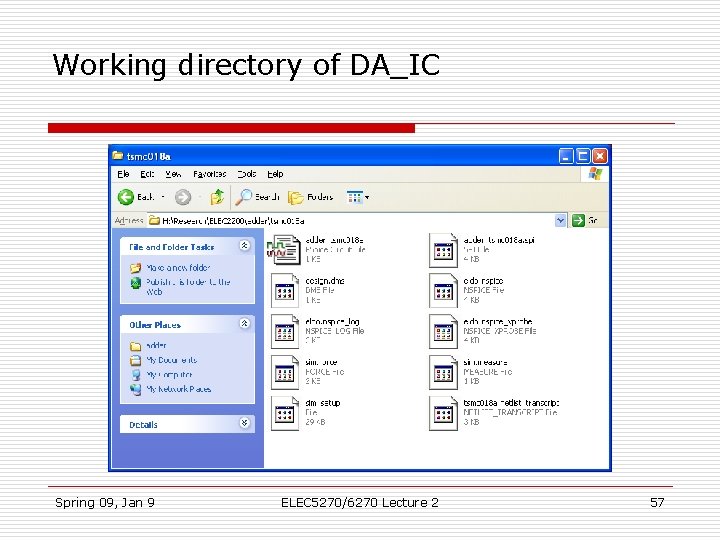

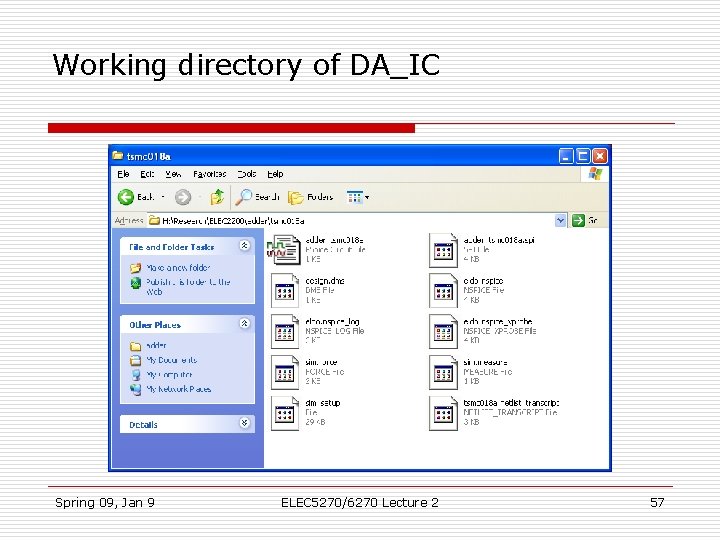

Working directory of DA_IC Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 57

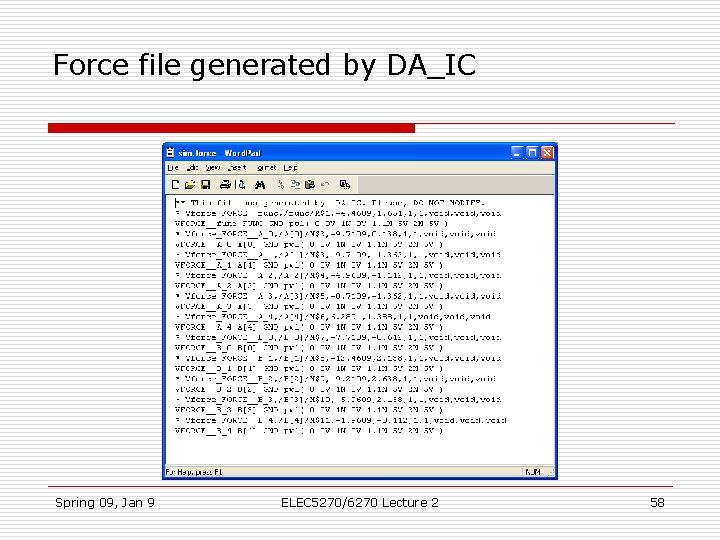

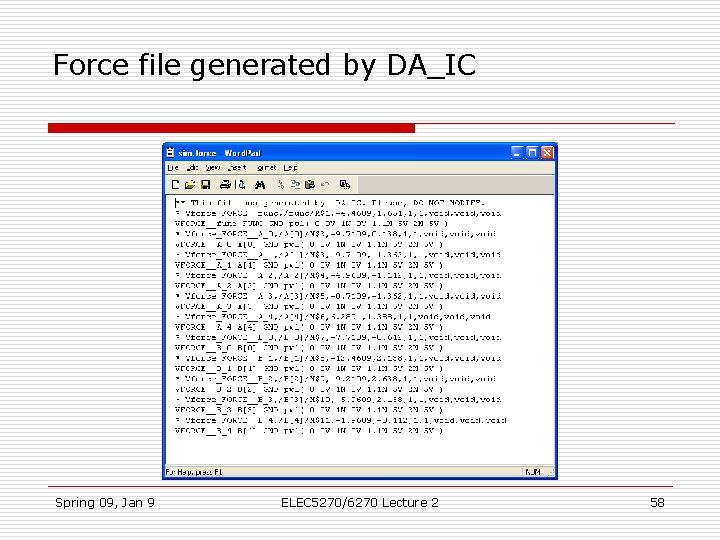

Force file generated by DA_IC Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 58

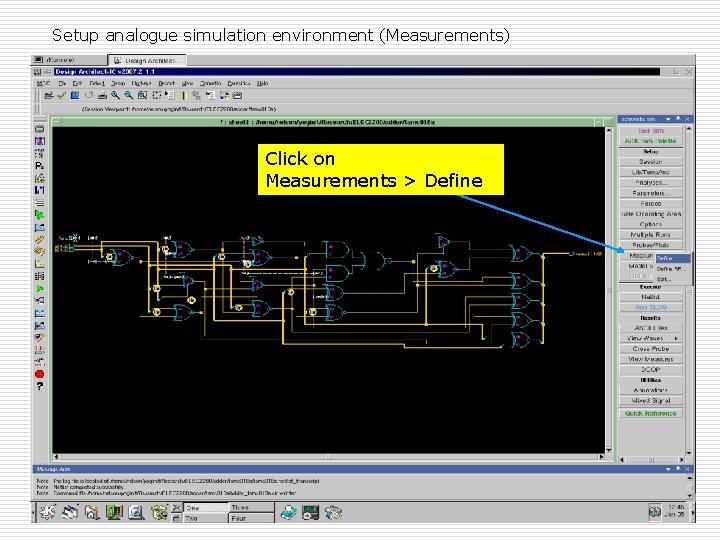

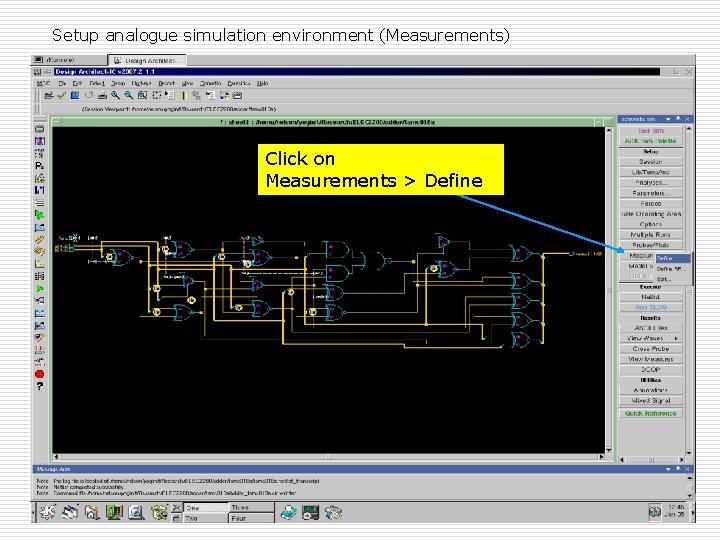

Setup analogue simulation environment (Measurements) Click on Measurements > Define Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 59

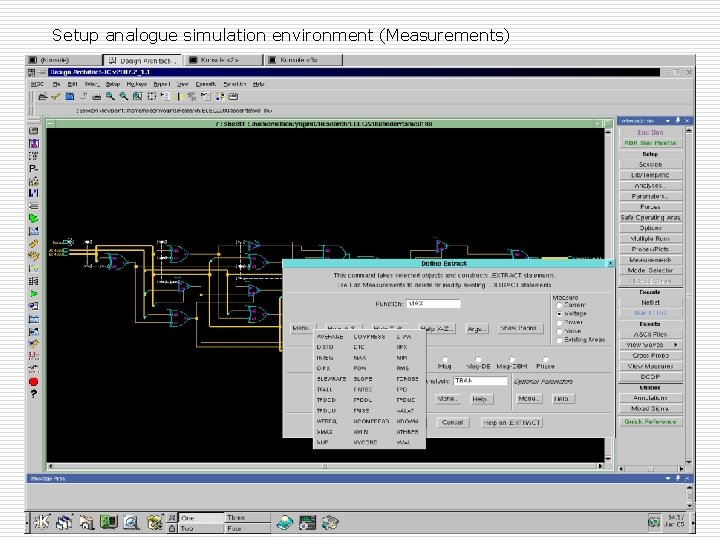

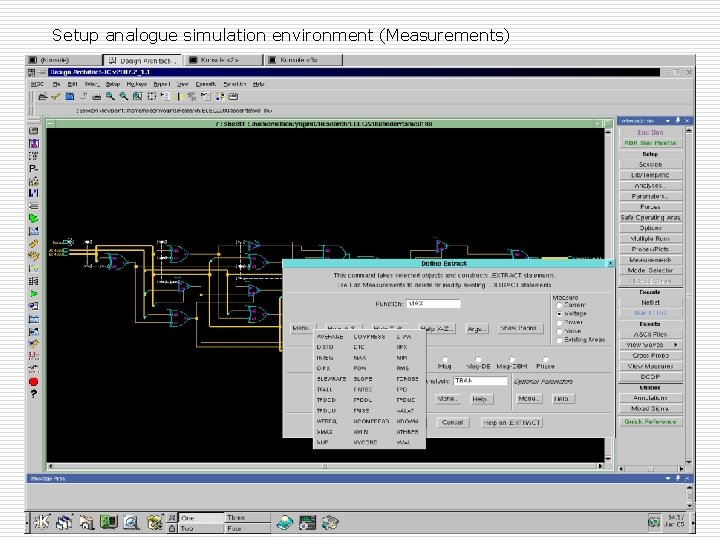

Setup analogue simulation environment (Measurements) Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 60

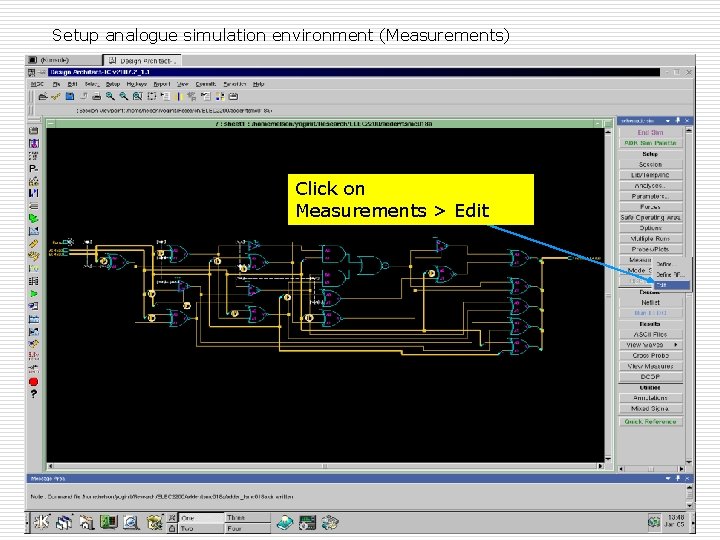

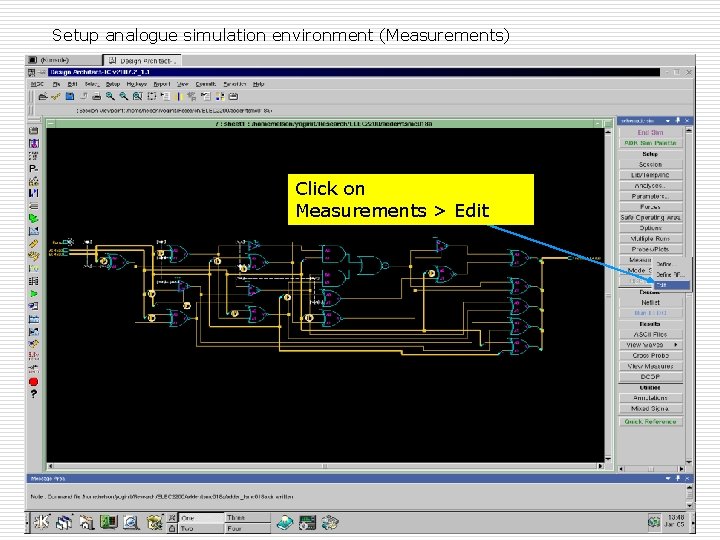

Setup analogue simulation environment (Measurements) Click on Measurements > Edit Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 61

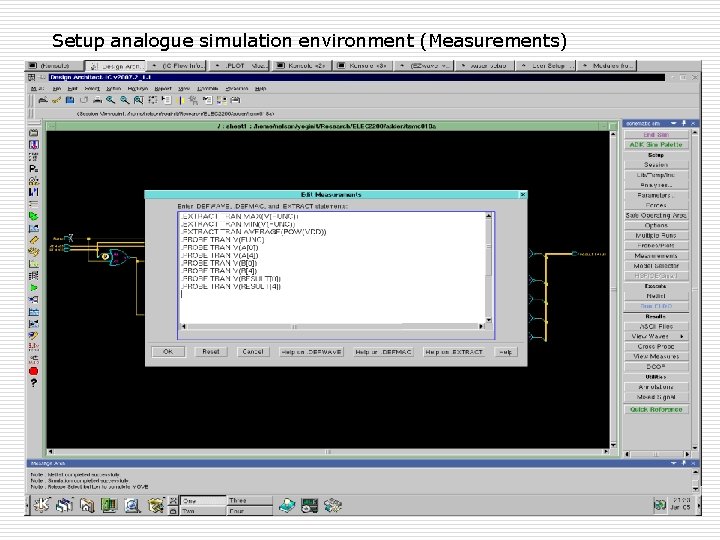

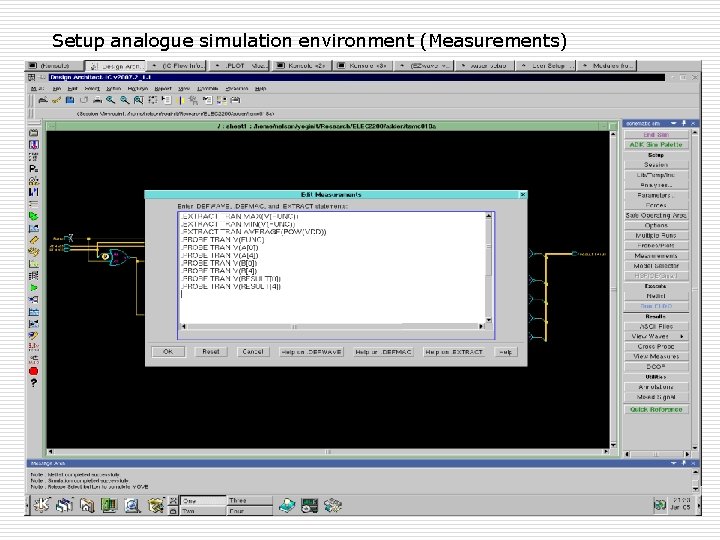

Setup analogue simulation environment (Measurements) Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 62

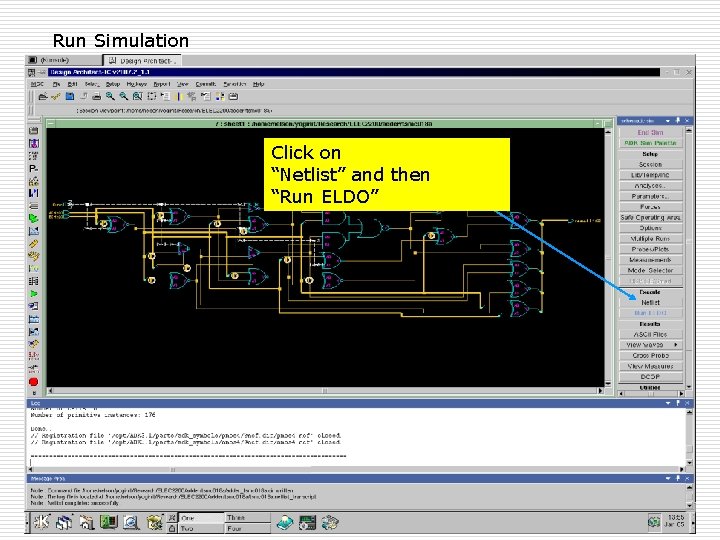

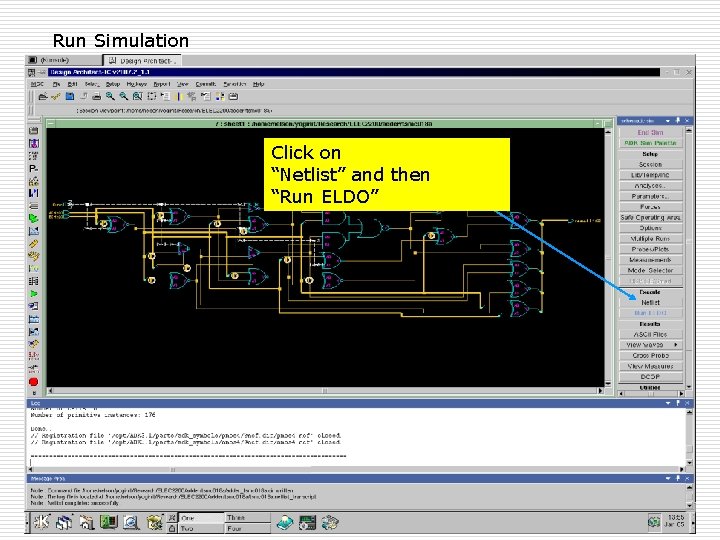

Run Simulation Click on “Netlist” and then “Run ELDO” Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 63

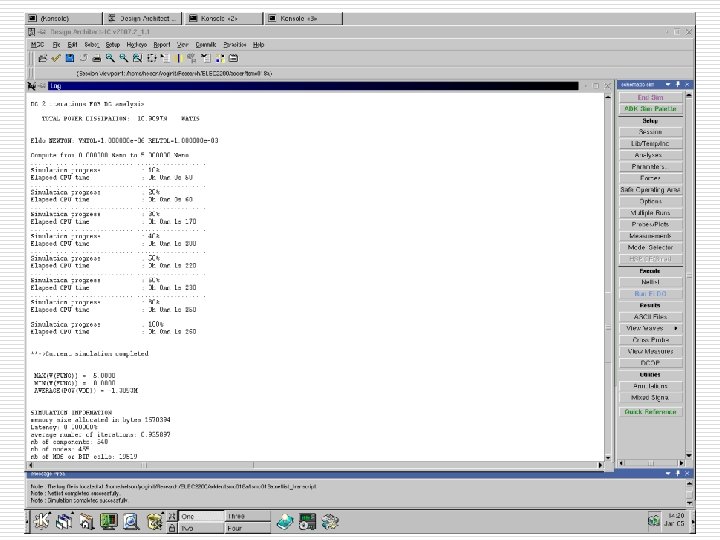

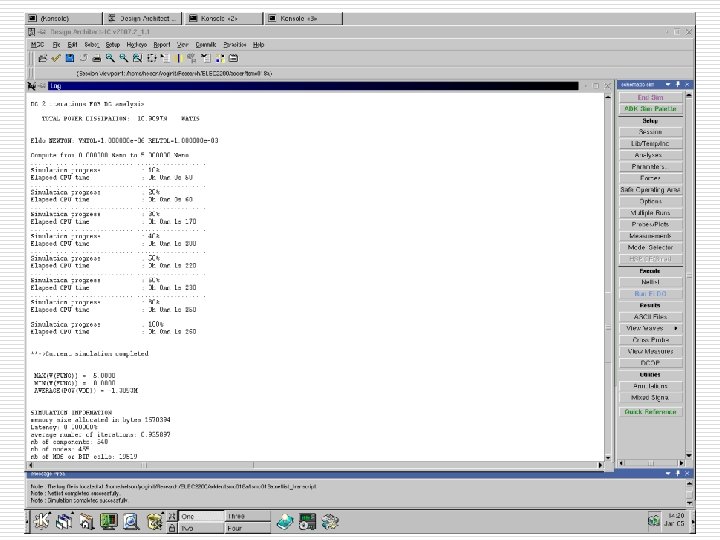

Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 64

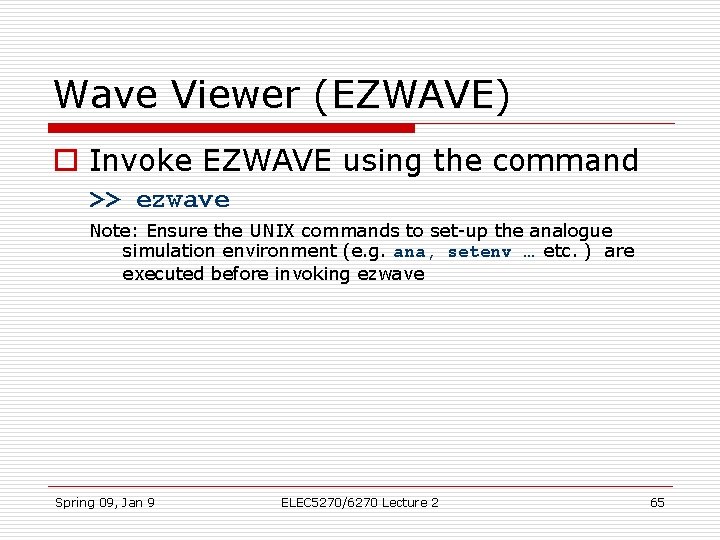

Wave Viewer (EZWAVE) o Invoke EZWAVE using the command >> ezwave Note: Ensure the UNIX commands to set-up the analogue simulation environment (e. g. ana, setenv … etc. ) are executed before invoking ezwave Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 65

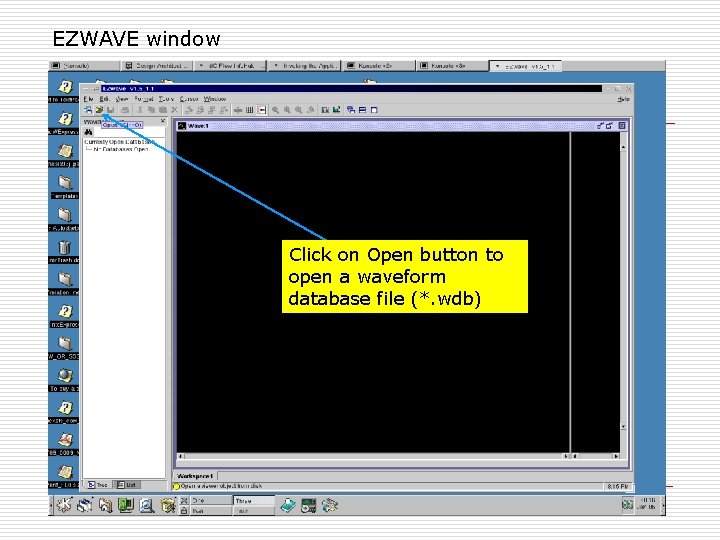

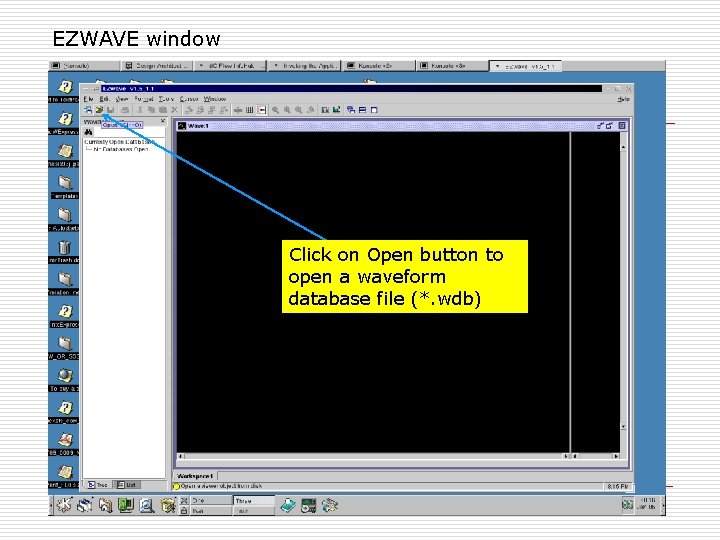

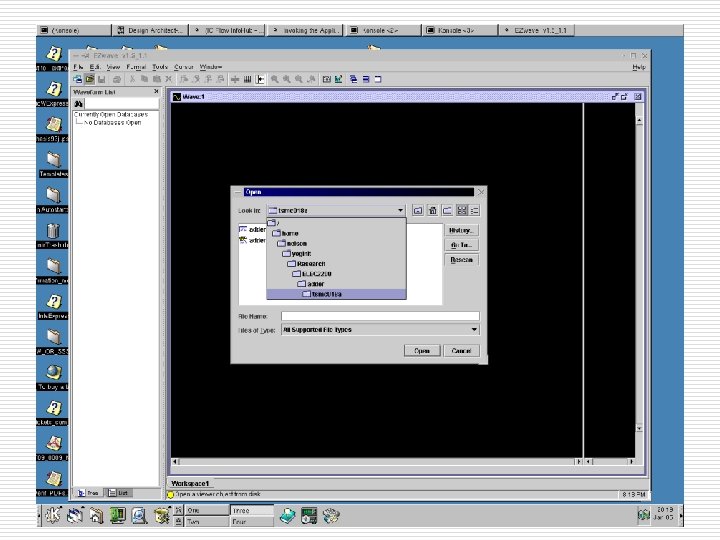

EZWAVE window Click on Open button to open a waveform database file (*. wdb) Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 66

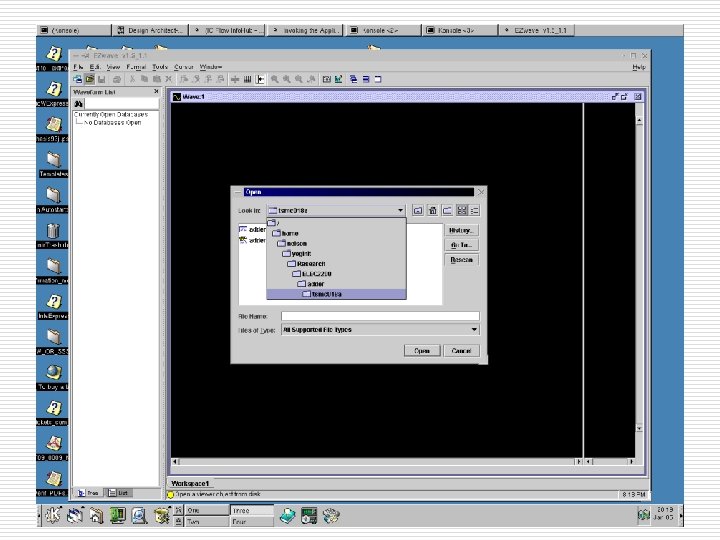

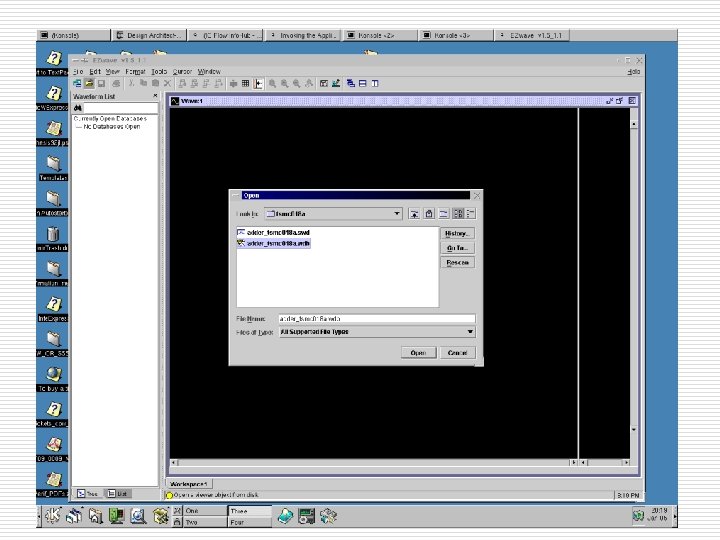

Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 67

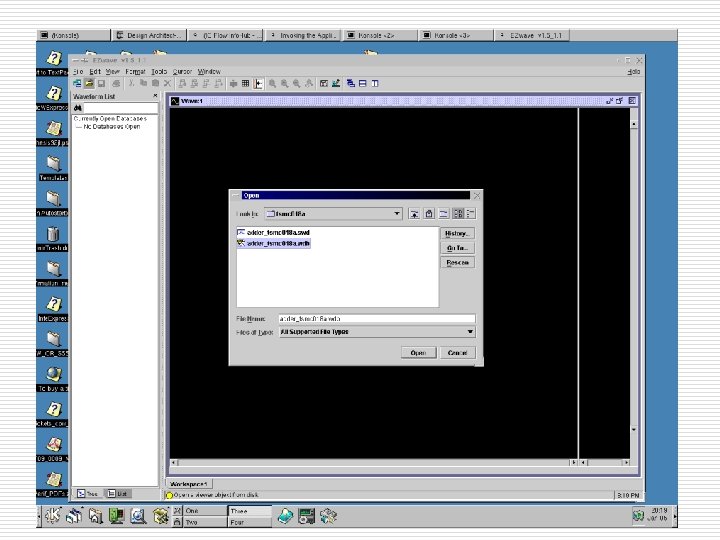

Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 68

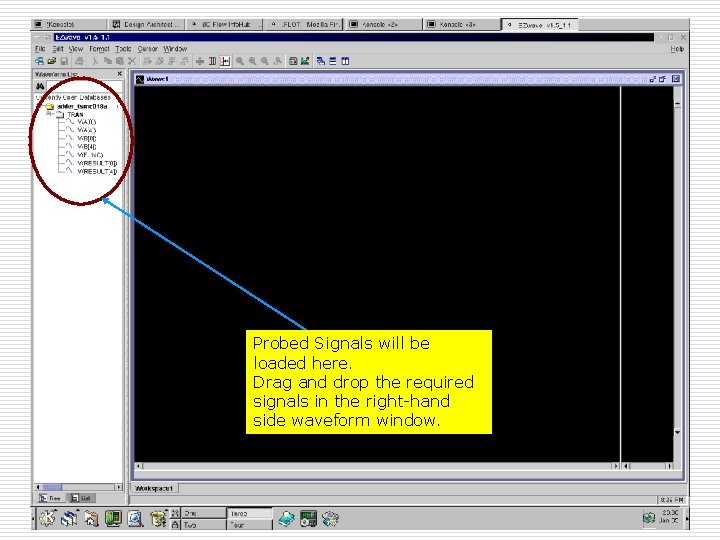

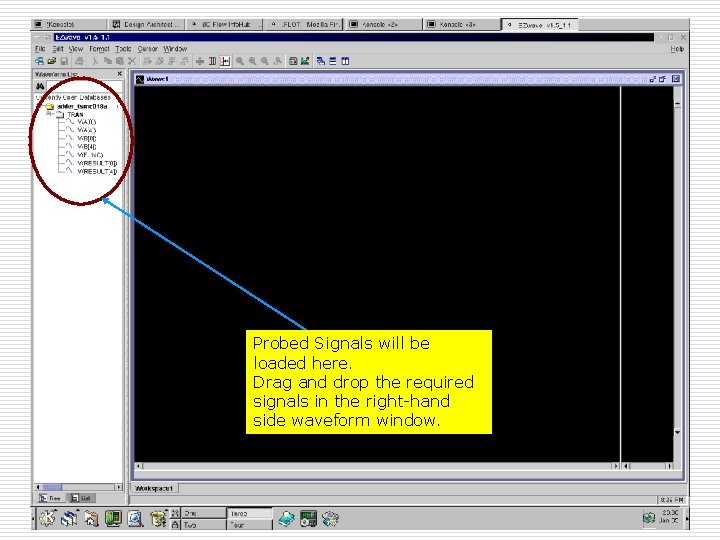

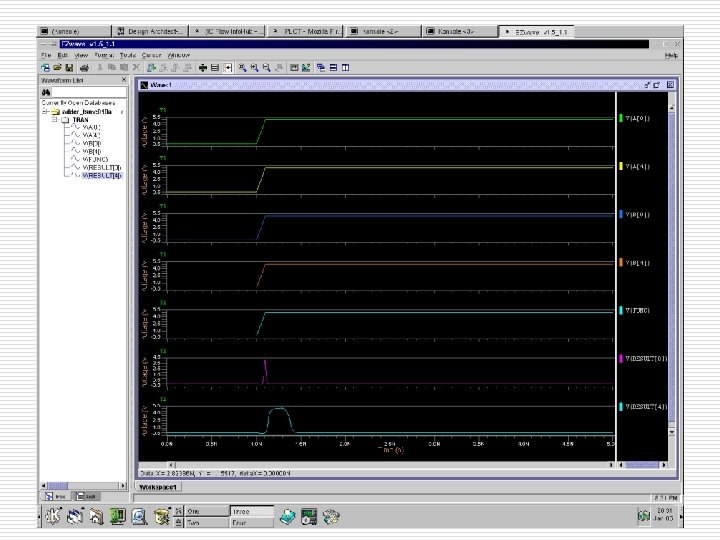

Probed Signals will be loaded here. Drag and drop the required signals in the right-hand side waveform window. Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 69

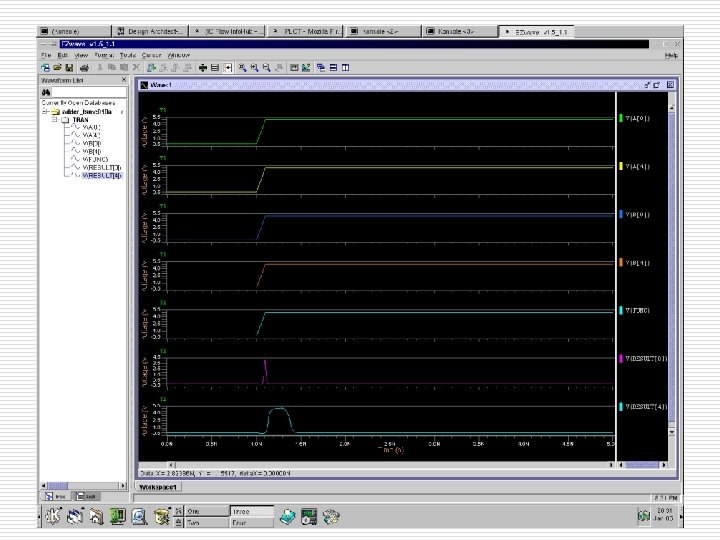

Spring 09, Jan 9 ELEC 5270/6270 Lecture 2 70