ELEC 516 VLSI System Design and Design Automation

![Example From [Horowitz] 17 ELEC 516/10 Lecture 11 Example From [Horowitz] 17 ELEC 516/10 Lecture 11](https://slidetodoc.com/presentation_image_h2/0304c7db51ecc0f0c781874143e180b7/image-17.jpg)

- Slides: 43

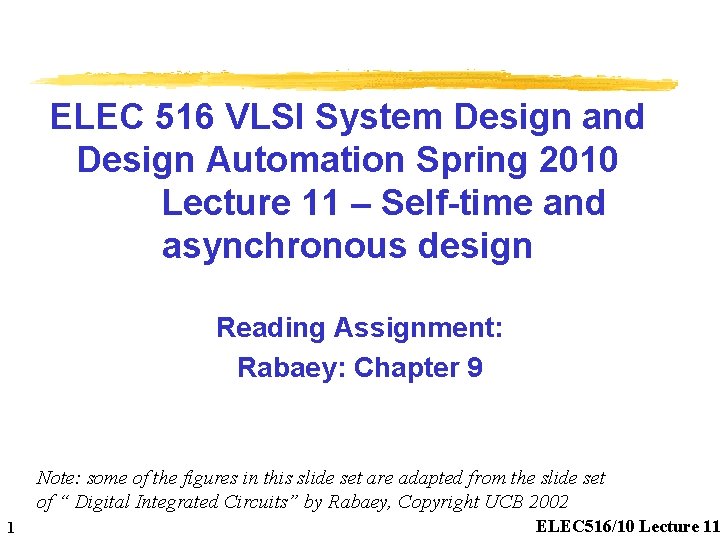

ELEC 516 VLSI System Design and Design Automation Spring 2010 Lecture 11 – Self-time and asynchronous design Reading Assignment: Rabaey: Chapter 9 Note: some of the figures in this slide set are adapted from the slide set of “ Digital Integrated Circuits” by Rabaey, Copyright UCB 2002 1 ELEC 516/10 Lecture 11

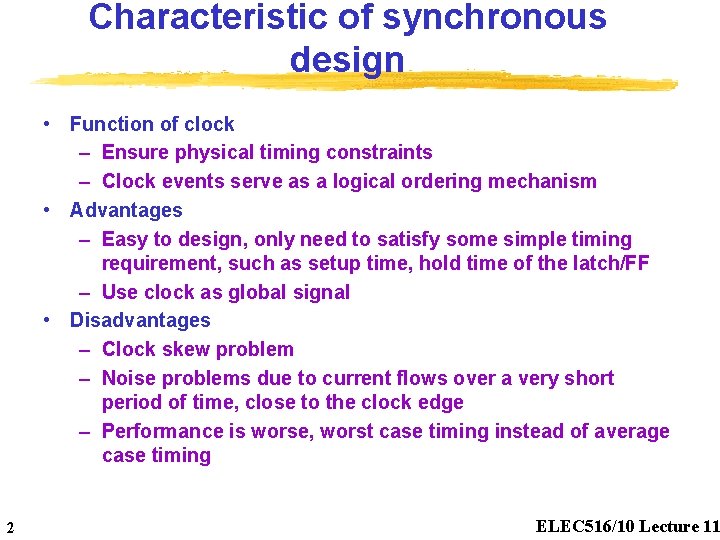

Characteristic of synchronous design • Function of clock – Ensure physical timing constraints – Clock events serve as a logical ordering mechanism • Advantages – Easy to design, only need to satisfy some simple timing requirement, such as setup time, hold time of the latch/FF – Use clock as global signal • Disadvantages – Clock skew problem – Noise problems due to current flows over a very short period of time, close to the clock edge – Performance is worse, worst case timing instead of average case timing 2 ELEC 516/10 Lecture 11

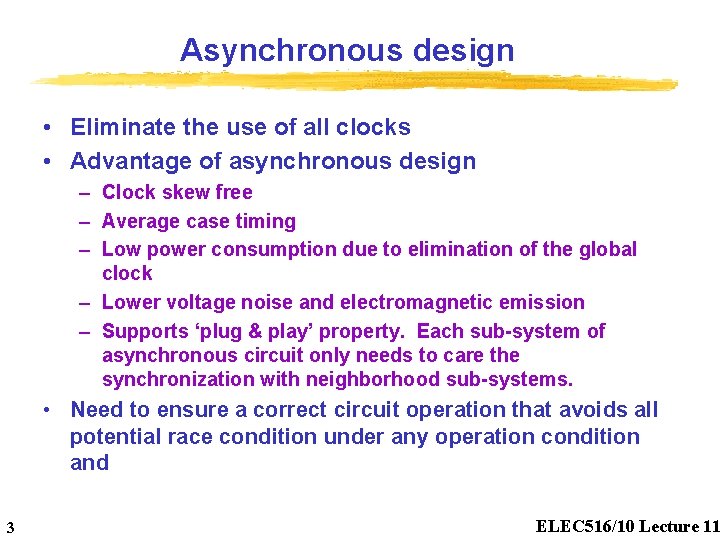

Asynchronous design • Eliminate the use of all clocks • Advantage of asynchronous design – Clock skew free – Average case timing – Low power consumption due to elimination of the global clock – Lower voltage noise and electromagnetic emission – Supports ‘plug & play’ property. Each sub-system of asynchronous circuit only needs to care the synchronization with neighborhood sub-systems. • Need to ensure a correct circuit operation that avoids all potential race condition under any operation condition and 3 ELEC 516/10 Lecture 11

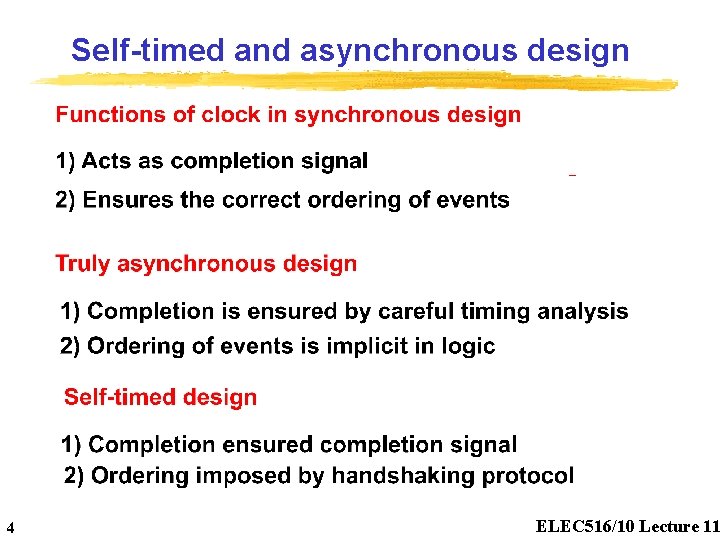

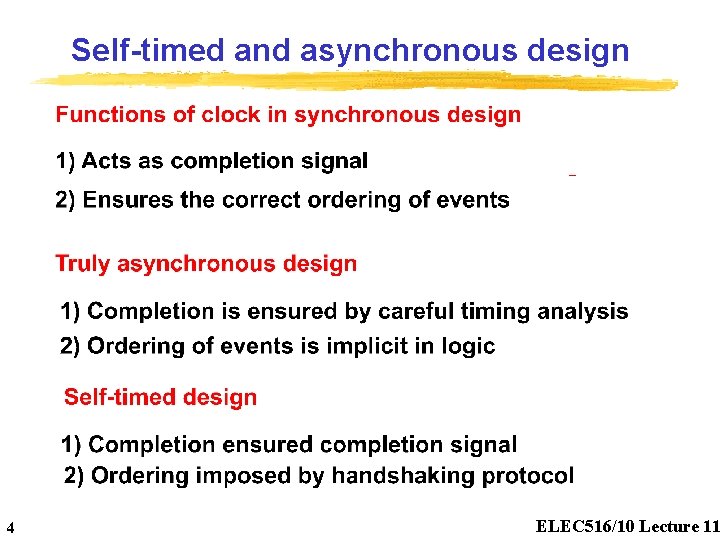

Self-timed and asynchronous design 4 ELEC 516/10 Lecture 11

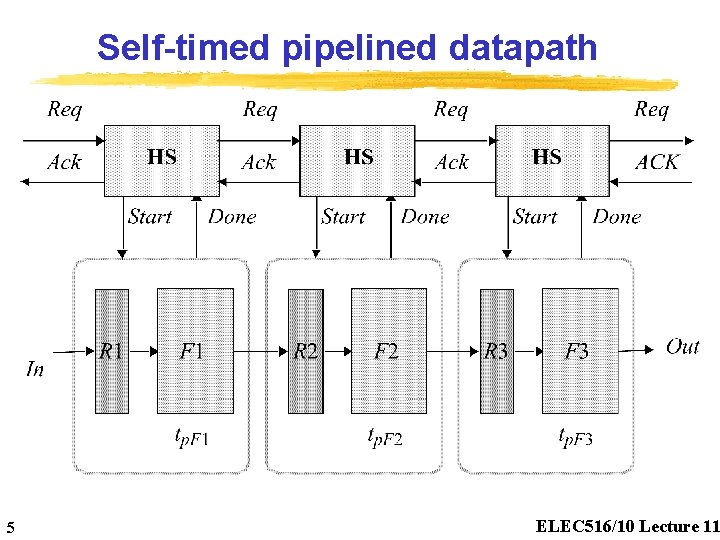

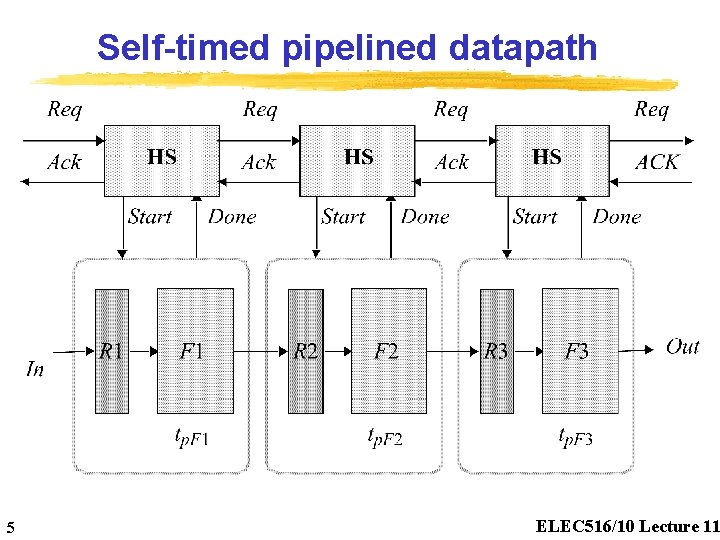

Self-timed pipelined datapath 5 ELEC 516/10 Lecture 11

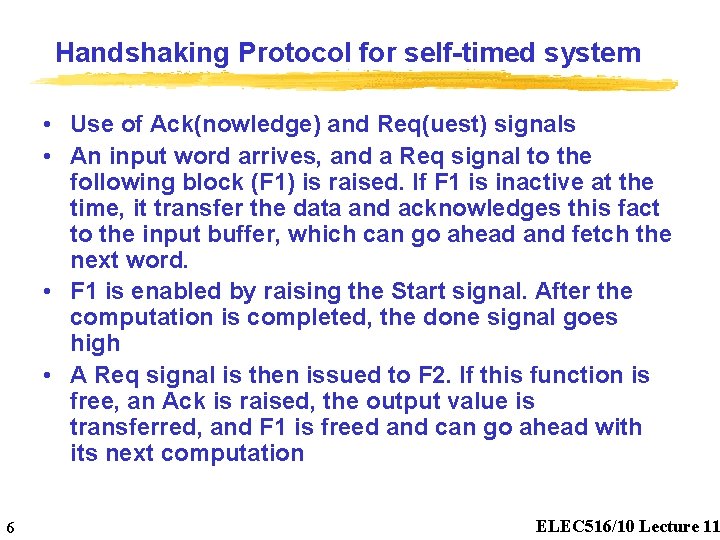

Handshaking Protocol for self-timed system • Use of Ack(nowledge) and Req(uest) signals • An input word arrives, and a Req signal to the following block (F 1) is raised. If F 1 is inactive at the time, it transfer the data and acknowledges this fact to the input buffer, which can go ahead and fetch the next word. • F 1 is enabled by raising the Start signal. After the computation is completed, the done signal goes high • A Req signal is then issued to F 2. If this function is free, an Ack is raised, the output value is transferred, and F 1 is freed and can go ahead with its next computation 6 ELEC 516/10 Lecture 11

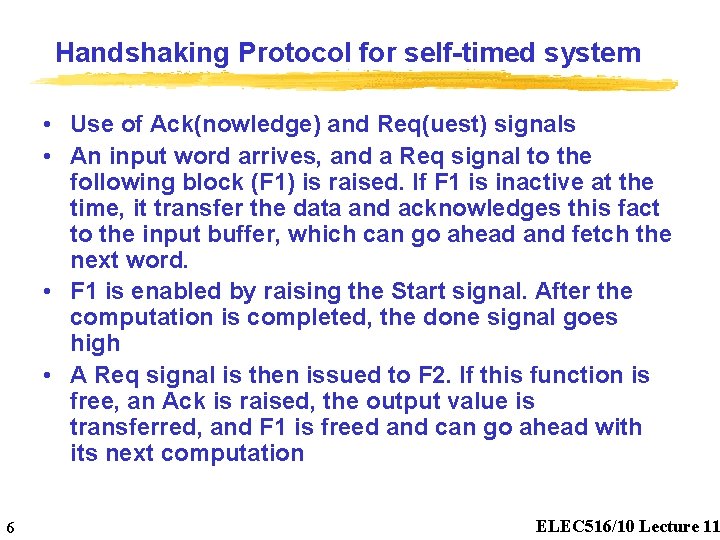

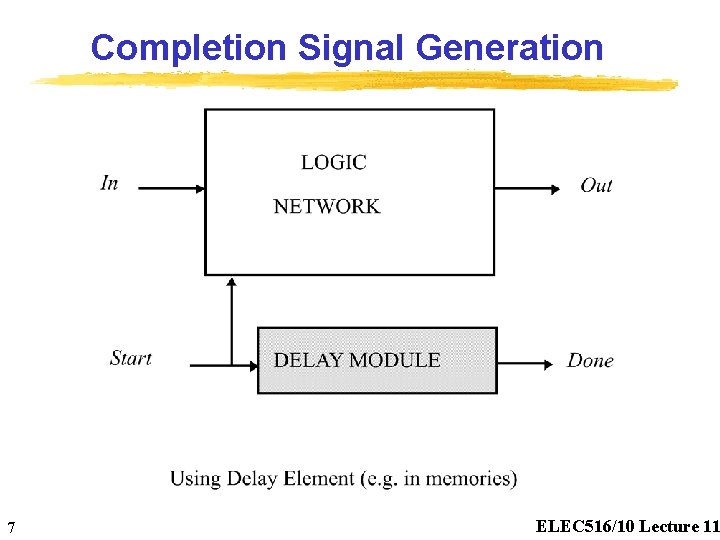

Completion Signal Generation 7 ELEC 516/10 Lecture 11

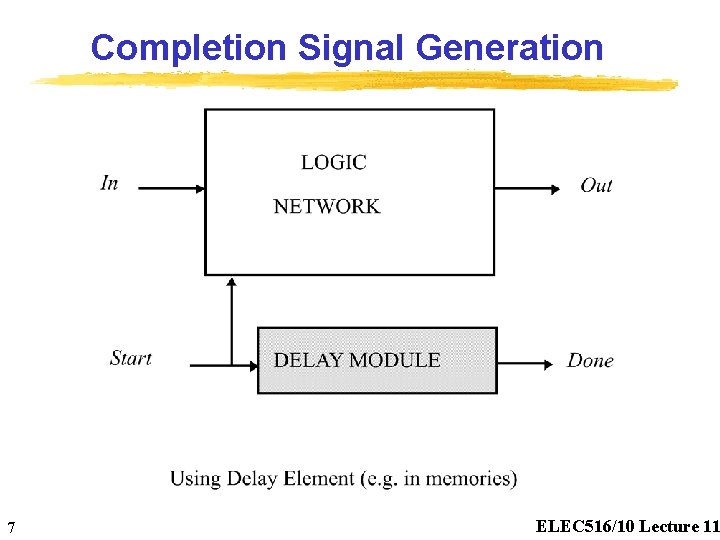

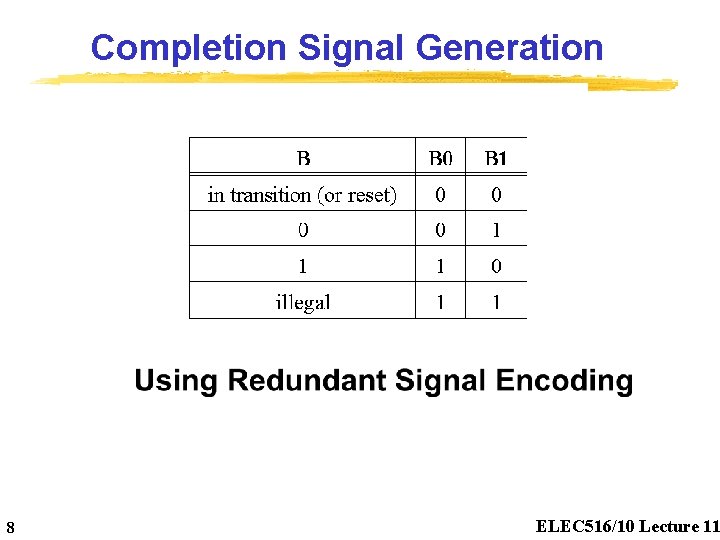

Completion Signal Generation 8 ELEC 516/10 Lecture 11

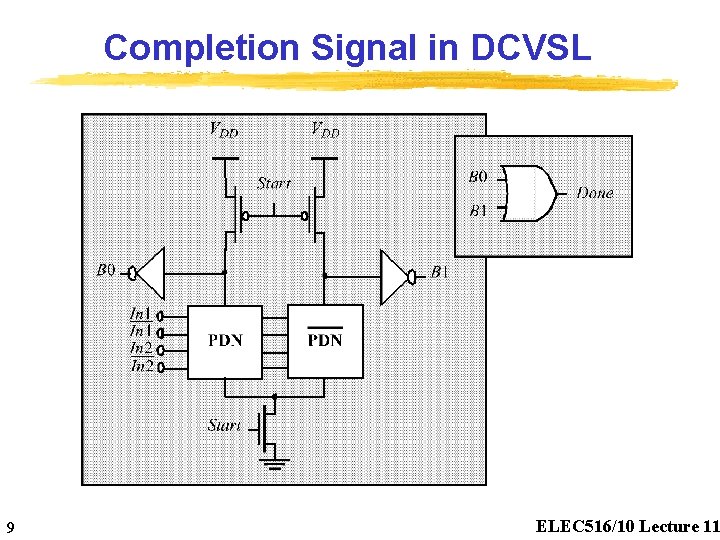

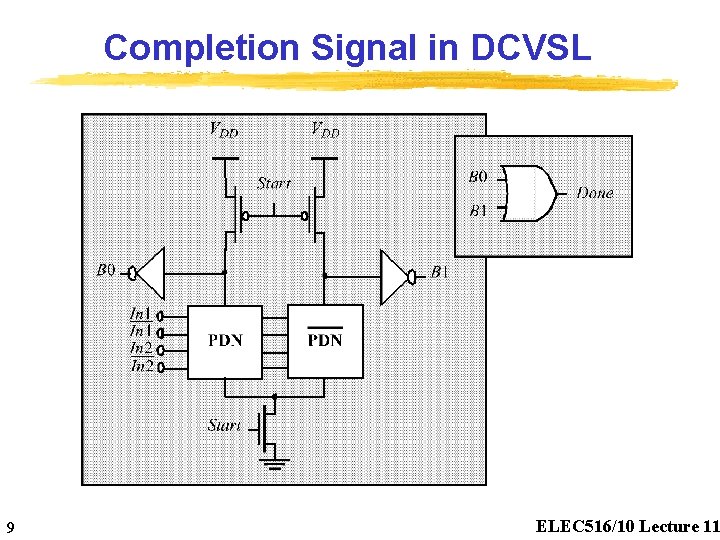

Completion Signal in DCVSL 9 ELEC 516/10 Lecture 11

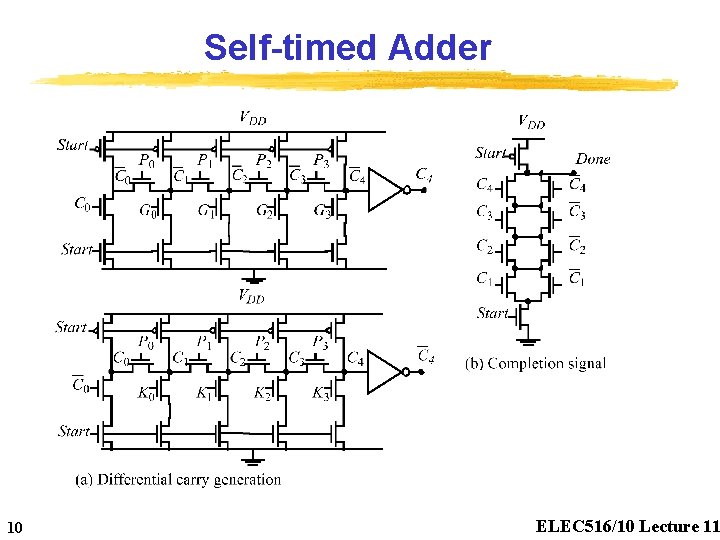

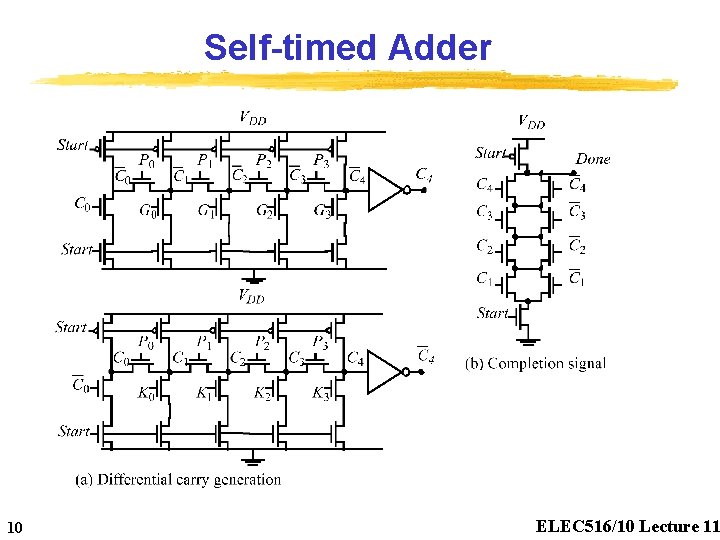

Self-timed Adder 10 ELEC 516/10 Lecture 11

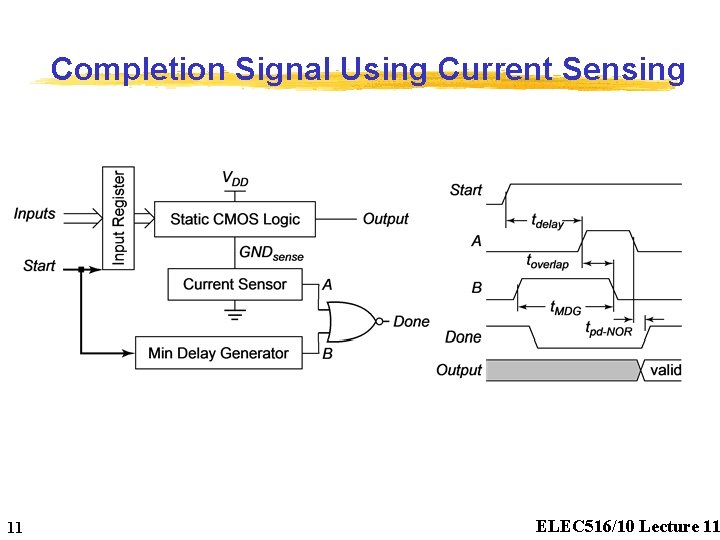

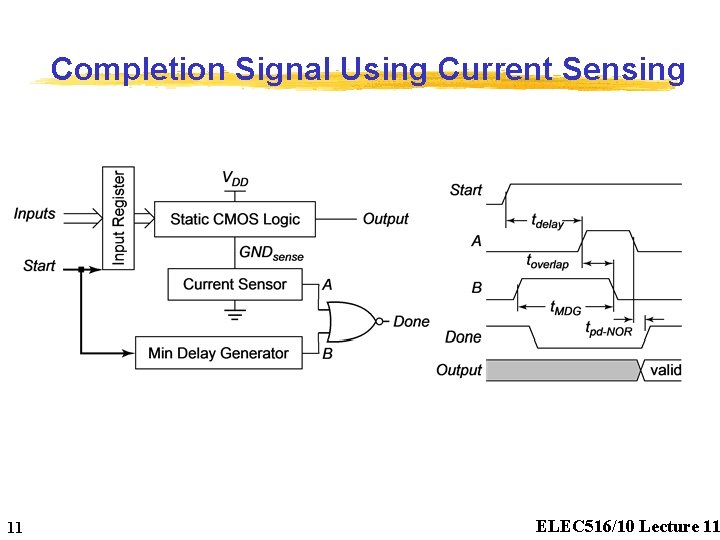

Completion Signal Using Current Sensing 11 ELEC 516/10 Lecture 11

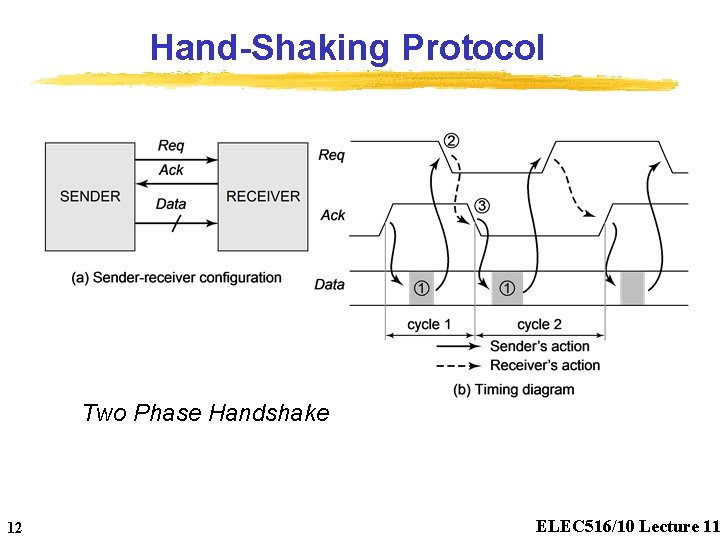

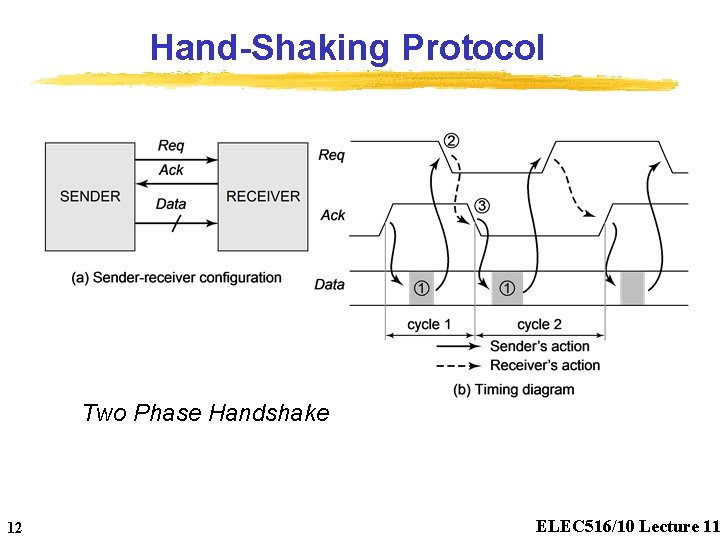

Hand-Shaking Protocol Two Phase Handshake 12 ELEC 516/10 Lecture 11

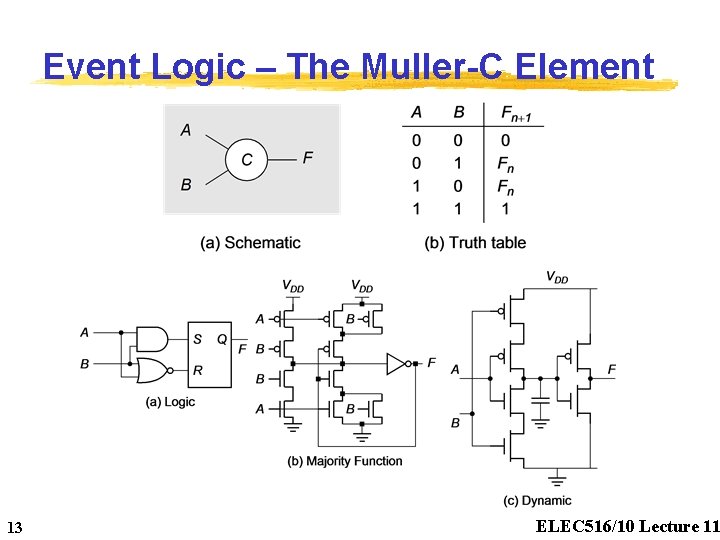

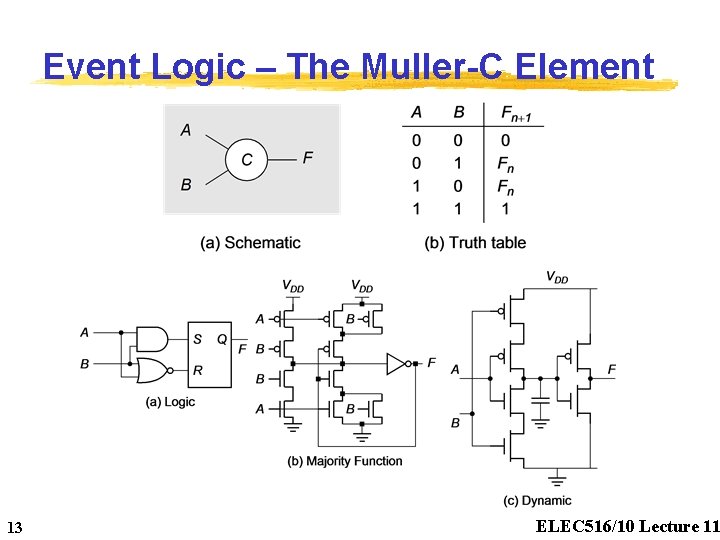

Event Logic – The Muller-C Element 13 ELEC 516/10 Lecture 11

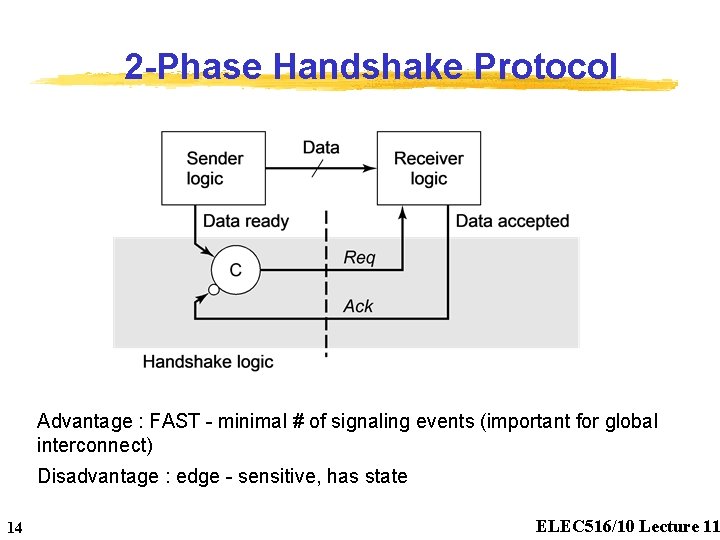

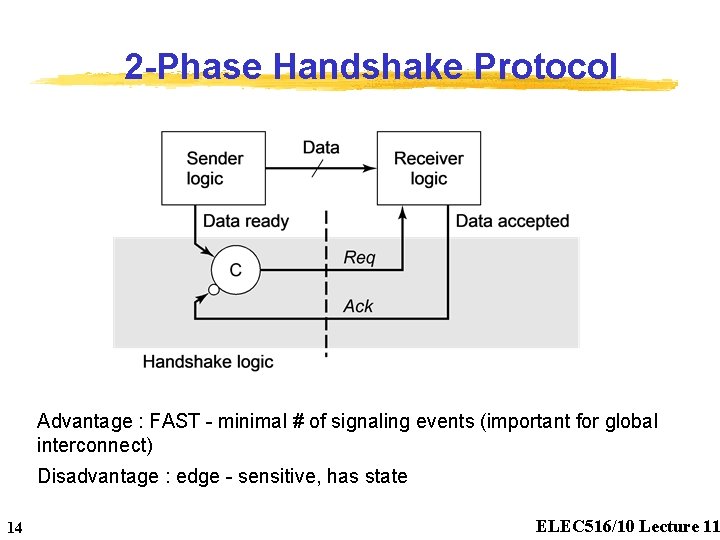

2 -Phase Handshake Protocol Advantage : FAST - minimal # of signaling events (important for global interconnect) Disadvantage : edge - sensitive, has state 14 ELEC 516/10 Lecture 11

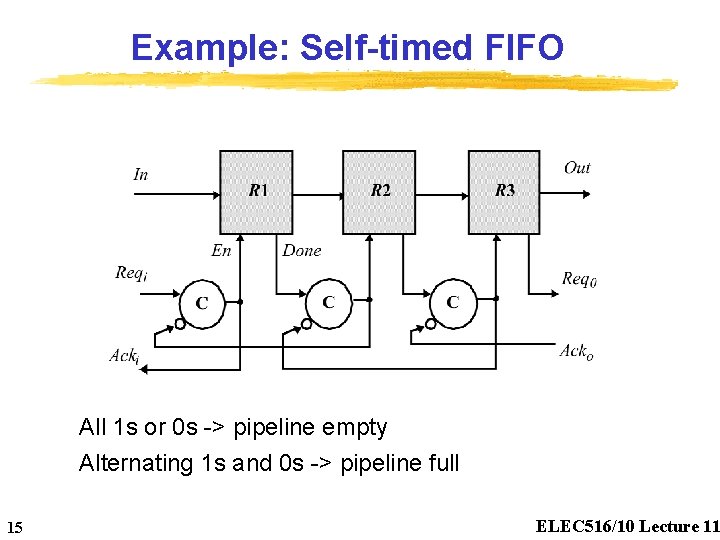

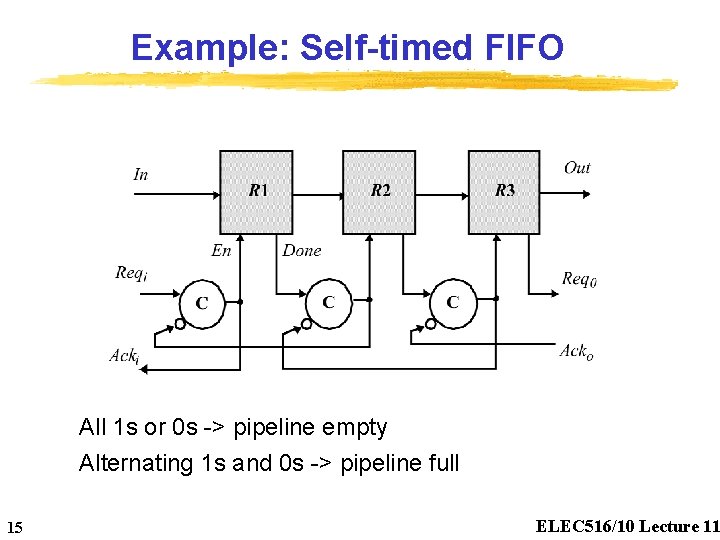

Example: Self-timed FIFO All 1 s or 0 s -> pipeline empty Alternating 1 s and 0 s -> pipeline full 15 ELEC 516/10 Lecture 11

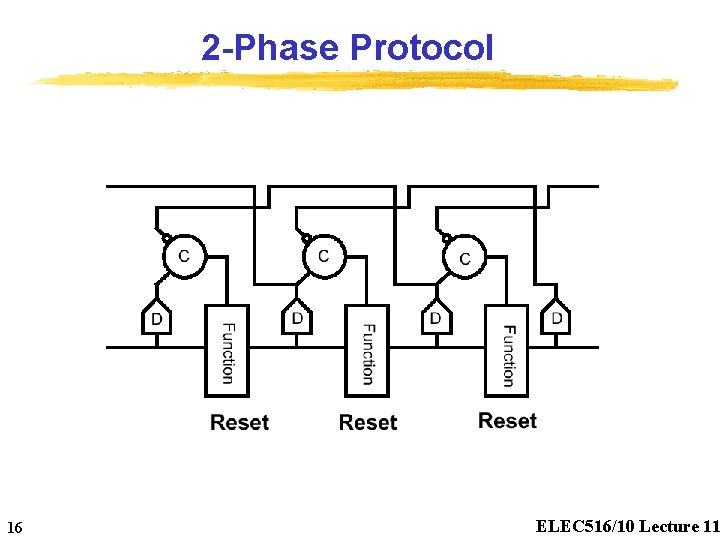

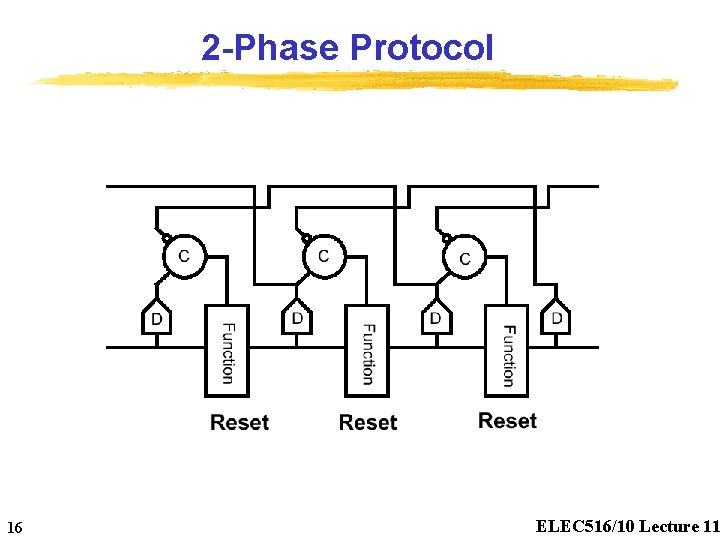

2 -Phase Protocol 16 ELEC 516/10 Lecture 11

![Example From Horowitz 17 ELEC 51610 Lecture 11 Example From [Horowitz] 17 ELEC 516/10 Lecture 11](https://slidetodoc.com/presentation_image_h2/0304c7db51ecc0f0c781874143e180b7/image-17.jpg)

Example From [Horowitz] 17 ELEC 516/10 Lecture 11

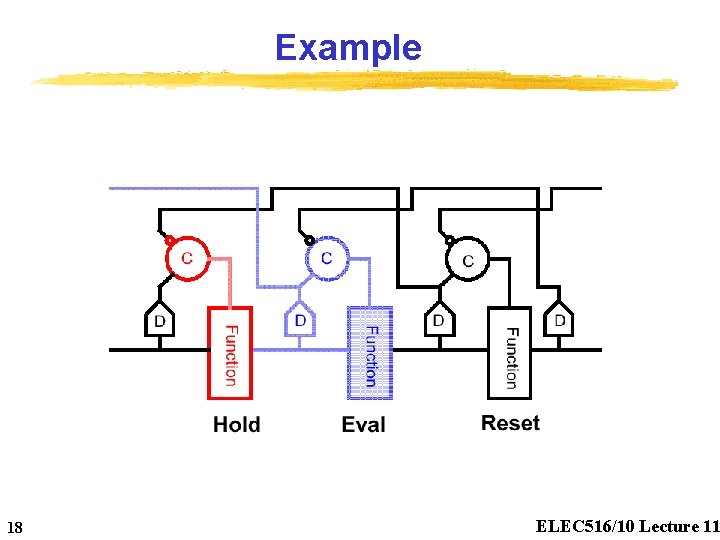

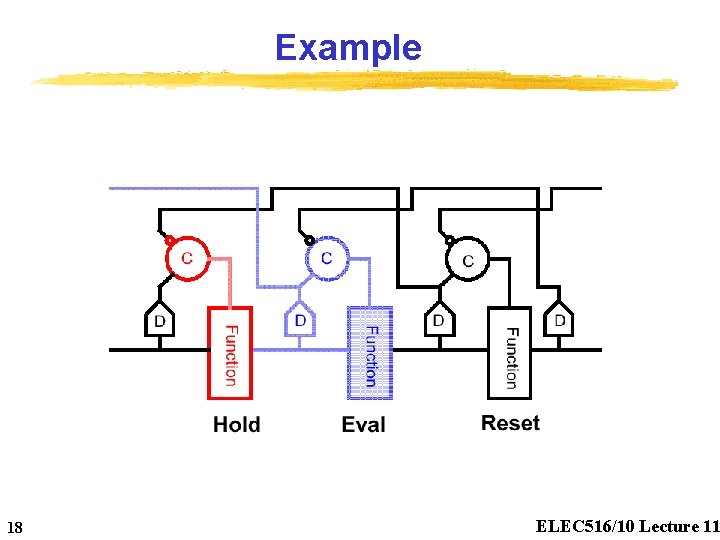

Example 18 ELEC 516/10 Lecture 11

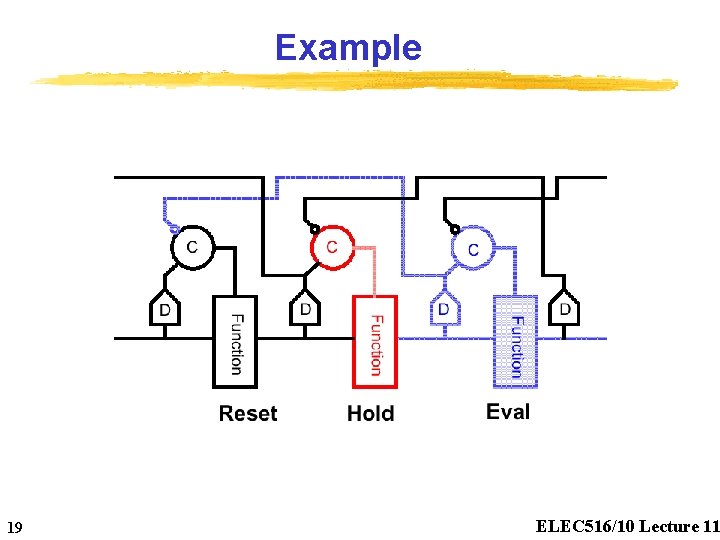

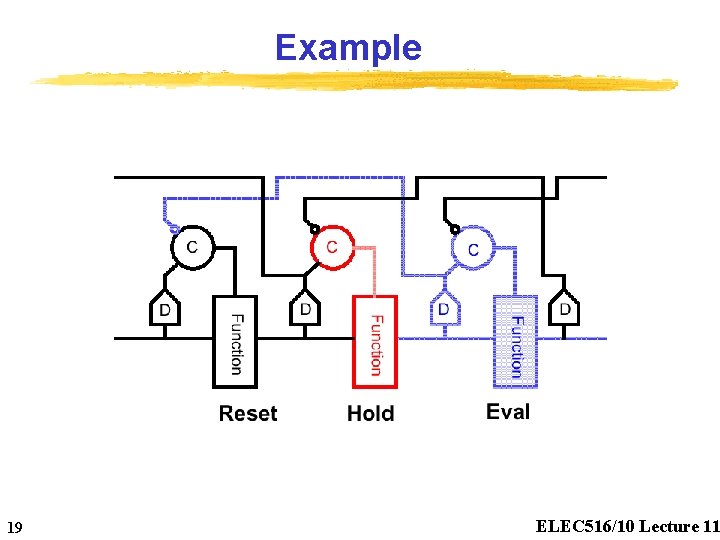

Example 19 ELEC 516/10 Lecture 11

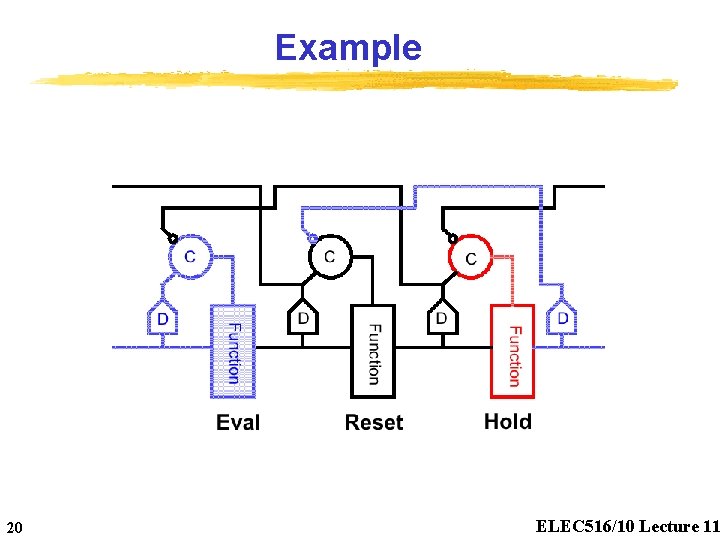

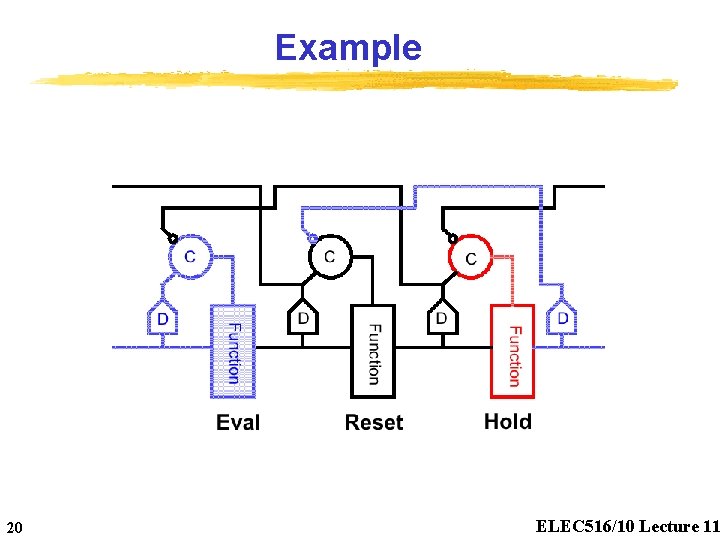

Example 20 ELEC 516/10 Lecture 11

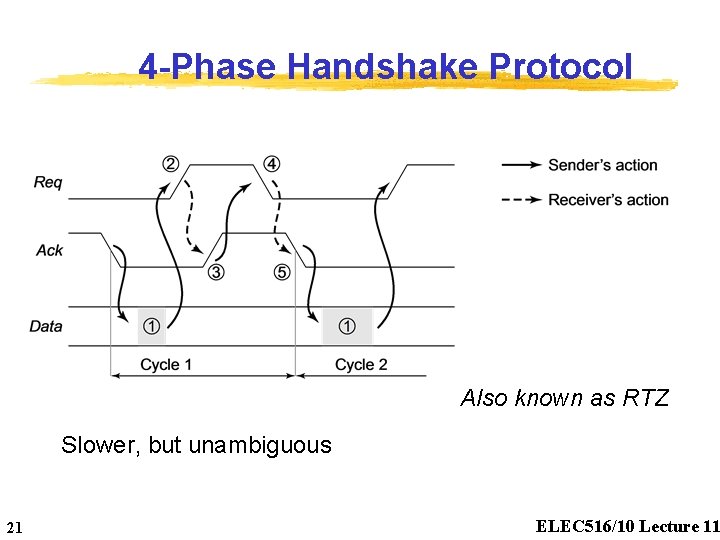

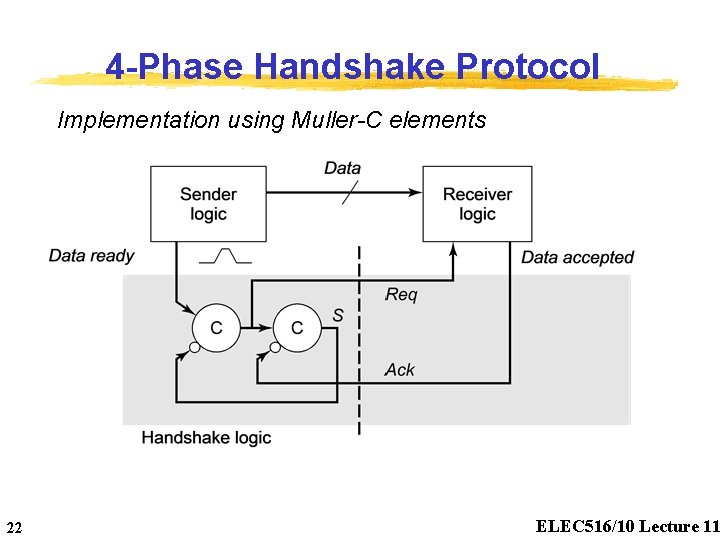

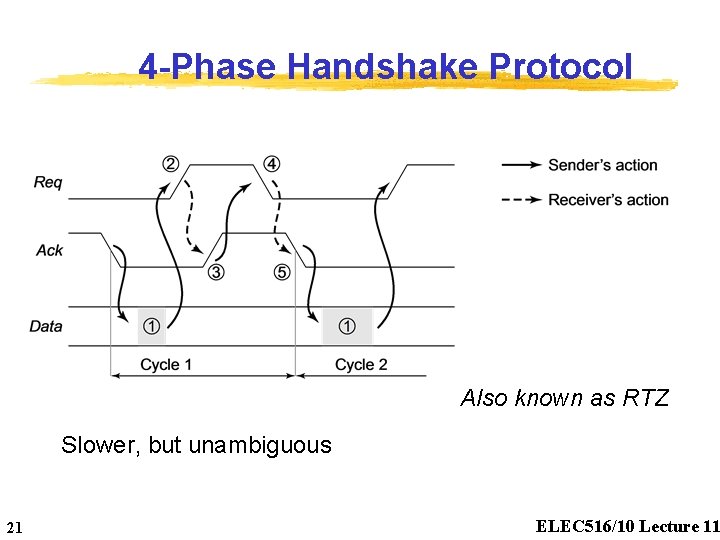

4 -Phase Handshake Protocol Also known as RTZ Slower, but unambiguous 21 ELEC 516/10 Lecture 11

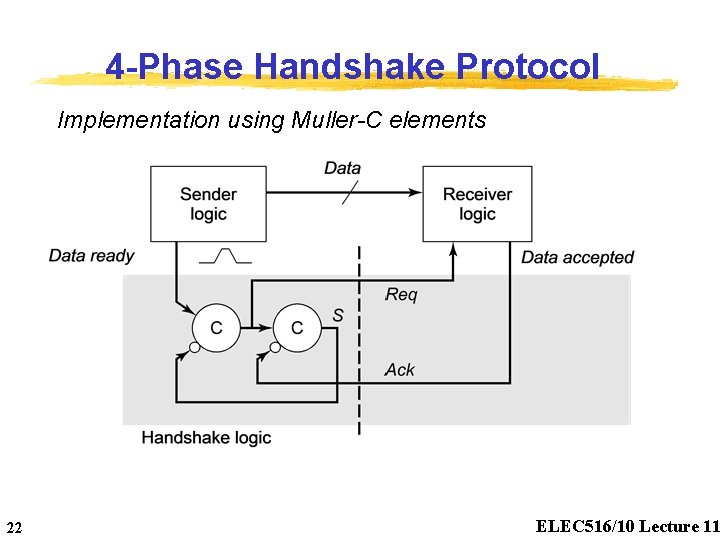

4 -Phase Handshake Protocol Implementation using Muller-C elements 22 ELEC 516/10 Lecture 11

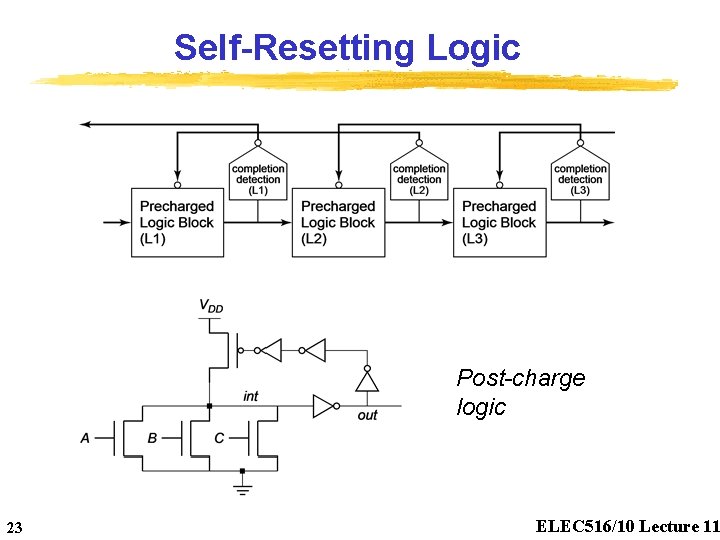

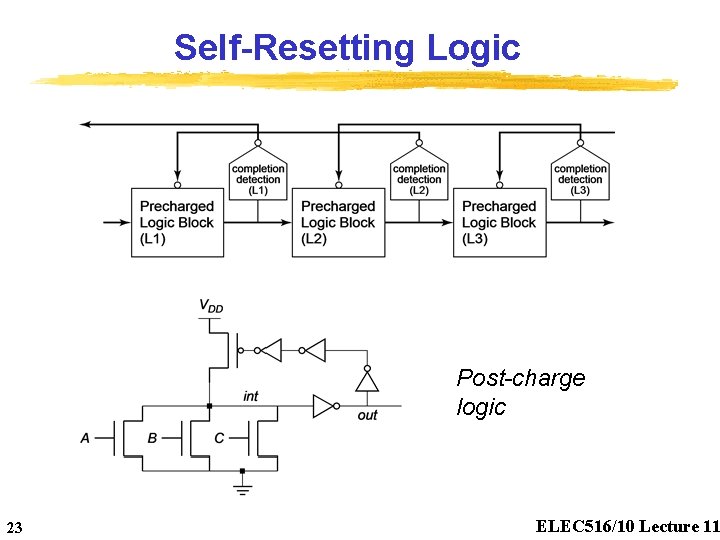

Self-Resetting Logic Post-charge logic 23 ELEC 516/10 Lecture 11

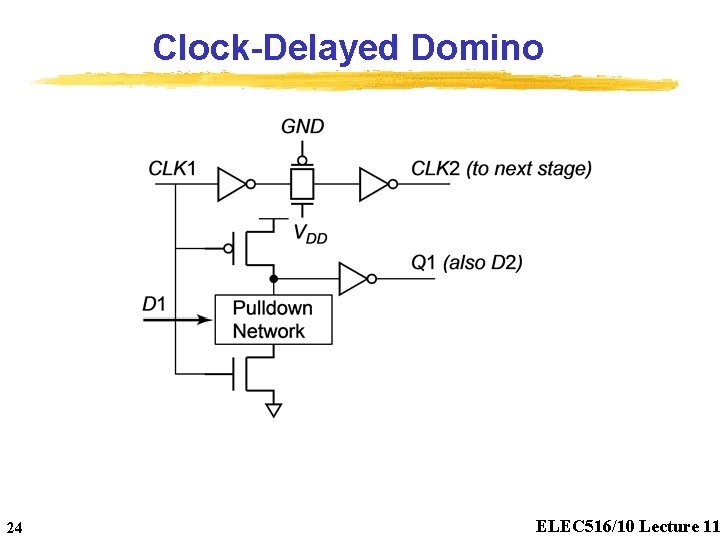

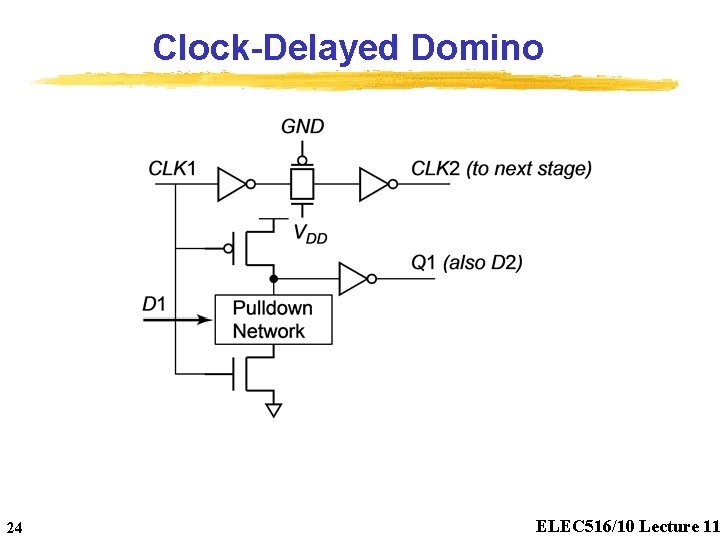

Clock-Delayed Domino 24 ELEC 516/10 Lecture 11

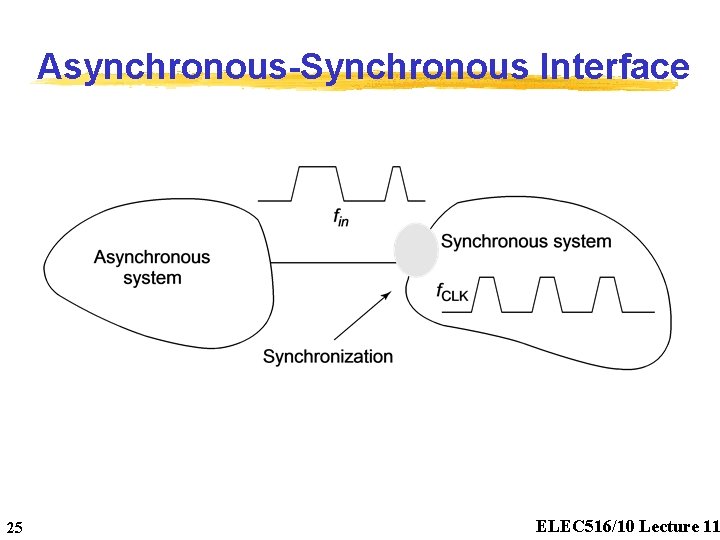

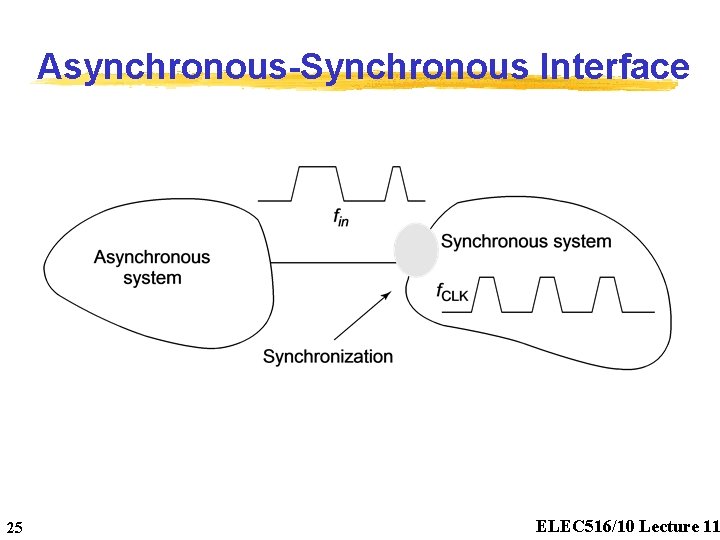

Asynchronous-Synchronous Interface 25 ELEC 516/10 Lecture 11

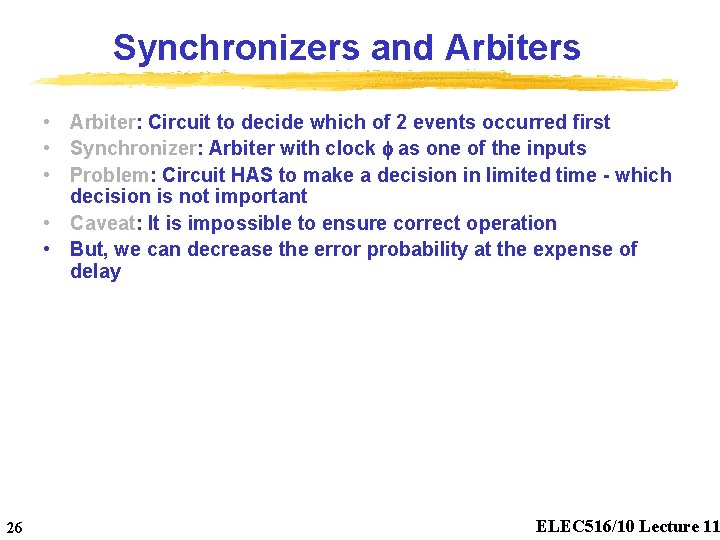

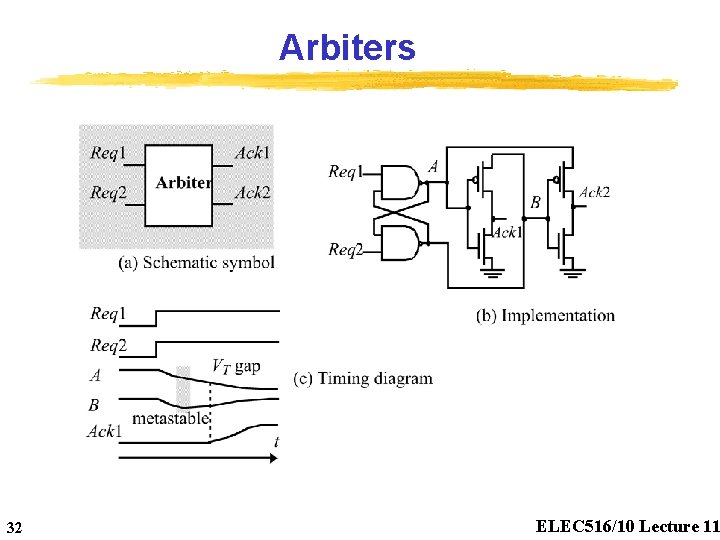

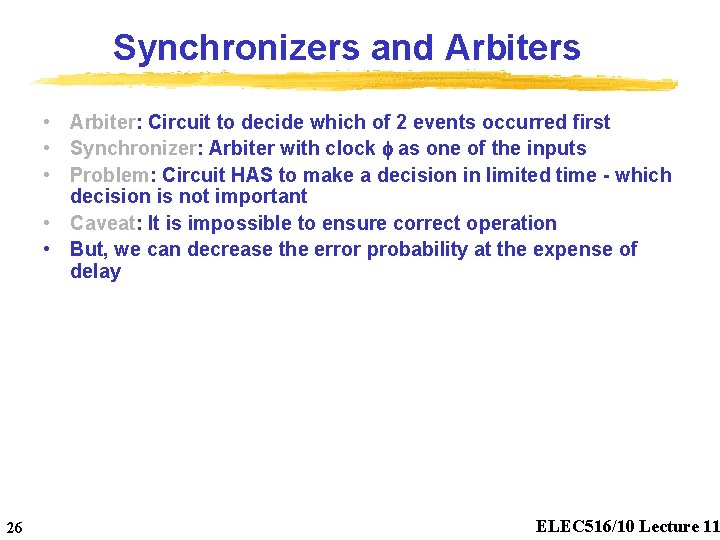

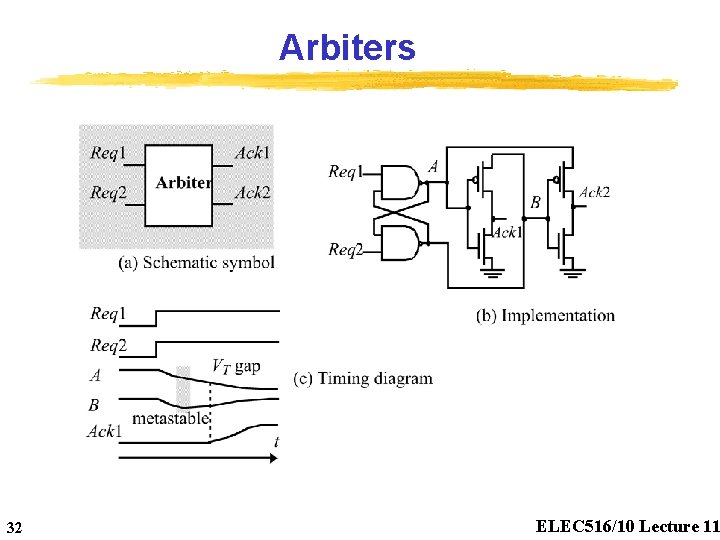

Synchronizers and Arbiters • Arbiter: Circuit to decide which of 2 events occurred first • Synchronizer: Arbiter with clock f as one of the inputs • Problem: Circuit HAS to make a decision in limited time - which decision is not important • Caveat: It is impossible to ensure correct operation • But, we can decrease the error probability at the expense of delay 26 ELEC 516/10 Lecture 11

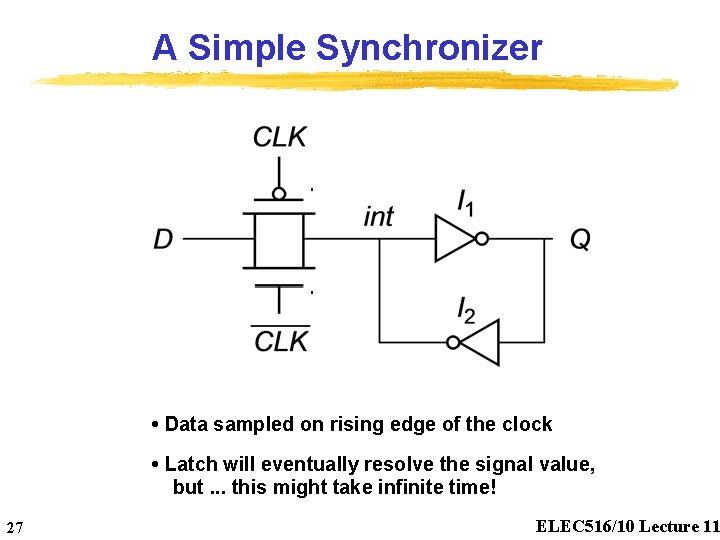

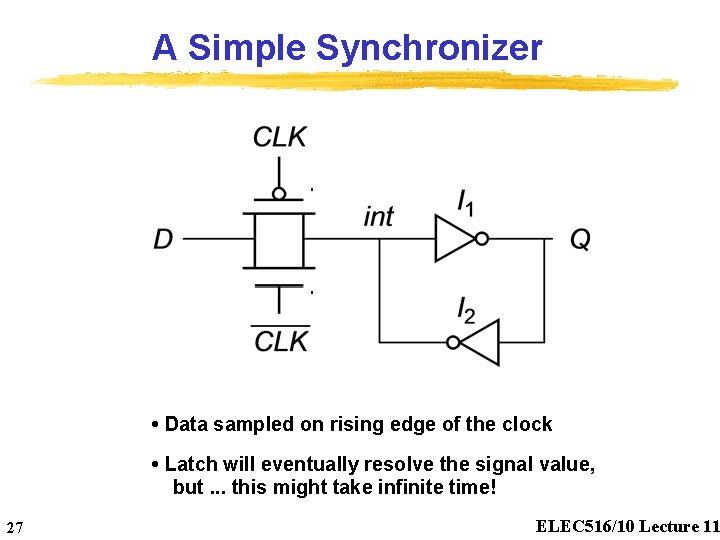

A Simple Synchronizer • Data sampled on rising edge of the clock • Latch will eventually resolve the signal value, but. . . this might take infinite time! 27 ELEC 516/10 Lecture 11

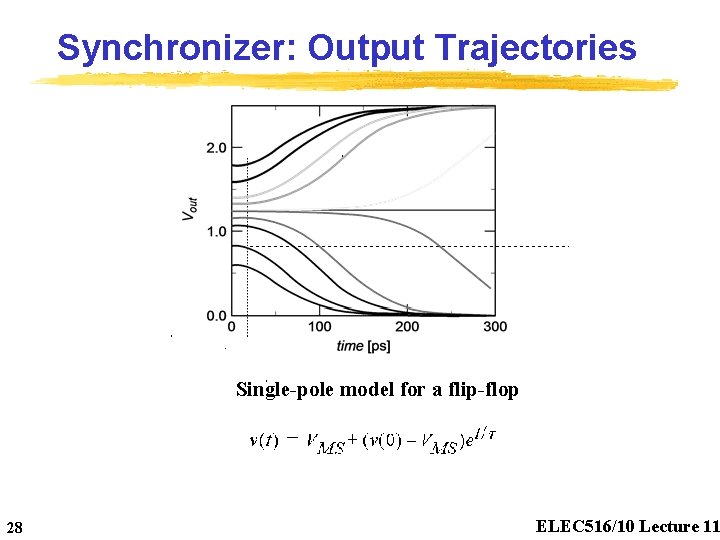

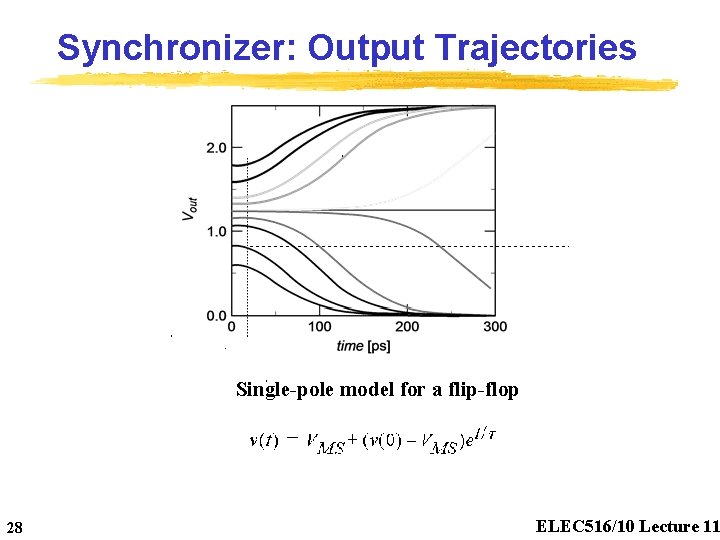

Synchronizer: Output Trajectories Single-pole model for a flip-flop 28 ELEC 516/10 Lecture 11

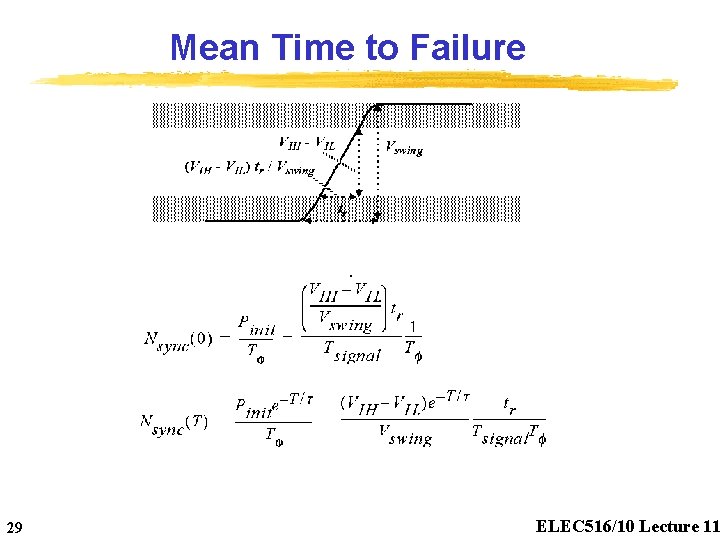

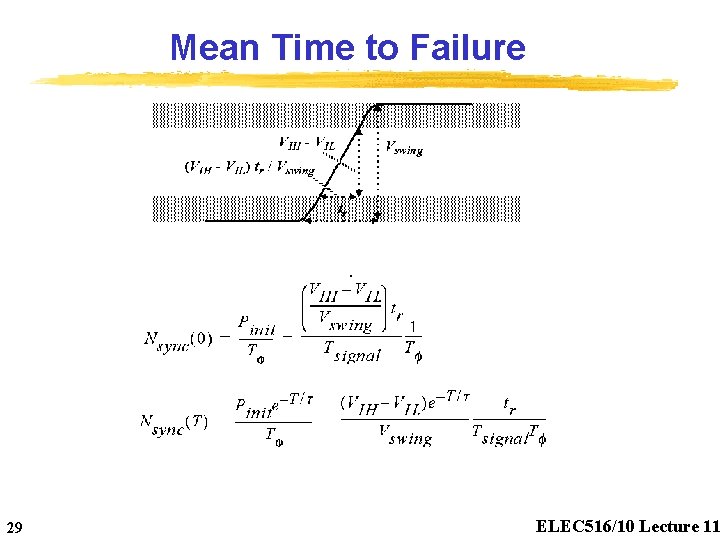

Mean Time to Failure 29 ELEC 516/10 Lecture 11

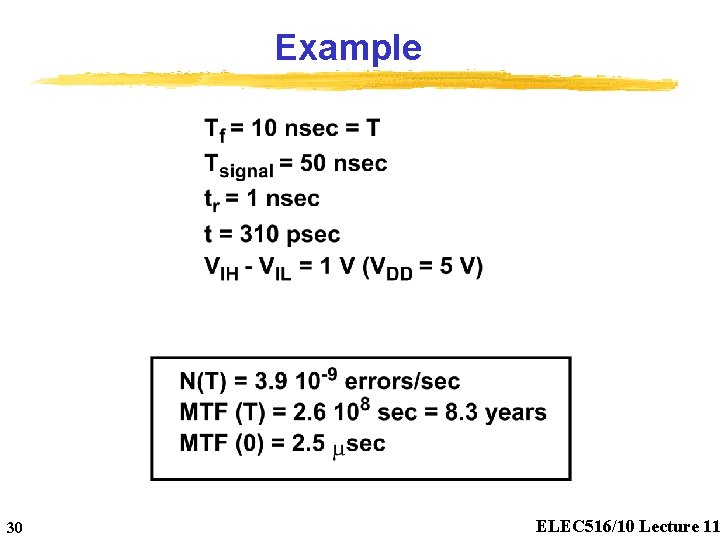

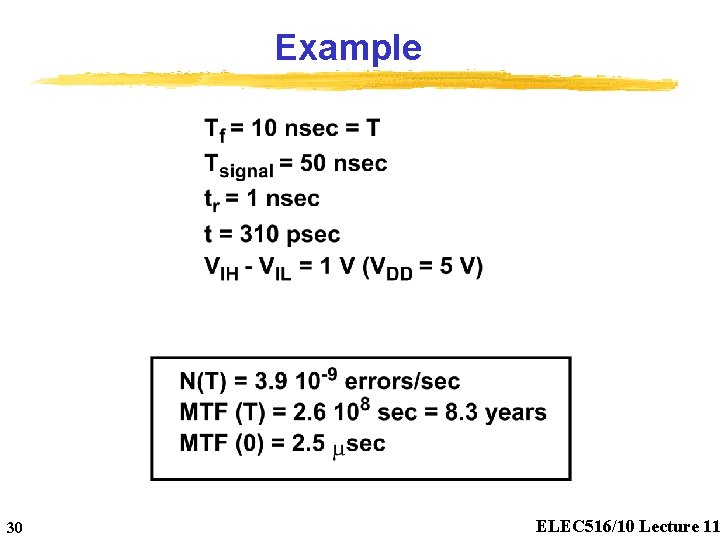

Example 30 ELEC 516/10 Lecture 11

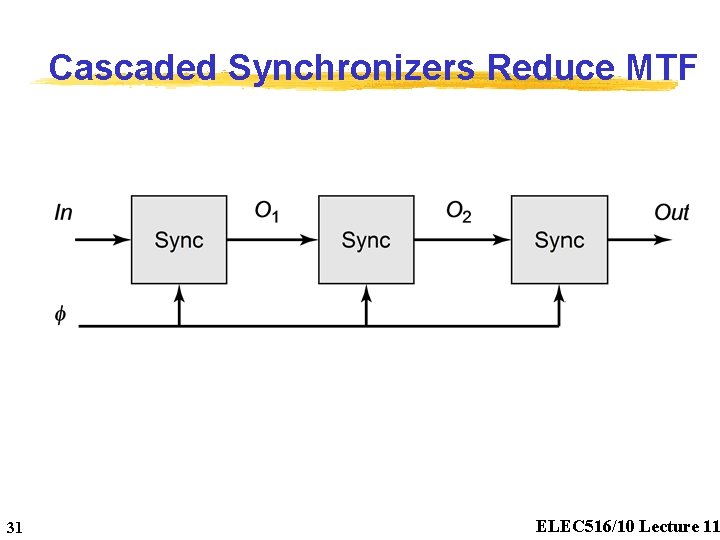

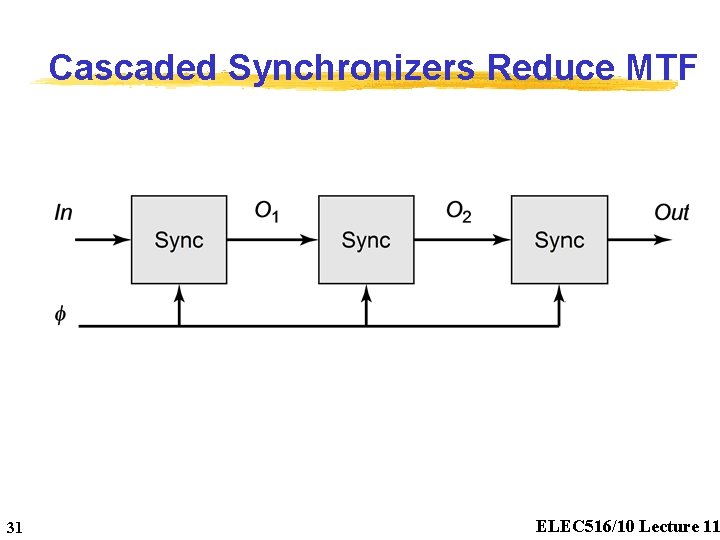

Cascaded Synchronizers Reduce MTF 31 ELEC 516/10 Lecture 11

Arbiters 32 ELEC 516/10 Lecture 11

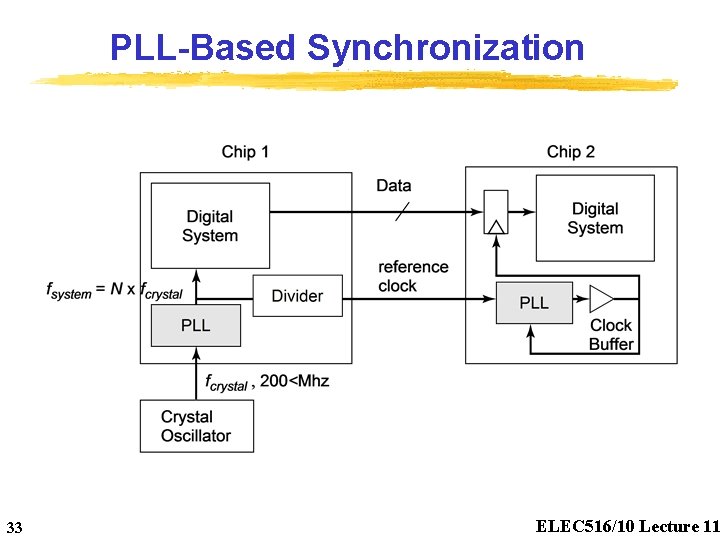

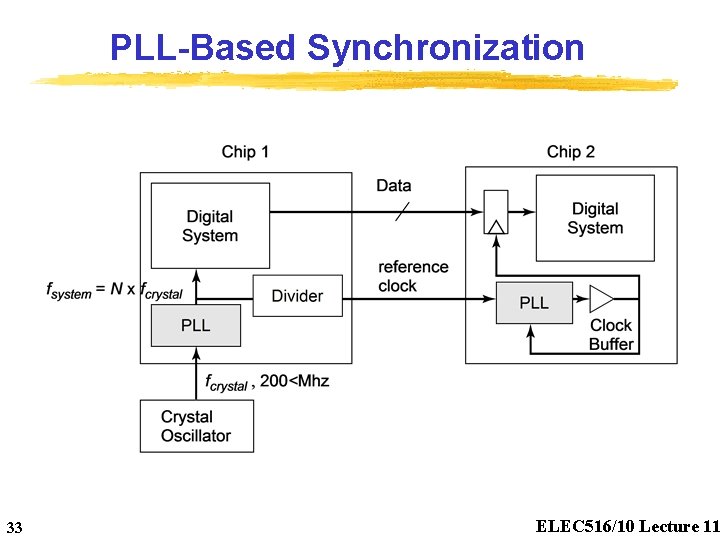

PLL-Based Synchronization 33 ELEC 516/10 Lecture 11

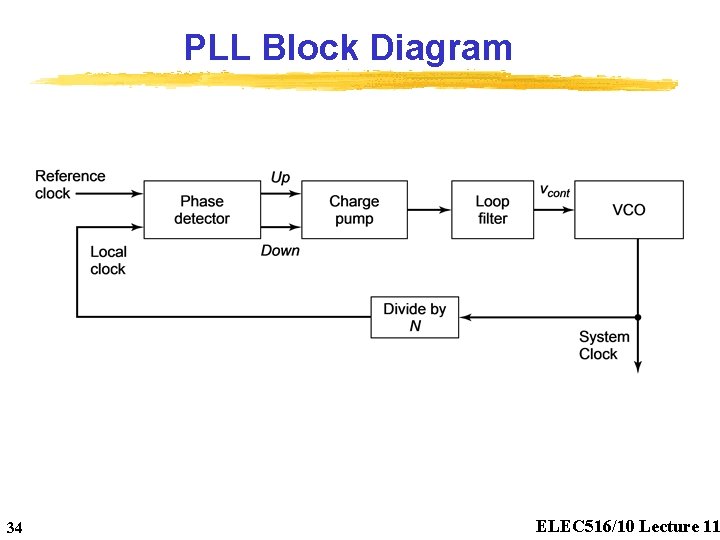

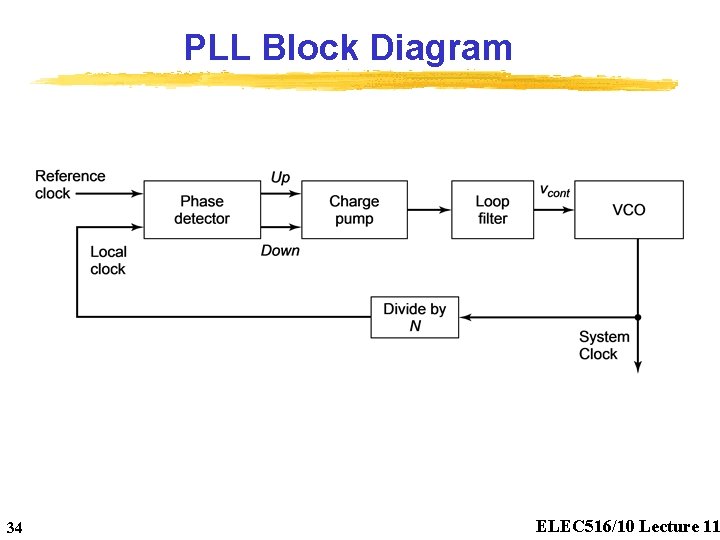

PLL Block Diagram 34 ELEC 516/10 Lecture 11

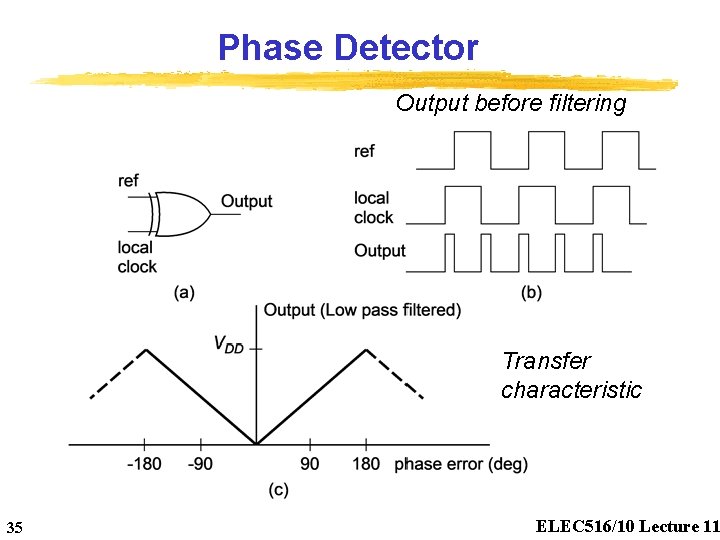

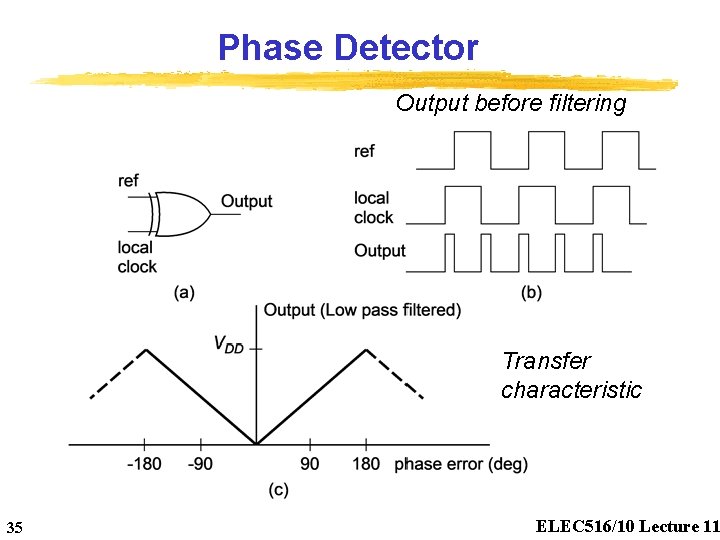

Phase Detector Output before filtering Transfer characteristic 35 ELEC 516/10 Lecture 11

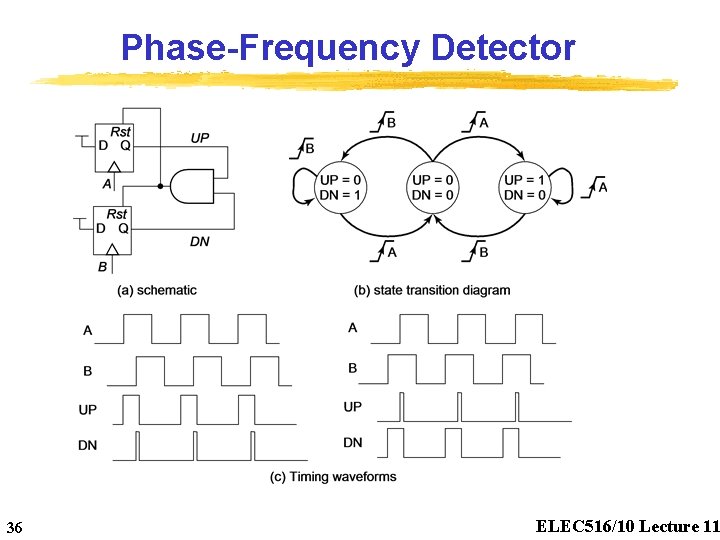

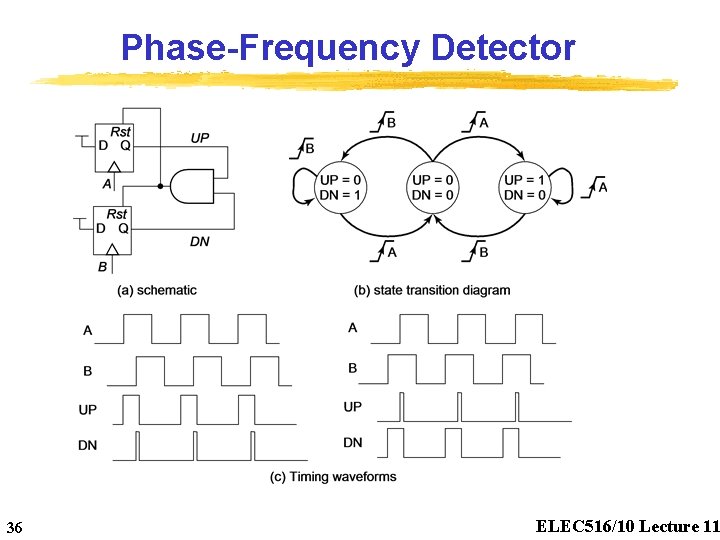

Phase-Frequency Detector 36 ELEC 516/10 Lecture 11

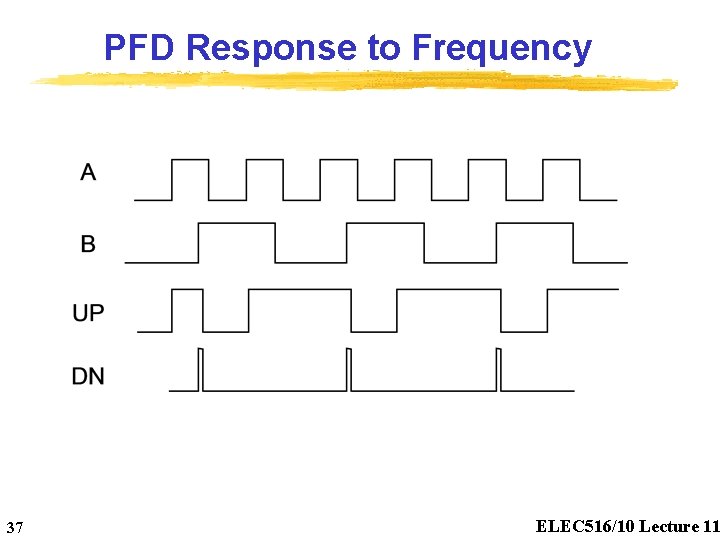

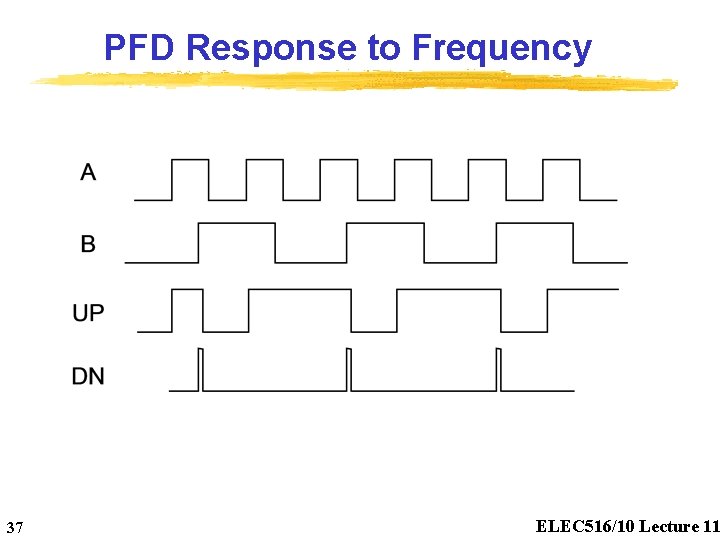

PFD Response to Frequency 37 ELEC 516/10 Lecture 11

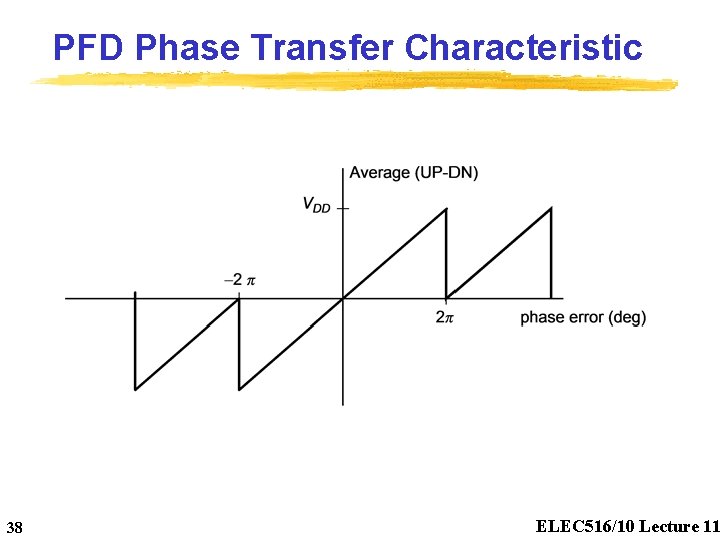

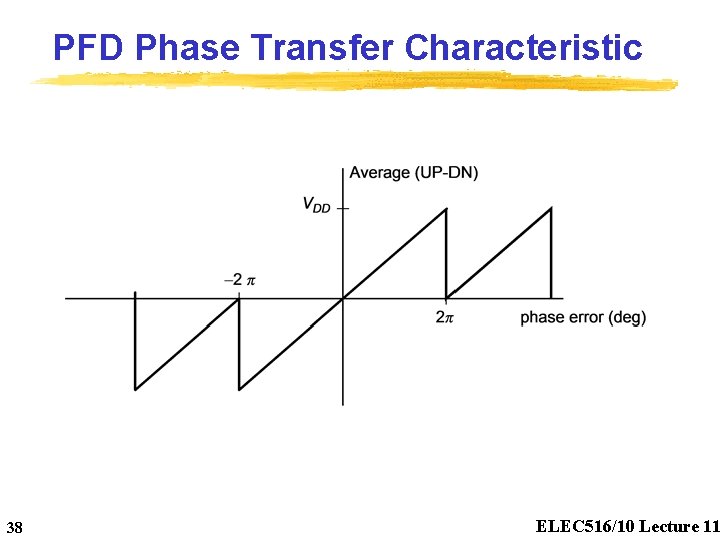

PFD Phase Transfer Characteristic 38 ELEC 516/10 Lecture 11

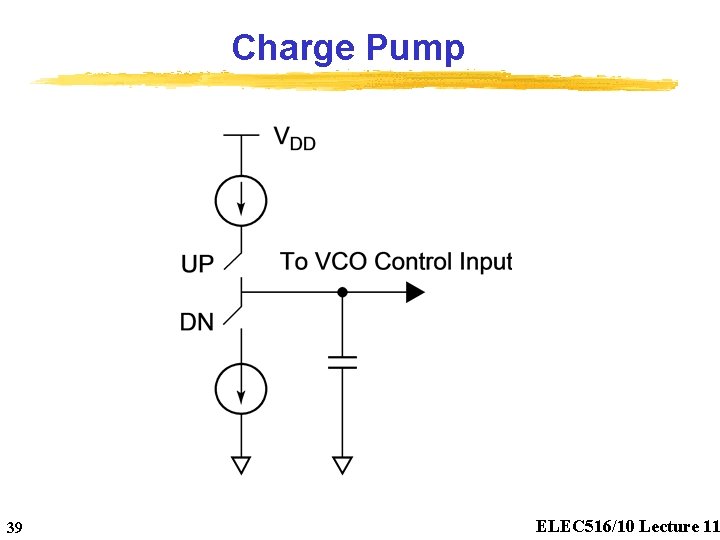

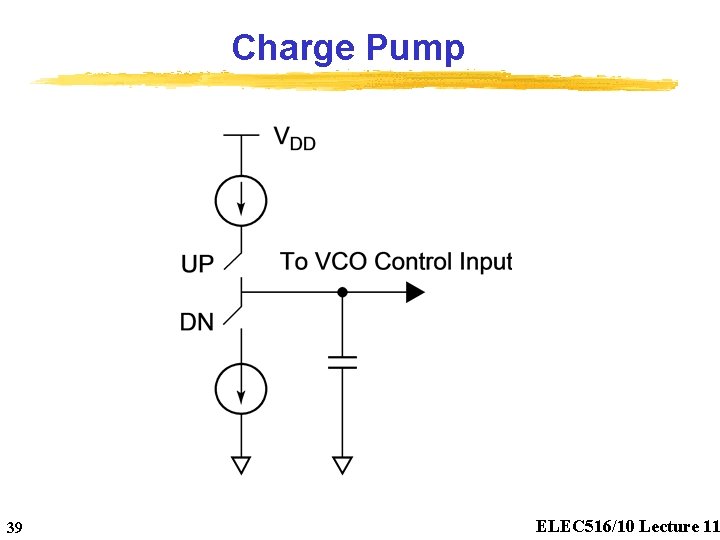

Charge Pump 39 ELEC 516/10 Lecture 11

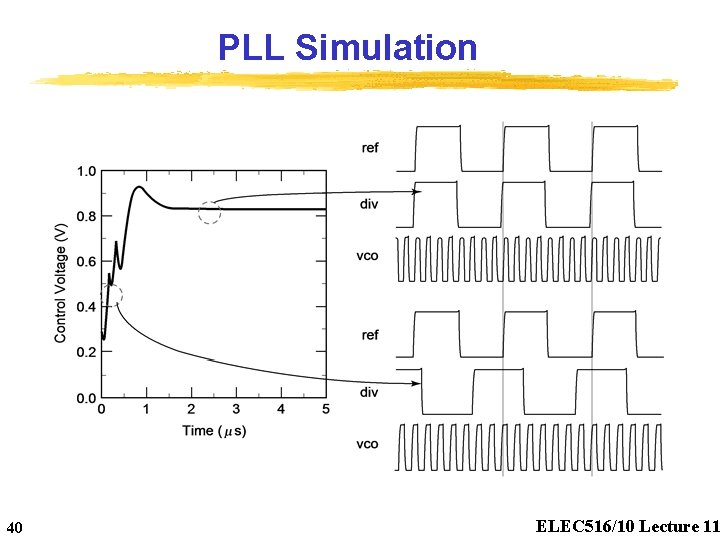

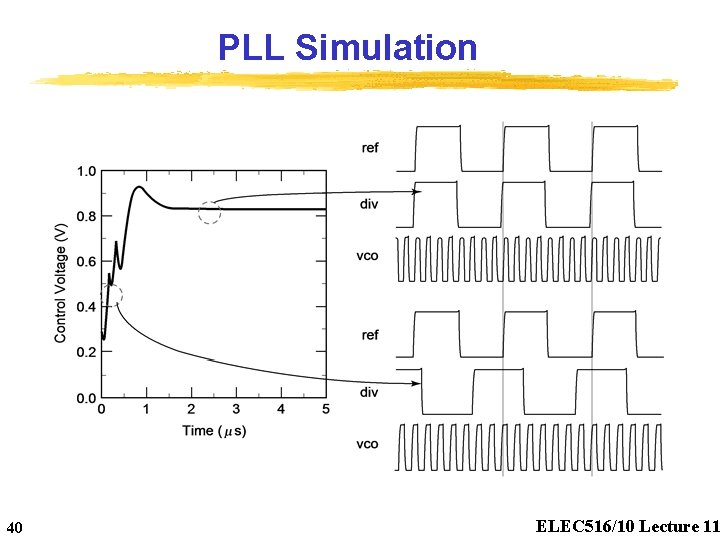

PLL Simulation 40 ELEC 516/10 Lecture 11

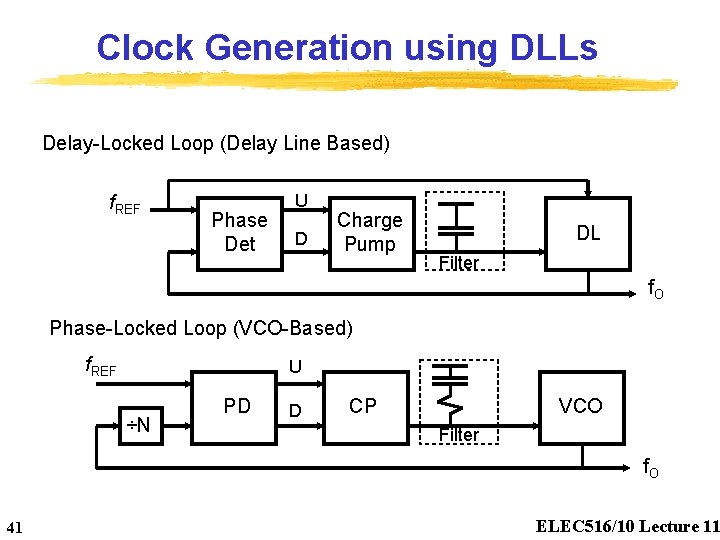

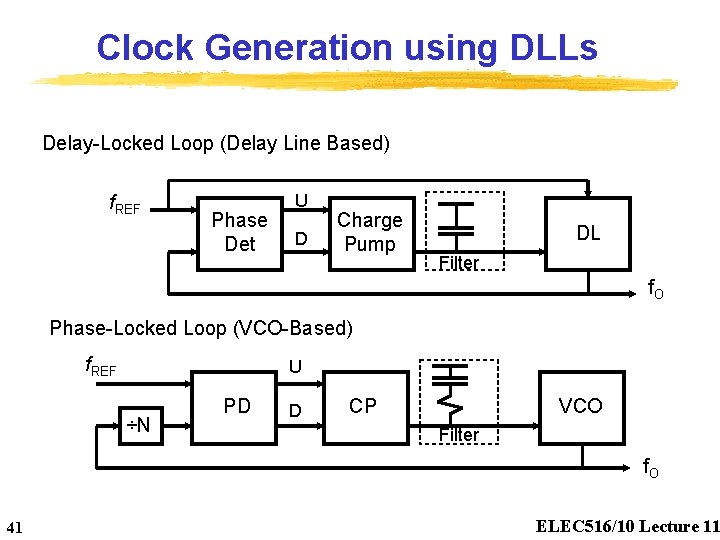

Clock Generation using DLLs Delay-Locked Loop (Delay Line Based) f. REF Phase Det U D Charge Pump DL Filter f. O Phase-Locked Loop (VCO-Based) f. REF U ÷N PD D CP VCO Filter f. O 41 ELEC 516/10 Lecture 11

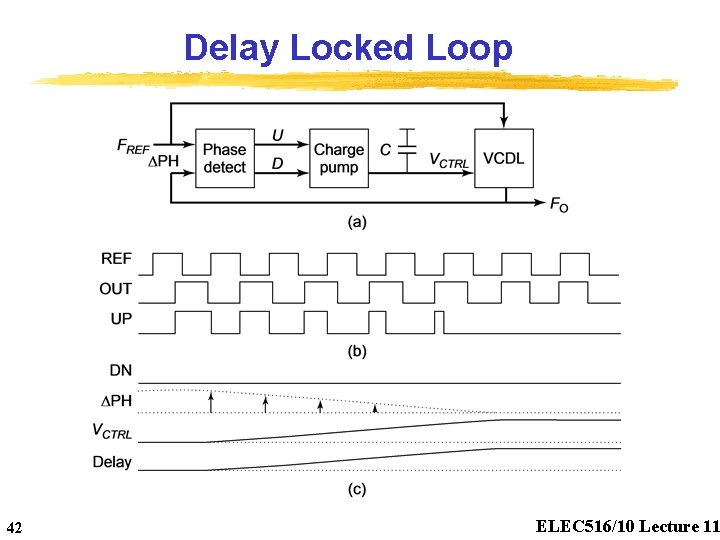

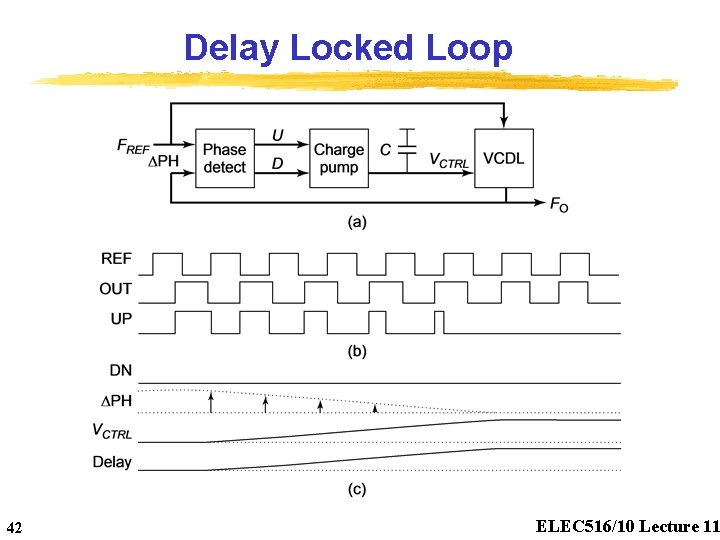

Delay Locked Loop 42 ELEC 516/10 Lecture 11

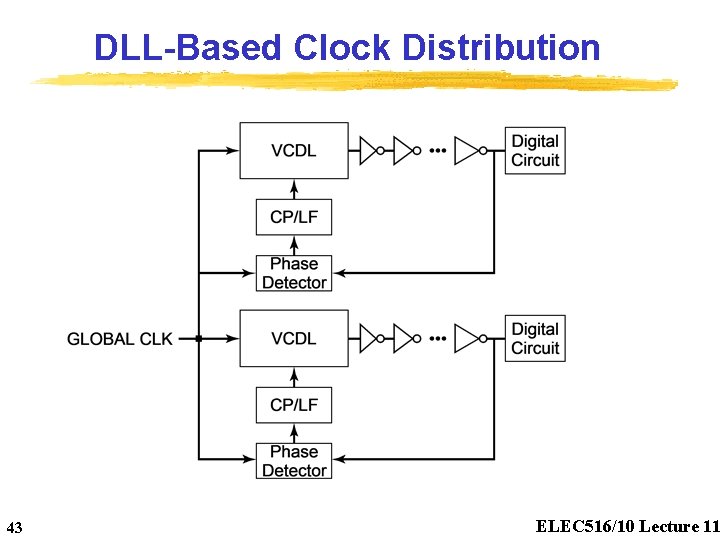

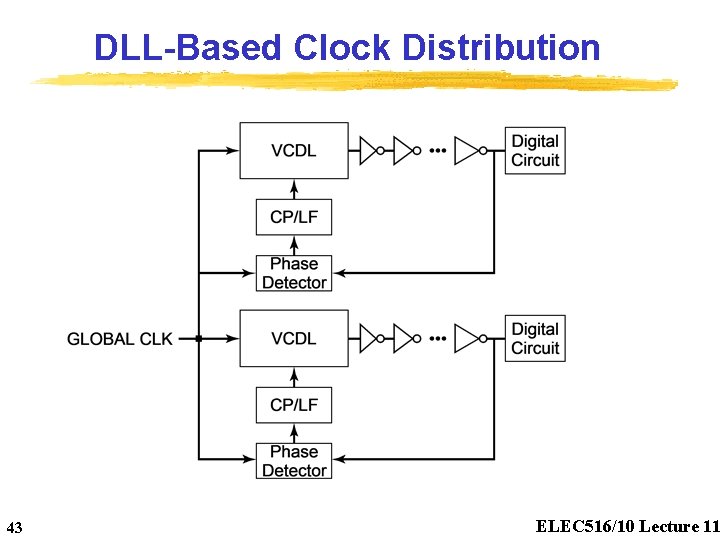

DLL-Based Clock Distribution 43 ELEC 516/10 Lecture 11