ELCT 903 Programmable Logic Circuits Introduction Dr Eng

ELCT 903 Programmable Logic Circuits: Introduction Dr. Eng. Amr T. Abdel-Hamid Fall 2010

Course Contents Programmable Logic Circuits Ø Introduction to Programmable Logic Devices Ø Number systems and basic arithmetic operations Ø Computer Arithmetic Basic Functions: Ø Addition Ø Multiplication Ø Division Ø Floating-point arithmetic Ø Special FP Functions Dr. Amr Talaat Ø Pipelining Basics Ø Test Bench Generation ELECT 90 X

Course Grading Programmable Logic Circuits Ø Exams Ø Quizzes (10%) 3 Quizzes: best 2 Ø Midterm (20%) Ø Final exam (40%) Ø Assignments(50%) Dr. Amr Talaat Ø Project(25%) ELECT 90 X

Project Programmable Logic Circuits Ø Course Project: Ø Building a Fast Floating Point MIPS Microprocessor Ø Other topics (after instructor approval) Ø Mixed Signal Design Ø IP Protection Ø More in your master/graduation project topic to publish a paper? Dr. Amr Talaat ELECT 90 X

Project Programmable Logic Circuits Ø Phase 0: Select your partner (27/9/2010) Ø Submit list of your group members (2 -4 per group) Dr. Amr Talaat Ø Phase 1: . . . Ø Phase N: Finael Project Implementation + Report (2 weeks before finals) FINAL Non-Negotiable deadline ELECT 90 X

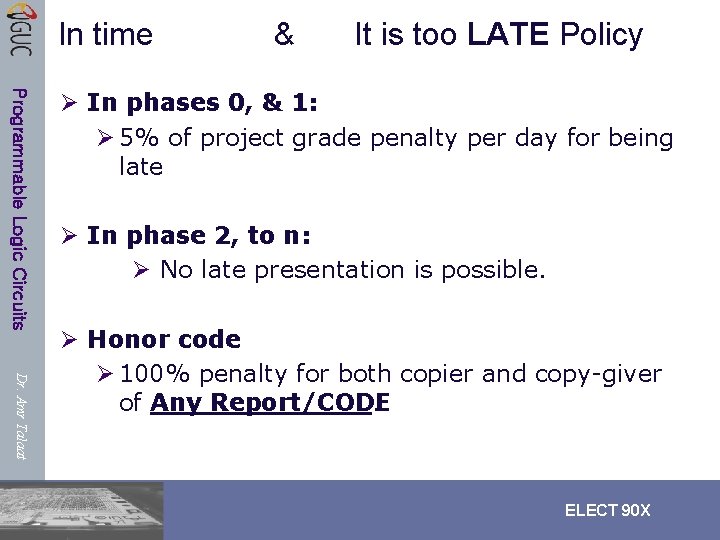

In time & It is too LATE Policy Programmable Logic Circuits Ø In phases 0, & 1: Ø 5% of project grade penalty per day for being late Ø In phase 2, to n: Ø No late presentation is possible. Dr. Amr Talaat Ø Honor code Ø 100% penalty for both copier and copy-giver of Any Report/CODE. ELECT 90 X

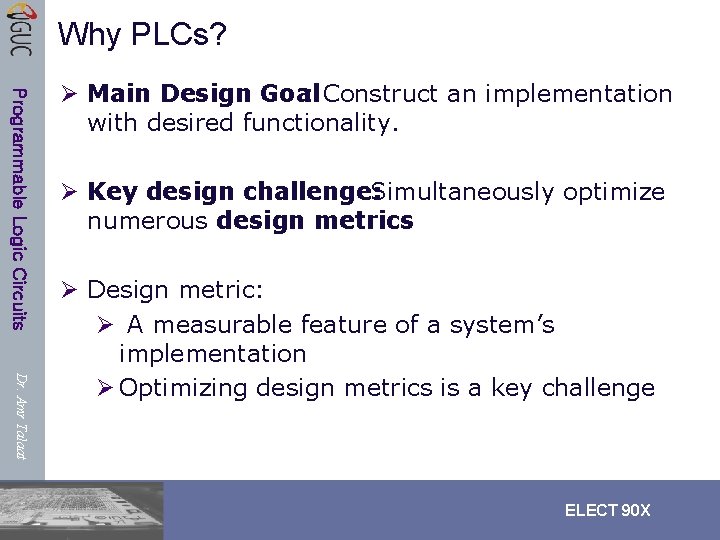

Why PLCs? Programmable Logic Circuits Ø Main Design Goal : Construct an implementation with desired functionality. Ø Key design challenge: Simultaneously optimize numerous design metrics Dr. Amr Talaat Ø Design metric: Ø A measurable feature of a system’s implementation Ø Optimizing design metrics is a key challenge ELECT 90 X

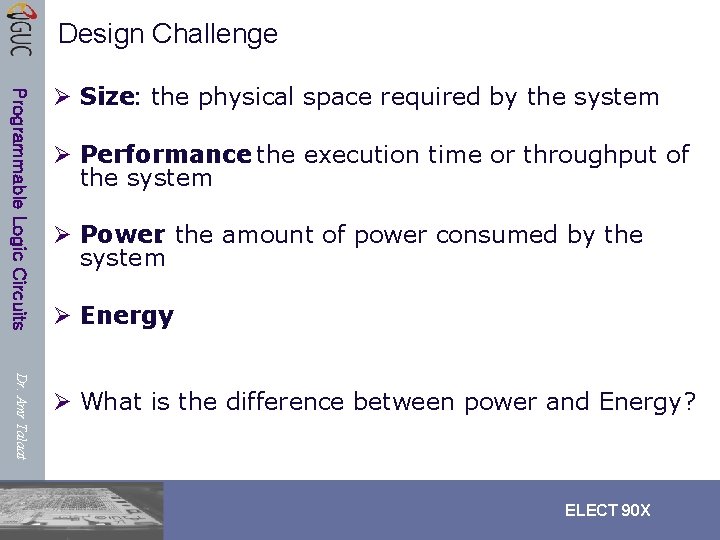

Design Challenge Programmable Logic Circuits Ø Size: the physical space required by the system Ø Performance : the execution time or throughput of the system Ø Power: the amount of power consumed by the system Ø Energy Dr. Amr Talaat Ø What is the difference between power and Energy? ELECT 90 X

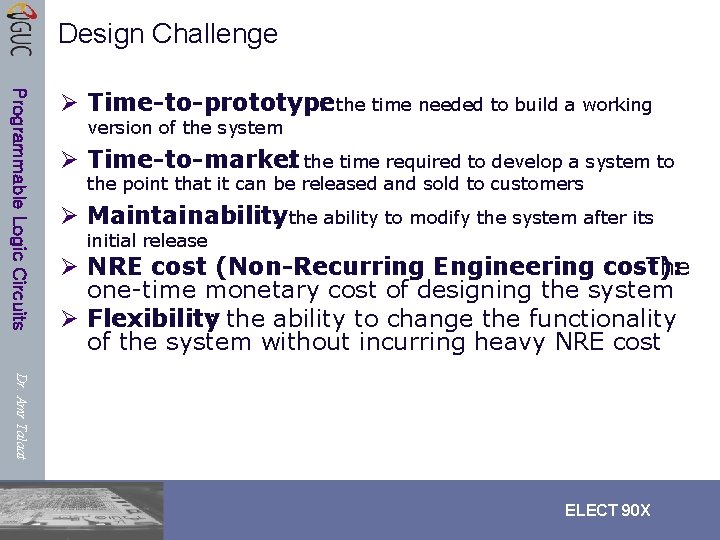

Design Challenge Programmable Logic Circuits Ø Time-to-prototype : the time needed to build a working version of the system Ø Time-to-market : the time required to develop a system to the point that it can be released and sold to customers Ø Maintainability : the ability to modify the system after its initial release Ø NRE cost (Non-Recurring Engineering cost): The one-time monetary cost of designing the system Ø Flexibility : the ability to change the functionality of the system without incurring heavy NRE cost Dr. Amr Talaat ELECT 90 X

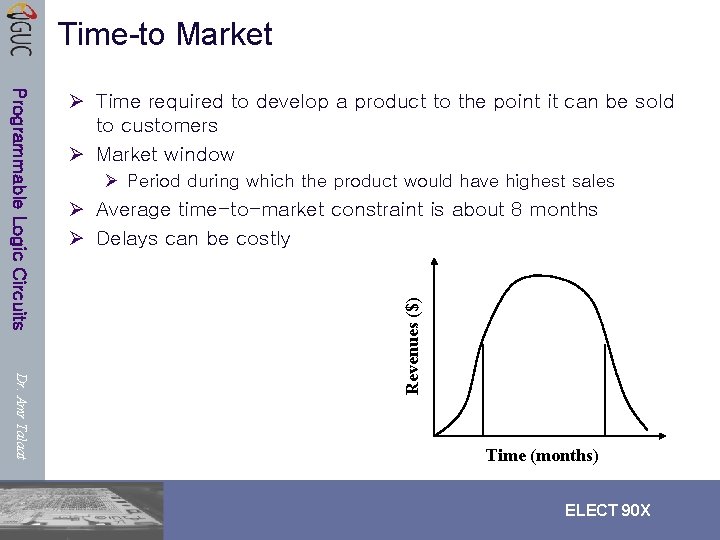

Time-to Market Ø Period during which the product would have highest sales Ø Average time-to-market constraint is about 8 months Ø Delays can be costly Dr. Amr Talaat Revenues ($) Programmable Logic Circuits Ø Time required to develop a product to the point it can be sold to customers Ø Market window Time (months) ELECT 90 X

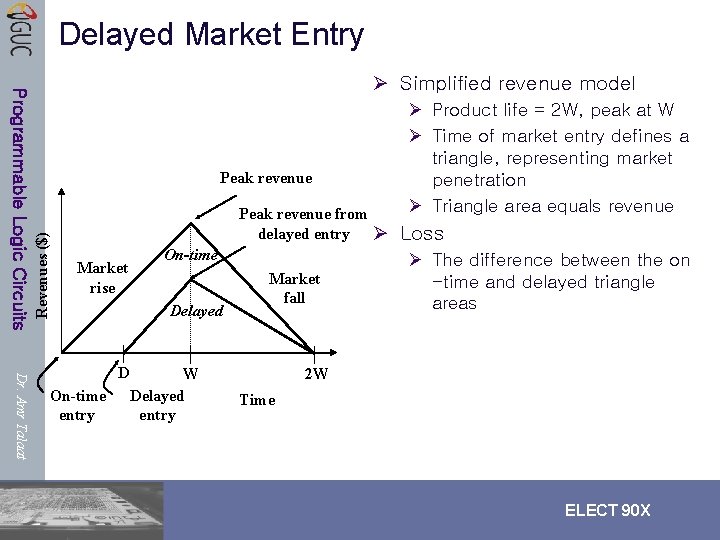

Delayed Market Entry Peak revenue Revenues ($) Programmable Logic Circuits Ø Simplified revenue model Peak revenue from delayed entry Ø Market rise Delayed Dr. Amr Talaat D On-time entry On-time W Delayed entry Market fall Ø Product life = 2 W, peak at W Ø Time of market entry defines a triangle, representing market penetration Ø Triangle area equals revenue Loss Ø The difference between the on -time and delayed triangle areas 2 W Time ELECT 90 X

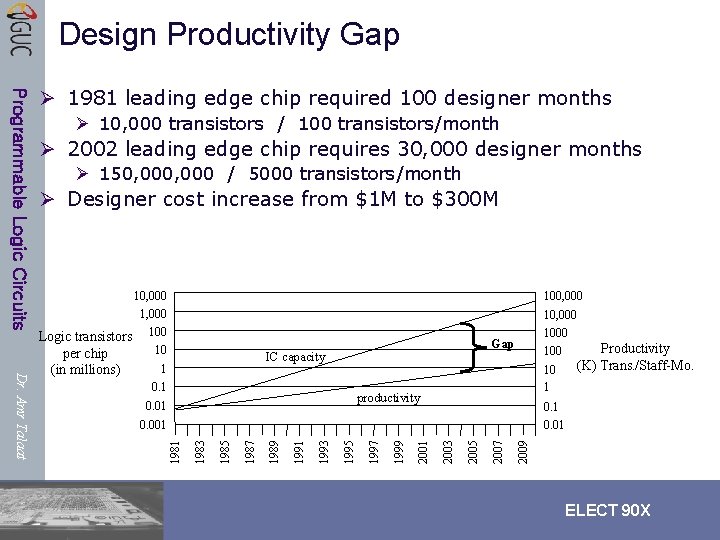

Design Productivity Gap Ø 10, 000 transistors / 100 transistors/month Ø 2002 leading edge chip requires 30, 000 designer months Ø 150, 000 / 5000 transistors/month Ø Designer cost increase from $1 M to $300 M 100, 000 10, 000 10 1 0. 1 1000 100 Gap IC capacity 10 1 productivity 0. 01 Productivity (K) Trans. /Staff-Mo. 0. 1 0. 001 2009 2007 2005 2003 2001 1999 1997 1995 1993 1991 1989 1987 1985 0. 01 1983 Dr. Amr Talaat Logic transistors per chip (in millions) 10, 000 1981 Programmable Logic Circuits Ø 1981 leading edge chip required 100 designer months ELECT 90 X

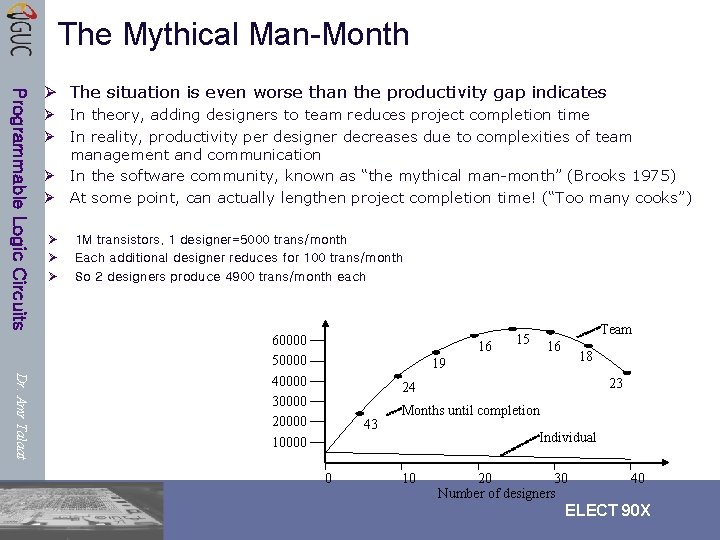

The Mythical Man-Month Programmable Logic Circuits Ø The situation is even worse than the productivity gap indicates Ø In theory, adding designers to team reduces project completion time Ø In reality, productivity per designer decreases due to complexities of team management and communication Ø In the software community, known as “the mythical man-month” (Brooks 1975) Ø At some point, can actually lengthen project completion time! (“Too many cooks”) Ø Ø Ø 1 M transistors, 1 designer=5000 trans/month Each additional designer reduces for 100 trans/month So 2 designers produce 4900 trans/month each Dr. Amr Talaat 60000 50000 40000 30000 20000 16 Team 15 16 18 19 23 24 43 0 Months until completion Individual 10 20 30 Number of designers 40 ELECT 90 X

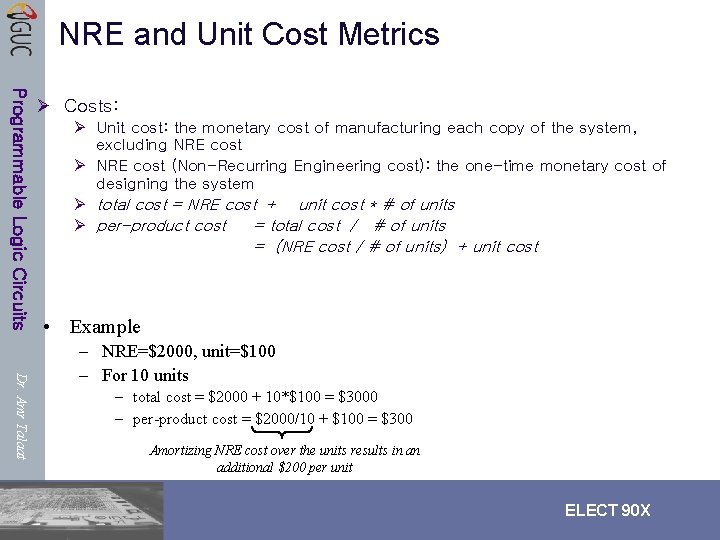

NRE and Unit Cost Metrics Programmable Logic Circuits Ø Costs: Ø Unit cost: the monetary cost of manufacturing each copy of the system, excluding NRE cost Ø NRE cost (Non-Recurring Engineering cost): the one-time monetary cost of designing the system Ø total cost = NRE cost + unit cost * # of units Ø per-product cost = total cost / # of units = (NRE cost / # of units) + unit cost • Example Dr. Amr Talaat – NRE=$2000, unit=$100 – For 10 units – total cost = $2000 + 10*$100 = $3000 – per-product cost = $2000/10 + $100 = $300 Amortizing NRE cost over the units results in an additional $200 per unit ELECT 90 X

NRE and unit cost metrics Programmable Logic Circuits Ø Compare technologies by costs -- best depends on quantity Ø Technology A: NRE=$2, 000, unit=$100 Ø Technology B: NRE=$30, 000, unit=$30 Ø Technology C: NRE=$100, 000, unit=$2 • But, must also consider time-to-market Dr. Amr Talaat ELECT 90 X

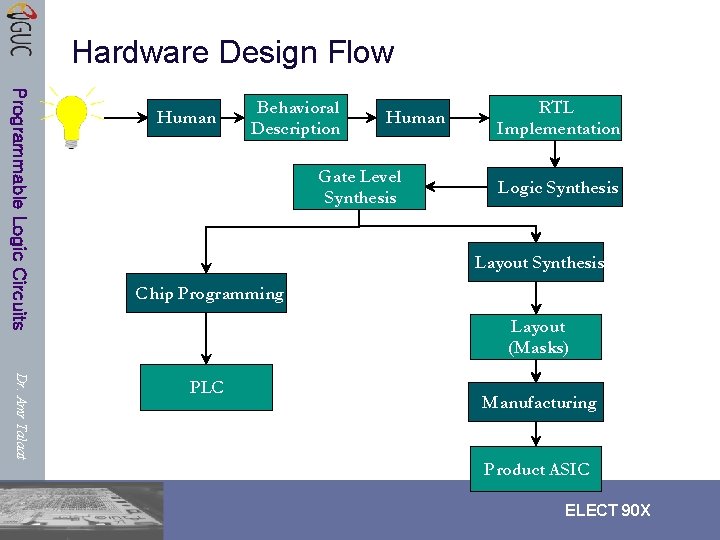

Hardware Design Flow Programmable Logic Circuits Human Behavioral Description Human Gate Level Synthesis RTL Implementation Logic Synthesis Layout Synthesis Chip Programming Layout (Masks) Dr. Amr Talaat PLC Manufacturing Product ASIC ELECT 90 X

Programmable Logic Circuits Dr. Amr Talaat Ø Many programmable logic devices are fieldprogrammable, i. e. , can be programmed outside of the manufacturing environment Ø Most programmable logic devices are erasable and reprogrammable. Ø Allows “updating” a device or correction of errors Ø Allows reuse the device for a different design - the ultimate in re-usability! Ø Ideal for course laboratories Ø Programmable logic devices can be used to prototype design that will be implemented for sale in regular ICs. Ø Complete Intel Pentium designs were actually prototyped with specialized systems based on large numbers of VLSI programmable devices! ELECT 90 X

Programmable Logic Circuits Ø Facts: Ø It is most economical to produce an IC in large volumes Ø Many designs required only small volumes of Ics Ø A programmable logic part can be: Ø made in large volumes Ø programmed to implement large numbers of different low-volume designs Dr. Amr Talaat ELECT 90 X

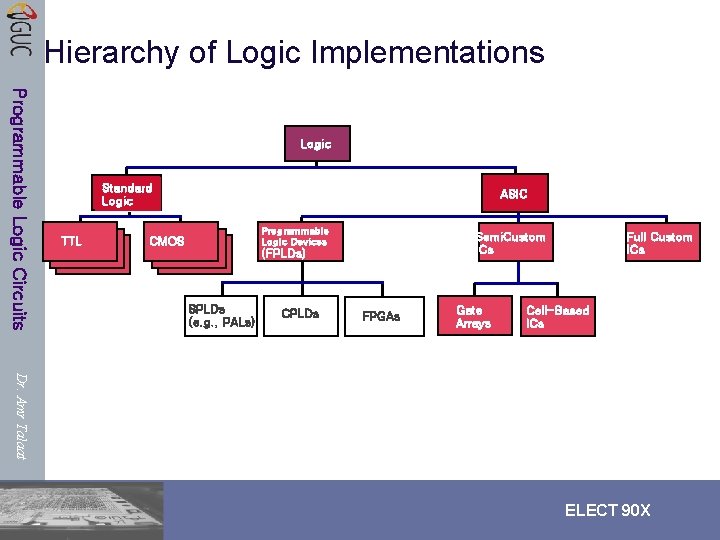

Hierarchy of Logic Implementations Programmable Logic Circuits Logic Standard Logic TTL ASIC Programmable Logic Devices CMOS Semi. Custom ICs (FPLDs) SPLDs (e. g. , PALs) CPLDs FPGAs Gate Arrays Full Custom ICs Cell-Based ICs Dr. Amr Talaat ELECT 90 X

Programming Technologies Programmable Logic Circuits Ø Programming technologies are used to: Ø Control connections Ø Build lookup tables Ø Control transistor switching Dr. Amr Talaat Ø The technologies Ø Control connections ØMask programming ØFuse ØAntifuse ØSingle-bit storage element ELECT 90 X

Programming Technologies Programmable Logic Circuits Dr. Amr Talaat Ø The technologies (continued) Ø Build lookup tables ØStorage elements (as in a memory) Ø Transistor Switching Control ØStored charge on a floating transistor gate ØErasable ØElectrically erasable ØFlash (as in Flash Memory) ØStorage elements (as in a memory) ELECT 90 X

Technology Characteristics Programmable Logic Circuits Ø Permanent - Cannot be erased and reprogrammed Ø Mask programming Ø Fuse Ø Antifuse Dr. Amr Talaat Ø Reprogrammable Ø Volatile - Programming lost if chip power lost Ø Single-bit storage element Ø Non-Volatile Ø Erasable Ø Electrically erasable Ø Flash (as in Flash Memory) ELECT 90 X

Field- Programmable Logic Devices Programmable Logic Circuits Dr. Amr Talaat • Component function is defined by users program. • Logic Cells Fields are interconnected by programming. • Advantages: - Flexible design that changes by reprogramming, ease of design changes - Reduce prototype-product time - Large scale integration (over 100 000 gates) - Reliability increased, low financial risk - Smaller device, low start-up cost ELECT 90 X 4/13

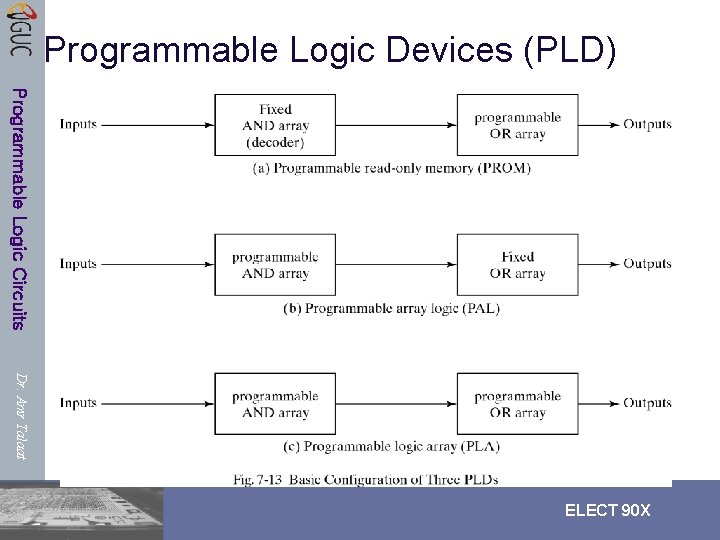

Programmable Configurations Programmable Logic Circuits Dr. Amr Talaat Ø Read Only Memory(ROM) - a fixed array of AND gates and a programmable array of OR gates Ò - a Ø Programmable Array Logic (PAL) programmable array of AND gates feeding a fixed array of OR gates. Ø Programmable Logic Array (PLA) - a programmable array of AND gates feeding a programmable array of OR gates. Ø Complex Programmable Logic Device (CPLD) /Field- Programmable Gate Array (FPGA) - complex enough to be called “architectures” ELECT 90 X

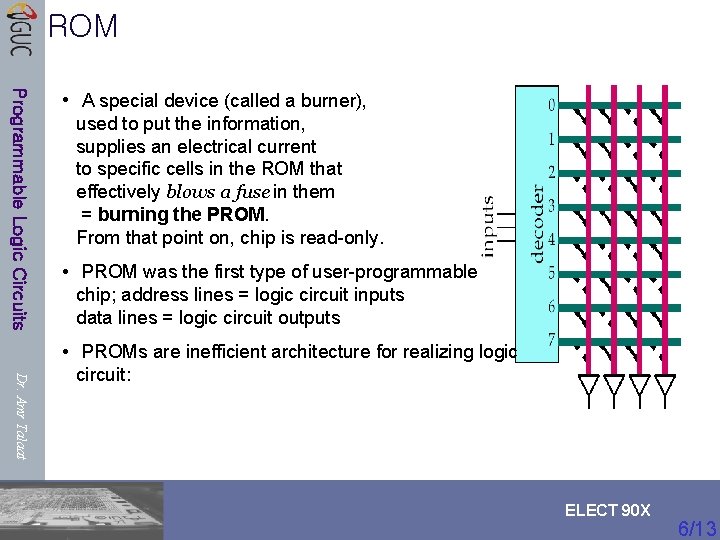

ROM Programmable Logic Circuits • A special device (called a burner), used to put the information, supplies an electrical current to specific cells in the ROM that effectively blows a fuse in them = burning the PROM. From that point on, chip is read-only. • PROM was the first type of user-programmable chip; address lines = logic circuit inputs data lines = logic circuit outputs Dr. Amr Talaat • PROMs are inefficient architecture for realizing logic circuit: ELECT 90 X 6/13

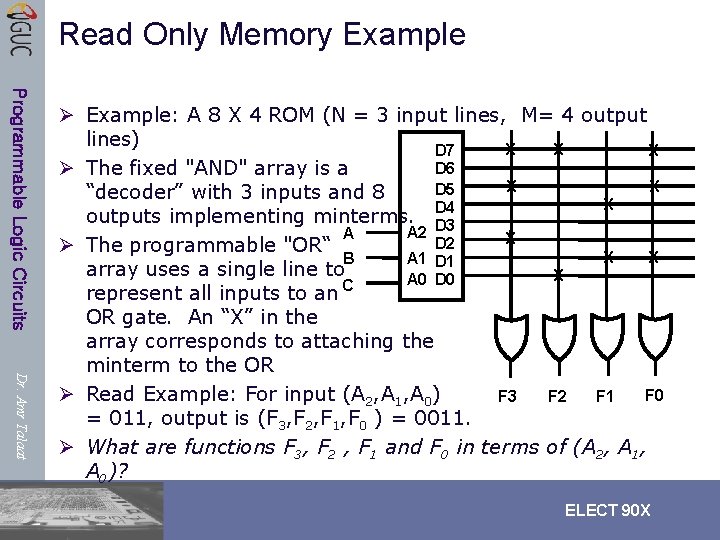

Read Only Memory Example Programmable Logic Circuits Dr. Amr Talaat Ø Example: A 8 X 4 ROM (N = 3 input lines, M= 4 output lines) X X X D 7 D 6 Ø The fixed "AND" array is a X X D 5 “decoder” with 3 inputs and 8 X outputs implementing minterms. D 4 A 2 D 3 A X D 2 Ø The programmable "OR“ X X B A 1 D 1 array uses a single line to X A 0 D 0 C represent all inputs to an OR gate. An “X” in the array corresponds to attaching the minterm to the OR F 0 Ø Read Example: For input (A 2, A 1, A 0) F 2 F 1 F 3 = 011, output is (F 3, F 2, F 1, F 0 ) = 0011. Ø What are functions F 3, F 2 , F 1 and F 0 in terms of (A 2, A 1, A 0)? ELECT 90 X

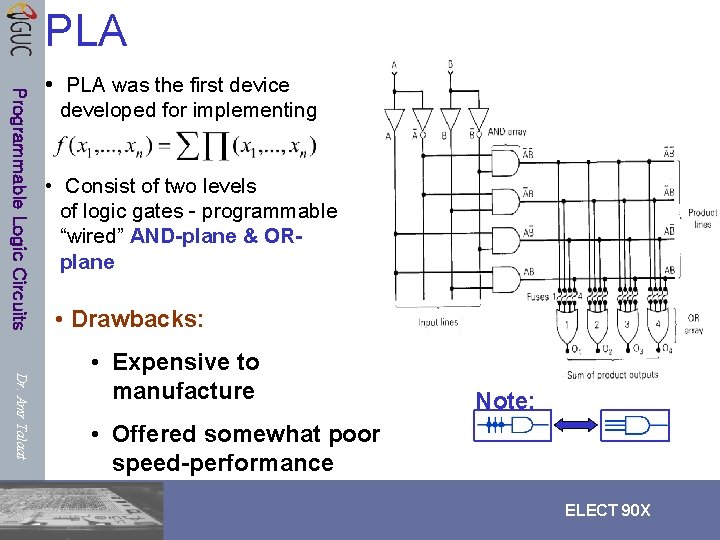

PLA Programmable Logic Circuits • PLA was the first device developed for implementing • Consist of two levels of logic gates - programmable “wired” AND-plane & ORplane • Drawbacks: Dr. Amr Talaat • Expensive to manufacture Note: • Offered somewhat poor speed-performance ELECT 90 X

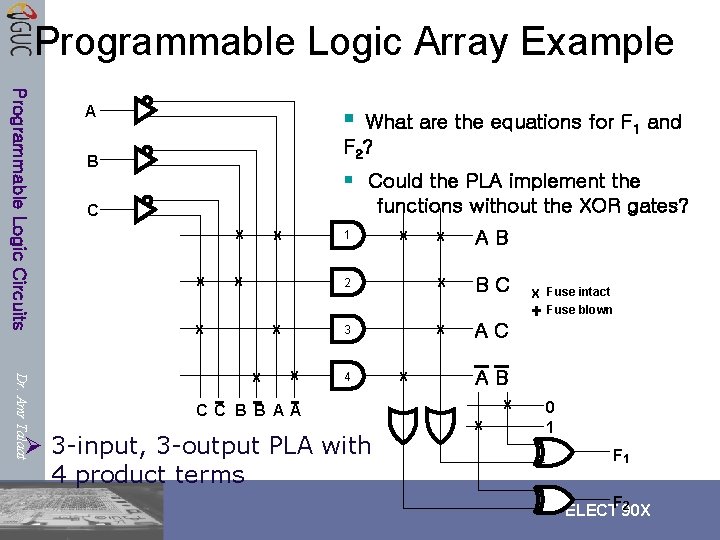

Programmable Logic Array Example Programmable Logic Circuits A § What are the equations for F 1 and F 2 ? B § Could the PLA implement the functions without the XOR gates? C X X X Dr. Amr Talaat X X AB 2 X BC 3 X AC 1 X X 4 C C B B AA Ø 3 -input, 3 -output PLA with 4 product terms X X X Fuse intact Fuse blown AB X X 0 1 F 2 ELECT 90 X

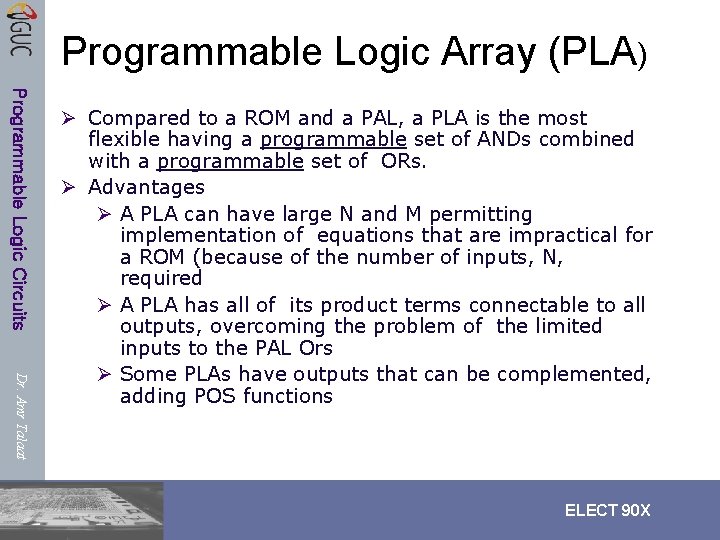

Programmable Logic Array (PLA) Programmable Logic Circuits Dr. Amr Talaat Ø Compared to a ROM and a PAL, a PLA is the most flexible having a programmable set of ANDs combined with a programmable set of ORs. Ø Advantages Ø A PLA can have large N and M permitting implementation of equations that are impractical for a ROM (because of the number of inputs, N, required Ø A PLA has all of its product terms connectable to all outputs, overcoming the problem of the limited inputs to the PAL Ors Ø Some PLAs have outputs that can be complemented, adding POS functions ELECT 90 X

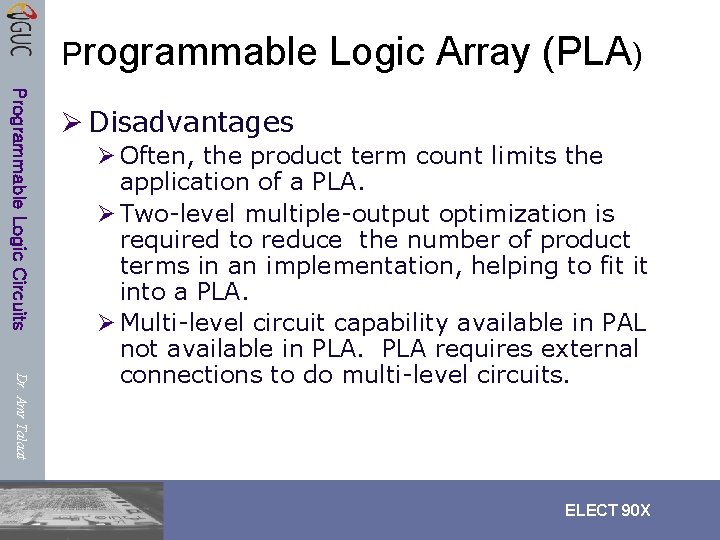

Programmable Logic Array (PLA) Programmable Logic Circuits Ø Disadvantages Dr. Amr Talaat Ø Often, the product term count limits the application of a PLA. Ø Two-level multiple-output optimization is required to reduce the number of product terms in an implementation, helping to fit it into a PLA. Ø Multi-level circuit capability available in PAL not available in PLA requires external connections to do multi-level circuits. ELECT 90 X

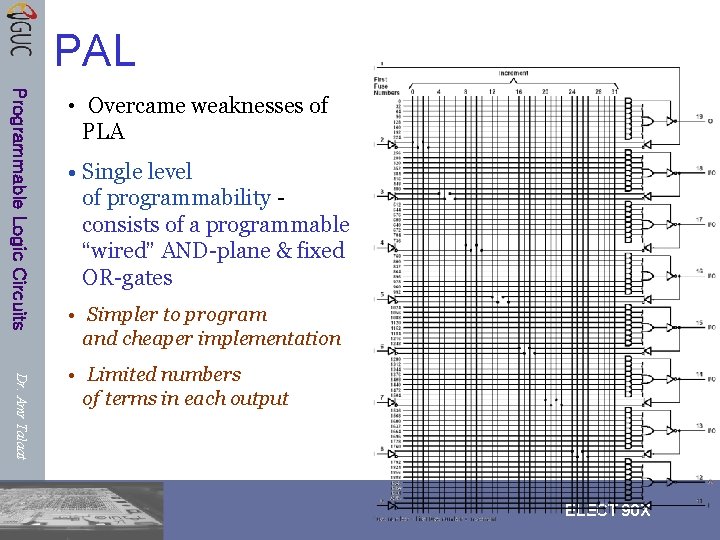

PAL Programmable Logic Circuits • Overcame weaknesses of PLA • Single level of programmability consists of a programmable “wired” AND-plane & fixed OR-gates • Simpler to program and cheaper implementation Dr. Amr Talaat • Limited numbers of terms in each output ELECT 90 X

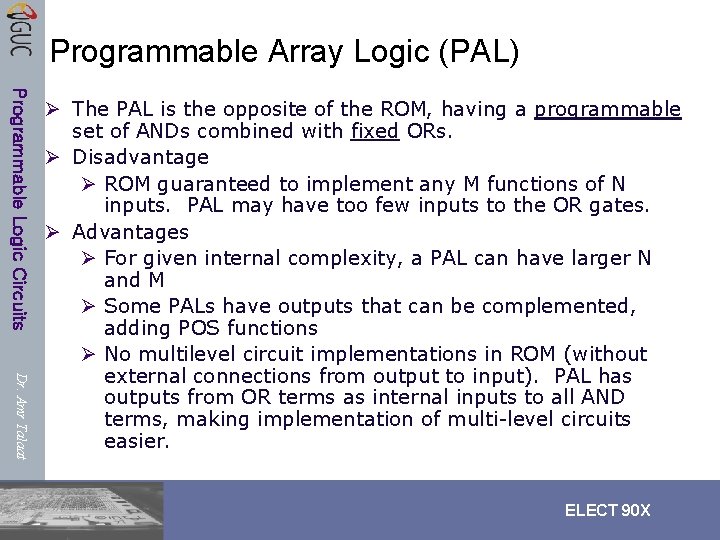

Programmable Array Logic (PAL) Programmable Logic Circuits Dr. Amr Talaat Ø The PAL is the opposite of the ROM, having a programmable set of ANDs combined with fixed ORs. Ø Disadvantage Ø ROM guaranteed to implement any M functions of N inputs. PAL may have too few inputs to the OR gates. Ø Advantages Ø For given internal complexity, a PAL can have larger N and M Ø Some PALs have outputs that can be complemented, adding POS functions Ø No multilevel circuit implementations in ROM (without external connections from output to input). PAL has outputs from OR terms as internal inputs to all AND terms, making implementation of multi-level circuits easier. ELECT 90 X

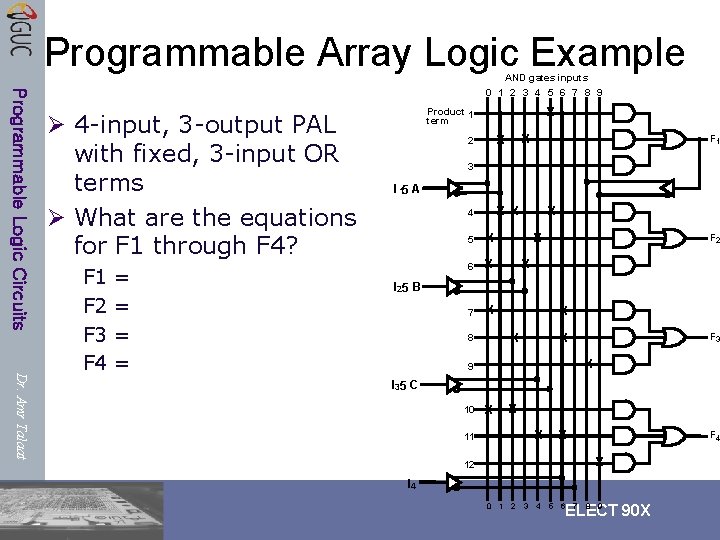

Programmable Array Logic Example X 2 F 1 3 I 15 A X X X 6 X 7 F 2 X 5 X 4 X X I 25 B X X 8 X F 3 X 9 I 35 C X X F 4 X 11 X 10 X Dr. Amr Talaat F 1 = F 2 = F 3 = F 4 = Product 1 term X Ø 4 -input, 3 -output PAL with fixed, 3 -input OR terms Ø What are the equations for F 1 through F 4? X Programmable Logic Circuits AND gates inputs 0 1 2 3 4 5 6 7 8 9 12 I 4 0 1 2 3 4 ELECT 90 X 5 6 7 8 9

Programmable Logic Devices (PLD) Programmable Logic Circuits Dr. Amr Talaat ELECT 90 X

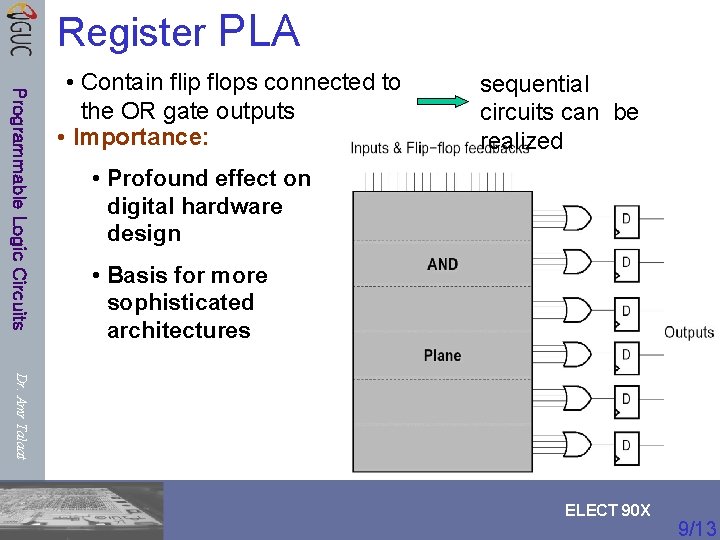

Register PLA Programmable Logic Circuits • Contain flip flops connected to the OR gate outputs • Importance: sequential circuits can be realized • Profound effect on digital hardware design • Basis for more sophisticated architectures Dr. Amr Talaat ELECT 90 X 9/13

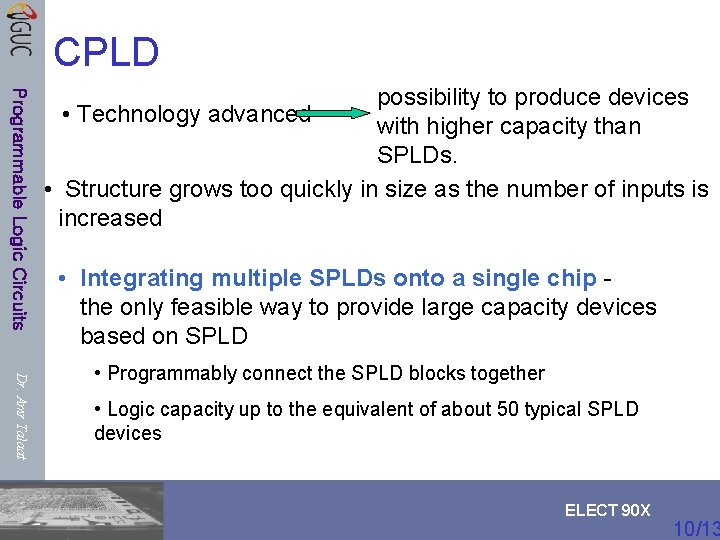

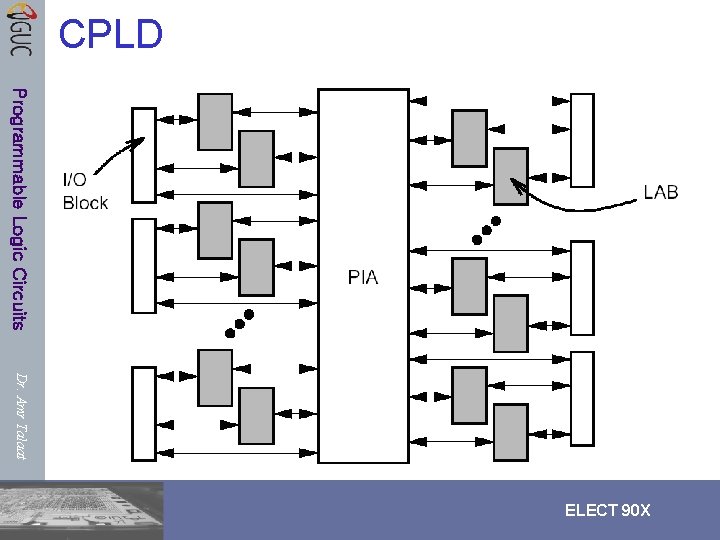

CPLD Programmable Logic Circuits possibility to produce devices • Technology advanced with higher capacity than SPLDs. • Structure grows too quickly in size as the number of inputs is increased • Integrating multiple SPLDs onto a single chip the only feasible way to provide large capacity devices based on SPLD Dr. Amr Talaat • Programmably connect the SPLD blocks together • Logic capacity up to the equivalent of about 50 typical SPLD devices ELECT 90 X 10/13

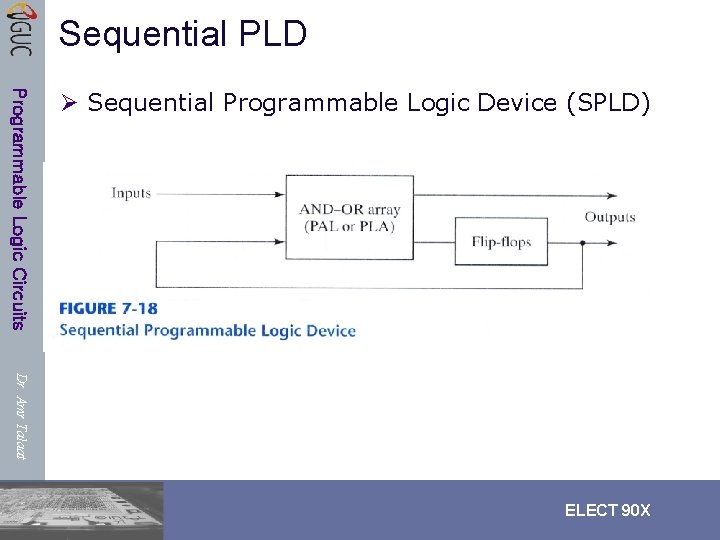

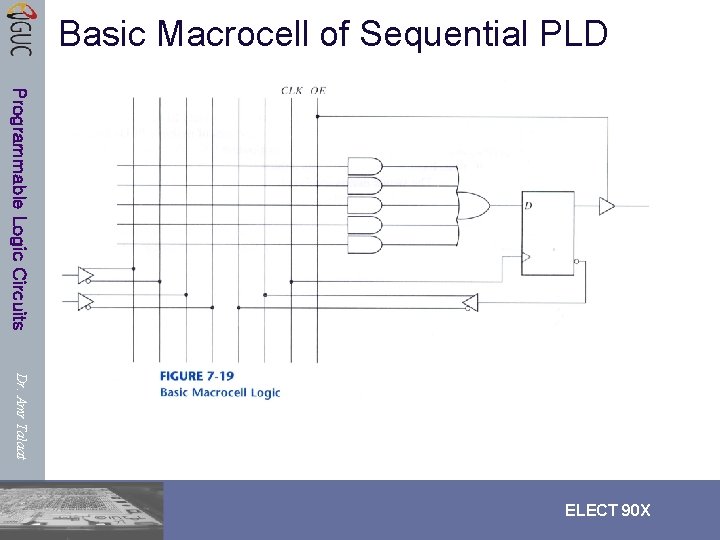

Sequential PLD Programmable Logic Circuits Ø Sequential Programmable Logic Device (SPLD) Dr. Amr Talaat ELECT 90 X

Basic Macrocell of Sequential PLD Programmable Logic Circuits Dr. Amr Talaat ELECT 90 X

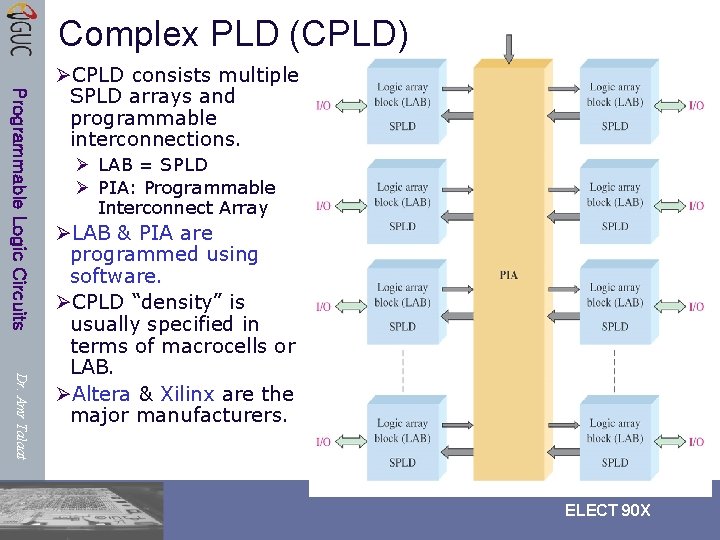

Complex PLD (CPLD) Programmable Logic Circuits ØCPLD consists multiple SPLD arrays and programmable interconnections. Ø LAB = SPLD Ø PIA: Programmable Interconnect Array Dr. Amr Talaat ØLAB & PIA are programmed using software. ØCPLD “density” is usually specified in terms of macrocells or LAB. ØAltera & Xilinx are the major manufacturers. ELECT 90 X

CPLD Programmable Logic Circuits Dr. Amr Talaat ELECT 90 X

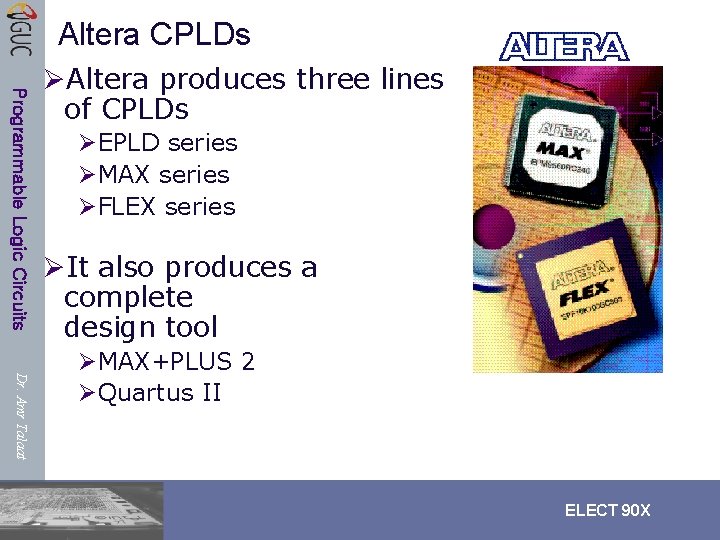

Altera CPLDs Programmable Logic Circuits ØAltera produces three lines of CPLDs ØEPLD series ØMAX series ØFLEX series ØIt also produces a complete design tool Dr. Amr Talaat ØMAX+PLUS 2 ØQuartus II ELECT 90 X

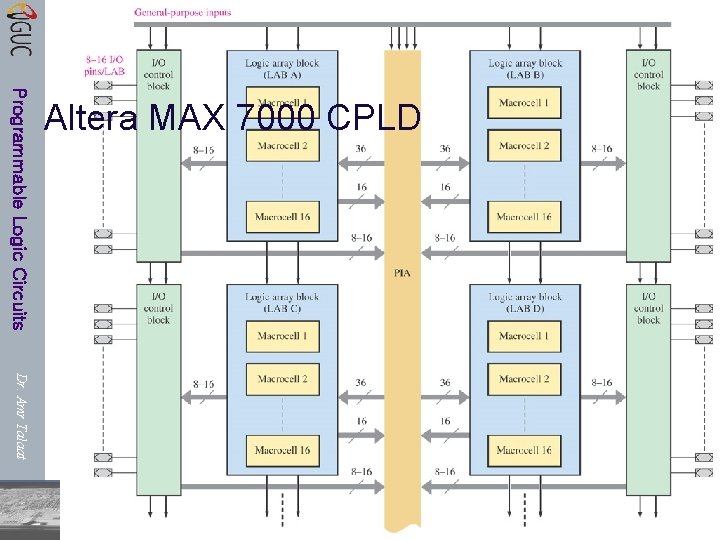

Programmable Logic Circuits Altera MAX 7000 CPLD Dr. Amr Talaat ELECT 90 X

Xilinx CPLDs Programmable Logic Circuits Ø Cool. Runner II, XC 9500 Ø XC 9500 is similar to MAX 7000, has PAL architecture Ø Cool. Runner II has PLA architecture Dr. Amr Talaat ELECT 90 X

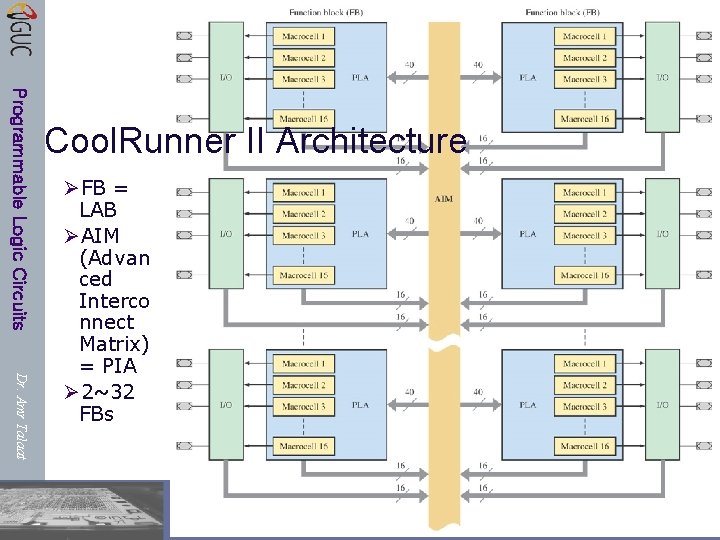

Programmable Logic Circuits Cool. Runner II Architecture Dr. Amr Talaat ØFB = LAB ØAIM (Advan ced Interco nnect Matrix) = PIA Ø 2~32 FBs ELECT 90 X

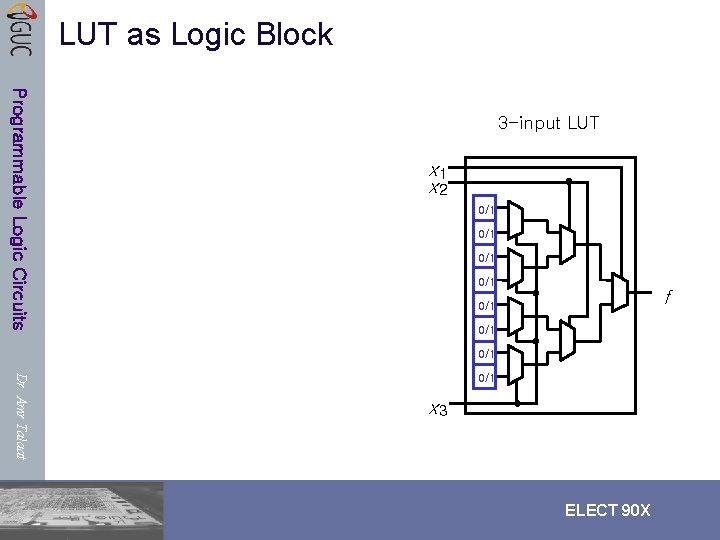

FPGA Programmable Logic Circuits Ø Provides logic blocks instead of AND or NAND plane Ø Typical logic blocks is LUT Ø Volatile devices Ø Programmable read-only memory (PROM) can be used to make it nonvolatile Dr. Amr Talaat ELECT 90 X

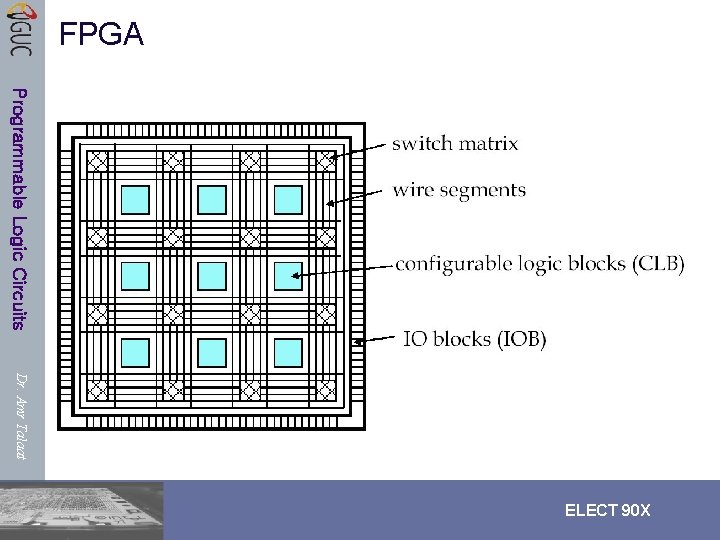

FPGA Programmable Logic Circuits • Difficult extending CPLDs architectures to higher densities - a different approach is needed • FPGAs comprise an array of uncommited circuit elements, called logic blocks, and interconnect resources • FPGA configuration is performed through programming by the end user. Dr. Amr Talaat ELECT 90 X

FPGA Programmable Logic Circuits Dr. Amr Talaat ELECT 90 X

LUT as Logic Block Programmable Logic Circuits 3 -input LUT x 1 x 2 0/1 0/1 f 0/1 0/1 Dr. Amr Talaat 0/1 x 3 ELECT 90 X

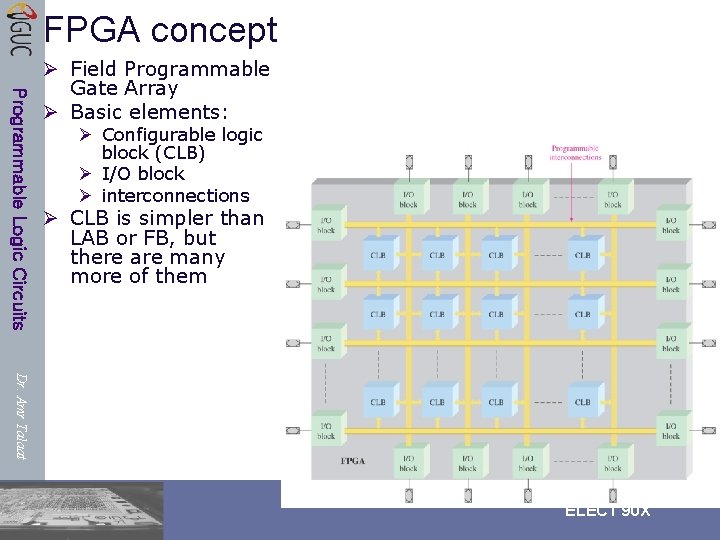

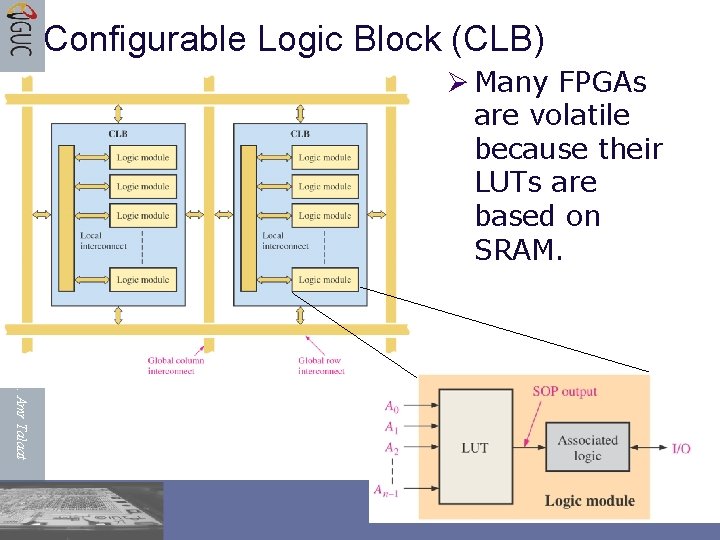

FPGA concept Programmable Logic Circuits Ø Field Programmable Gate Array Ø Basic elements: Ø Configurable logic block (CLB) Ø I/O block Ø interconnections Ø CLB is simpler than LAB or FB, but there are many more of them Dr. Amr Talaat ELECT 90 X

Configurable Logic Block (CLB) Programmable Logic Circuits Ø Many FPGAs are volatile because their LUTs are based on SRAM. Dr. Amr Talaat ELECT 90 X

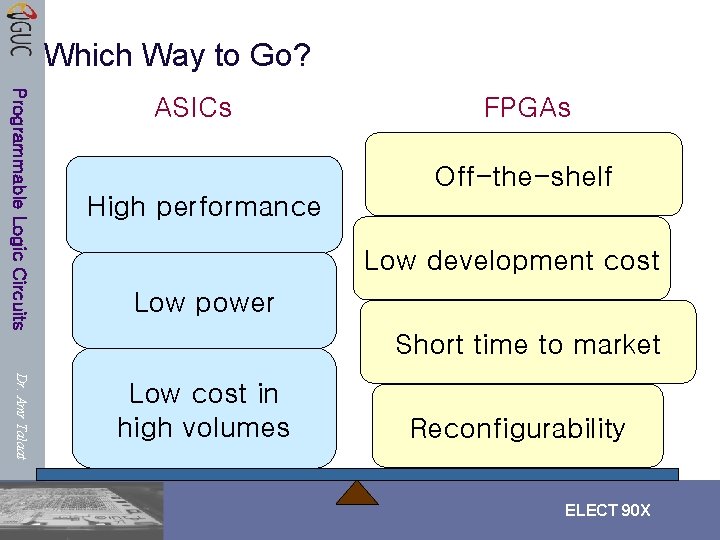

Which Way to Go? Programmable Logic Circuits High performance Dr. Amr Talaat Low cost in high volumes ASICs FPGAs Off-the-shelf Low development cost Low power Short time to market Reconfigurability ELECT 90 X

- Slides: 51