Eine elektronische Schaltung von der Idee bis zum

Eine elektronische Schaltung von der Idee bis zum Einbau am Experiment H. Leich: Einführung Schaltungsentwicklung Layout-Bearbeitung W. Philipp Technologische Umsetzung Technical seminar June 2005

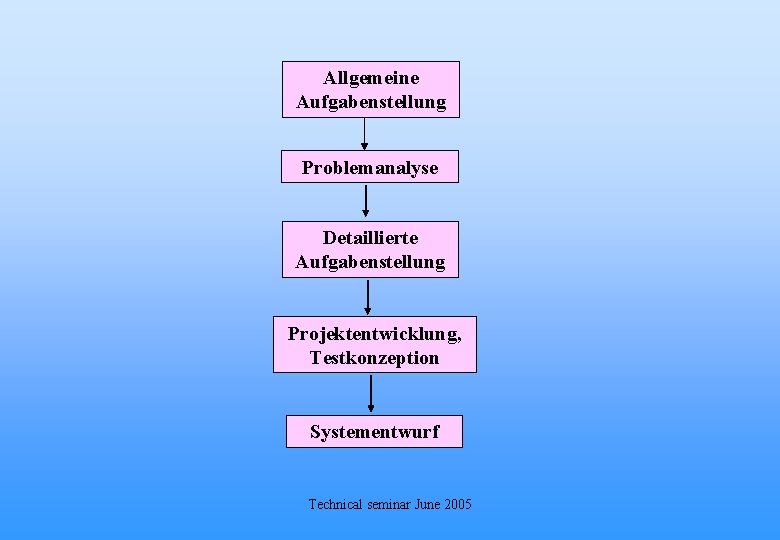

Allgemeine Aufgabenstellung Problemanalyse Detaillierte Aufgabenstellung Projektentwicklung, Testkonzeption Systementwurf Technical seminar June 2005

Ein Projekt „Interlock für die XFEL-RF-Station“ Ø 1. Generation: erfüllt die Grundfunktionen Ø 2. Generation: Funktionserweiterung, komfortable Anbindung an DOOCS über Metaserver Ø 3. Generation (im Bau): für den Einsatz bei XFEL ausgerichtet; modular; flexibel; Softwareanbindung über Standardprotokoll Export der Zeuthener Lösung nach HH Technical seminar June 2005

“The TTF 2 / XFEL RF Station Interlock: Requirements and Implementation” 1. Requirements 2. Implementation Details 3. System Modules • Crate, Power supply, Slow control • Controller • Digital Input/Output • Analog Input/Output • Digital IO for Light Links • Analog Input Module with Window Comparator Functionality 4. Control Functions 5. Interface to a higher level Control System (DOOCS) 6. Design documents Technical seminar June 2005

Architecture Overview Interlock Controller Pure Hardware Progr. Processor Hardwired Interlock Logic Interlock Status Bus Slave Expansion Board (optional) Backplane 32 Bit RISC CPU (NIOS-II) Slave … Module Technical seminar June 2005 Slave Module Processor Bus, Interrrupt and misc. Busses

Controller Architecture Cyclone-II EP 2 C 35 F 484 -C 7 Interlock Direct Data Out Interlock Service Request Time Mux Bus : Address Out Data In 32 -Bit RISC CPU 32 MByte SDRAM 64 MByte Internal SPI Interface Ethernet Controller Read Interlock Status, Channel masking, … 256 KByte MRAM RTC Hardwired Interlock Logic (connected to SPI) Data Bus Technical seminar June 2005 Address Bus External Devices Interlock Bus Interfaces: Control Bus, Time Multiplex Bus Service Request lines, … Cntrl Bus: Address Out Strb, We Data I/O NIOS-II Flash Memory

handle side A -inverted CPCI connector -no cables ! side B -CPCI Form -cable outlet Slotnumber: 0 1 2 3 . . . Technical seminar June 2005 19 20

PLD Design Simulation Bestellung BE Schaltungsentwicklung ØAnalog ØDigital ØMixed Simulation Layoutentwicklung Produktion PCB Bestücken und Löten Test der Schaltung Technical seminar June 2005 Testsoftware, Testhilfsmittel

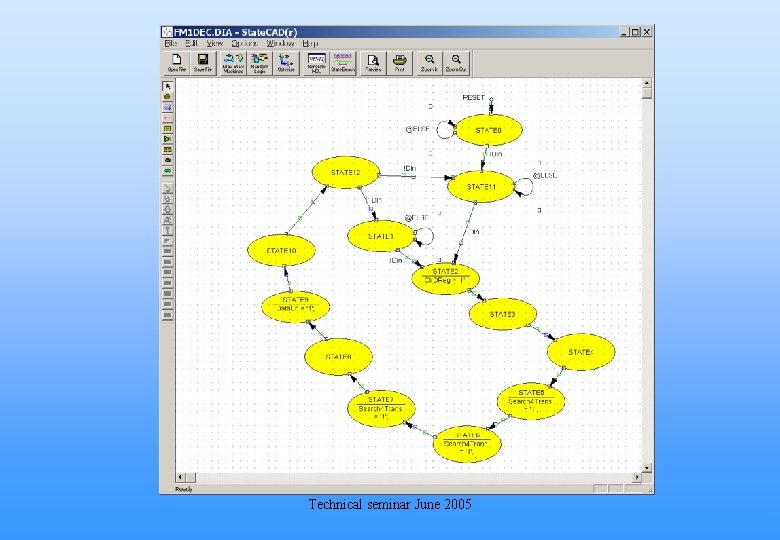

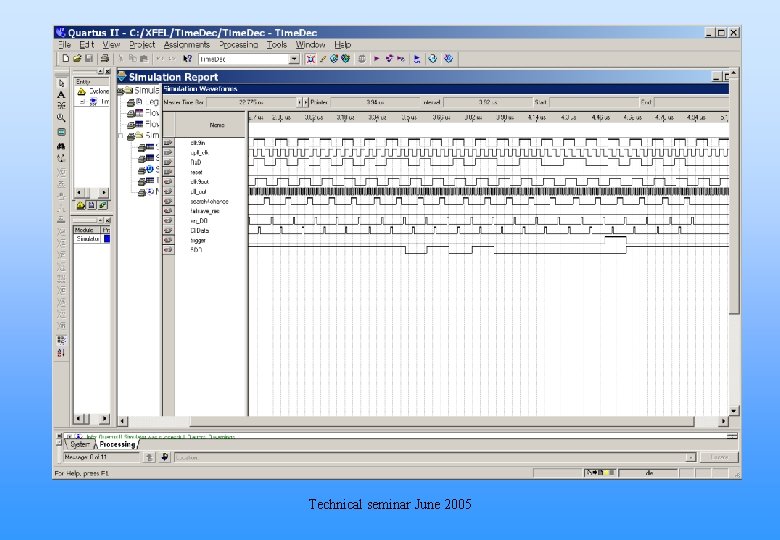

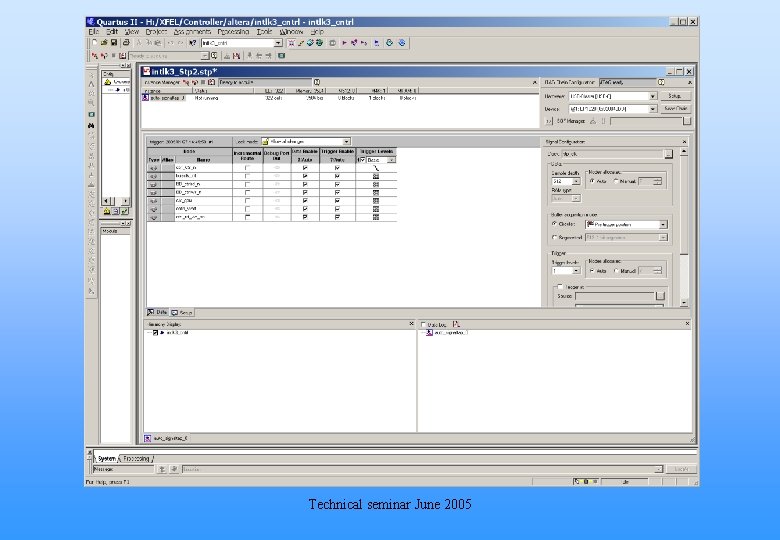

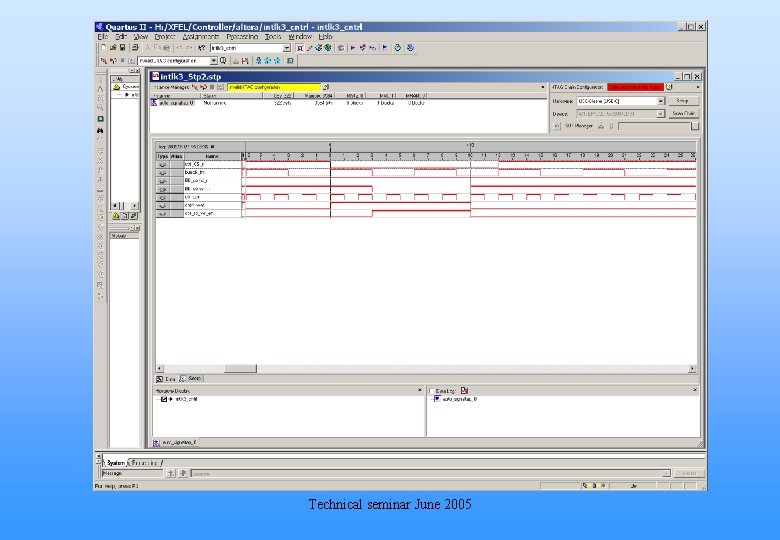

Hilfsmittel für den Entwurfsprozeß (I) Schaltungsentwurf: Ø Handzeichnung Ø Grafische Eingabe mittels CAD-Software ØBeschreibungssprache (VHDL, Verilog) Ø Zustandsdiagramm Verifizierung: Ø meist nur für Teile (Zustandsdiagramm, PLD) § Problem: Modelle! Ø Simulatoren: VHDL, Verilog § funktionelle Simulation § Zeitsimulation Technical seminar June 2005

Hilfsmittel für den Entwurfsprozeß (II) PLD Design: Ø Design tools der PLD-Hersteller (XILINX, ALTERA, LATTICE) Ø Design tools der CAD-Firmen (Mentor Graphics, Cadence, …) Ø Simulation ist ein muß! Layoutentwicklung: Ø Handzeichnung Ø Integrierte design tools von CAD-Firmen (Mentor Graphics, Cadence, Altium, …) Ø im DESY: ORCAD, Expedition, Protel, Eagle Technical seminar June 2005

Technical seminar June 2005

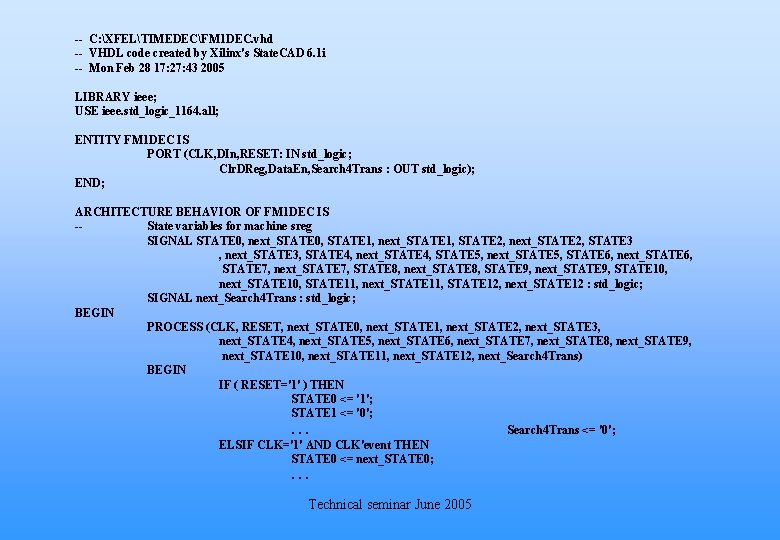

-- C: XFELTIMEDECFM 1 DEC. vhd -- VHDL code created by Xilinx's State. CAD 6. 1 i -- Mon Feb 28 17: 27: 43 2005 LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY FM 1 DEC IS PORT (CLK, DIn, RESET: IN std_logic; Clr. DReg, Data. En, Search 4 Trans : OUT std_logic); END; ARCHITECTURE BEHAVIOR OF FM 1 DEC IS -State variables for machine sreg SIGNAL STATE 0, next_STATE 0, STATE 1, next_STATE 1, STATE 2, next_STATE 2, STATE 3 , next_STATE 3, STATE 4, next_STATE 4, STATE 5, next_STATE 5, STATE 6, next_STATE 6, STATE 7, next_STATE 7, STATE 8, next_STATE 8, STATE 9, next_STATE 9, STATE 10, next_STATE 10, STATE 11, next_STATE 11, STATE 12, next_STATE 12 : std_logic; SIGNAL next_Search 4 Trans : std_logic; BEGIN PROCESS (CLK, RESET, next_STATE 0, next_STATE 1, next_STATE 2, next_STATE 3, next_STATE 4, next_STATE 5, next_STATE 6, next_STATE 7, next_STATE 8, next_STATE 9, next_STATE 10, next_STATE 11, next_STATE 12, next_Search 4 Trans) BEGIN IF ( RESET='1' ) THEN STATE 0 <= '1'; STATE 1 <= '0'; . . . Search 4 Trans <= '0'; ELSIF CLK='1' AND CLK'event THEN STATE 0 <= next_STATE 0; . . . Technical seminar June 2005

Technical seminar June 2005

Technical seminar June 2005

Technical seminar June 2005

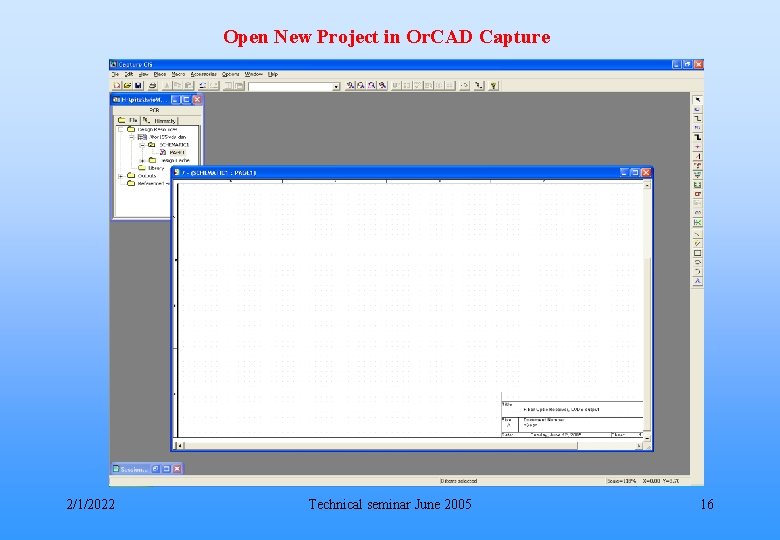

Open New Project in Or. CAD Capture 2/1/2022 Technical seminar June 2005 16

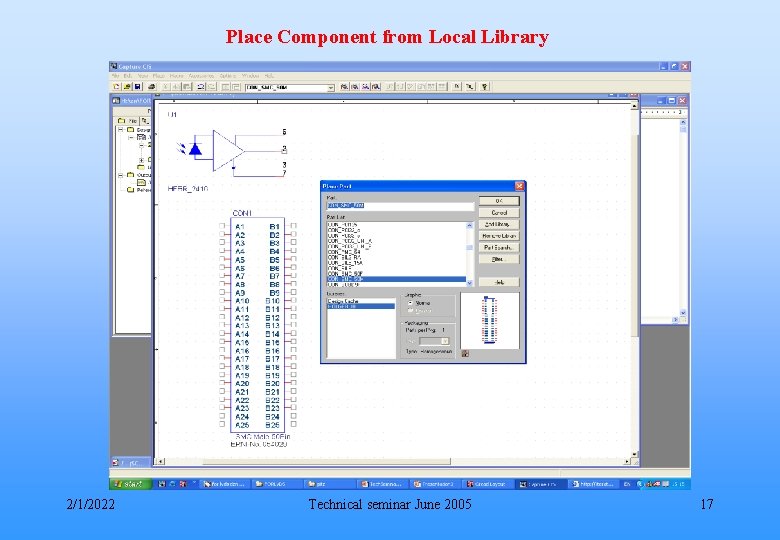

Place Component from Local Library 2/1/2022 Technical seminar June 2005 17

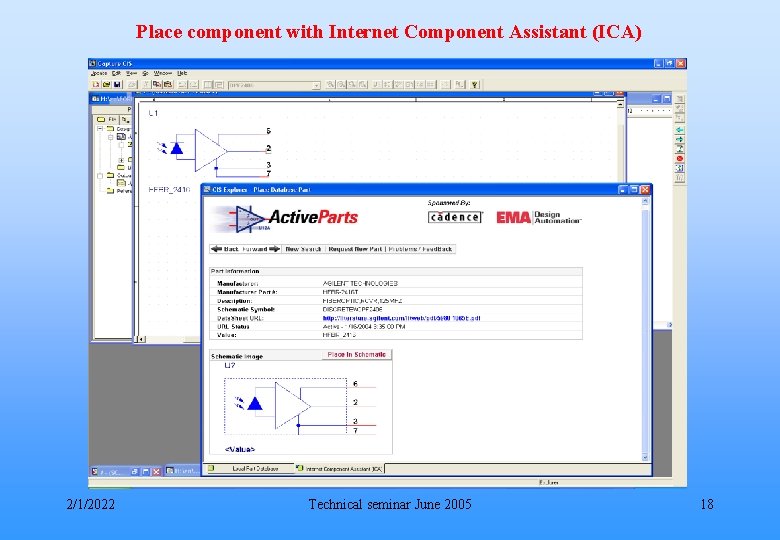

Place component with Internet Component Assistant (ICA) 2/1/2022 Technical seminar June 2005 18

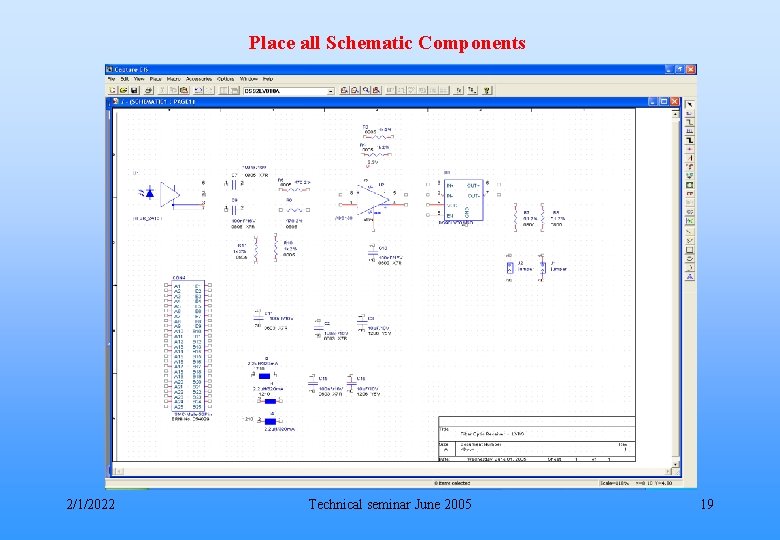

Place all Schematic Components 2/1/2022 Technical seminar June 2005 19

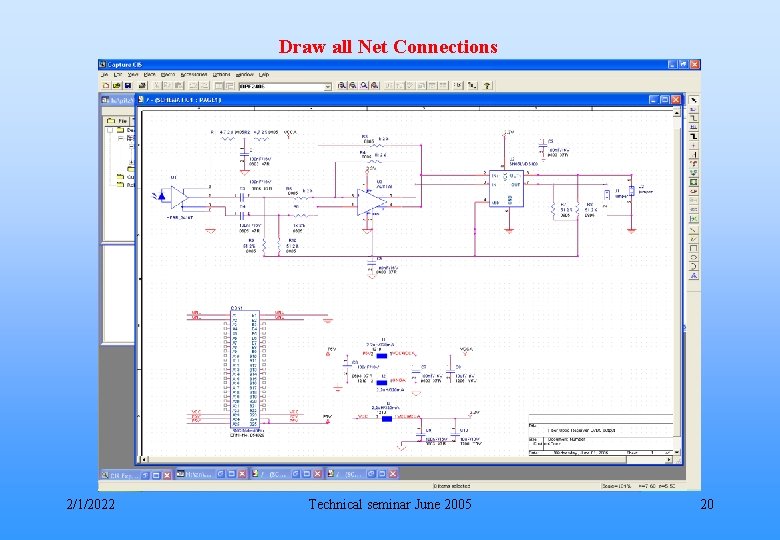

Draw all Net Connections 2/1/2022 Technical seminar June 2005 20

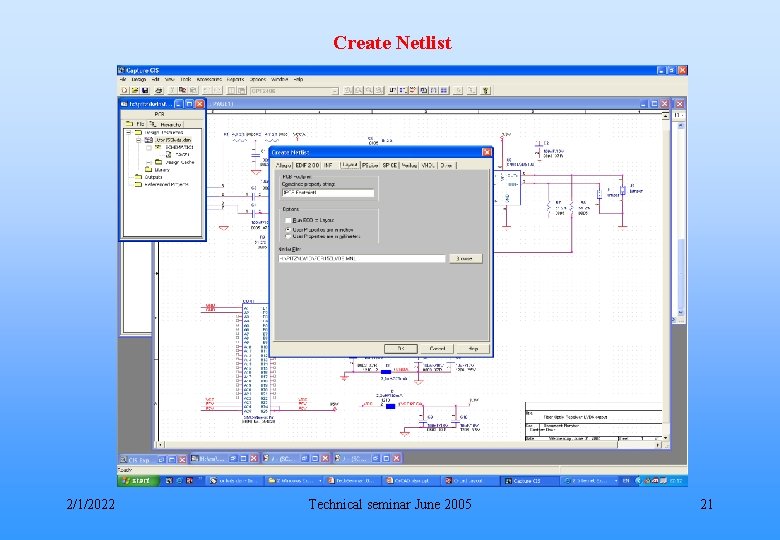

Create Netlist 2/1/2022 Technical seminar June 2005 21

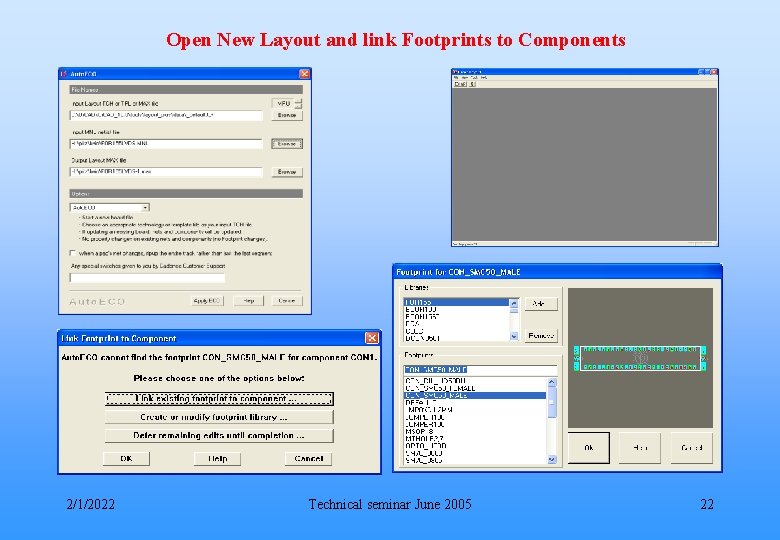

Open New Layout and link Footprints to Components 2/1/2022 Technical seminar June 2005 22

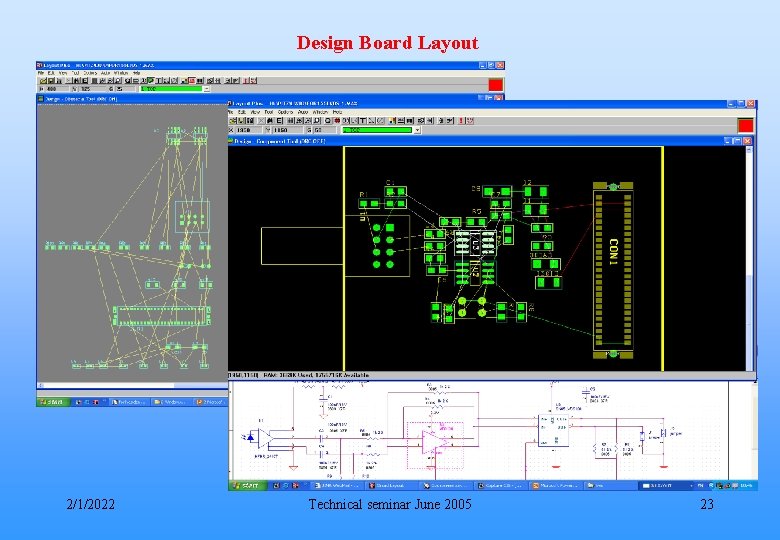

Design Board Layout 2/1/2022 Technical seminar June 2005 23

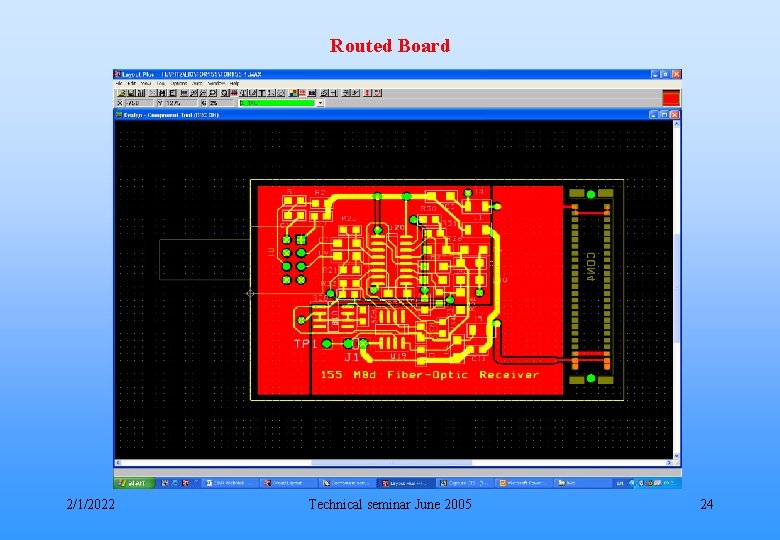

Routed Board 2/1/2022 Technical seminar June 2005 24

PLD Design Ø ALTERA: Quartus Ø XILINX: ISE Ø andere Technical seminar June 2005

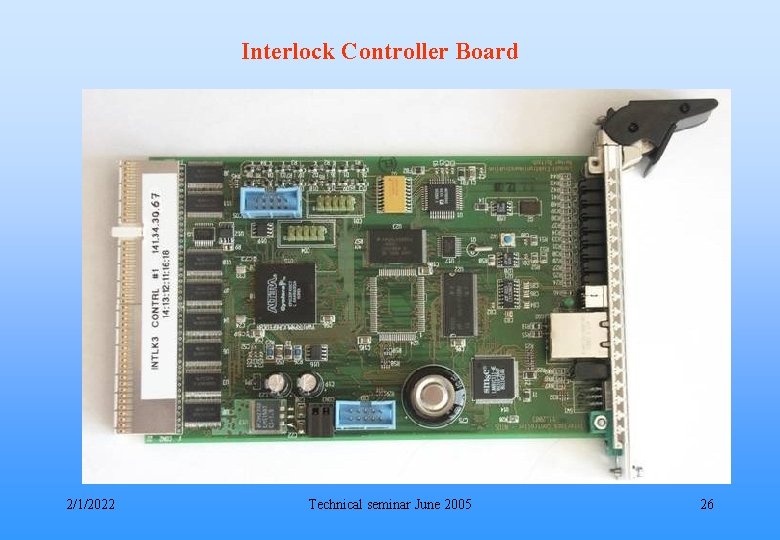

Interlock Controller Board 2/1/2022 Technical seminar June 2005 26

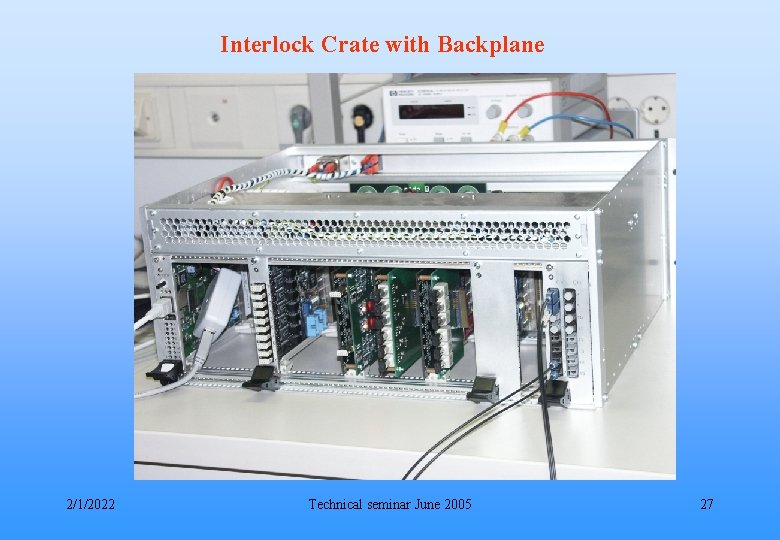

Interlock Crate with Backplane 2/1/2022 Technical seminar June 2005 27

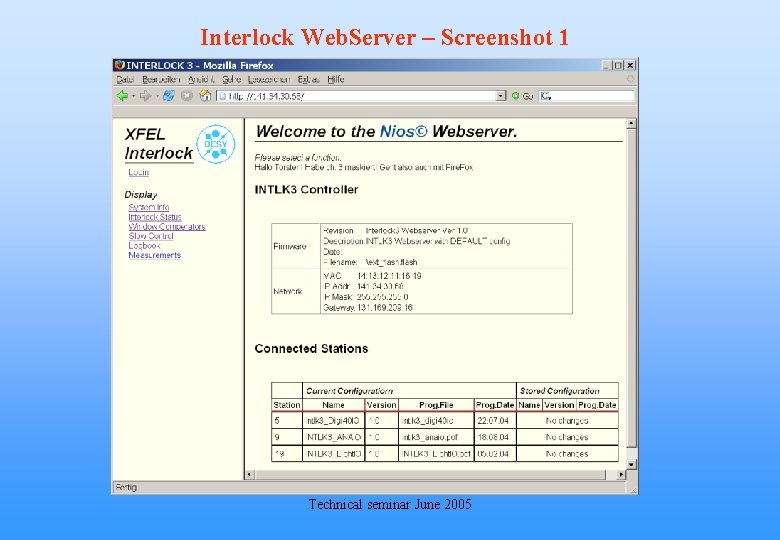

Interlock Web. Server – Screenshot 1 Technical seminar June 2005

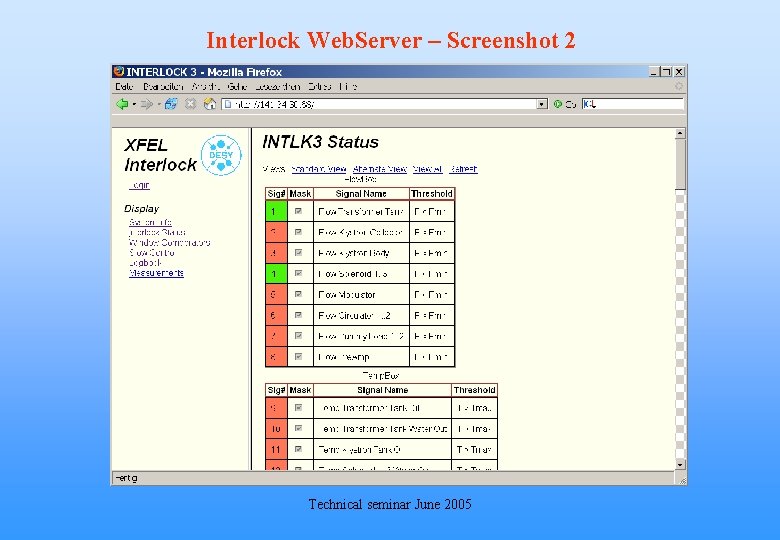

Interlock Web. Server – Screenshot 2 Technical seminar June 2005

- Slides: 29