EET 1131 Unit 6 ExclusiveOR and ExclusiveNOR Gates

- Slides: 35

EET 1131 Unit 6 Exclusive-OR and Exclusive-NOR Gates ¡ Read Kleitz, Chapter 6. Homework #6 and Lab #6 due next week. ¡ Quiz next week. ¡

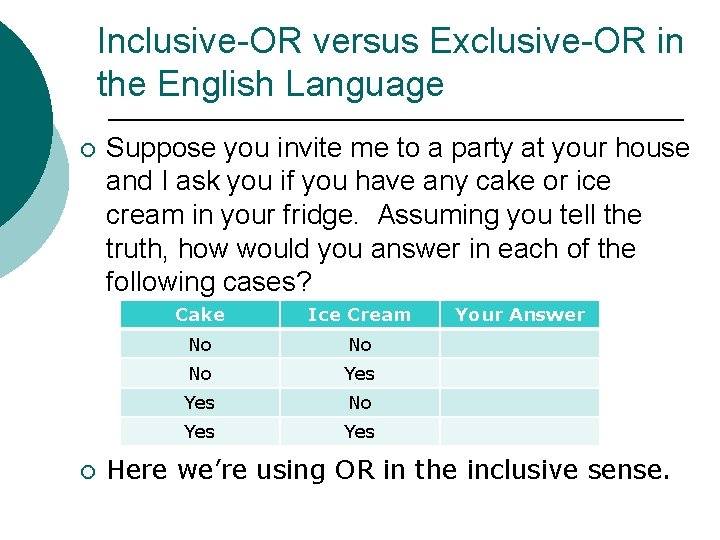

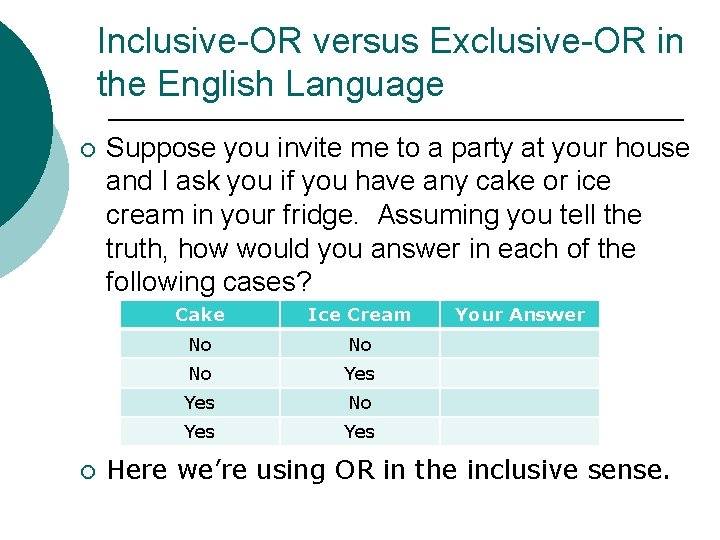

Inclusive-OR versus Exclusive-OR in the English Language ¡ ¡ Suppose you invite me to a party at your house and I ask you if you have any cake or ice cream in your fridge. Assuming you tell the truth, how would you answer in each of the following cases? Cake Ice Cream No No No Yes Yes Your Answer Here we’re using OR in the inclusive sense.

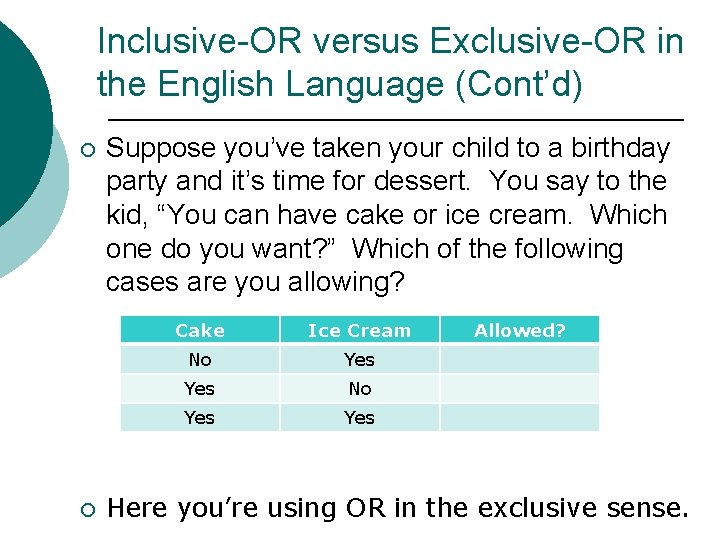

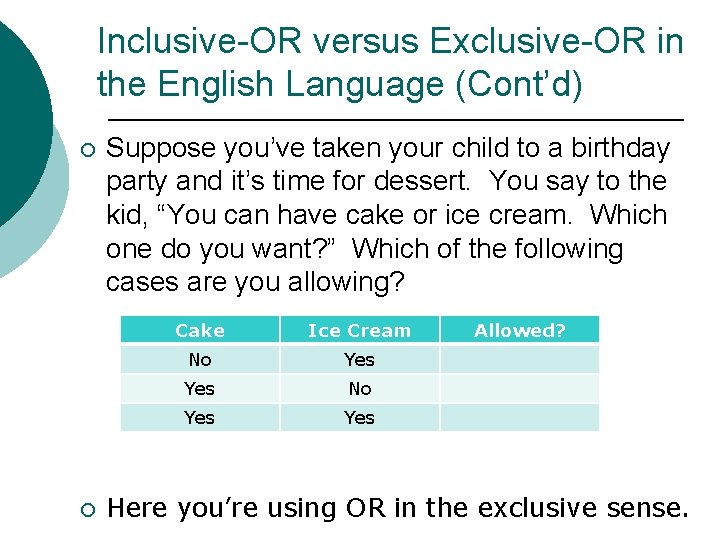

Inclusive-OR versus Exclusive-OR in the English Language (Cont’d) ¡ ¡ Suppose you’ve taken your child to a birthday party and it’s time for dessert. You say to the kid, “You can have cake or ice cream. Which one do you want? ” Which of the following cases are you allowing? Cake Ice Cream No Yes Yes Allowed? Here you’re using OR in the exclusive sense.

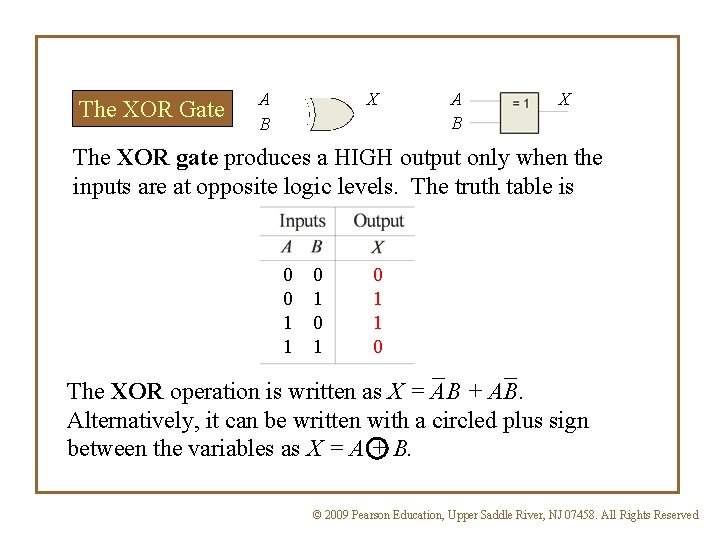

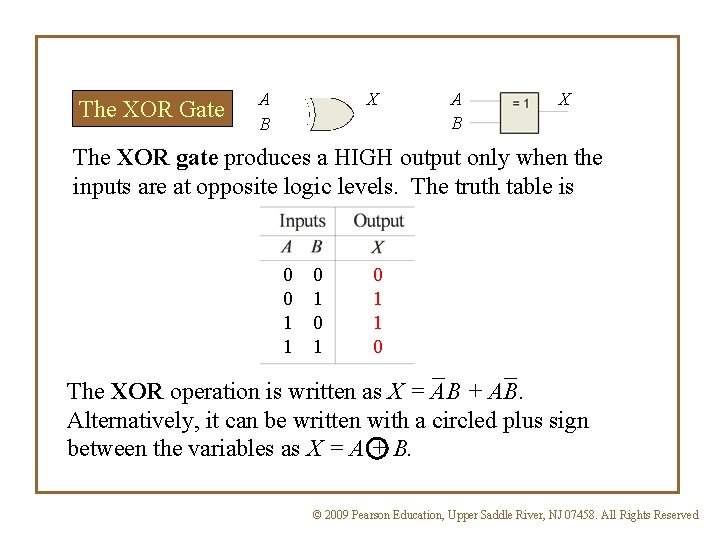

The XOR Gate A B X The XOR gate produces a HIGH output only when the inputs are at opposite logic levels. The truth table is 0 0 1 1 0 1 0 1 1 0 The XOR operation is written as X = AB + AB. Alternatively, it can be written with a circled plus sign between the variables as X = A + B. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

Applying Boolean-Algebra Rules to Expressions with XOR ¡ The “circle-OR” symbol doesn’t appear in any of our Boolean-algebra rules, so if you’re doing a Boolean simplifcation, write out the longer form shown above for XOR (AB + AB). ¡ We’ll do an example later.

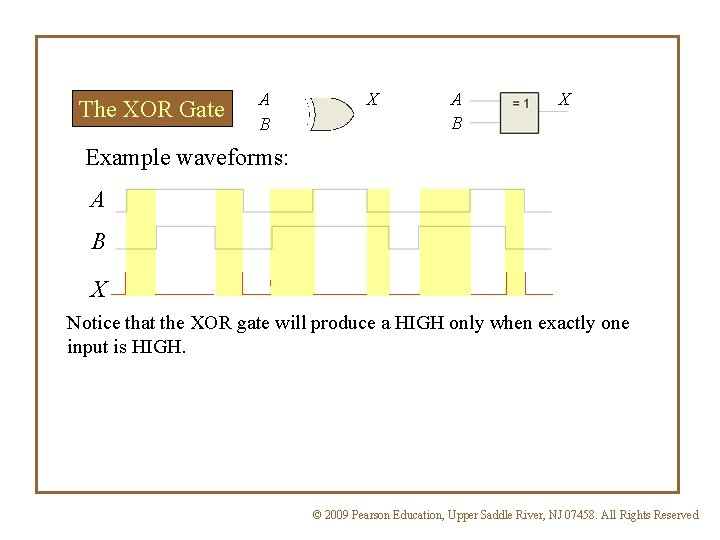

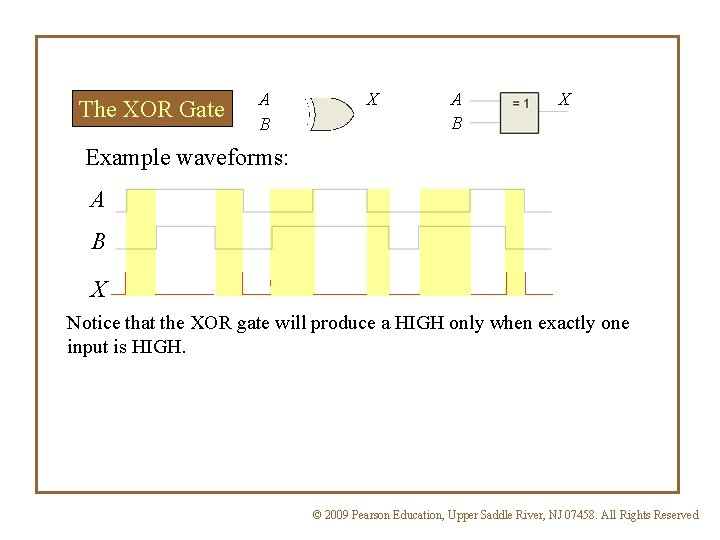

The XOR Gate A B X Example waveforms: A B X Notice that the XOR gate will produce a HIGH only when exactly one input is HIGH. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

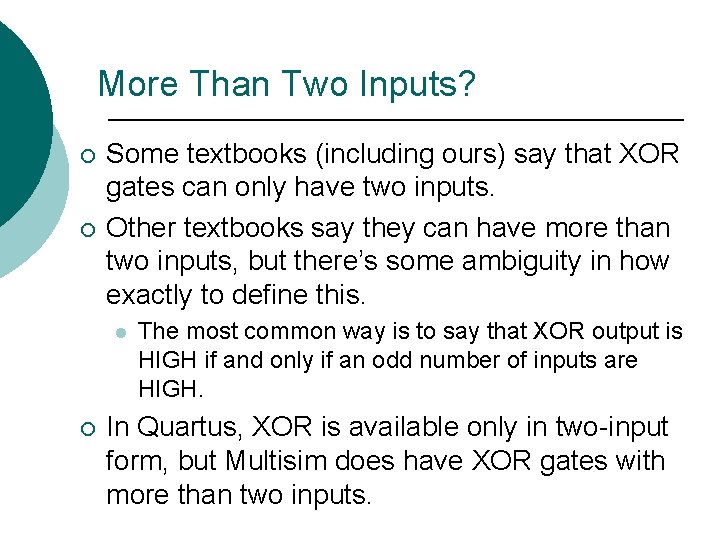

More Than Two Inputs? ¡ ¡ Some textbooks (including ours) say that XOR gates can only have two inputs. Other textbooks say they can have more than two inputs, but there’s some ambiguity in how exactly to define this. l ¡ The most common way is to say that XOR output is HIGH if and only if an odd number of inputs are HIGH. In Quartus, XOR is available only in two-input form, but Multisim does have XOR gates with more than two inputs.

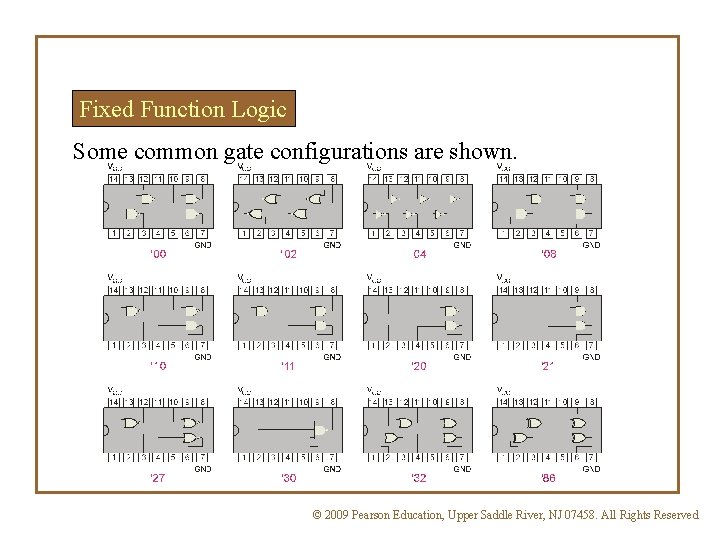

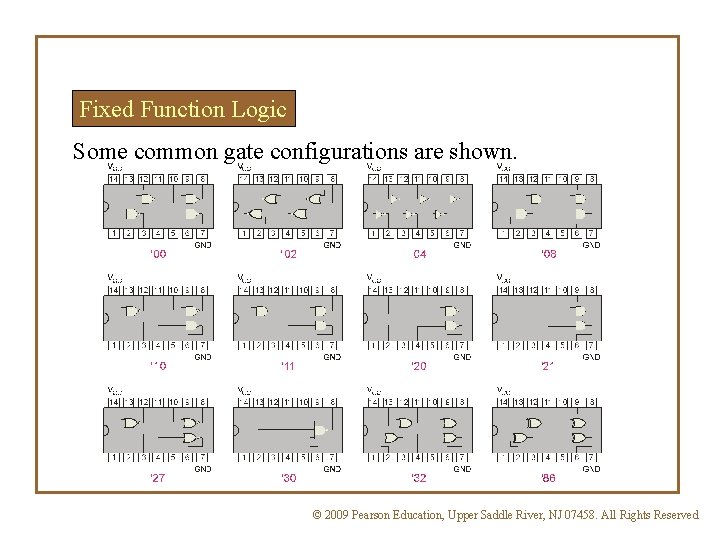

Fixed Function Logic Some common gate configurations are shown. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

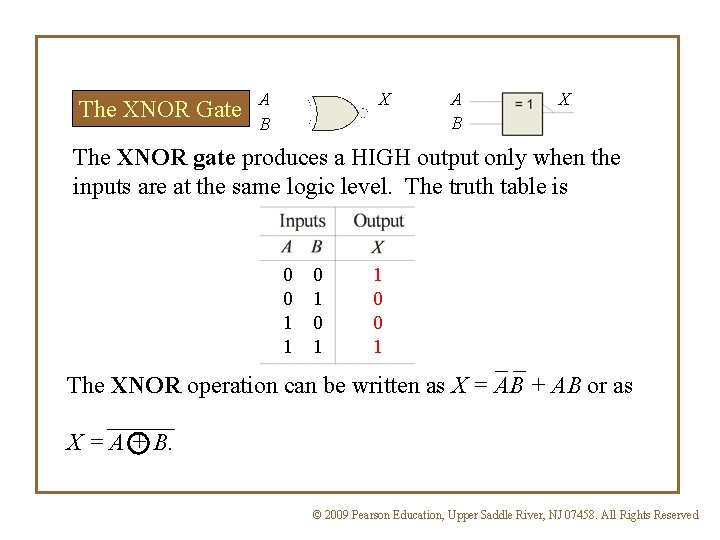

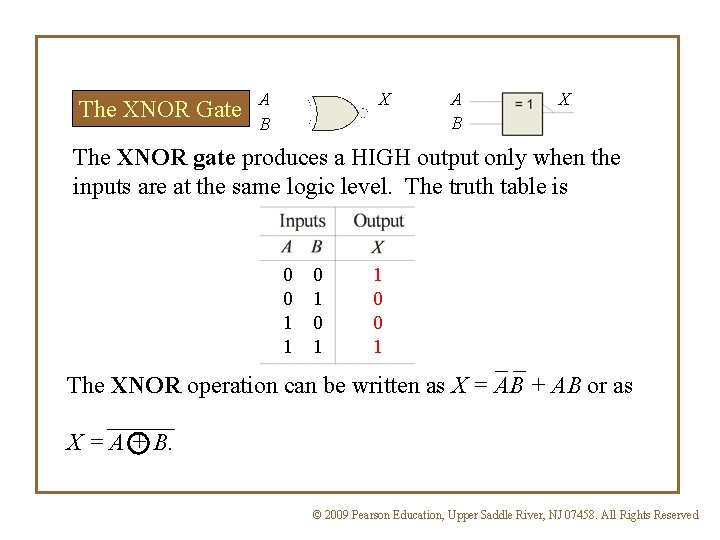

The XNOR Gate A B X The XNOR gate produces a HIGH output only when the inputs are at the same logic level. The truth table is 0 0 1 1 0 0 1 The XNOR operation can be written as X = AB + AB or as X = A + B. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

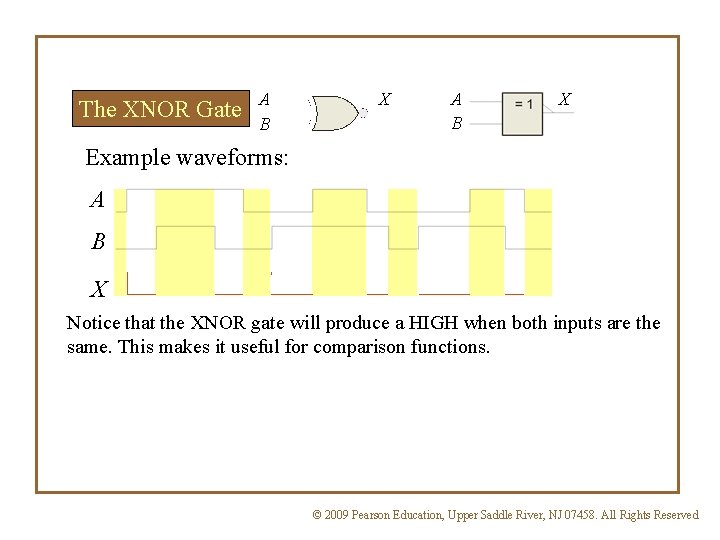

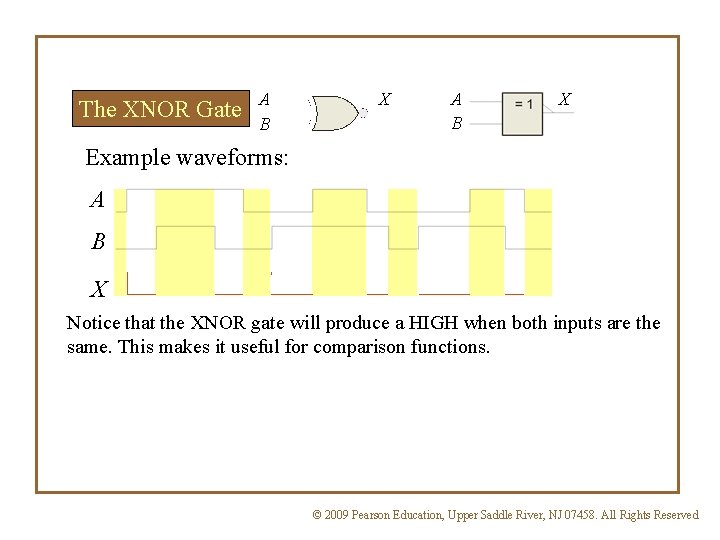

The XNOR Gate A B X Example waveforms: A B X Notice that the XNOR gate will produce a HIGH when both inputs are the same. This makes it useful for comparison functions. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

Applications of XOR and XNOR Gates ¡ Three 1. 2. 3. common applications: Comparators Controlled inverters Parity generation and checking

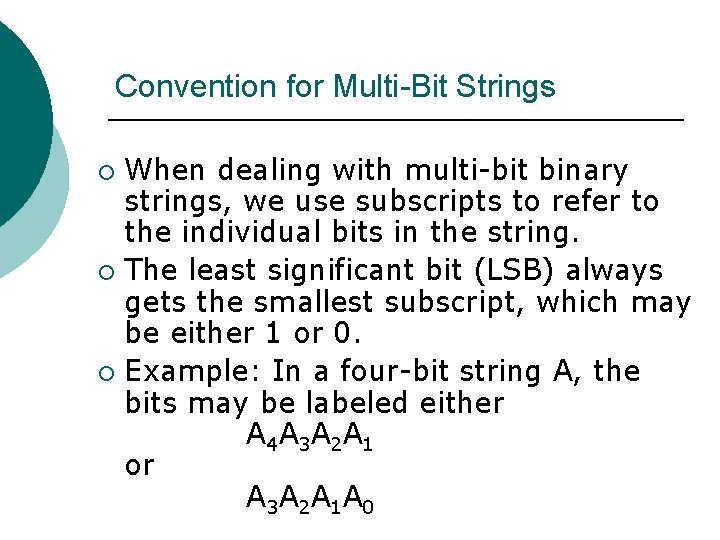

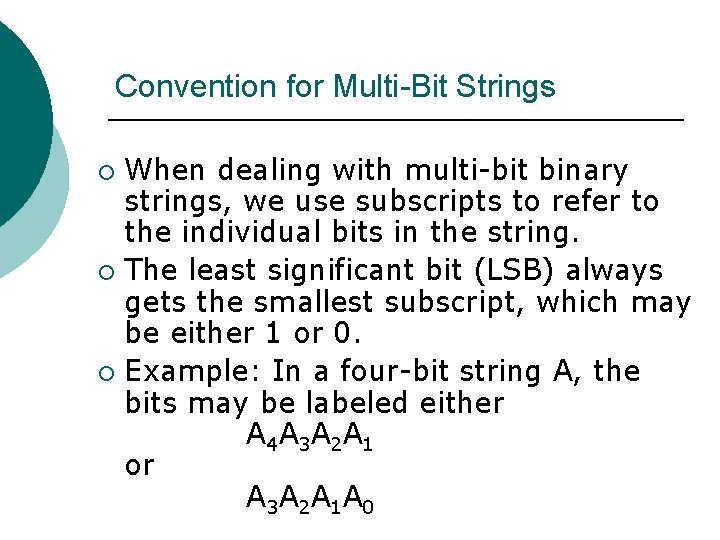

Convention for Multi-Bit Strings When dealing with multi-bit binary strings, we use subscripts to refer to the individual bits in the string. ¡ The least significant bit (LSB) always gets the smallest subscript, which may be either 1 or 0. ¡ Example: In a four-bit string A, the bits may be labeled either A 4 A 3 A 2 A 1 or A 3 A 2 A 1 A 0 ¡

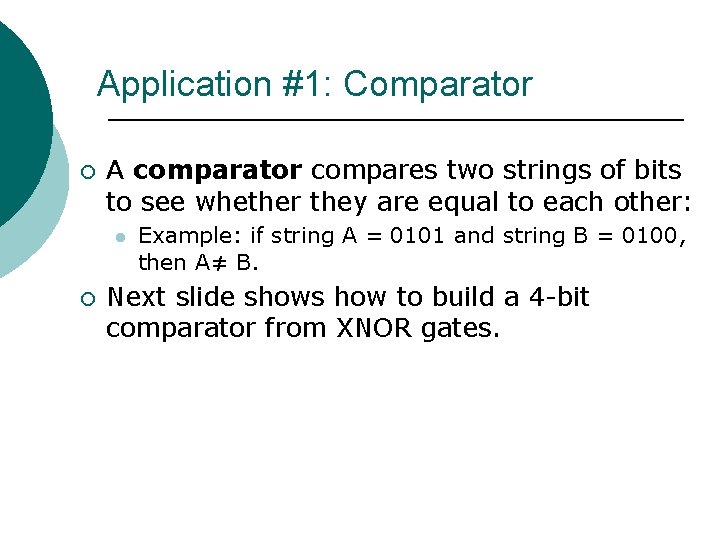

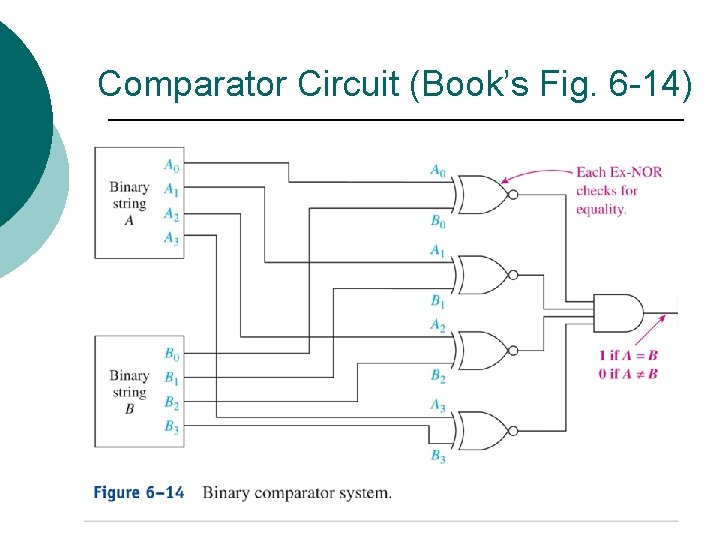

Application #1: Comparator ¡ A comparator compares two strings of bits to see whether they are equal to each other: l ¡ Example: if string A = 0101 and string B = 0100, then A≠ B. Next slide shows how to build a 4 -bit comparator from XNOR gates.

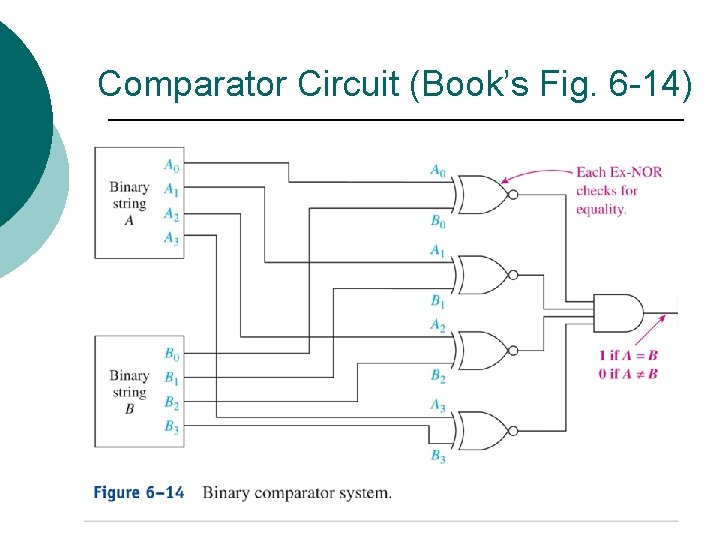

Comparator Circuit (Book’s Fig. 6 -14)

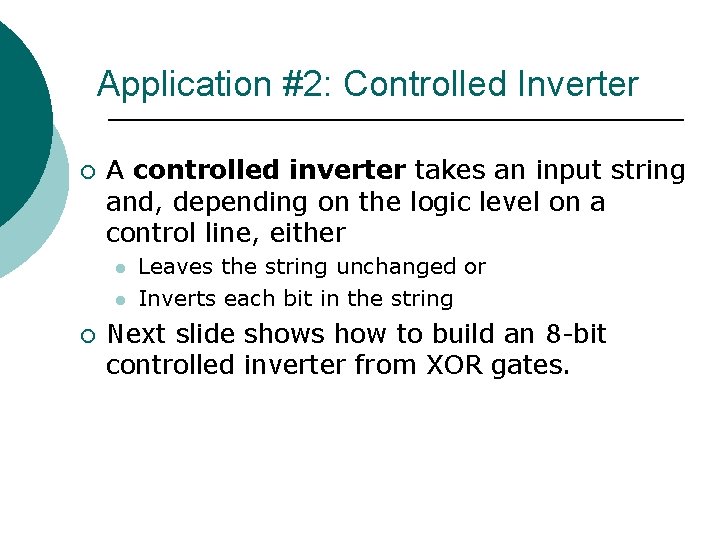

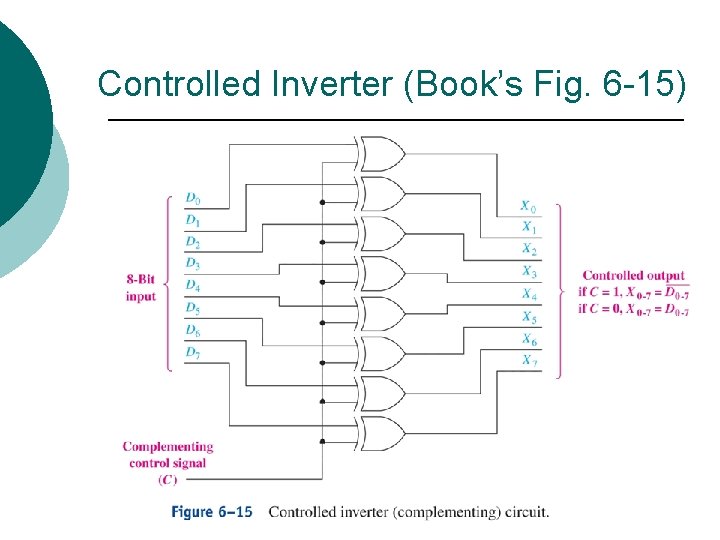

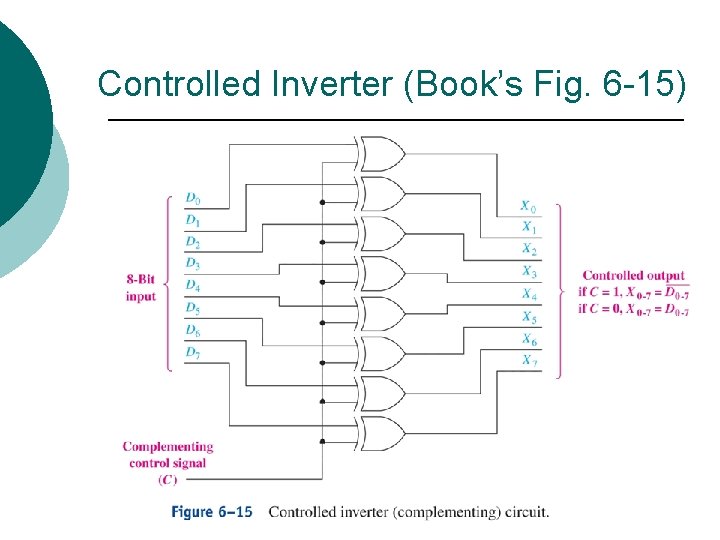

Application #2: Controlled Inverter ¡ A controlled inverter takes an input string and, depending on the logic level on a control line, either l l ¡ Leaves the string unchanged or Inverts each bit in the string Next slide shows how to build an 8 -bit controlled inverter from XOR gates.

Controlled Inverter (Book’s Fig. 6 -15)

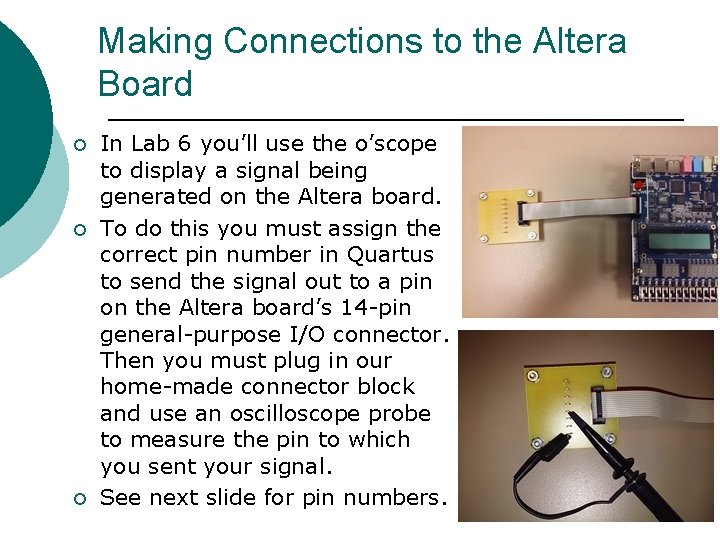

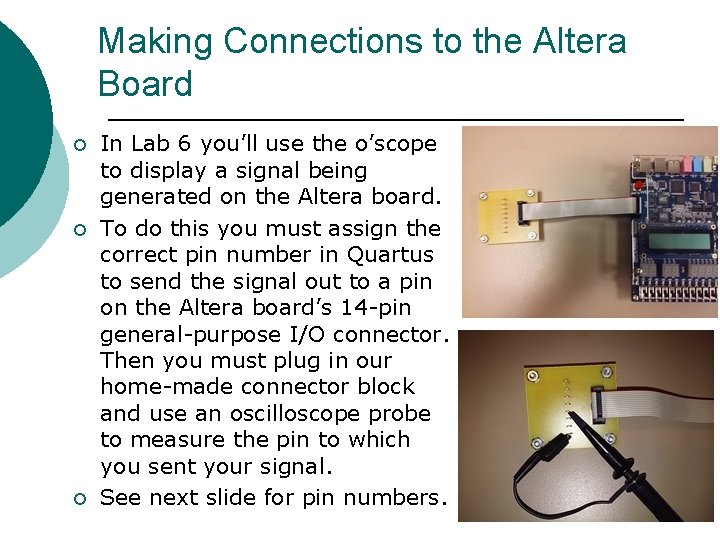

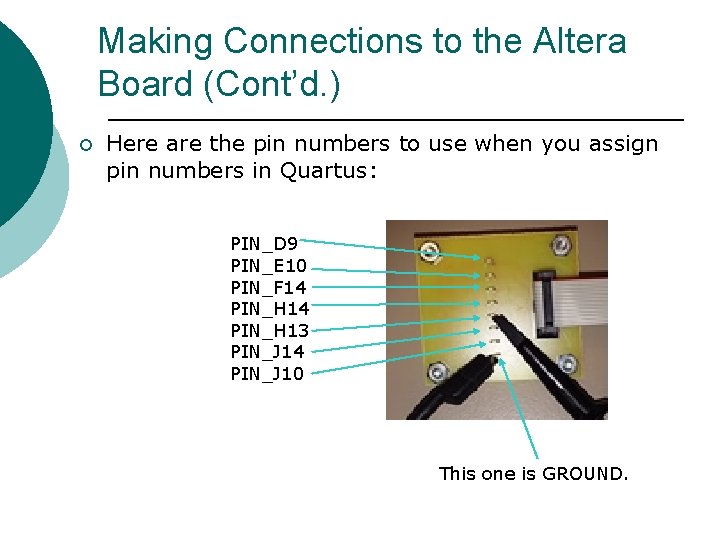

Making Connections to the Altera Board ¡ ¡ ¡ In Lab 6 you’ll use the o’scope to display a signal being generated on the Altera board. To do this you must assign the correct pin number in Quartus to send the signal out to a pin on the Altera board’s 14 -pin general-purpose I/O connector. Then you must plug in our home-made connector block and use an oscilloscope probe to measure the pin to which you sent your signal. See next slide for pin numbers.

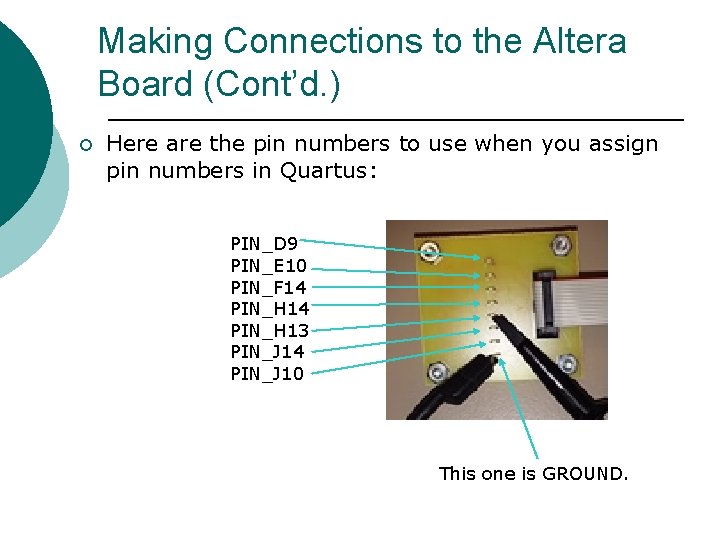

Making Connections to the Altera Board (Cont’d. ) ¡ Here are the pin numbers to use when you assign pin numbers in Quartus: PIN_D 9 PIN_E 10 PIN_F 14 PIN_H 13 PIN_J 14 PIN_J 10 This one is GROUND.

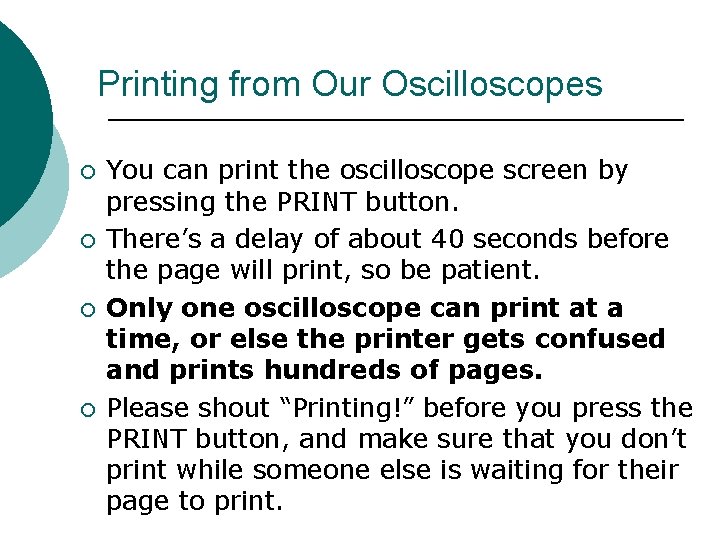

Printing from Our Oscilloscopes ¡ ¡ You can print the oscilloscope screen by pressing the PRINT button. There’s a delay of about 40 seconds before the page will print, so be patient. Only one oscilloscope can print at a time, or else the printer gets confused and prints hundreds of pages. Please shout “Printing!” before you press the PRINT button, and make sure that you don’t print while someone else is waiting for their page to print.

Error Detection ¡ Whenever we transmit data from one place to another, we must recognize that our data may be corrupted during transmission. l ¡ For example, a digital 1 becomes a 0 or vice versa. Many methods have been developed for detecting such errors. The oldest and simplest of these methods is called parity checking.

Parity—Even or Odd? ¡ Whenever parity checking is used, the sender and receiver must first agree whether to use even parity or odd parity. l l We’ll see on the next slide what this means. Recall that we saw this in Week 2 when we used Hyper. Terminal software on the PC to communicate with the Fluke multimeter.

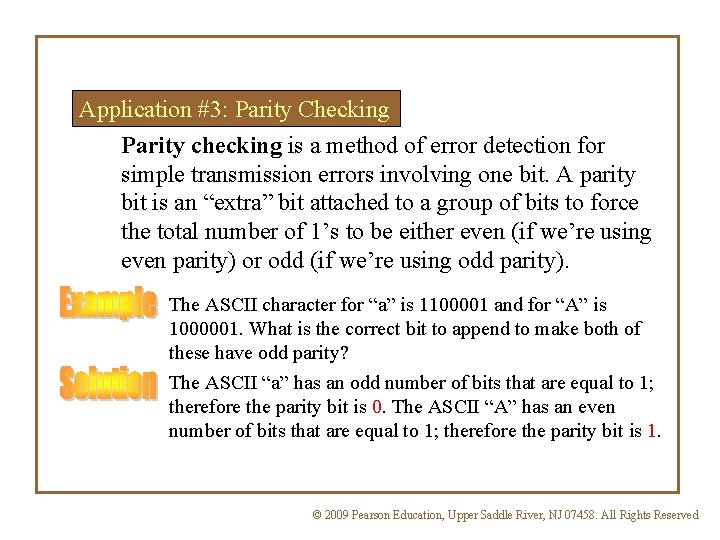

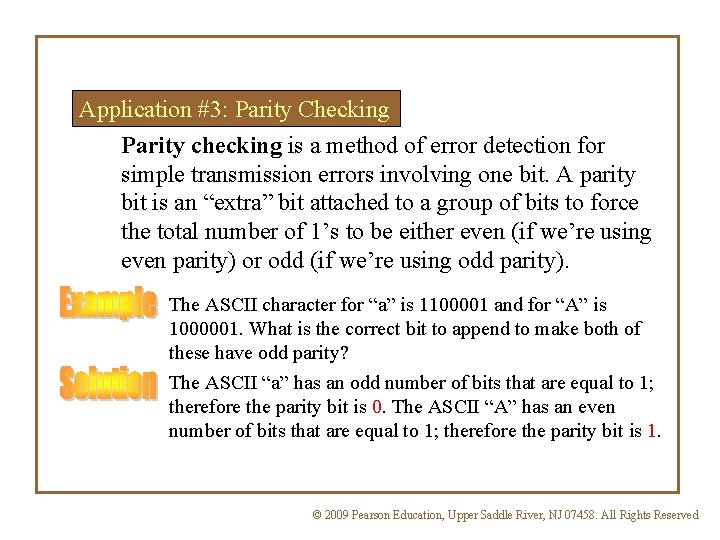

Application #3: Parity Checking Parity checking is a method of error detection for simple transmission errors involving one bit. A parity bit is an “extra” bit attached to a group of bits to force the total number of 1’s to be either even (if we’re using even parity) or odd (if we’re using odd parity). The ASCII character for “a” is 1100001 and for “A” is 1000001. What is the correct bit to append to make both of these have odd parity? The ASCII “a” has an odd number of bits that are equal to 1; therefore the parity bit is 0. The ASCII “A” has an even number of bits that are equal to 1; therefore the parity bit is 1. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

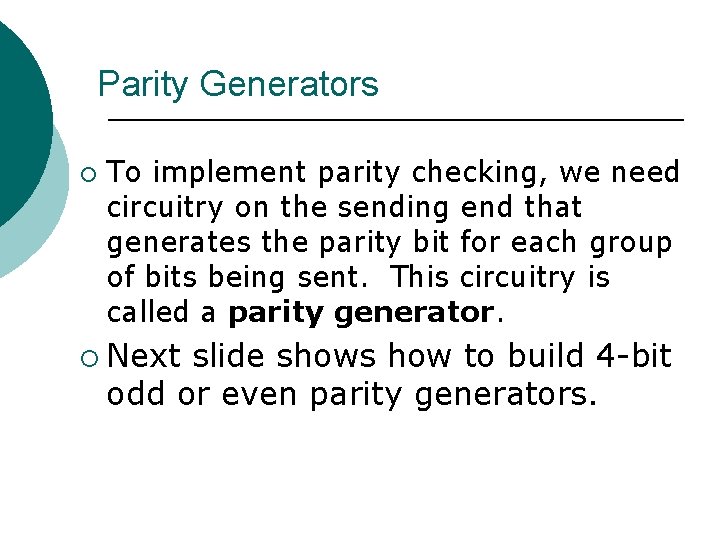

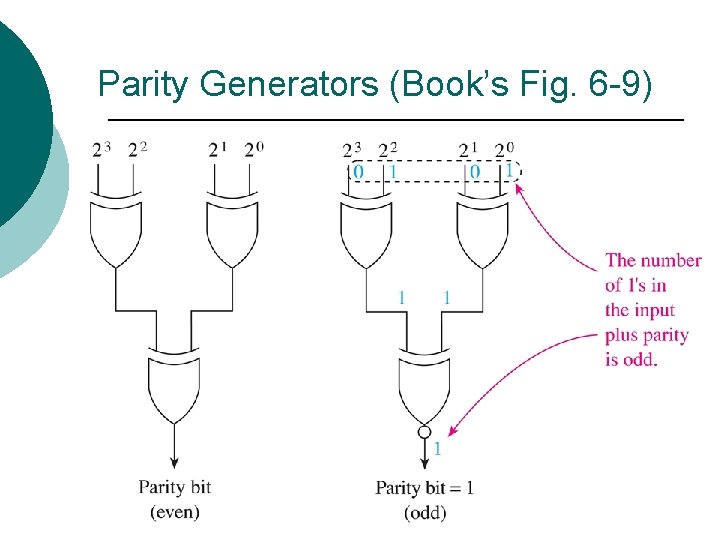

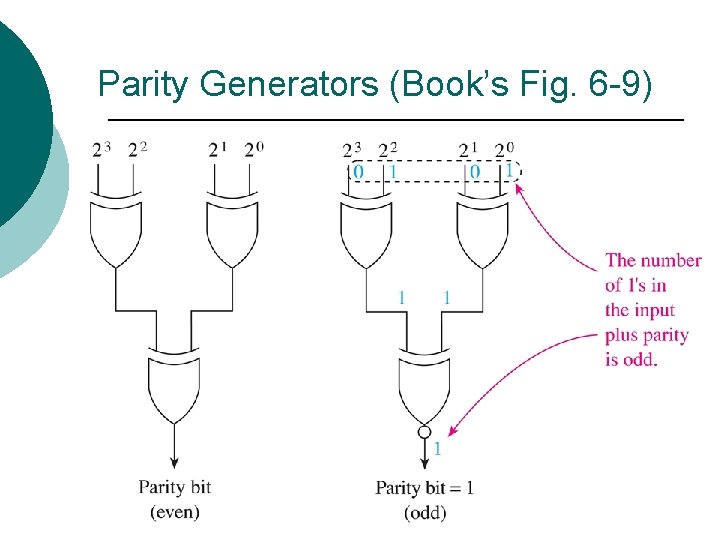

Parity Generators ¡ To implement parity checking, we need circuitry on the sending end that generates the parity bit for each group of bits being sent. This circuitry is called a parity generator. ¡ Next slide shows how to build 4 -bit odd or even parity generators.

Parity Generators (Book’s Fig. 6 -9)

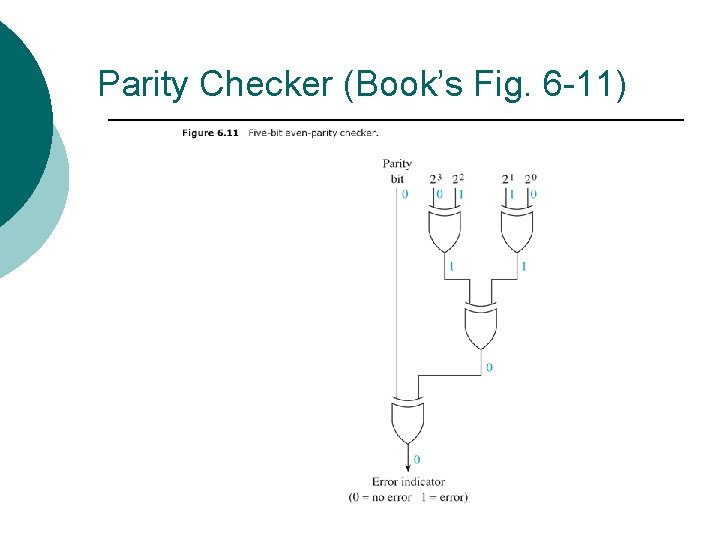

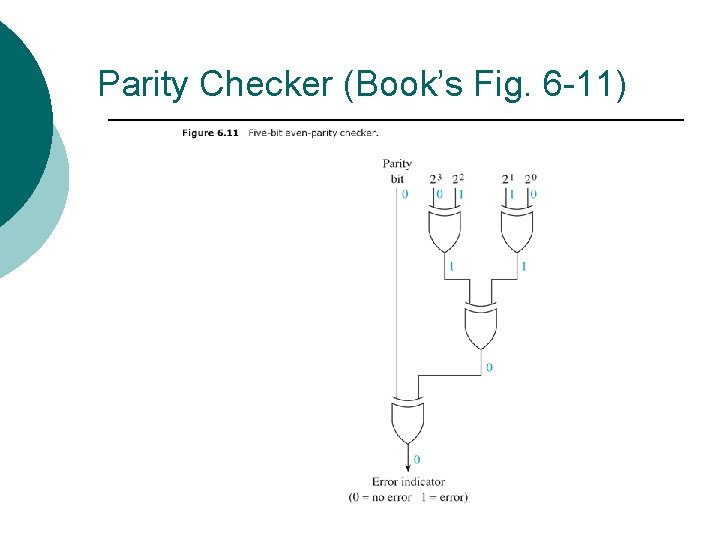

Parity Checkers ¡ On the receiving end, we need circuitry that checks the data bits and parity bit as they’re received to decide whether an error has occurred during transmission. This circuitry is called a parity checker. ¡ Next slide shows how to build a 4 bit-plus-parity even parity checker.

Parity Checker (Book’s Fig. 6 -11)

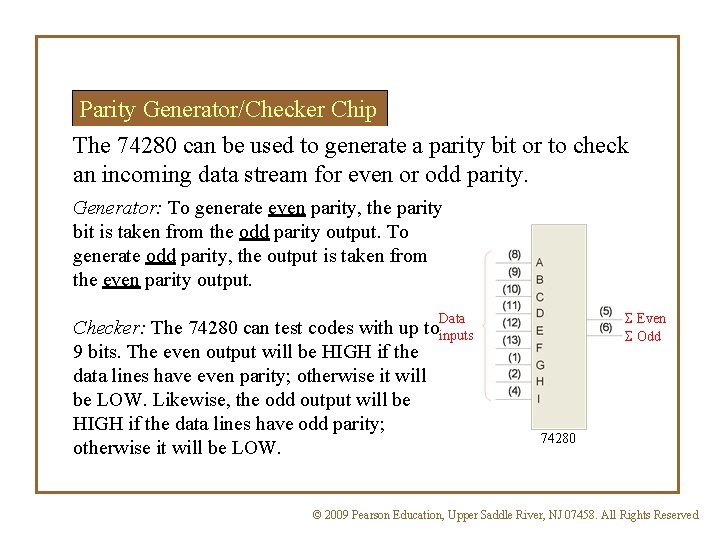

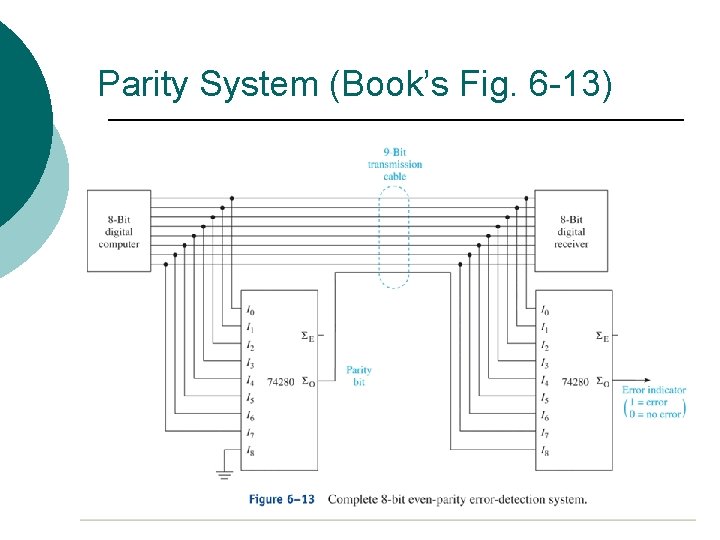

A Parity Generator/Checker Chip ¡ ¡ ¡ 74280 Nine-bit Parity Generator/Checker Most chips we’ve studied have been SSI (small-scale integration) chips containing fewer than 10 gates that are not connected to each other. The 74280 is an MSI (medium-scale integration) chip. Instead of containing a few disconnected gates, it contains about 45 gates connected internally on the chip to perform a specific function.

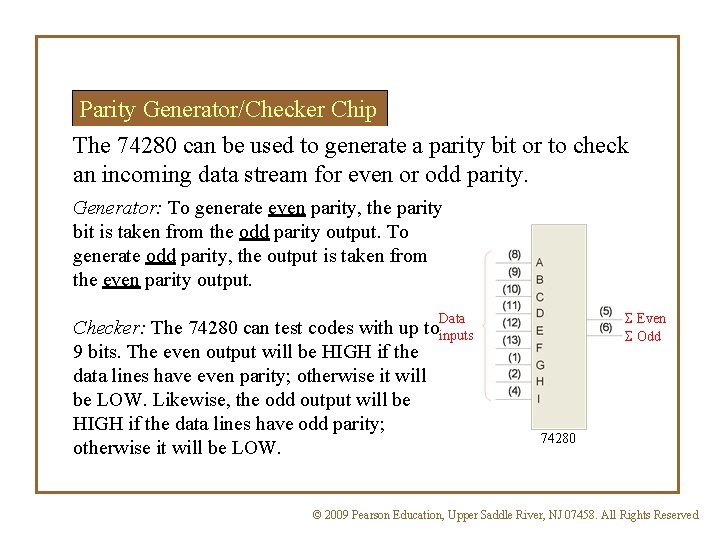

Parity Generator/Checker Chip The 74280 can be used to generate a parity bit or to check an incoming data stream for even or odd parity. Generator: To generate even parity, the parity bit is taken from the odd parity output. To generate odd parity, the output is taken from the even parity output. S Even S Odd Data Checker: The 74280 can test codes with up toinputs 9 bits. The even output will be HIGH if the data lines have even parity; otherwise it will be LOW. Likewise, the odd output will be HIGH if the data lines have odd parity; otherwise it will be LOW. 74280 © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

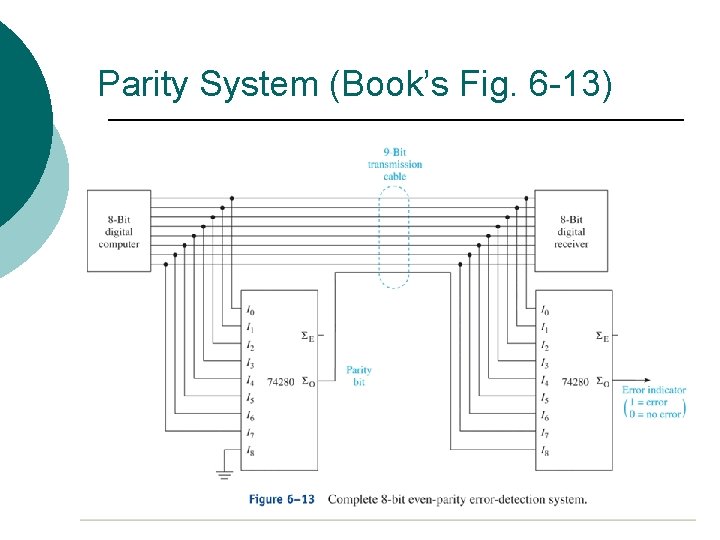

Parity System (Book’s Fig. 6 -13)

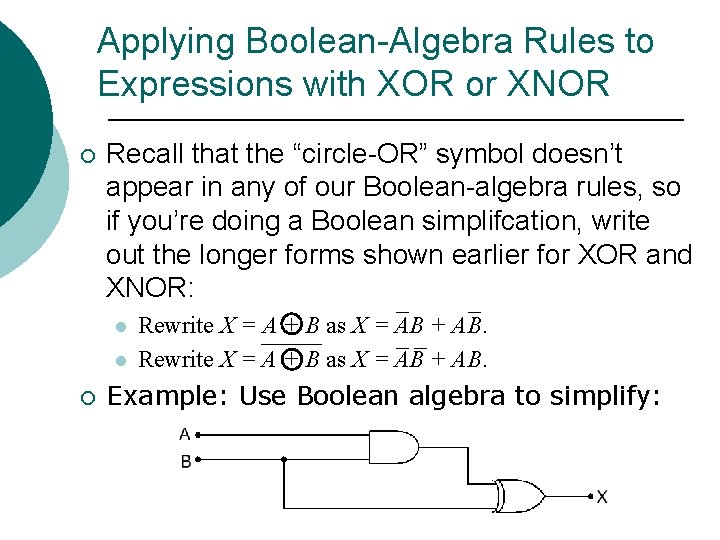

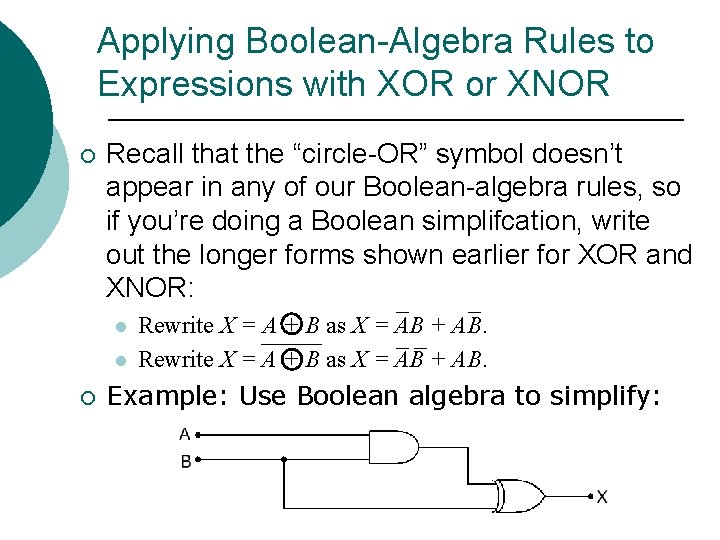

Applying Boolean-Algebra Rules to Expressions with XOR or XNOR ¡ Recall that the “circle-OR” symbol doesn’t appear in any of our Boolean-algebra rules, so if you’re doing a Boolean simplifcation, write out the longer forms shown earlier for XOR and XNOR: l l ¡ Rewrite X = A + B as X = AB + AB. Example: Use Boolean algebra to simplify:

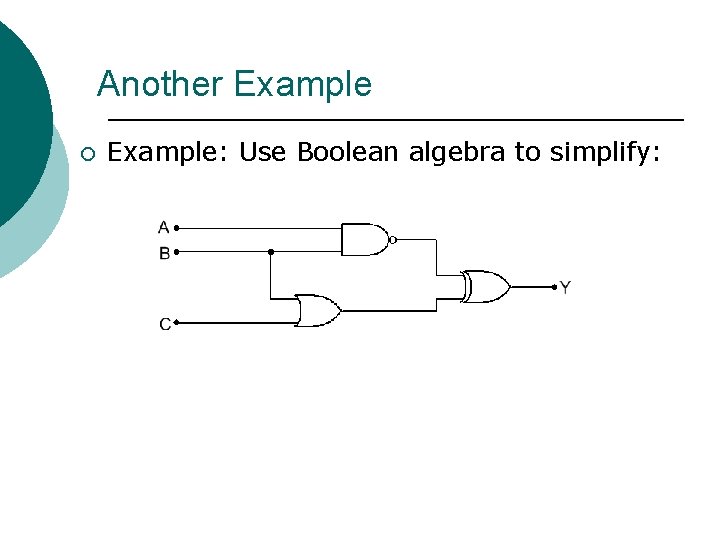

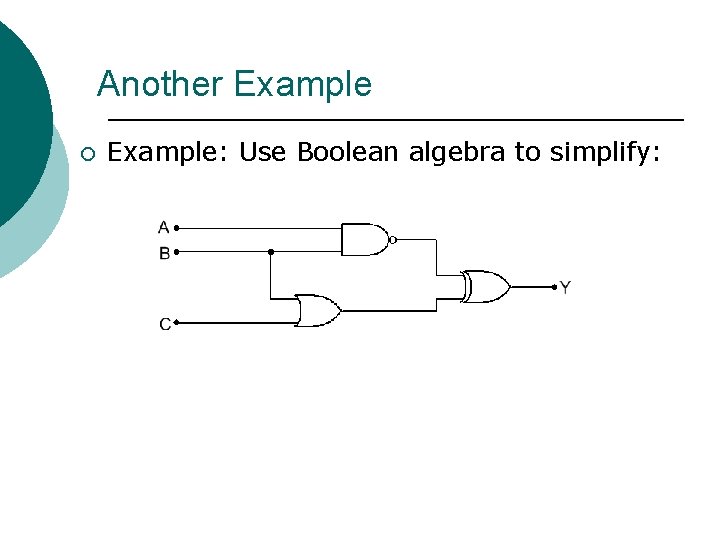

Another Example ¡ Example: Use Boolean algebra to simplify:

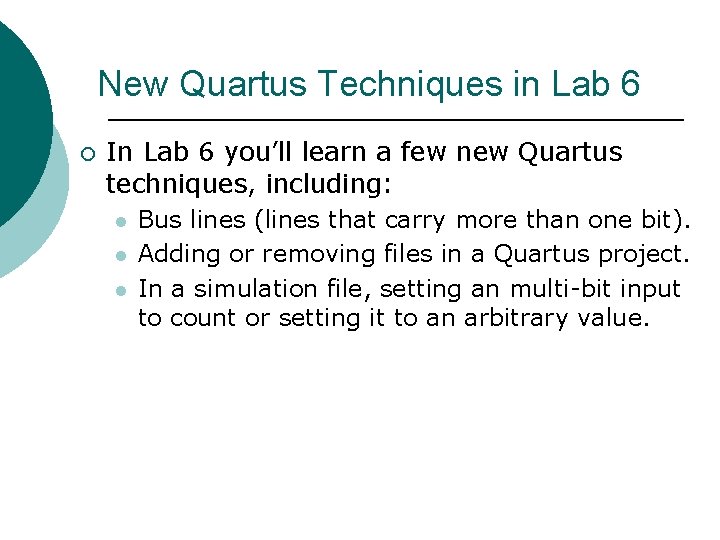

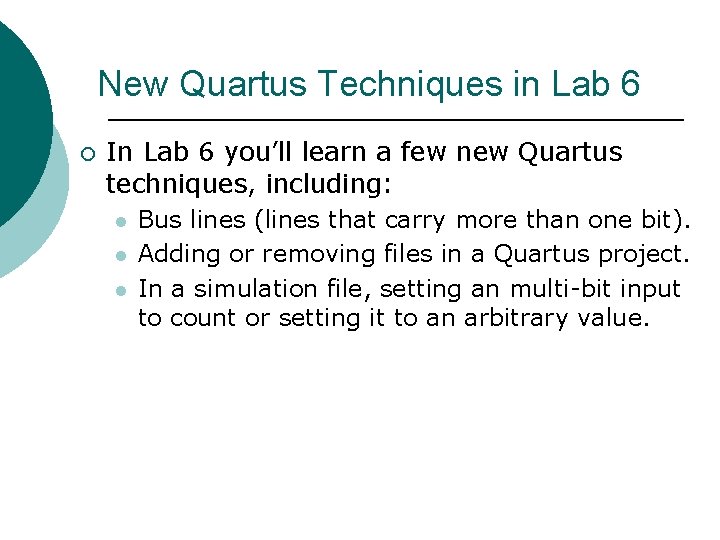

New Quartus Techniques in Lab 6 ¡ In Lab 6 you’ll learn a few new Quartus techniques, including: l l l Bus lines (lines that carry more than one bit). Adding or removing files in a Quartus project. In a simulation file, setting an multi-bit input to count or setting it to an arbitrary value.

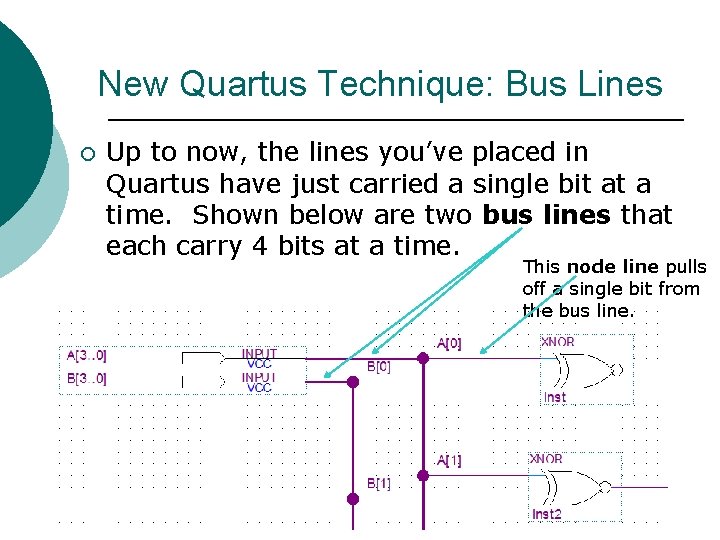

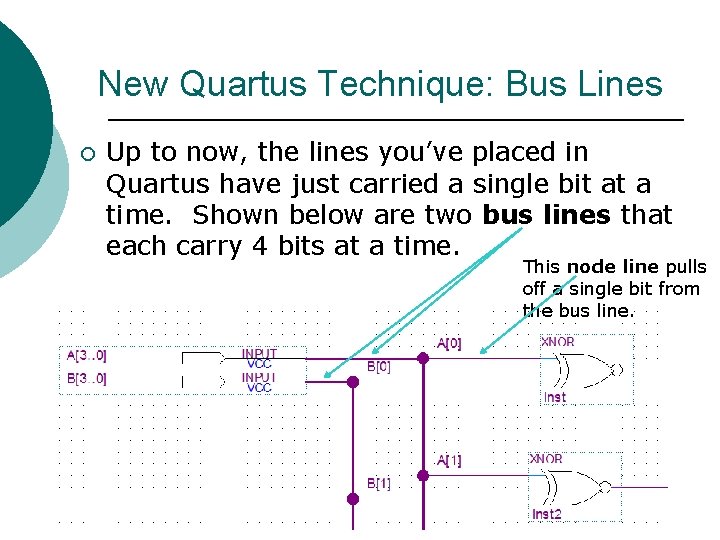

New Quartus Technique: Bus Lines ¡ Up to now, the lines you’ve placed in Quartus have just carried a single bit at a time. Shown below are two bus lines that each carry 4 bits at a time. This node line pulls off a single bit from the bus line.

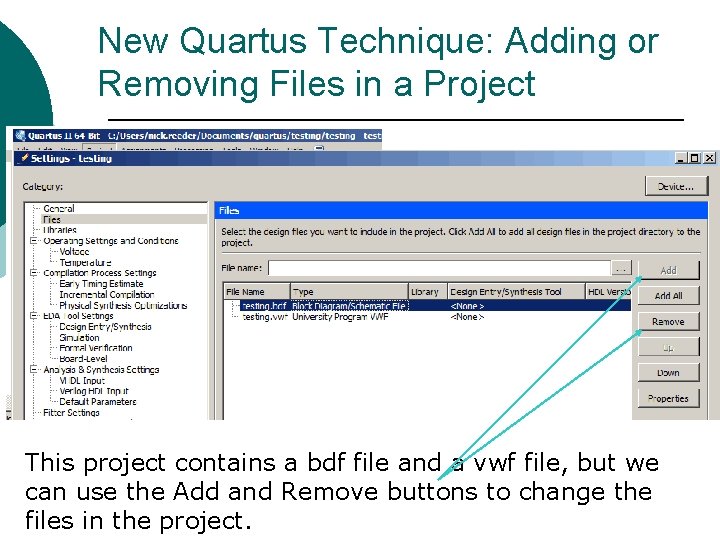

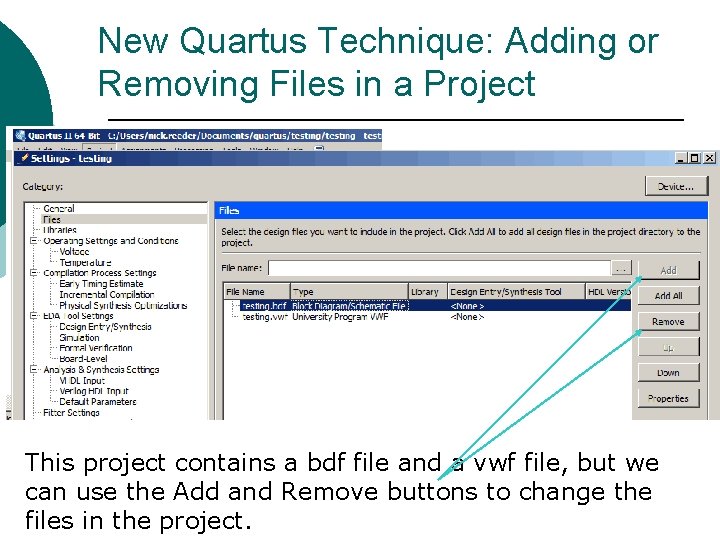

New Quartus Technique: Adding or Removing Files in a Project This project contains a bdf file and a vwf file, but we can use the Add and Remove buttons to change the files in the project.

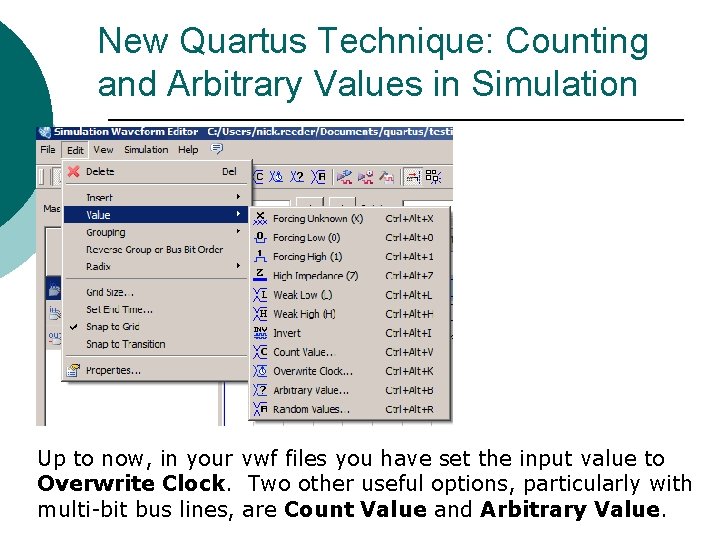

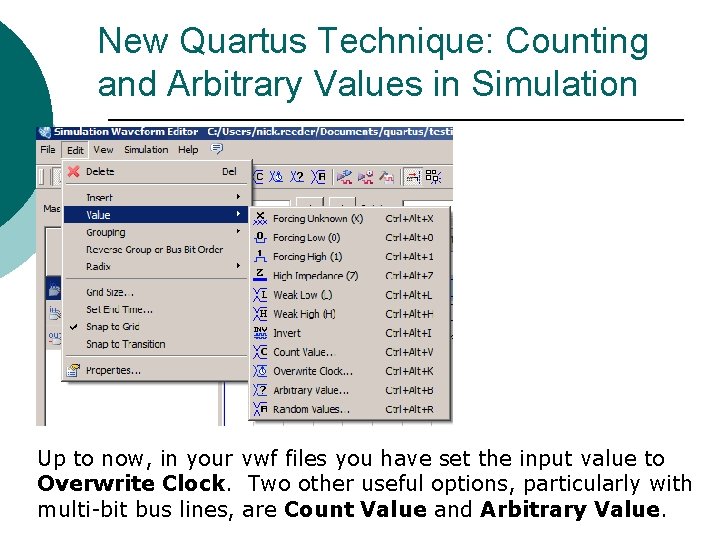

New Quartus Technique: Counting and Arbitrary Values in Simulation Up to now, in your vwf files you have set the input value to Overwrite Clock. Two other useful options, particularly with multi-bit bus lines, are Count Value and Arbitrary Value.