EECE 320 Digital Systems Design Lecture 14 Combinational

EECE 320 Digital Systems Design Lecture 14: Combinational Logic Design Practices Ali Chehab EECE 320 L 14: Combinational Logic design Practices 1 Chehab, AUB, 2003

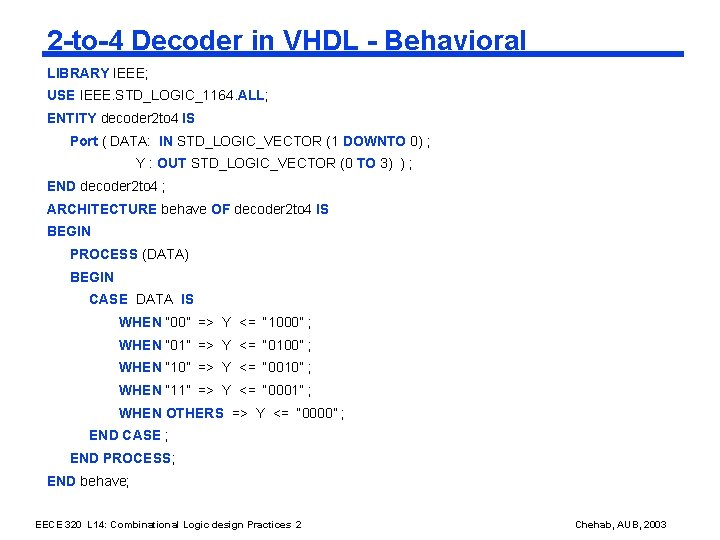

2 -to-4 Decoder in VHDL - Behavioral LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. ALL; ENTITY decoder 2 to 4 IS Port ( DATA: IN STD_LOGIC_VECTOR (1 DOWNTO 0) ; Y : OUT STD_LOGIC_VECTOR (0 TO 3) ) ; END decoder 2 to 4 ; ARCHITECTURE behave OF decoder 2 to 4 IS BEGIN PROCESS (DATA) BEGIN CASE DATA IS WHEN “ 00” => Y <= “ 1000” ; WHEN “ 01” => Y <= “ 0100” ; WHEN “ 10” => Y <= “ 0010” ; WHEN “ 11” => Y <= “ 0001” ; WHEN OTHERS => Y <= “ 0000” ; END CASE ; END PROCESS; END behave; EECE 320 L 14: Combinational Logic design Practices 2 Chehab, AUB, 2003

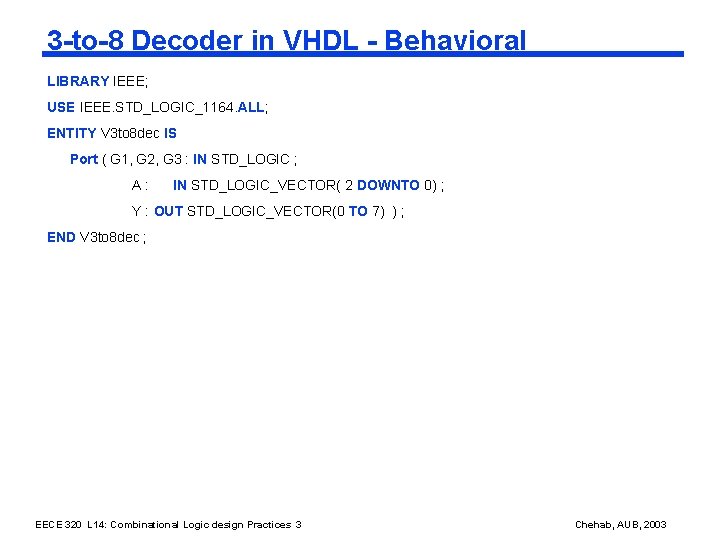

3 -to-8 Decoder in VHDL - Behavioral LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. ALL; ENTITY V 3 to 8 dec IS Port ( G 1, G 2, G 3 : IN STD_LOGIC ; A: IN STD_LOGIC_VECTOR( 2 DOWNTO 0) ; Y : OUT STD_LOGIC_VECTOR(0 TO 7) ) ; END V 3 to 8 dec ; EECE 320 L 14: Combinational Logic design Practices 3 Chehab, AUB, 2003

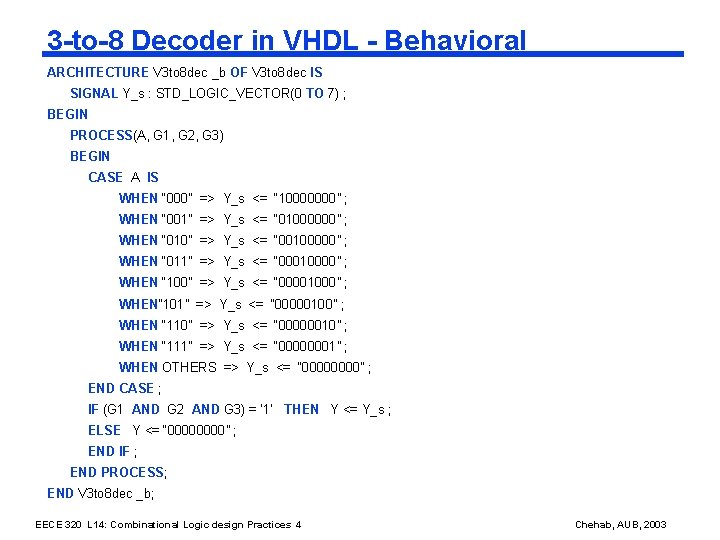

3 -to-8 Decoder in VHDL - Behavioral ARCHITECTURE V 3 to 8 dec _b OF V 3 to 8 dec IS SIGNAL Y_s : STD_LOGIC_VECTOR(0 TO 7) ; BEGIN PROCESS(A, G 1, G 2, G 3) BEGIN CASE A IS WHEN “ 000” => Y_s <= “ 10000000” ; WHEN “ 001” => Y_s <= “ 01000000” ; WHEN “ 010” => Y_s <= “ 00100000” ; WHEN “ 011” => Y_s <= “ 00010000” ; WHEN “ 100” => Y_s <= “ 00001000” ; WHEN“ 101” => Y_s <= “ 00000100” ; WHEN “ 110” => Y_s <= “ 00000010” ; WHEN “ 111” => Y_s <= “ 00000001” ; WHEN OTHERS => Y_s <= “ 0000” ; END CASE ; IF (G 1 AND G 2 AND G 3) = ‘ 1’ THEN Y <= Y_s ; ELSE Y <= “ 0000” ; END IF ; END PROCESS; END V 3 to 8 dec _b; EECE 320 L 14: Combinational Logic design Practices 4 Chehab, AUB, 2003

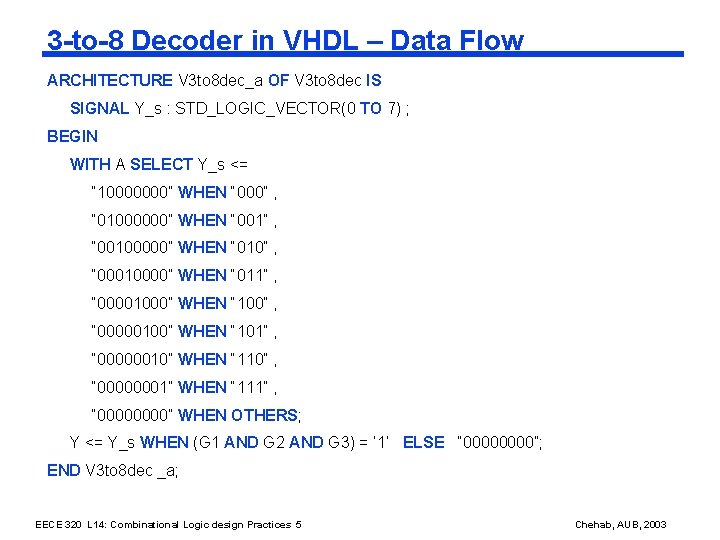

3 -to-8 Decoder in VHDL – Data Flow ARCHITECTURE V 3 to 8 dec_a OF V 3 to 8 dec IS SIGNAL Y_s : STD_LOGIC_VECTOR(0 TO 7) ; BEGIN WITH A SELECT Y_s <= “ 10000000” WHEN “ 000” , “ 01000000” WHEN “ 001” , “ 00100000” WHEN “ 010” , “ 00010000” WHEN “ 011” , “ 00001000” WHEN “ 100” , “ 00000100” WHEN “ 101” , “ 00000010” WHEN “ 110” , “ 00000001” WHEN “ 111” , “ 0000” WHEN OTHERS; Y <= Y_s WHEN (G 1 AND G 2 AND G 3) = ‘ 1’ ELSE “ 0000”; END V 3 to 8 dec _a; EECE 320 L 14: Combinational Logic design Practices 5 Chehab, AUB, 2003

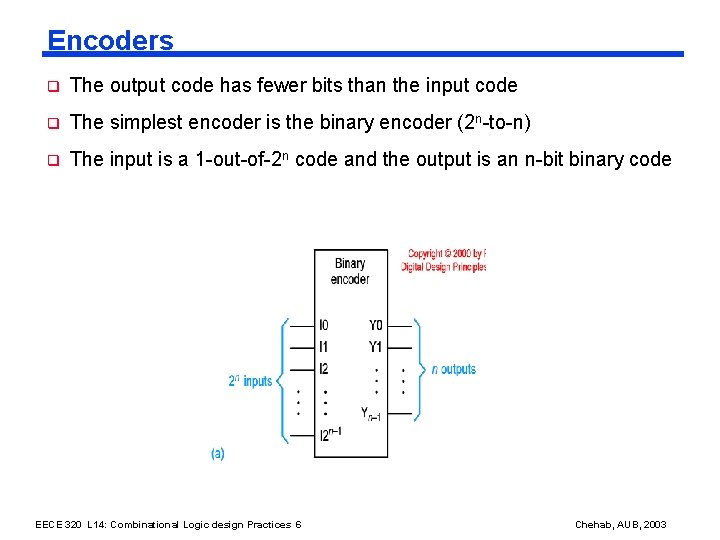

Encoders q The output code has fewer bits than the input code q The simplest encoder is the binary encoder (2 n-to-n) q The input is a 1 -out-of-2 n code and the output is an n-bit binary code EECE 320 L 14: Combinational Logic design Practices 6 Chehab, AUB, 2003

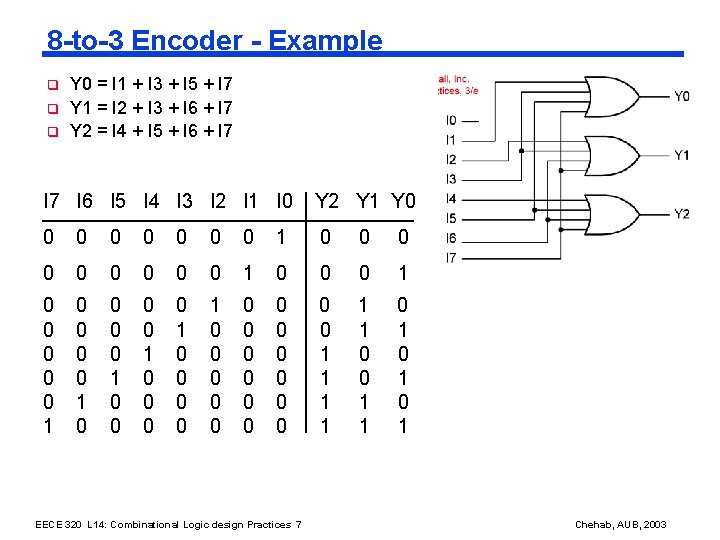

8 -to-3 Encoder - Example q q q Y 0 = I 1 + I 3 + I 5 + I 7 Y 1 = I 2 + I 3 + I 6 + I 7 Y 2 = I 4 + I 5 + I 6 + I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 Y 2 Y 1 Y 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 1 1 0 0 1 1 0 1 0 1 EECE 320 L 14: Combinational Logic design Practices 7 Chehab, AUB, 2003

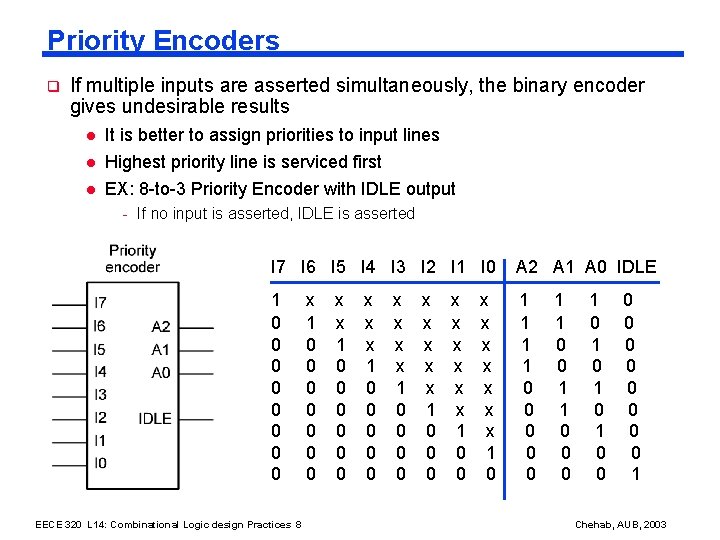

Priority Encoders q If multiple inputs are asserted simultaneously, the binary encoder gives undesirable results l l l It is better to assign priorities to input lines Highest priority line is serviced first EX: 8 -to-3 Priority Encoder with IDLE output - If no input is asserted, IDLE is asserted I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 A 2 A 1 A 0 IDLE 1 0 0 0 0 1 1 1 0 0 1 0 1 0 0 1 1 0 0 0 0 1 EECE 320 L 14: Combinational Logic design Practices 8 x 1 0 0 0 0 x x x x 1 x x x 0 1 x x 0 0 1 x 0 0 0 1 0 0 0 x x x 1 0 0 x x x x 1 0 Chehab, AUB, 2003

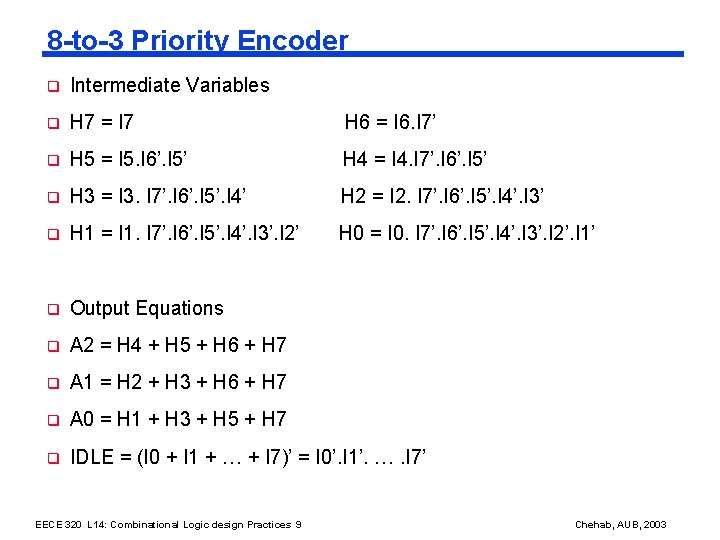

8 -to-3 Priority Encoder q Intermediate Variables q H 7 = I 7 H 6 = I 6. I 7’ q H 5 = I 5. I 6’. I 5’ H 4 = I 4. I 7’. I 6’. I 5’ q H 3 = I 3. I 7’. I 6’. I 5’. I 4’ H 2 = I 2. I 7’. I 6’. I 5’. I 4’. I 3’ q H 1 = I 1. I 7’. I 6’. I 5’. I 4’. I 3’. I 2’ H 0 = I 0. I 7’. I 6’. I 5’. I 4’. I 3’. I 2’. I 1’ q Output Equations q A 2 = H 4 + H 5 + H 6 + H 7 q A 1 = H 2 + H 3 + H 6 + H 7 q A 0 = H 1 + H 3 + H 5 + H 7 q IDLE = (I 0 + I 1 + … + I 7)’ = I 0’. I 1’. …. I 7’ EECE 320 L 14: Combinational Logic design Practices 9 Chehab, AUB, 2003

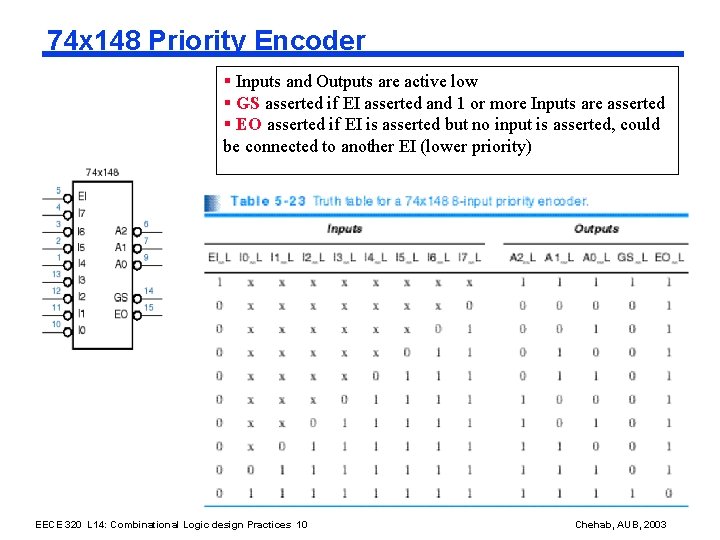

74 x 148 Priority Encoder § Inputs and Outputs are active low § GS asserted if EI asserted and 1 or more Inputs are asserted § EO asserted if EI is asserted but no input is asserted, could be connected to another EI (lower priority) EECE 320 L 14: Combinational Logic design Practices 10 Chehab, AUB, 2003

Next Lecture and Reminders q Next lecture q Reminders EECE 320 L 14: Combinational Logic design Practices 11 Chehab, AUB, 2003

- Slides: 11