EECE 320 Digital Systems Design Lecture 11 VHDL

- Slides: 18

EECE 320 Digital Systems Design Lecture 11: VHDL – Some Basics in Implementation Youssef Nasser EECE 320 L 11: VHDL 1 Nasser, AUB, 2010

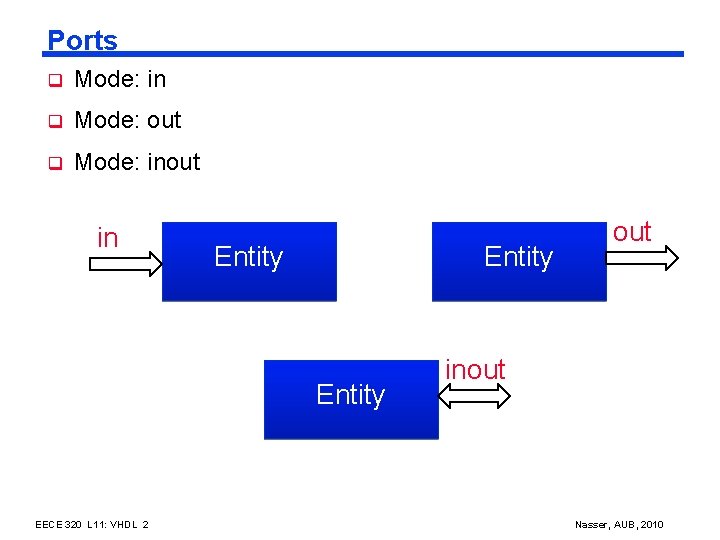

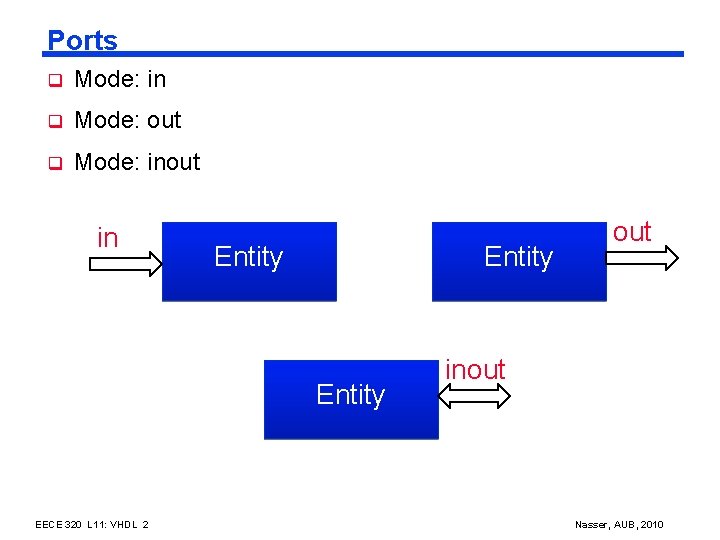

Ports q Mode: in q Mode: out q Mode: inout in Entity EECE 320 L 11: VHDL 2 out inout Nasser, AUB, 2010

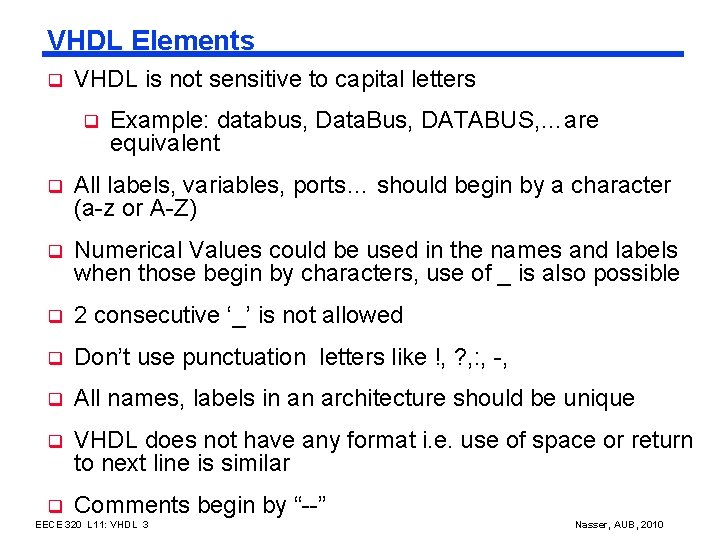

VHDL Elements q VHDL is not sensitive to capital letters q Example: databus, Data. Bus, DATABUS, …are equivalent q All labels, variables, ports… should begin by a character (a-z or A-Z) q Numerical Values could be used in the names and labels when those begin by characters, use of _ is also possible q 2 consecutive ‘_’ is not allowed q Don’t use punctuation letters like !, ? , : , -, q All names, labels in an architecture should be unique q VHDL does not have any format i. e. use of space or return to next line is similar q Comments begin by “--” EECE 320 L 11: VHDL 3 Nasser, AUB, 2010

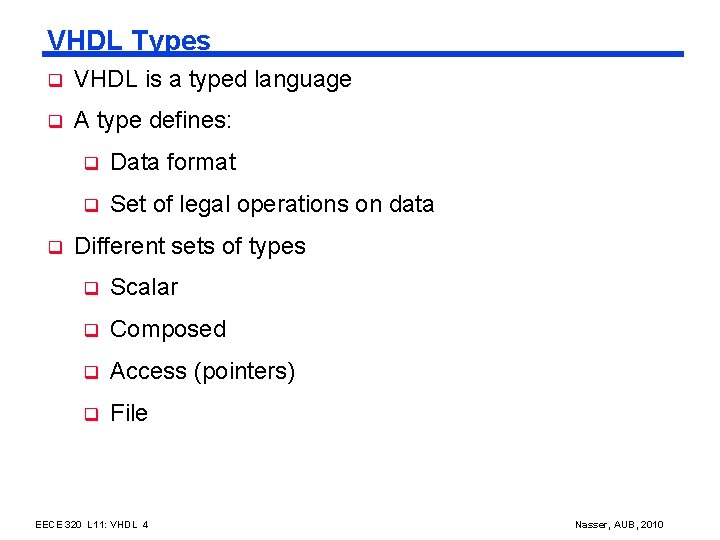

VHDL Types q VHDL is a typed language q A type defines: q q Data format q Set of legal operations on data Different sets of types q Scalar q Composed q Access (pointers) q File EECE 320 L 11: VHDL 4 Nasser, AUB, 2010

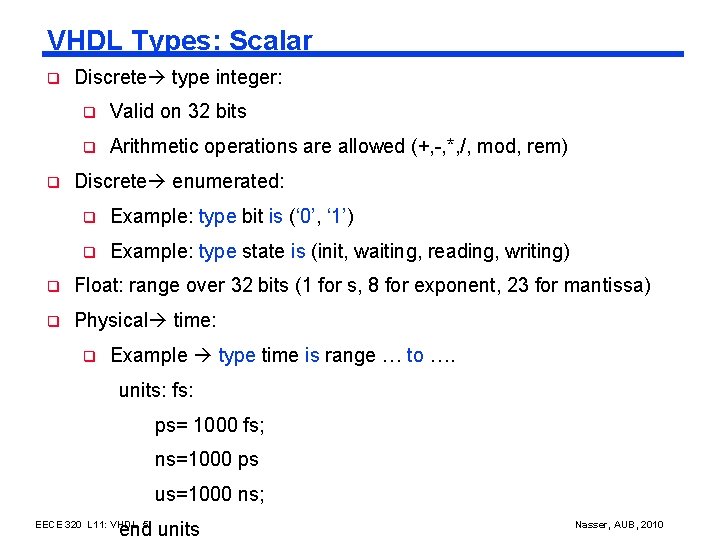

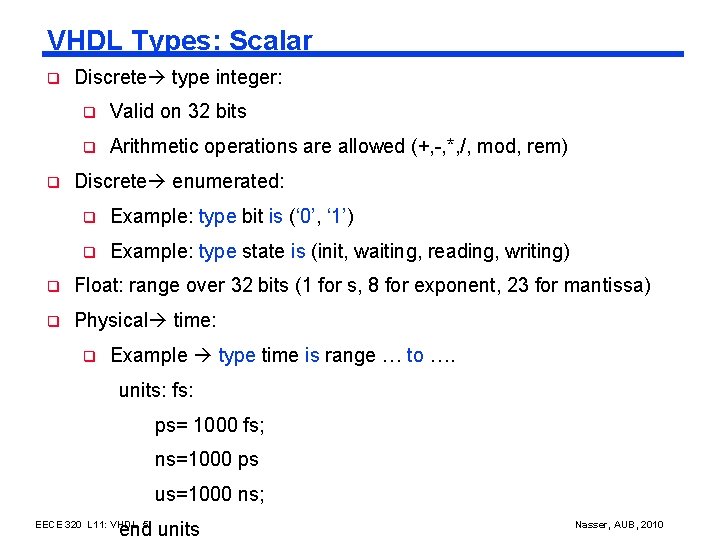

VHDL Types: Scalar q q Discrete type integer: q Valid on 32 bits q Arithmetic operations are allowed (+, -, *, /, mod, rem) Discrete enumerated: q Example: type bit is (‘ 0’, ‘ 1’) q Example: type state is (init, waiting, reading, writing) q Float: range over 32 bits (1 for s, 8 for exponent, 23 for mantissa) q Physical time: q Example type time is range … to …. units: fs: ps= 1000 fs; ns=1000 ps us=1000 ns; end units EECE 320 L 11: VHDL 5 Nasser, AUB, 2010

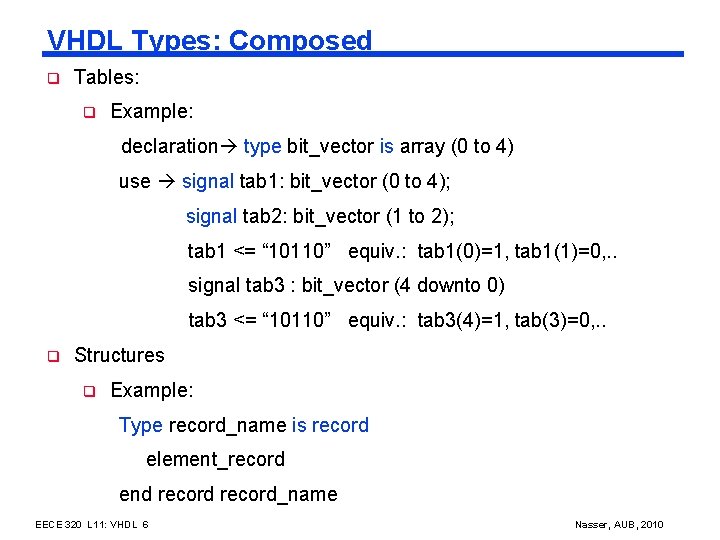

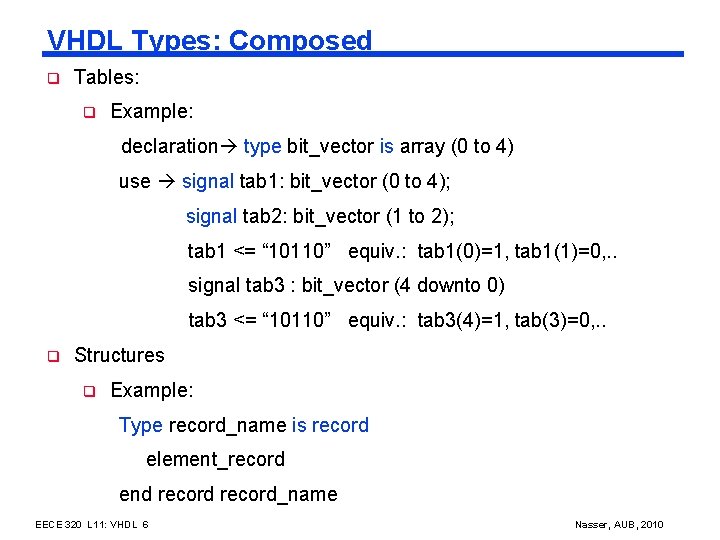

VHDL Types: Composed q Tables: q Example: declaration type bit_vector is array (0 to 4) use signal tab 1: bit_vector (0 to 4); signal tab 2: bit_vector (1 to 2); tab 1 <= “ 10110” equiv. : tab 1(0)=1, tab 1(1)=0, . . signal tab 3 : bit_vector (4 downto 0) tab 3 <= “ 10110” equiv. : tab 3(4)=1, tab(3)=0, . . q Structures q Example: Type record_name is record element_record end record_name EECE 320 L 11: VHDL 6 Nasser, AUB, 2010

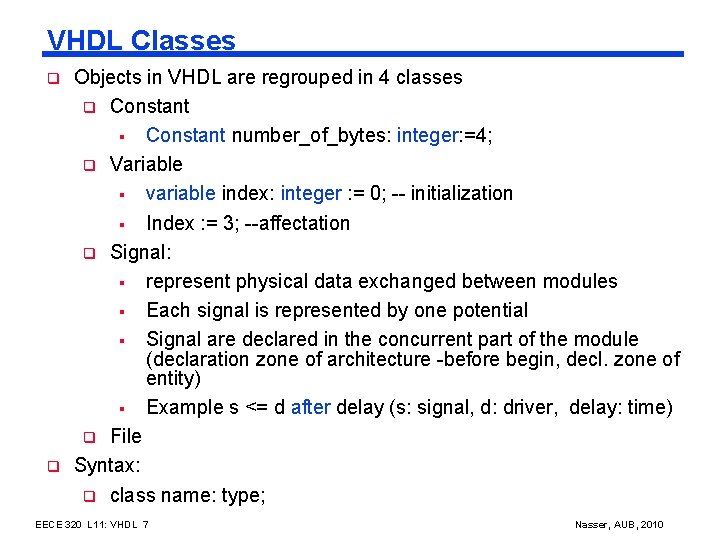

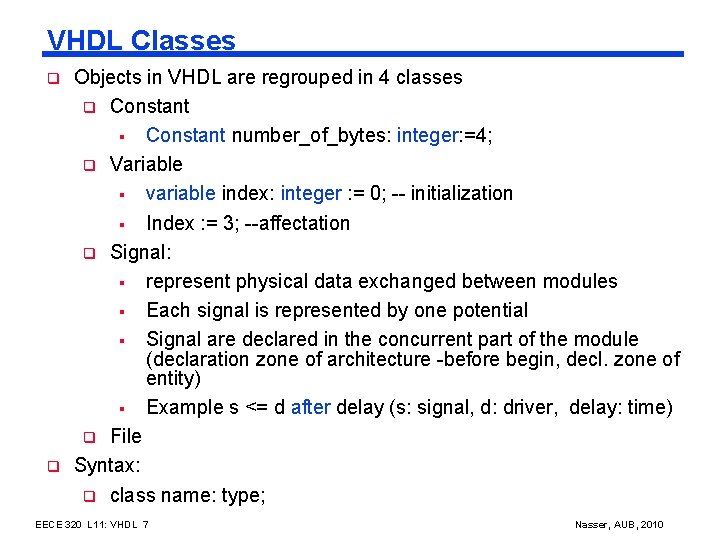

VHDL Classes q q Objects in VHDL are regrouped in 4 classes q Constant § Constant number_of_bytes: integer: =4; q Variable § variable index: integer : = 0; -- initialization § Index : = 3; --affectation q Signal: § represent physical data exchanged between modules § Each signal is represented by one potential § Signal are declared in the concurrent part of the module (declaration zone of architecture -before begin, decl. zone of entity) § Example s <= d after delay (s: signal, d: driver, delay: time) q File Syntax: q class name: type; EECE 320 L 11: VHDL 7 Nasser, AUB, 2010

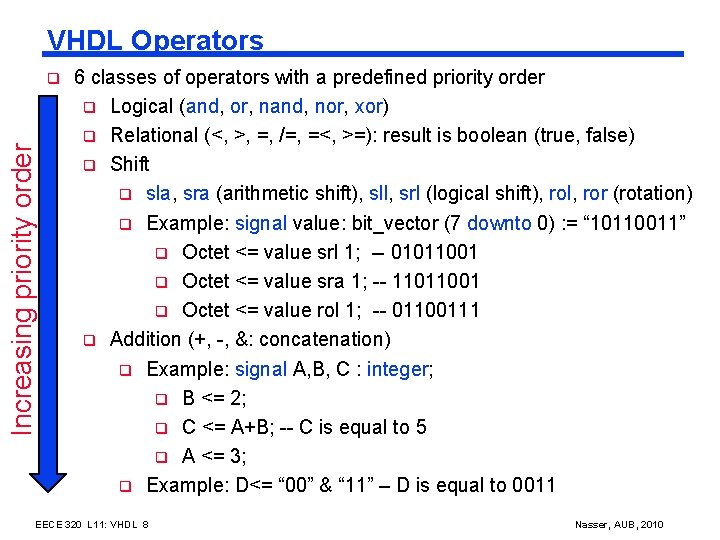

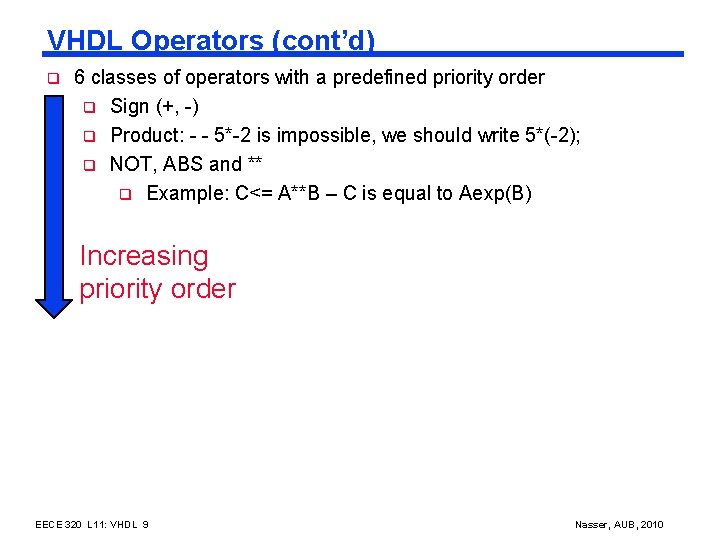

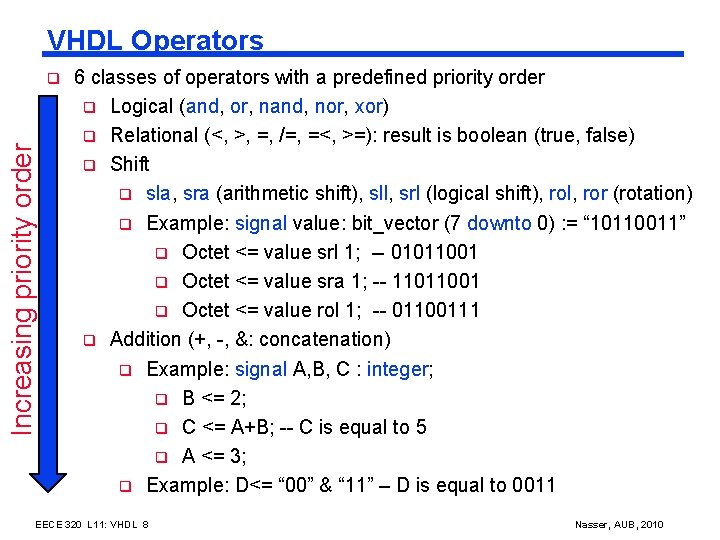

VHDL Operators Increasing priority order q 6 classes of operators with a predefined priority order q Logical (and, or, nand, nor, xor) q Relational (<, >, =, /=, =<, >=): result is boolean (true, false) q Shift q sla, sra (arithmetic shift), sll, srl (logical shift), rol, ror (rotation) q Example: signal value: bit_vector (7 downto 0) : = “ 10110011” q Octet <= value srl 1; -- 01011001 q Octet <= value sra 1; -- 11011001 q Octet <= value rol 1; -- 01100111 q Addition (+, -, &: concatenation) q Example: signal A, B, C : integer; q B <= 2; q C <= A+B; -- C is equal to 5 q A <= 3; q Example: D<= “ 00” & “ 11” – D is equal to 0011 EECE 320 L 11: VHDL 8 Nasser, AUB, 2010

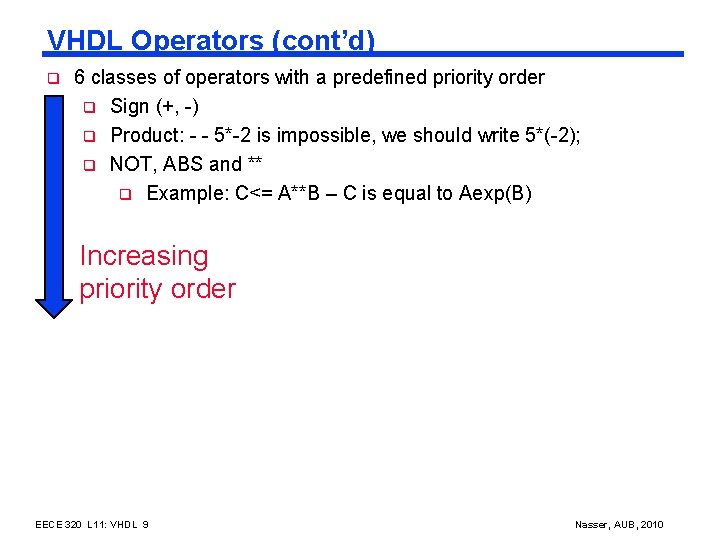

VHDL Operators (cont’d) q 6 classes of operators with a predefined priority order q Sign (+, -) q Product: - - 5*-2 is impossible, we should write 5*(-2); q NOT, ABS and ** q Example: C<= A**B – C is equal to Aexp(B) Increasing priority order EECE 320 L 11: VHDL 9 Nasser, AUB, 2010

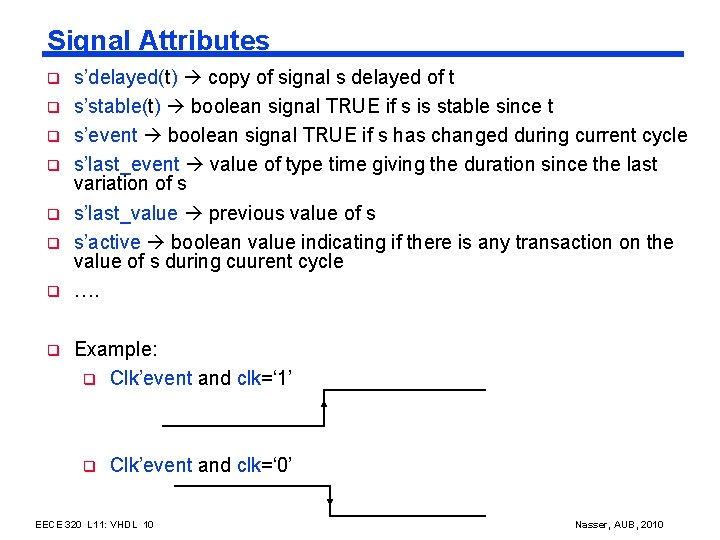

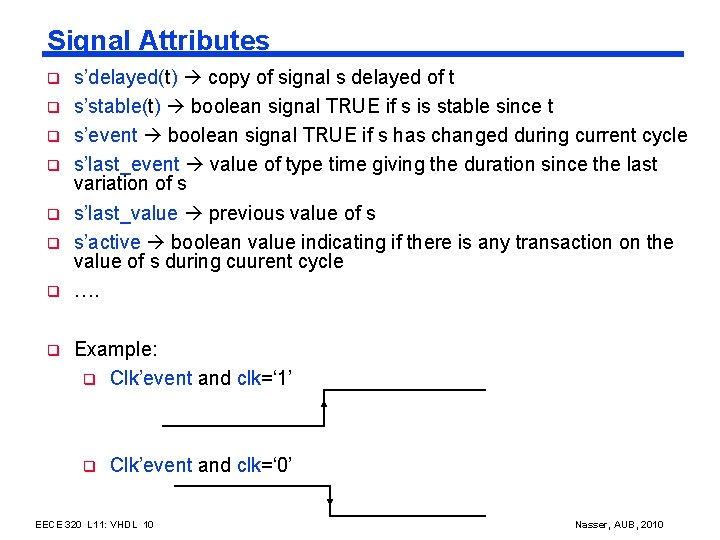

Signal Attributes q q q q s’delayed(t) copy of signal s delayed of t s’stable(t) boolean signal TRUE if s is stable since t s’event boolean signal TRUE if s has changed during current cycle s’last_event value of type time giving the duration since the last variation of s s’last_value previous value of s s’active boolean value indicating if there is any transaction on the value of s during cuurent cycle …. Example: q Clk’event and clk=‘ 1’ q Clk’event and clk=‘ 0’ EECE 320 L 11: VHDL 10 Nasser, AUB, 2010

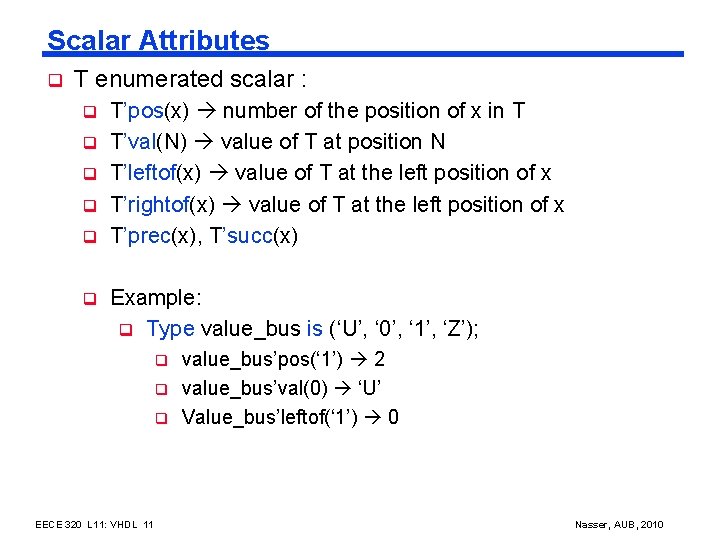

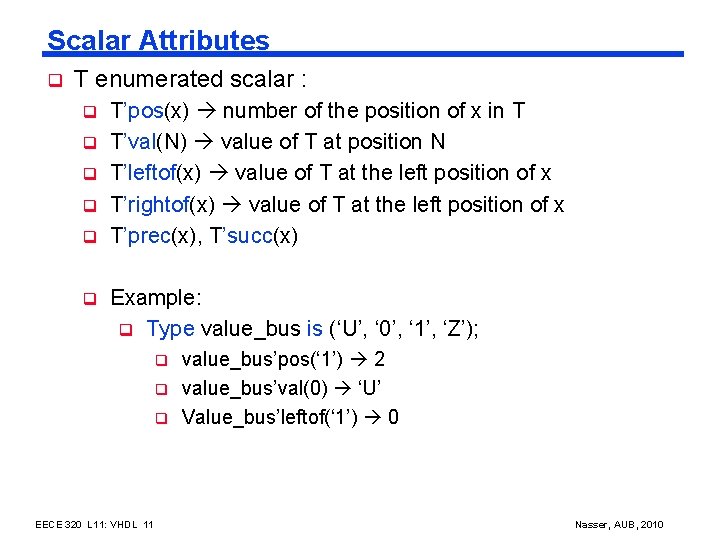

Scalar Attributes q T enumerated scalar : q q q T’pos(x) number of the position of x in T T’val(N) value of T at position N T’leftof(x) value of T at the left position of x T’rightof(x) value of T at the left position of x T’prec(x), T’succ(x) Example: q Type value_bus is (‘U’, ‘ 0’, ‘ 1’, ‘Z’); q q q EECE 320 L 11: VHDL 11 value_bus’pos(‘ 1’) 2 value_bus’val(0) ‘U’ Value_bus’leftof(‘ 1’) 0 Nasser, AUB, 2010

Concurrent Instructions q q q Affectation instructions Instruction: block Instructions: component, port map, generic map Instruction: generate Process EECE 320 L 11: VHDL 12 Nasser, AUB, 2010

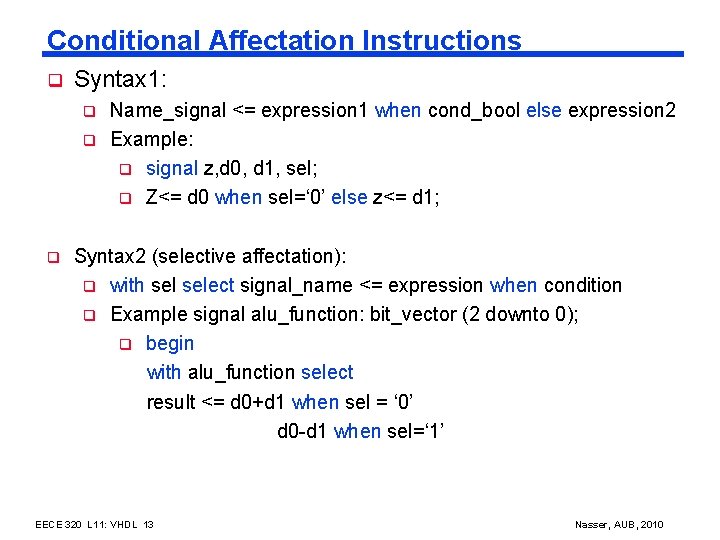

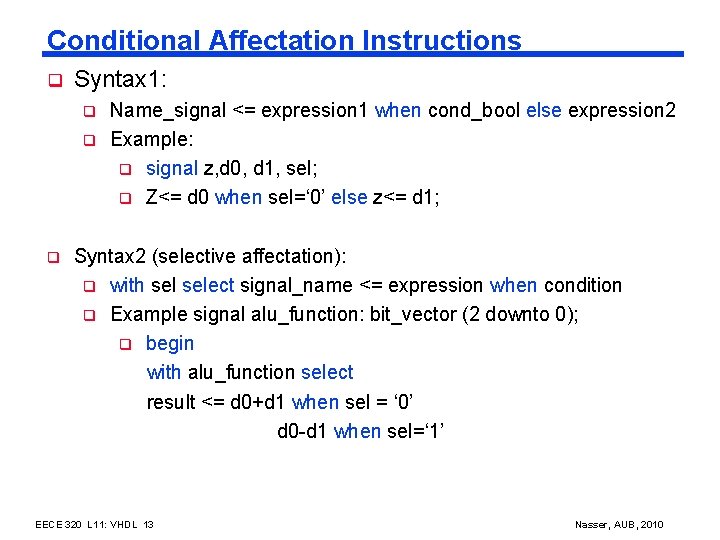

Conditional Affectation Instructions q Syntax 1: q q q Name_signal <= expression 1 when cond_bool else expression 2 Example: q signal z, d 0, d 1, sel; q Z<= d 0 when sel=‘ 0’ else z<= d 1; Syntax 2 (selective affectation): q with select signal_name <= expression when condition q Example signal alu_function: bit_vector (2 downto 0); q begin with alu_function select result <= d 0+d 1 when sel = ‘ 0’ d 0 -d 1 when sel=‘ 1’ EECE 320 L 11: VHDL 13 Nasser, AUB, 2010

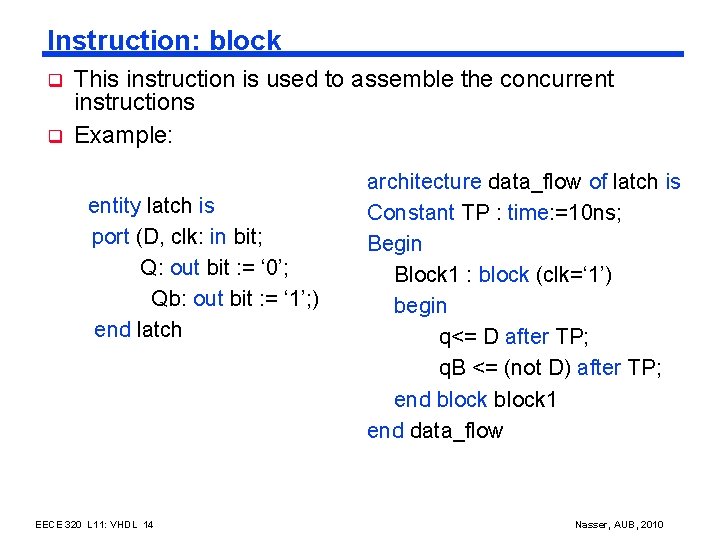

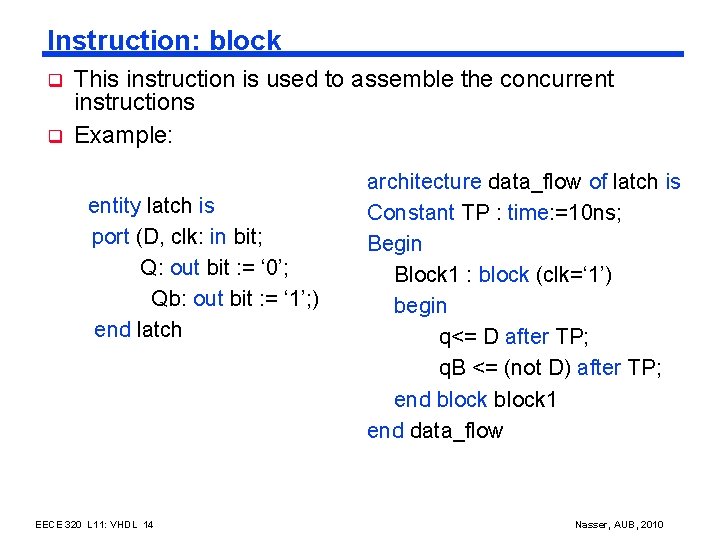

Instruction: block q q This instruction is used to assemble the concurrent instructions Example: entity latch is port (D, clk: in bit; Q: out bit : = ‘ 0’; Qb: out bit : = ‘ 1’; ) end latch EECE 320 L 11: VHDL 14 architecture data_flow of latch is Constant TP : time: =10 ns; Begin Block 1 : block (clk=‘ 1’) begin q<= D after TP; q. B <= (not D) after TP; end block 1 end data_flow Nasser, AUB, 2010

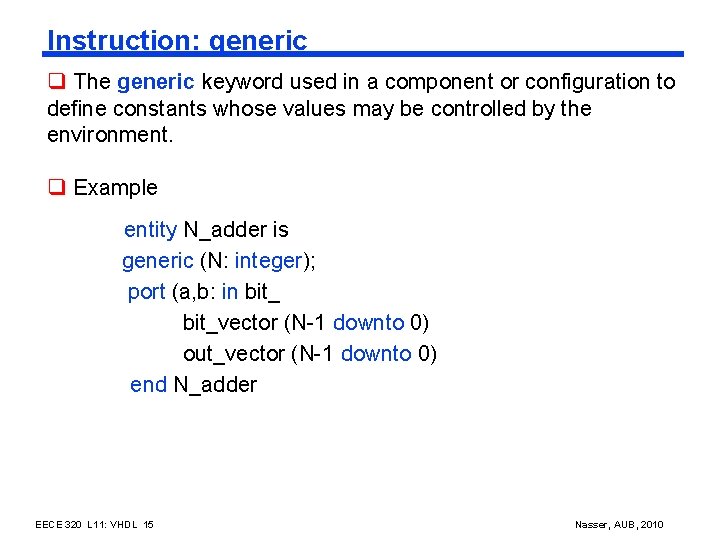

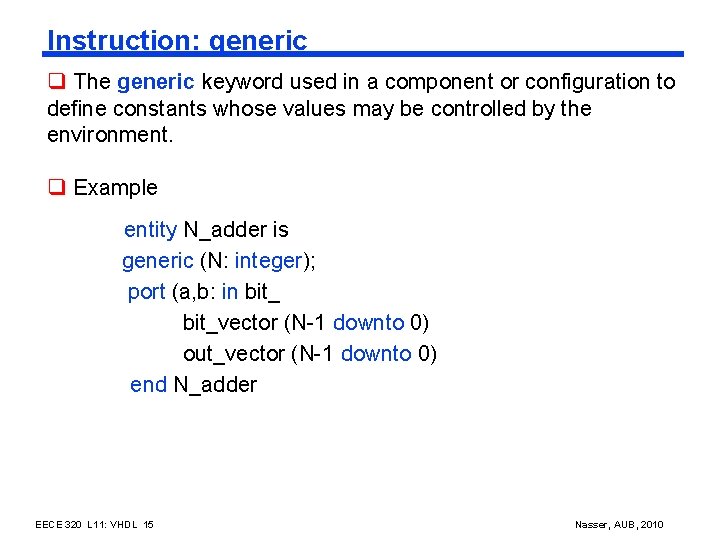

Instruction: generic q The generic keyword used in a component or configuration to define constants whose values may be controlled by the environment. q Example entity N_adder is generic (N: integer); port (a, b: in bit_ bit_vector (N-1 downto 0) out_vector (N-1 downto 0) end N_adder EECE 320 L 11: VHDL 15 Nasser, AUB, 2010

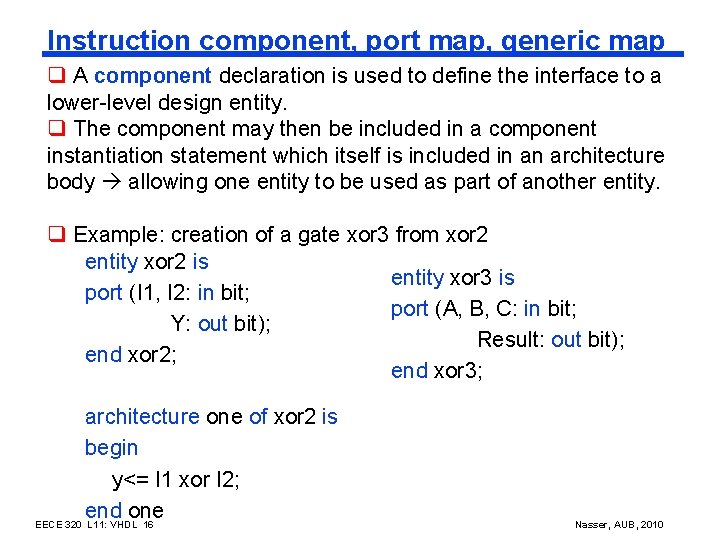

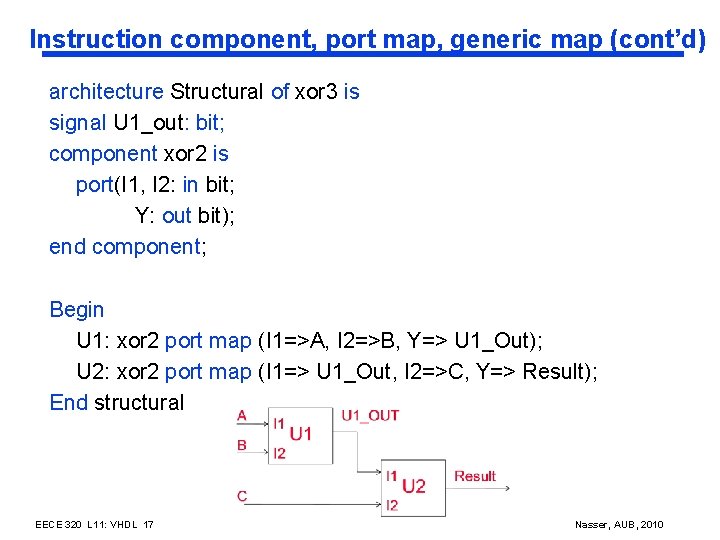

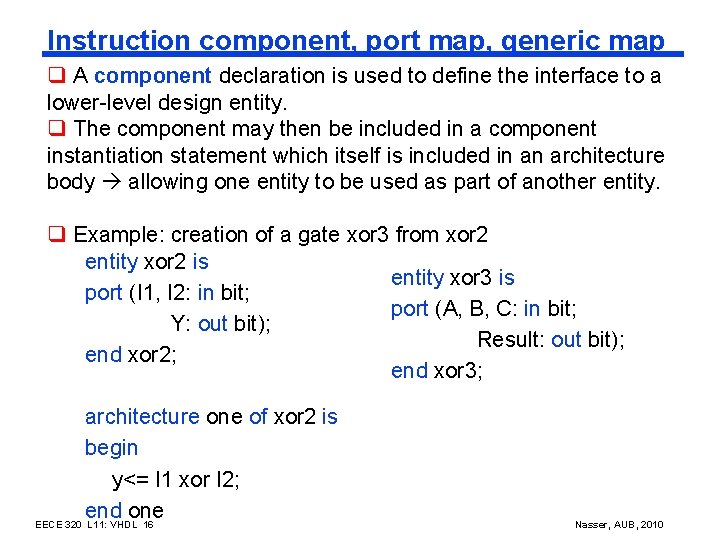

Instruction component, port map, generic map q A component declaration is used to define the interface to a lower-level design entity. q The component may then be included in a component instantiation statement which itself is included in an architecture body allowing one entity to be used as part of another entity. q Example: creation of a gate xor 3 from xor 2 entity xor 2 is entity xor 3 is port (I 1, I 2: in bit; port (A, B, C: in bit; Y: out bit); Result: out bit); end xor 2; end xor 3; architecture one of xor 2 is begin y<= I 1 xor I 2; end one EECE 320 L 11: VHDL 16 Nasser, AUB, 2010

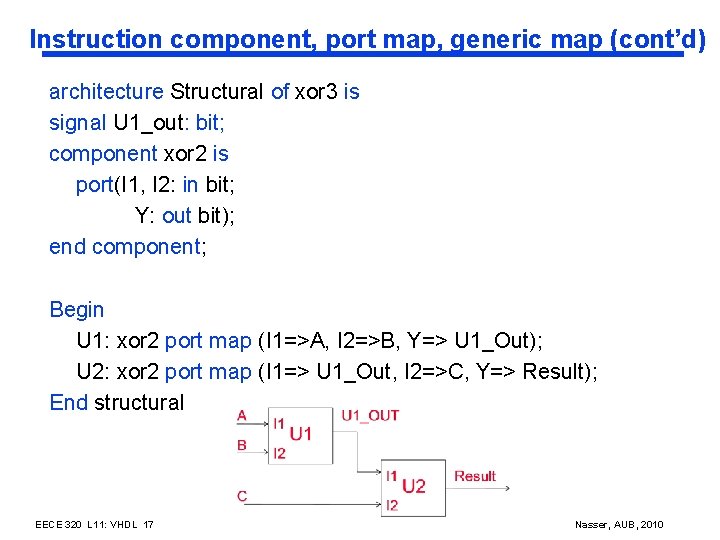

Instruction component, port map, generic map (cont’d) architecture Structural of xor 3 is signal U 1_out: bit; component xor 2 is port(I 1, I 2: in bit; Y: out bit); end component; Begin U 1: xor 2 port map (I 1=>A, I 2=>B, Y=> U 1_Out); U 2: xor 2 port map (I 1=> U 1_Out, I 2=>C, Y=> Result); End structural EECE 320 L 11: VHDL 17 Nasser, AUB, 2010

Next Lecture and Reminders q Next lecture q Reminders EECE 320 L 11: VHDL 18 Nasser, AUB, 2010