EECE 3170 Microprocessor Systems Design I Instructor Dr

- Slides: 31

EECE. 3170 Microprocessor Systems Design I Instructor: Dr. Michael Geiger Summer 2017 Lecture 9: PIC microcontroller intro

Lecture outline n Announcements/reminders q q HW 4 due 1: 00 PM Thursday, 6/8 Exam 2: Monday, 6/12 n n n Will again be allowed one 8. 5” x 11” note sheet, calculator Instruction list provided Today’s lecture: q PIC microcontroller intro 10/24/2020 Microprocessors I: Lecture 9 2

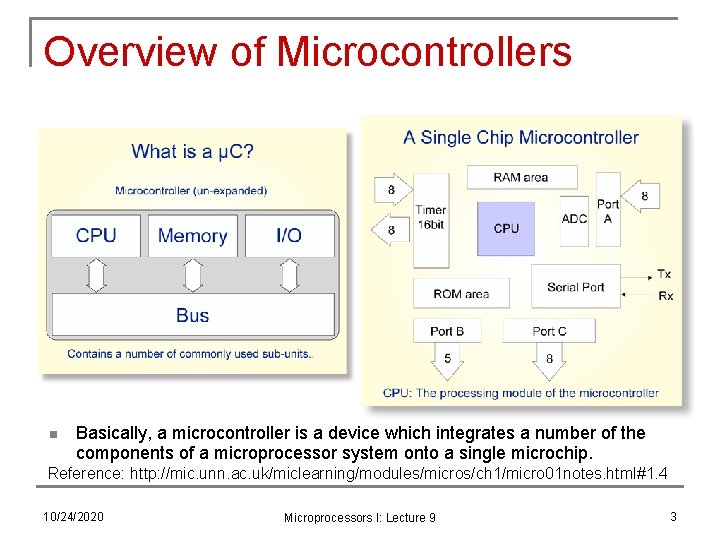

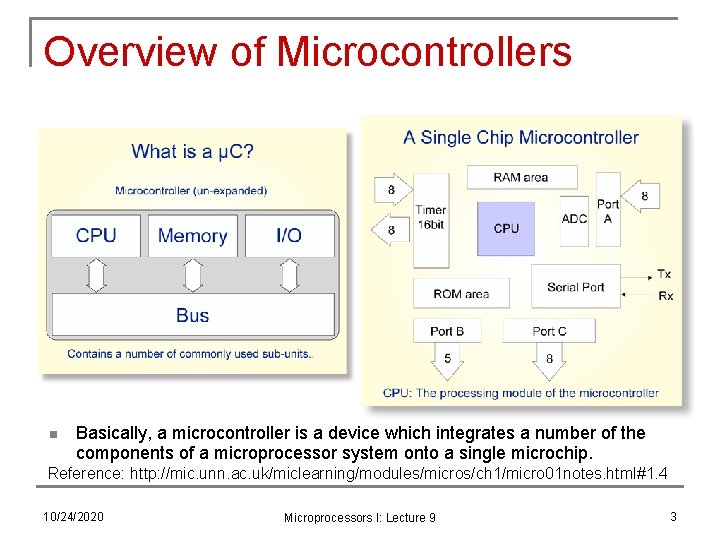

Overview of Microcontrollers n Basically, a microcontroller is a device which integrates a number of the components of a microprocessor system onto a single microchip. Reference: http: //mic. unn. ac. uk/miclearning/modules/micros/ch 1/micro 01 notes. html#1. 4 10/24/2020 Microprocessors I: Lecture 9 3

Microcontroller features n Processor q n On-chip memory q n Usually general-purpose but can be app-specific Often RAM for data, EEPROM/Flash for code Integrated peripherals q Common peripherals n n n q Parallel I/O port(s) Clock generator(s) Timers/event counters Special-purpose devices such as: n n 10/24/2020 Analog-to-digital converter (sensor inputs) Mixed signal components Serial port + other serial interfaces (SPI, USB) Ethernet Microprocessors I: Lecture 9 4

Microcontroller features n Benefits q Typically low-power/low-cost n q Easily programmable n n n Target for embedded applications Simple ISAs (RISC processors) Use of development kits simplifies process Limitations q q Small storage space (registers, memory) Restricted instruction set May be required to multiplex pins Not typically used for high performance 10/24/2020 Microprocessors I: Lecture 9 5

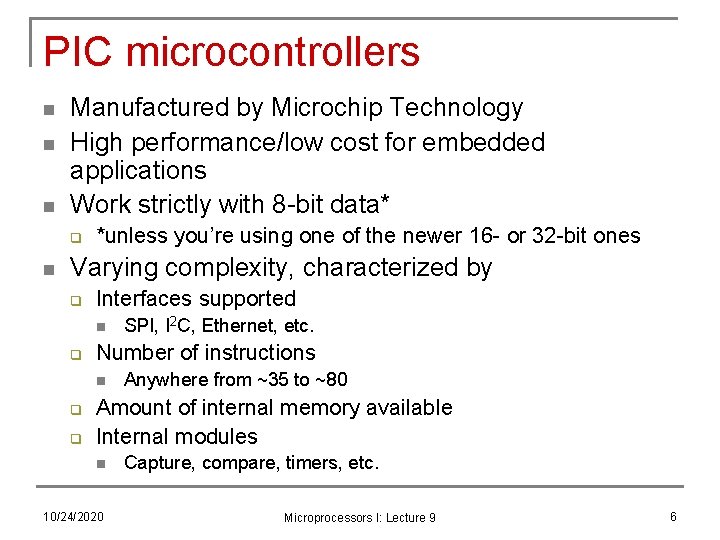

PIC microcontrollers n n n Manufactured by Microchip Technology High performance/low cost for embedded applications Work strictly with 8 -bit data* q n *unless you’re using one of the newer 16 - or 32 -bit ones Varying complexity, characterized by q Interfaces supported n q Number of instructions n q q SPI, I 2 C, Ethernet, etc. Anywhere from ~35 to ~80 Amount of internal memory available Internal modules n 10/24/2020 Capture, compare, timers, etc. Microprocessors I: Lecture 9 6

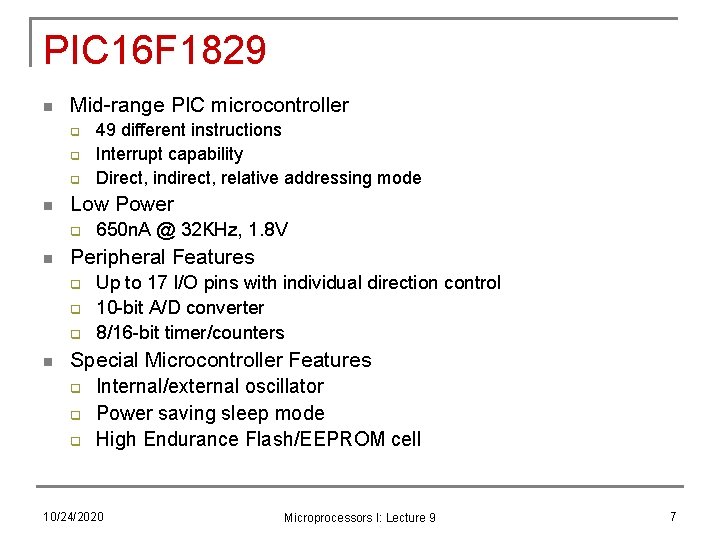

PIC 16 F 1829 n Mid-range PIC microcontroller q q q n Low Power q n 650 n. A @ 32 KHz, 1. 8 V Peripheral Features q q q n 49 different instructions Interrupt capability Direct, indirect, relative addressing mode Up to 17 I/O pins with individual direction control 10 -bit A/D converter 8/16 -bit timer/counters Special Microcontroller Features q Internal/external oscillator q Power saving sleep mode q High Endurance Flash/EEPROM cell 10/24/2020 Microprocessors I: Lecture 9 7

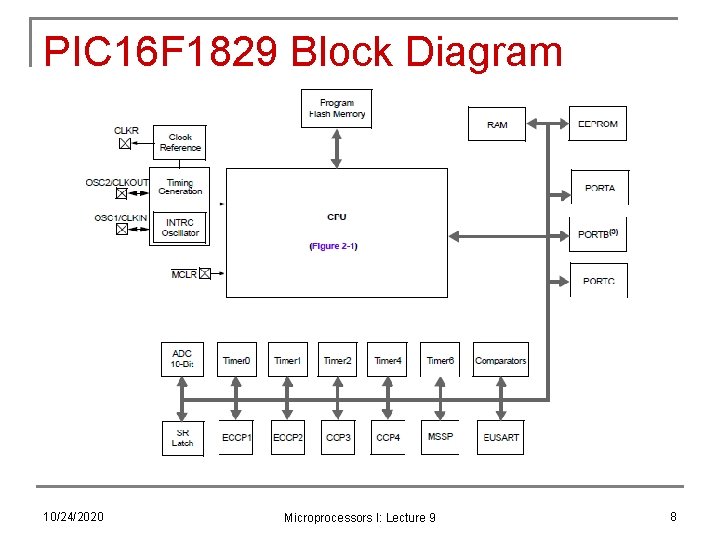

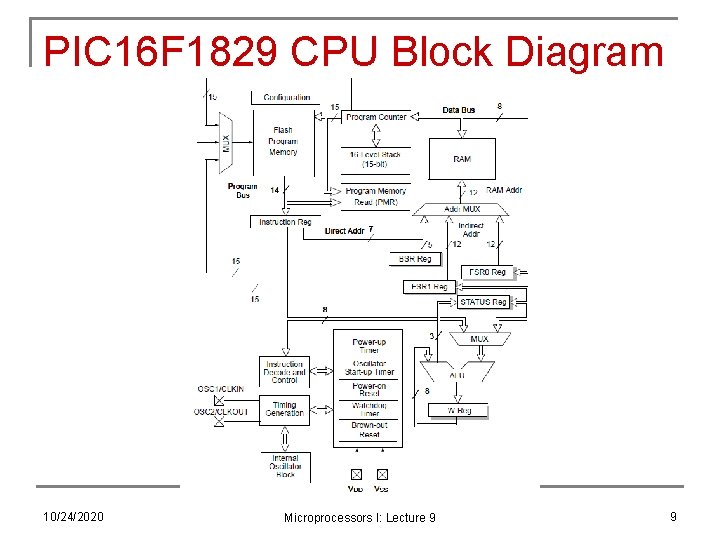

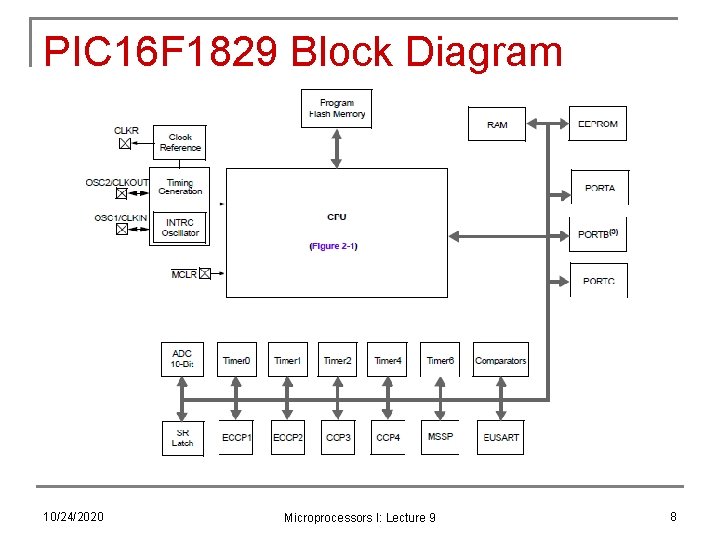

PIC 16 F 1829 Block Diagram 10/24/2020 Microprocessors I: Lecture 9 8

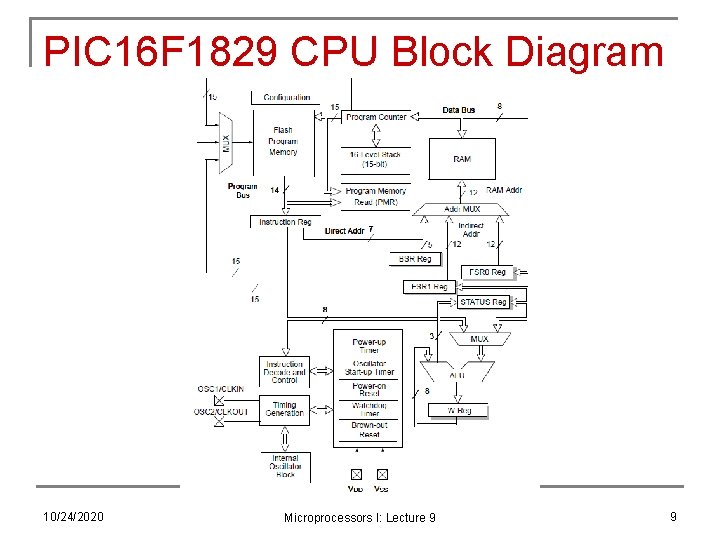

PIC 16 F 1829 CPU Block Diagram 10/24/2020 Microprocessors I: Lecture 9 9

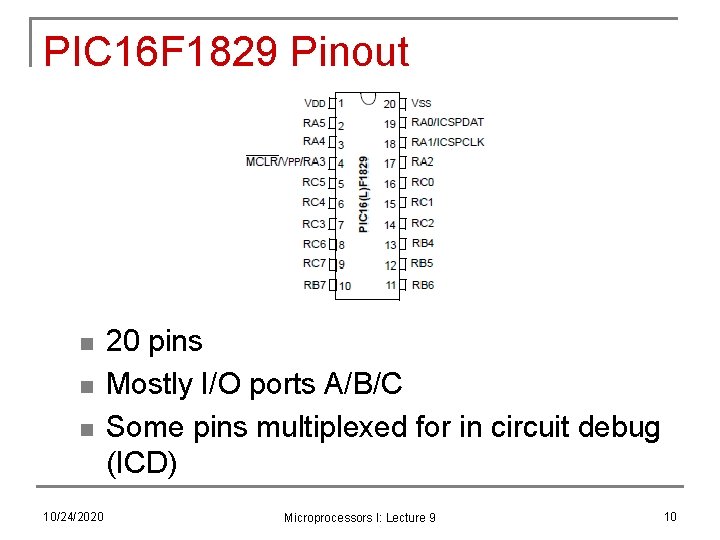

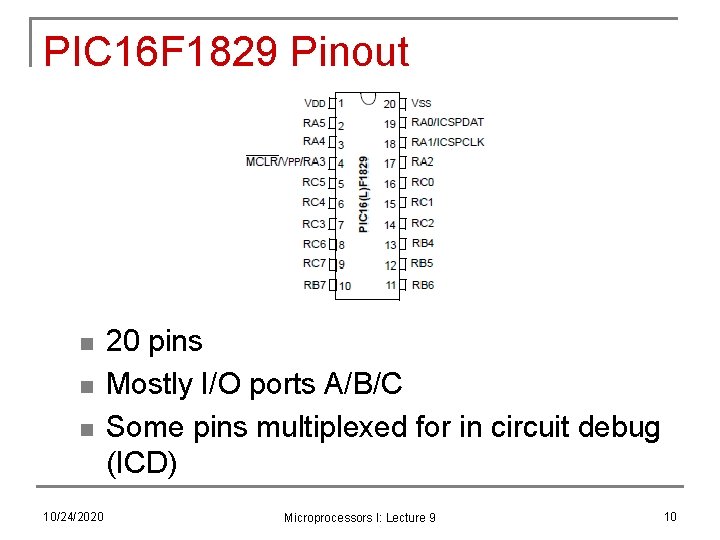

PIC 16 F 1829 Pinout n n n 10/24/2020 20 pins Mostly I/O ports A/B/C Some pins multiplexed for in circuit debug (ICD) Microprocessors I: Lecture 9 10

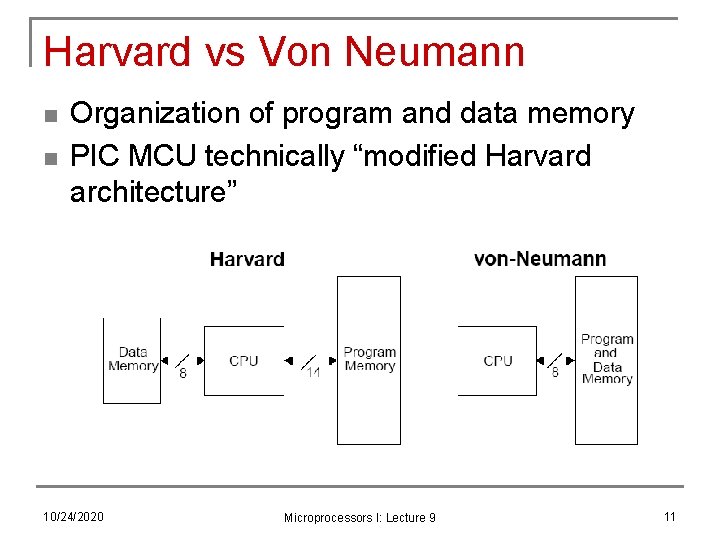

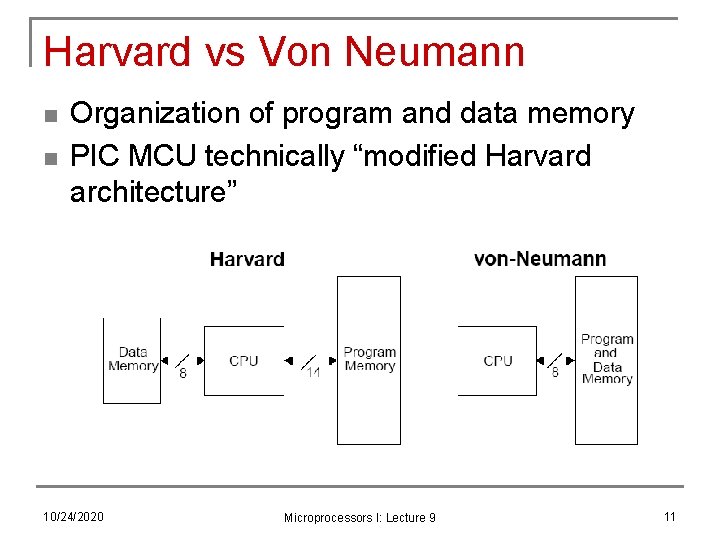

Harvard vs Von Neumann n n Organization of program and data memory PIC MCU technically “modified Harvard architecture” 10/24/2020 Microprocessors I: Lecture 9 11

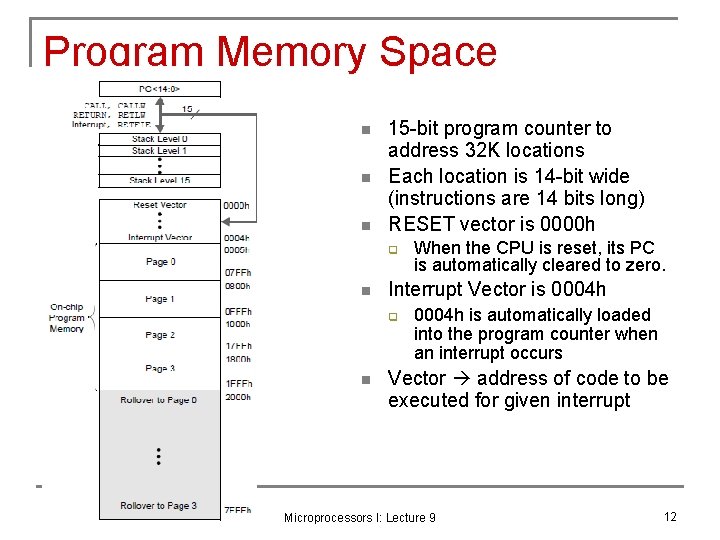

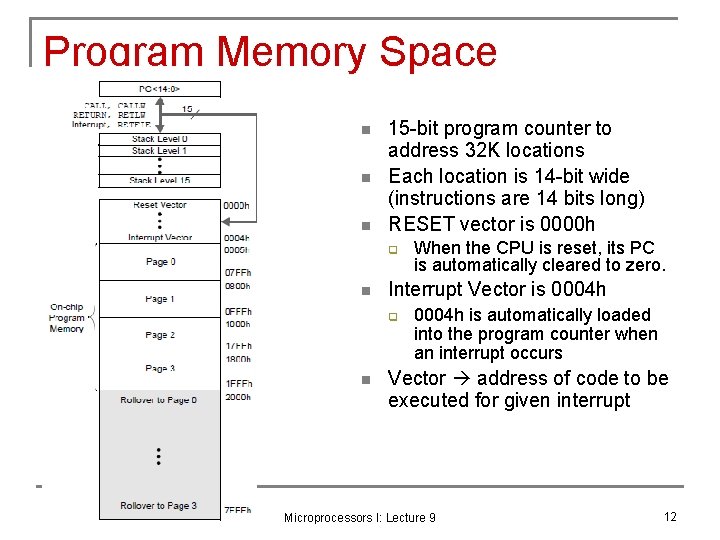

Program Memory Space n n n 15 -bit program counter to address 32 K locations Each location is 14 -bit wide (instructions are 14 bits long) RESET vector is 0000 h q n Interrupt Vector is 0004 h q n 10/24/2020 When the CPU is reset, its PC is automatically cleared to zero. 0004 h is automatically loaded into the program counter when an interrupt occurs Vector address of code to be executed for given interrupt Microprocessors I: Lecture 9 12

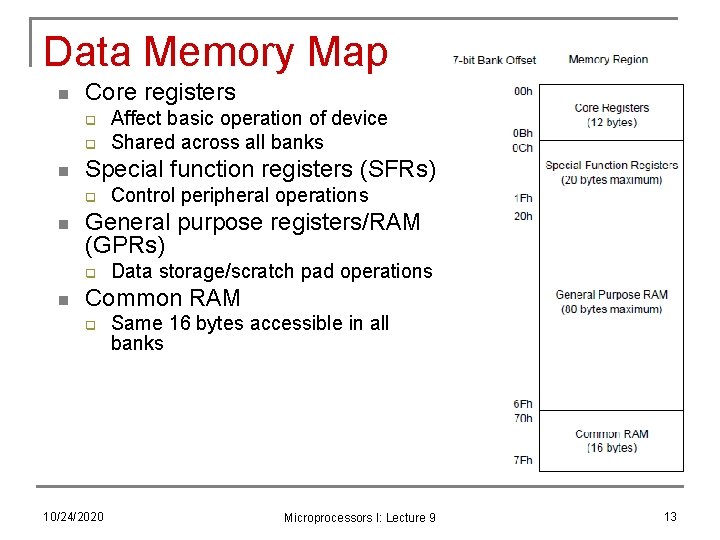

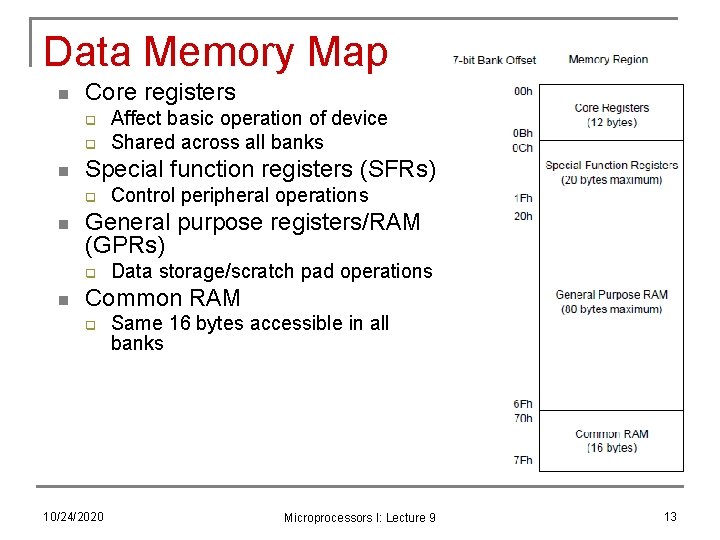

Data Memory Map n Core registers q q n Special function registers (SFRs) q n Control peripheral operations General purpose registers/RAM (GPRs) q n Affect basic operation of device Shared across all banks Data storage/scratch pad operations Common RAM q 10/24/2020 Same 16 bytes accessible in all banks Microprocessors I: Lecture 9 13

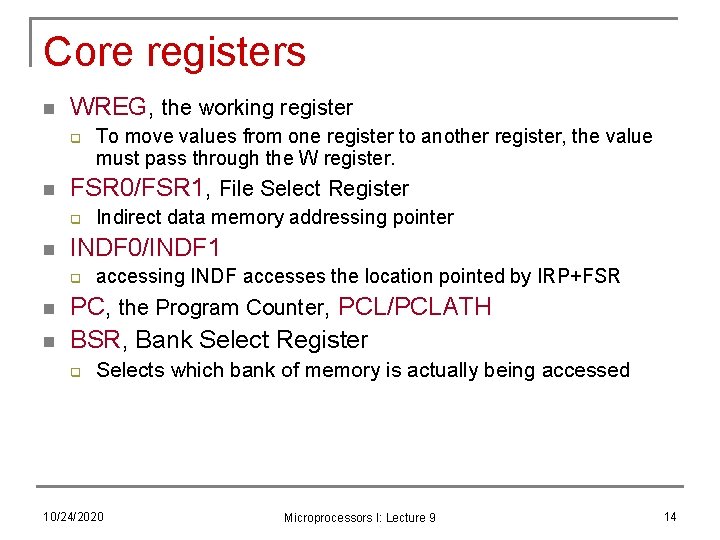

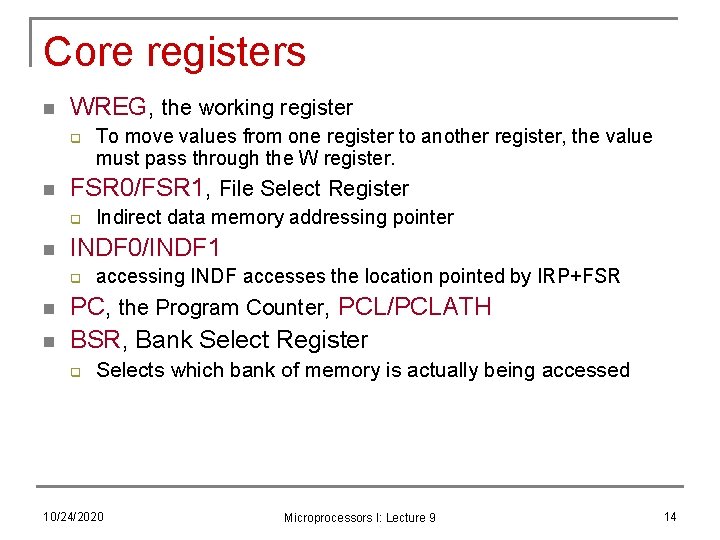

Core registers n WREG, the working register q n FSR 0/FSR 1, File Select Register q n n Indirect data memory addressing pointer INDF 0/INDF 1 q n To move values from one register to another register, the value must pass through the W register. accessing INDF accesses the location pointed by IRP+FSR PC, the Program Counter, PCL/PCLATH BSR, Bank Select Register q Selects which bank of memory is actually being accessed 10/24/2020 Microprocessors I: Lecture 9 14

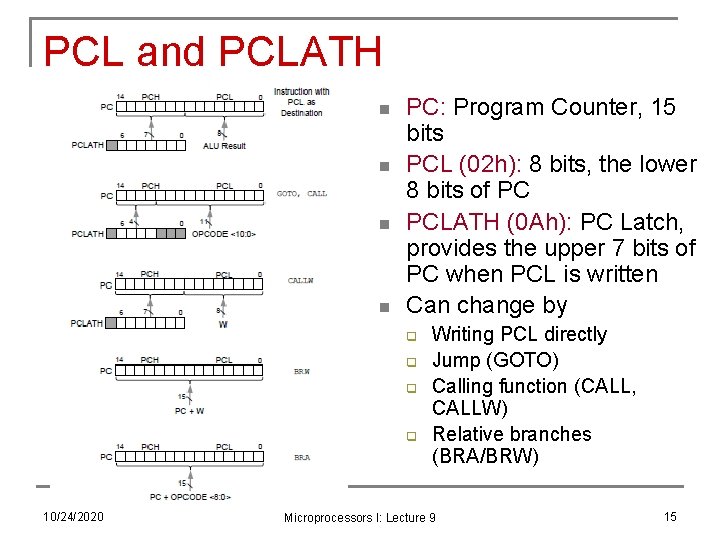

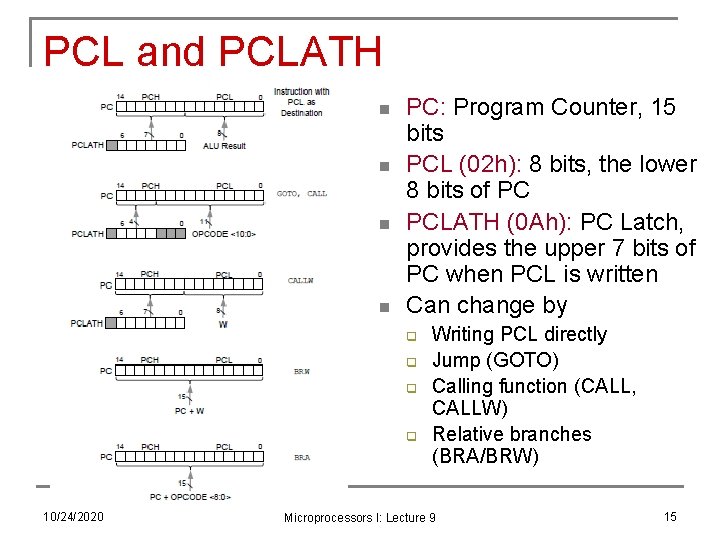

PCL and PCLATH n n PC: Program Counter, 15 bits PCL (02 h): 8 bits, the lower 8 bits of PC PCLATH (0 Ah): PC Latch, provides the upper 7 bits of PC when PCL is written Can change by q q 10/24/2020 Writing PCL directly Jump (GOTO) Calling function (CALL, CALLW) Relative branches (BRA/BRW) Microprocessors I: Lecture 9 15

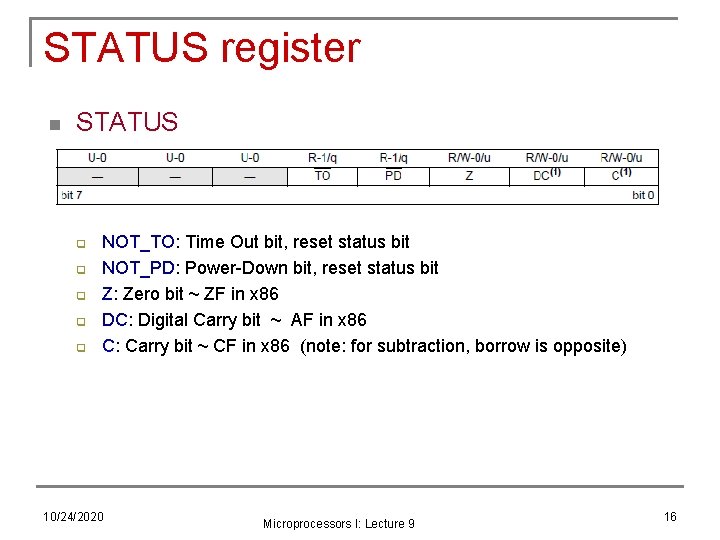

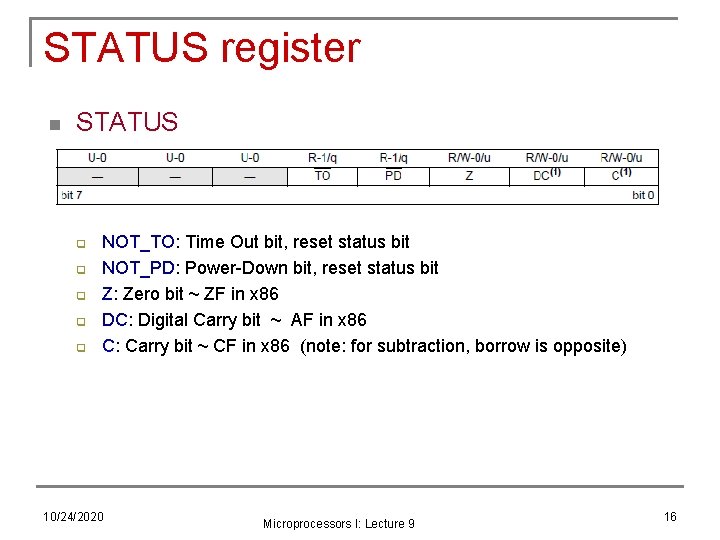

STATUS register n STATUS q q q NOT_TO: Time Out bit, reset status bit NOT_PD: Power-Down bit, reset status bit Z: Zero bit ~ ZF in x 86 DC: Digital Carry bit ~ AF in x 86 C: Carry bit ~ CF in x 86 (note: for subtraction, borrow is opposite) 10/24/2020 Microprocessors I: Lecture 9 16

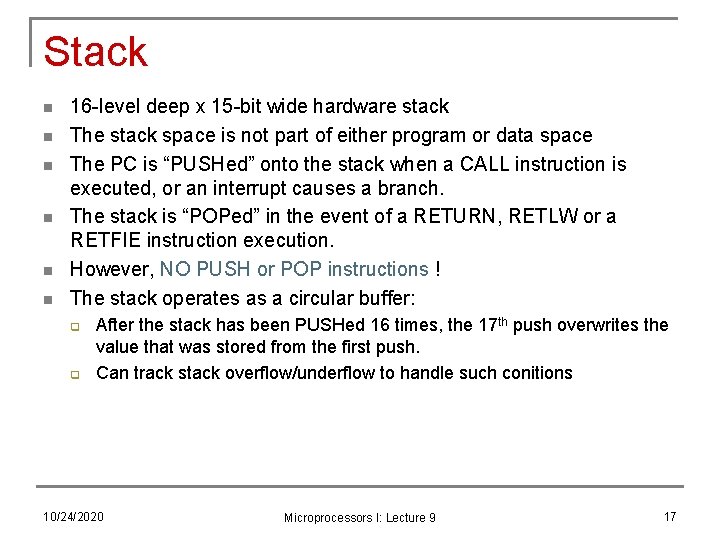

Stack n n n 16 -level deep x 15 -bit wide hardware stack The stack space is not part of either program or data space The PC is “PUSHed” onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is “POPed” in the event of a RETURN, RETLW or a RETFIE instruction execution. However, NO PUSH or POP instructions ! The stack operates as a circular buffer: q q After the stack has been PUSHed 16 times, the 17 th push overwrites the value that was stored from the first push. Can track stack overflow/underflow to handle such conitions 10/24/2020 Microprocessors I: Lecture 9 17

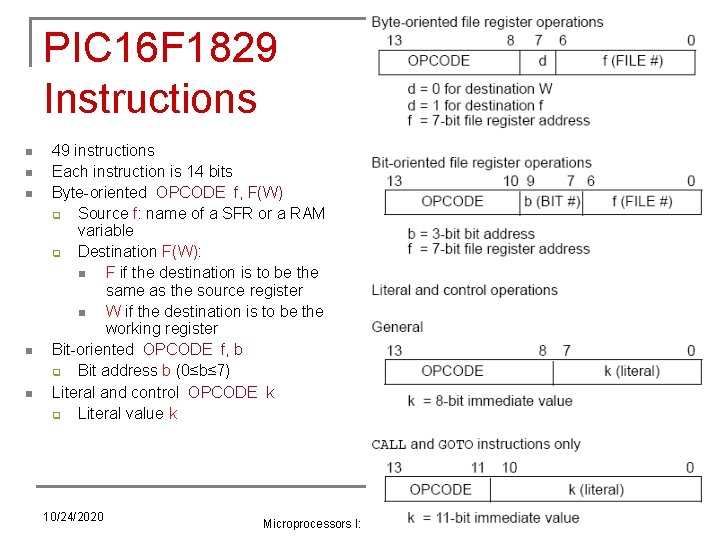

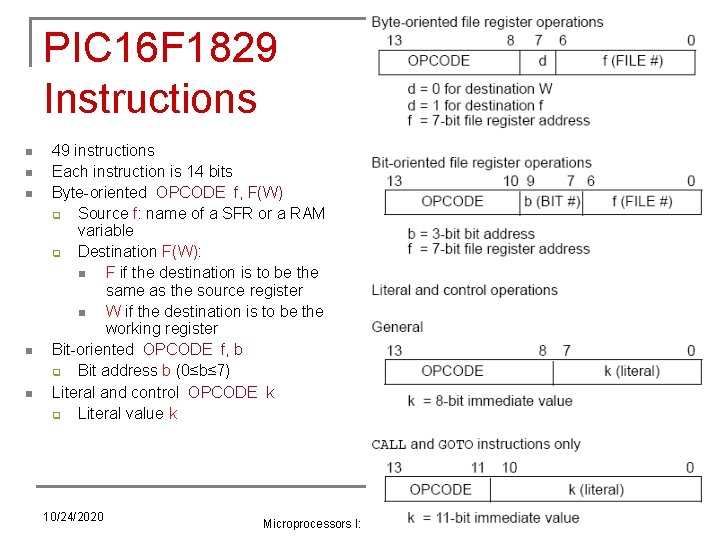

PIC 16 F 1829 Instructions n n n 49 instructions Each instruction is 14 bits Byte-oriented OPCODE f, F(W) q Source f: name of a SFR or a RAM variable q Destination F(W): n F if the destination is to be the same as the source register n W if the destination is to be the working register Bit-oriented OPCODE f, b q Bit address b (0≤b≤ 7) Literal and control OPCODE k q Literal value k 10/24/2020 Microprocessors I: Lecture 9 18

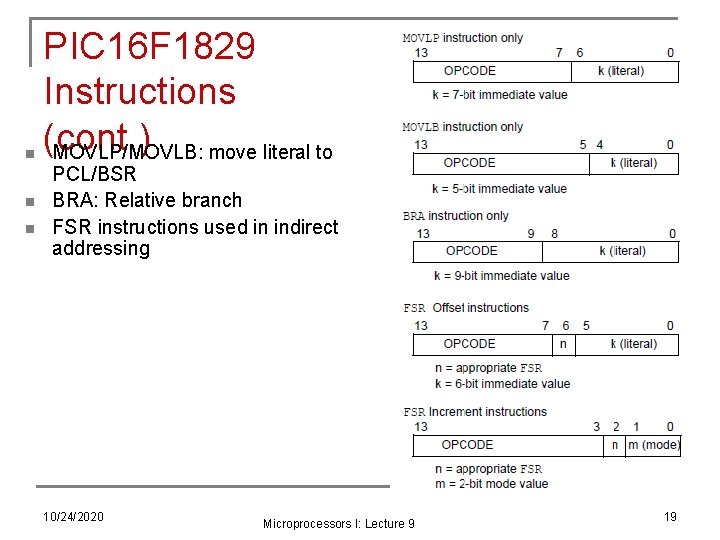

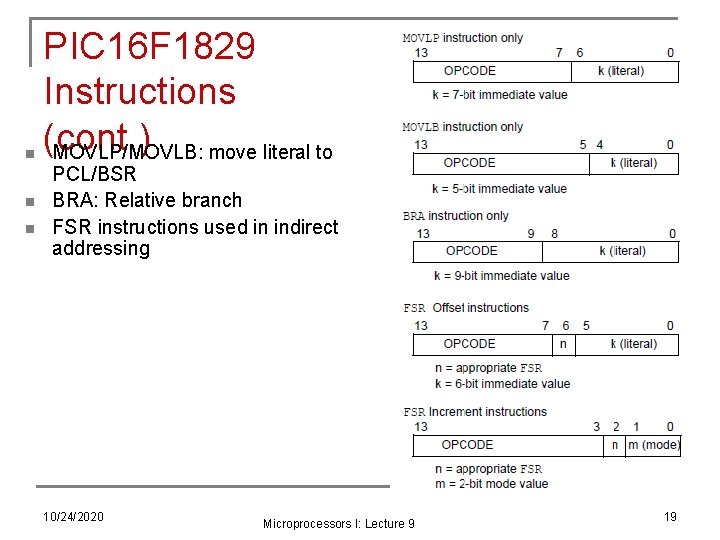

n n n PIC 16 F 1829 Instructions (cont. ) MOVLP/MOVLB: move literal to PCL/BSR BRA: Relative branch FSR instructions used in indirect addressing 10/24/2020 Microprocessors I: Lecture 9 19

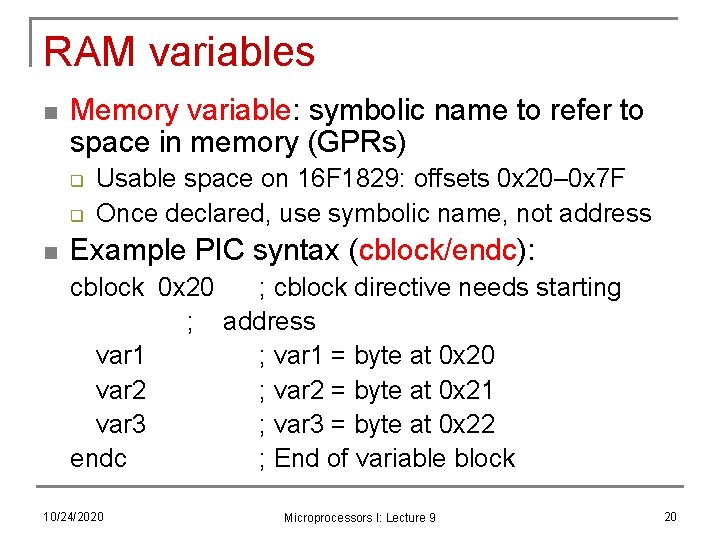

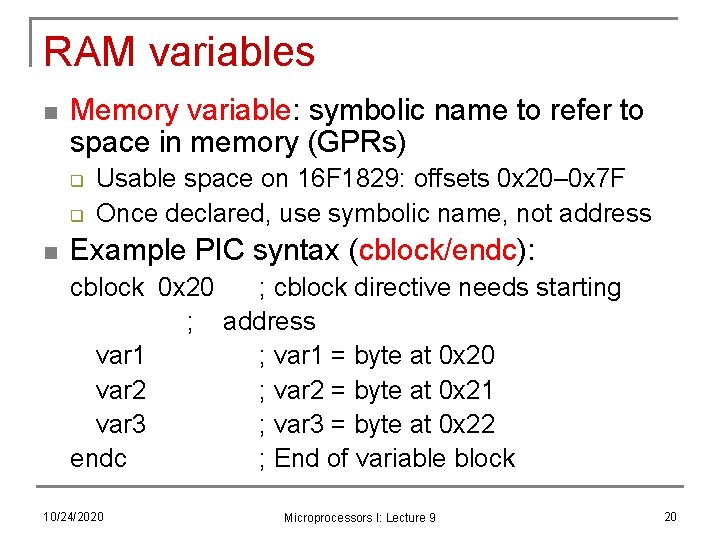

RAM variables n Memory variable: symbolic name to refer to space in memory (GPRs) q q n Usable space on 16 F 1829: offsets 0 x 20– 0 x 7 F Once declared, use symbolic name, not address Example PIC syntax (cblock/endc): cblock 0 x 20 ; cblock directive needs starting ; address var 1 ; var 1 = byte at 0 x 20 var 2 ; var 2 = byte at 0 x 21 var 3 ; var 3 = byte at 0 x 22 endc ; End of variable block 10/24/2020 Microprocessors I: Lecture 9 20

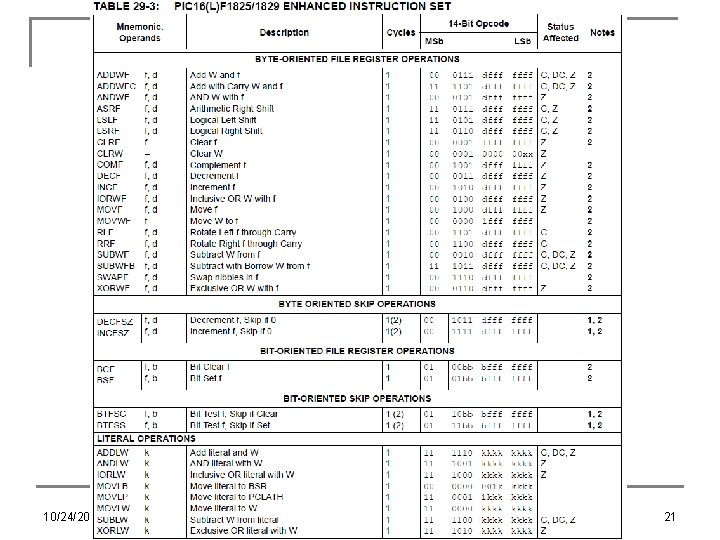

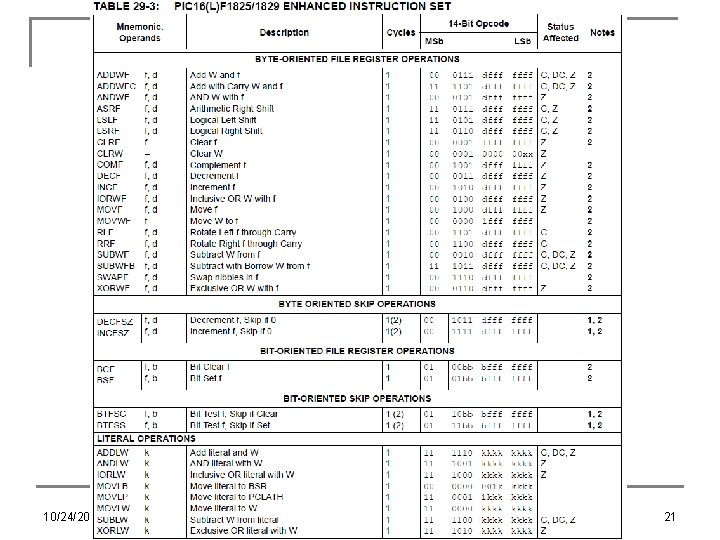

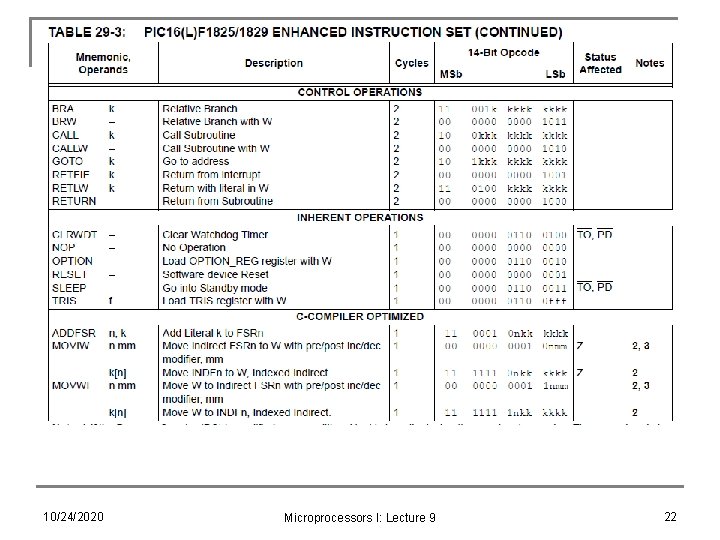

10/24/2020 Microprocessors I: Lecture 9 21

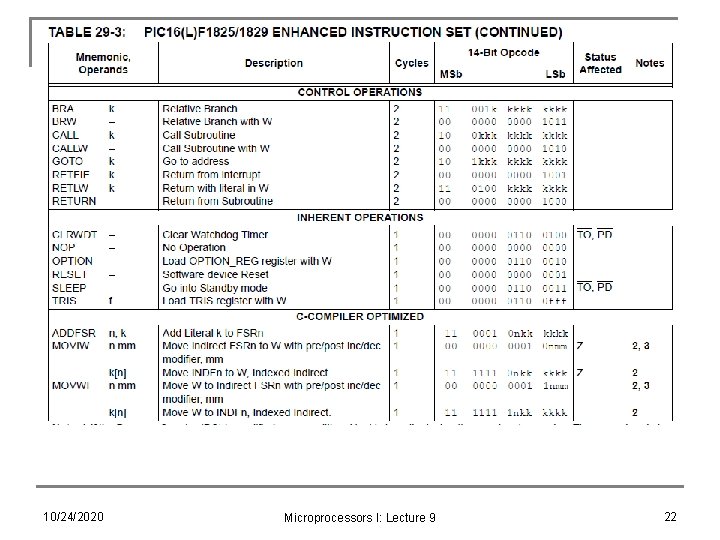

10/24/2020 Microprocessors I: Lecture 9 22

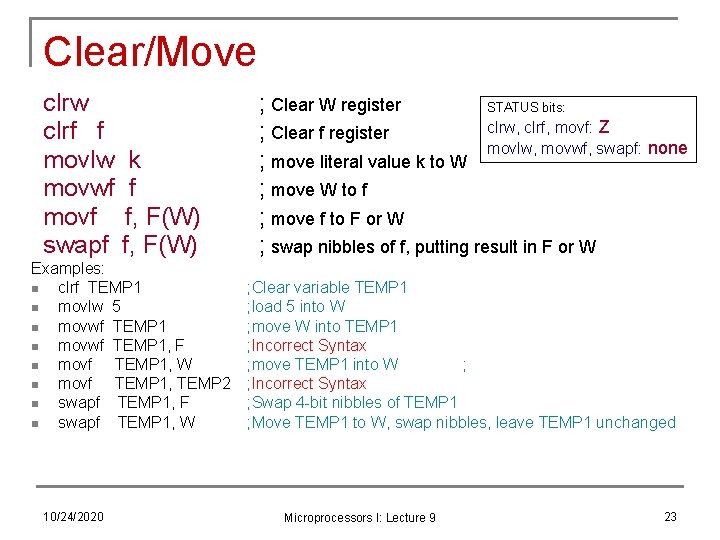

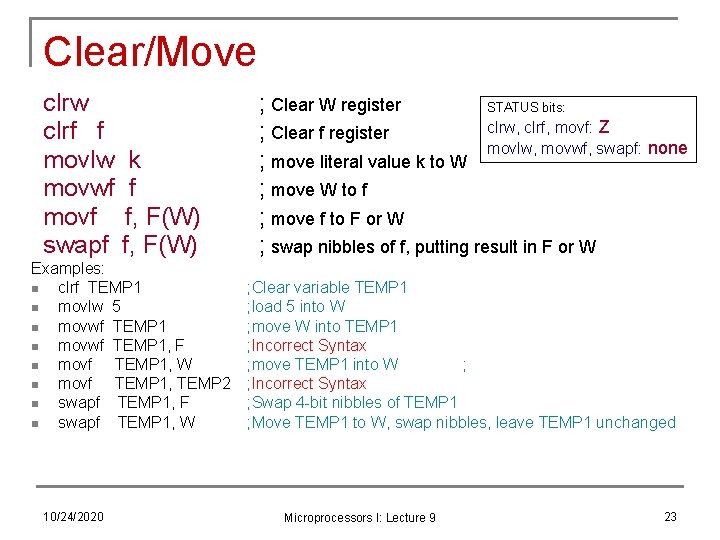

Clear/Move clrw clrf f movlw k movwf f movf f, F(W) swapf f, F(W) Examples: n clrf TEMP 1 n movlw 5 n movwf TEMP 1, F n movf TEMP 1, W n movf TEMP 1, TEMP 2 n swapf TEMP 1, F n swapf TEMP 1, W 10/24/2020 ; Clear W register STATUS bits: clrw, clrf, movf: Z ; Clear f register movlw, movwf, swapf: none ; move literal value k to W ; move W to f ; move f to F or W ; swap nibbles of f, putting result in F or W ; Clear variable TEMP 1 ; load 5 into W ; move W into TEMP 1 ; Incorrect Syntax ; move TEMP 1 into W ; ; Incorrect Syntax ; Swap 4 -bit nibbles of TEMP 1 ; Move TEMP 1 to W, swap nibbles, leave TEMP 1 unchanged Microprocessors I: Lecture 9 23

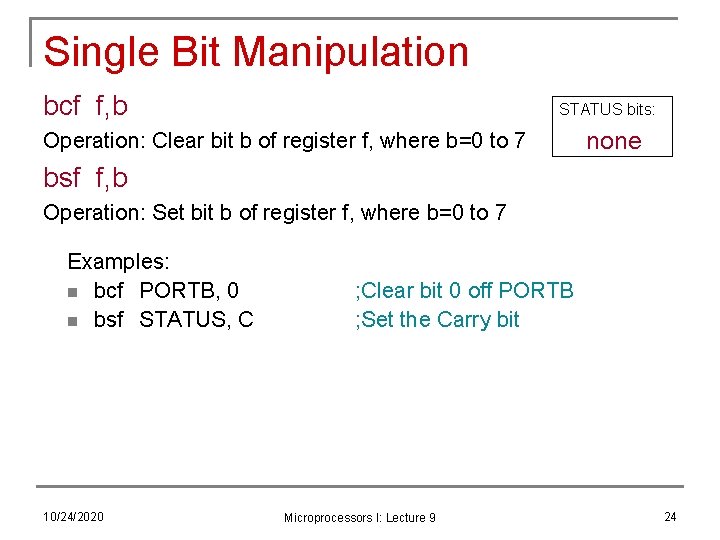

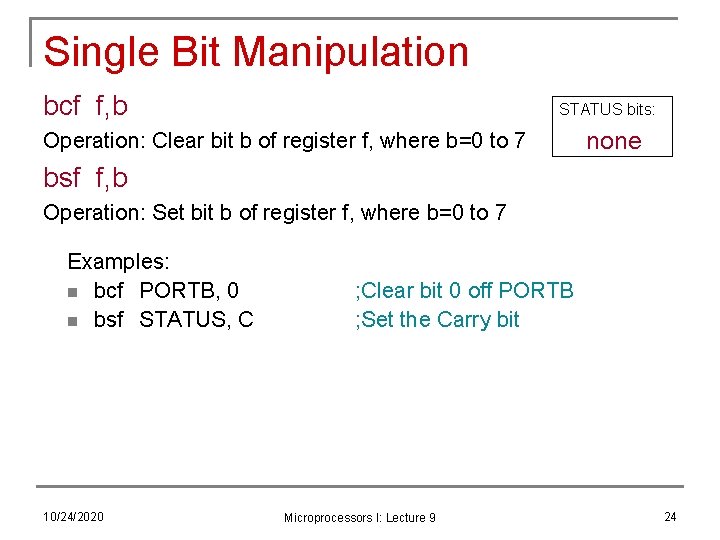

Single Bit Manipulation bcf f, b STATUS bits: Operation: Clear bit b of register f, where b=0 to 7 none bsf f, b Operation: Set bit b of register f, where b=0 to 7 Examples: n bcf PORTB, 0 n bsf STATUS, C 10/24/2020 ; Clear bit 0 off PORTB ; Set the Carry bit Microprocessors I: Lecture 9 24

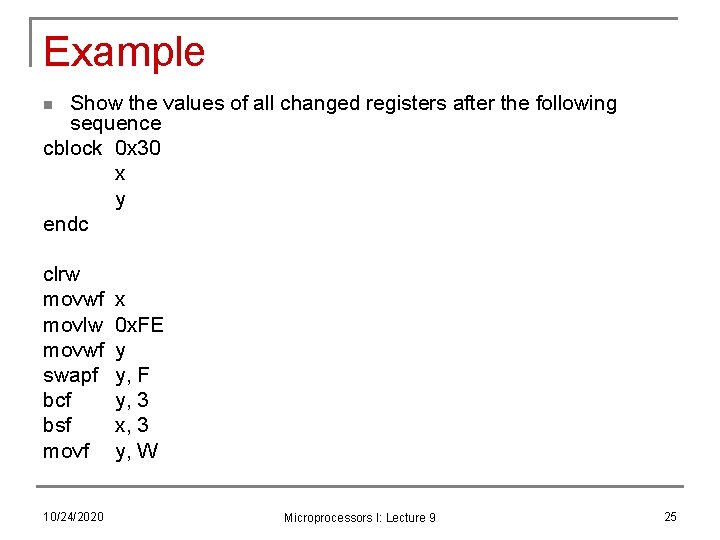

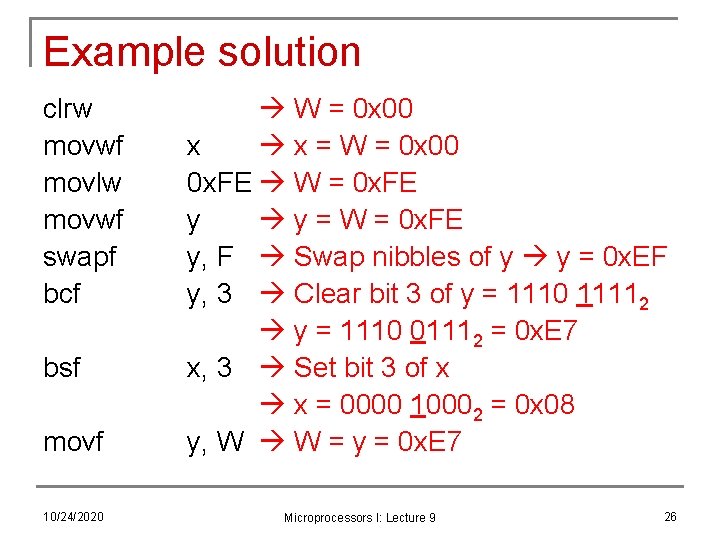

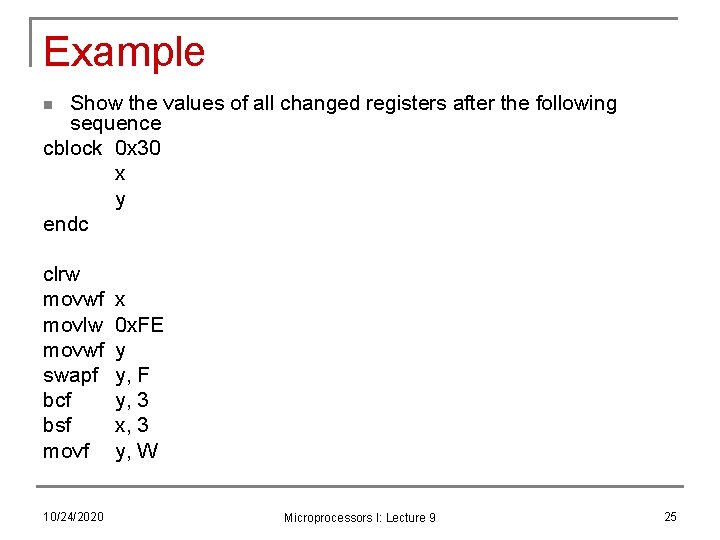

Example Show the values of all changed registers after the following sequence cblock 0 x 30 x y endc n clrw movwf movlw movwf swapf bcf bsf movf 10/24/2020 x 0 x. FE y y, F y, 3 x, 3 y, W Microprocessors I: Lecture 9 25

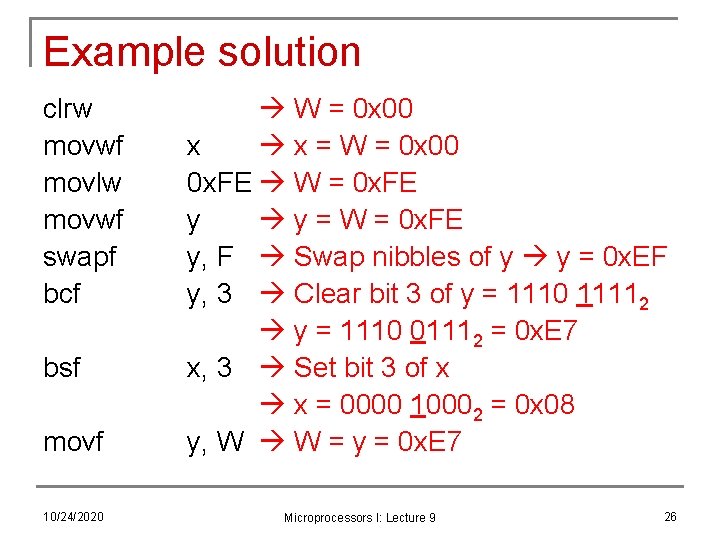

Example solution clrw movwf movlw movwf swapf bcf bsf movf 10/24/2020 W = 0 x 00 x x = W = 0 x 00 0 x. FE W = 0 x. FE y y = W = 0 x. FE y, F Swap nibbles of y y = 0 x. EF y, 3 Clear bit 3 of y = 1110 11112 y = 1110 01112 = 0 x. E 7 x, 3 Set bit 3 of x x = 0000 10002 = 0 x 08 y, W W = y = 0 x. E 7 Microprocessors I: Lecture 9 26

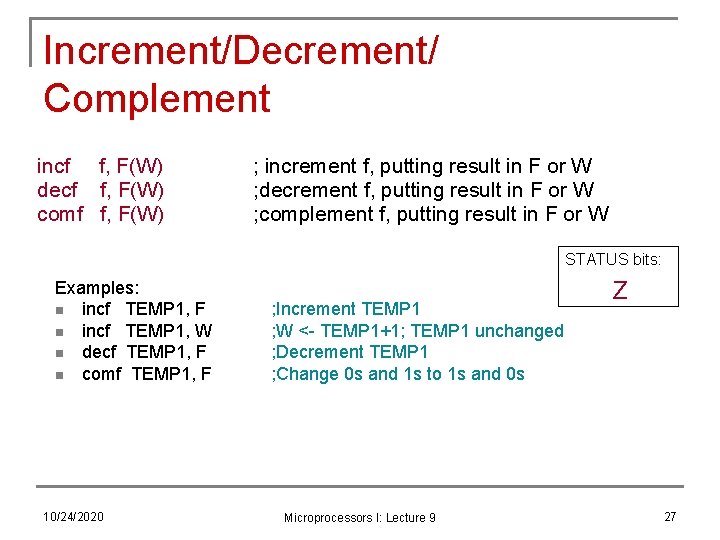

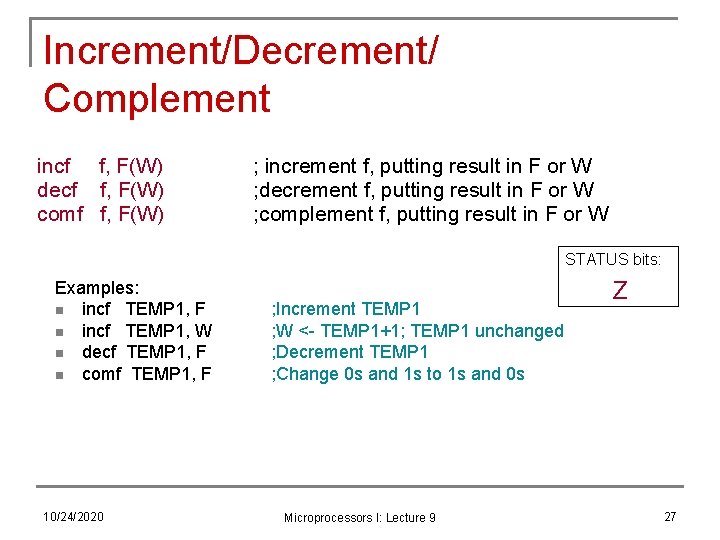

Increment/Decrement/ Complement incf f, F(W) decf f, F(W) comf f, F(W) ; increment f, putting result in F or W ; decrement f, putting result in F or W ; complement f, putting result in F or W STATUS bits: Examples: n incf TEMP 1, F n incf TEMP 1, W n decf TEMP 1, F n comf TEMP 1, F 10/24/2020 ; Increment TEMP 1 ; W <- TEMP 1+1; TEMP 1 unchanged ; Decrement TEMP 1 ; Change 0 s and 1 s to 1 s and 0 s Microprocessors I: Lecture 9 Z 27

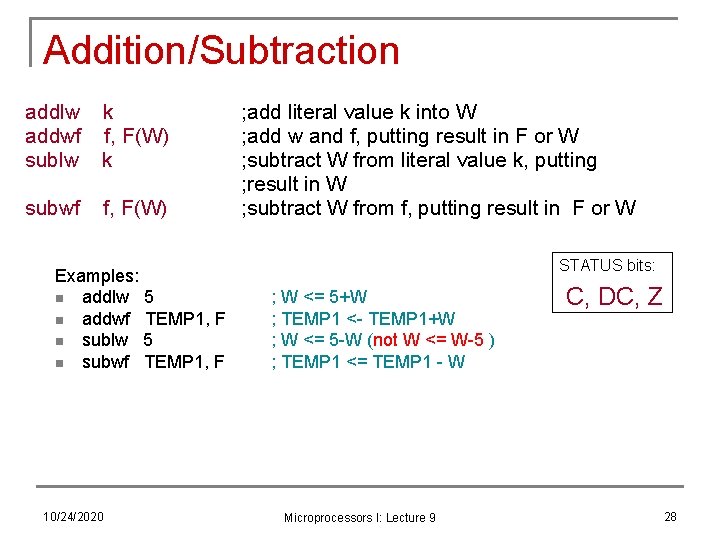

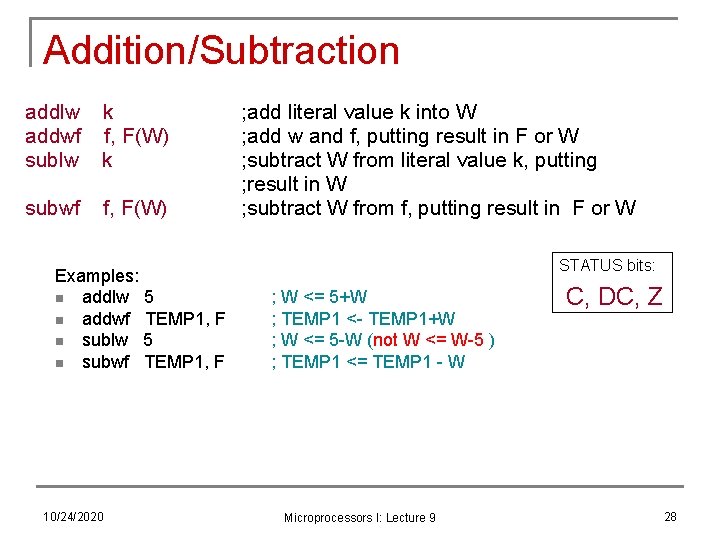

Addition/Subtraction addlw k addwf f, F(W) sublw k subwf f, F(W) Examples: n addlw 5 n addwf TEMP 1, F n sublw 5 n subwf TEMP 1, F 10/24/2020 ; add literal value k into W ; add w and f, putting result in F or W ; subtract W from literal value k, putting ; result in W ; subtract W from f, putting result in F or W STATUS bits: ; W <= 5+W ; TEMP 1 <- TEMP 1+W ; W <= 5 -W (not W <= W-5 ) ; TEMP 1 <= TEMP 1 - W Microprocessors I: Lecture 9 C, DC, Z 28

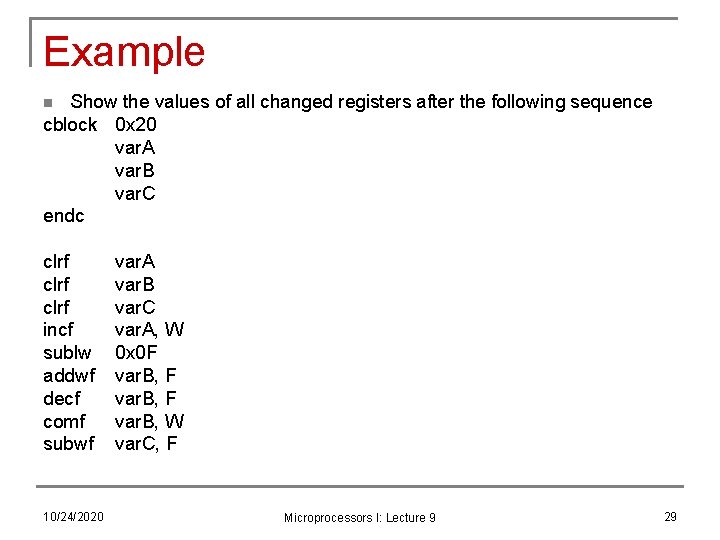

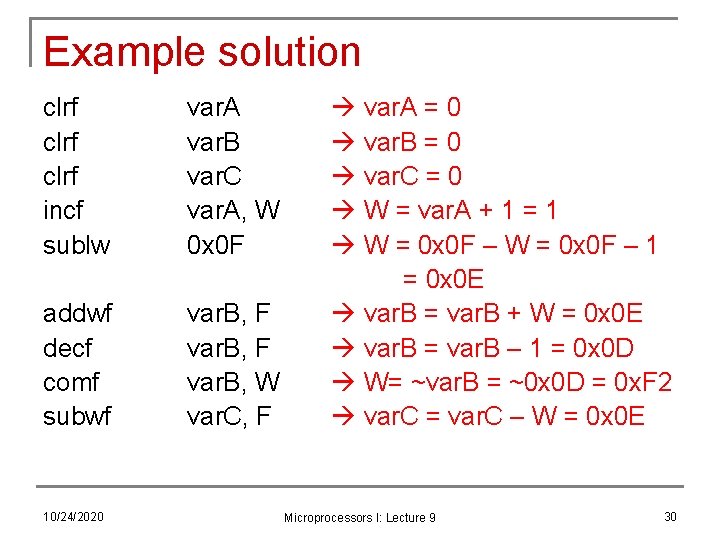

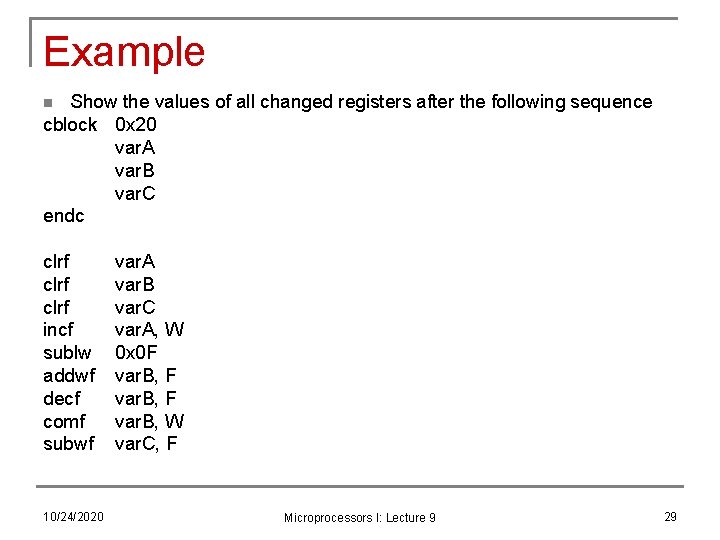

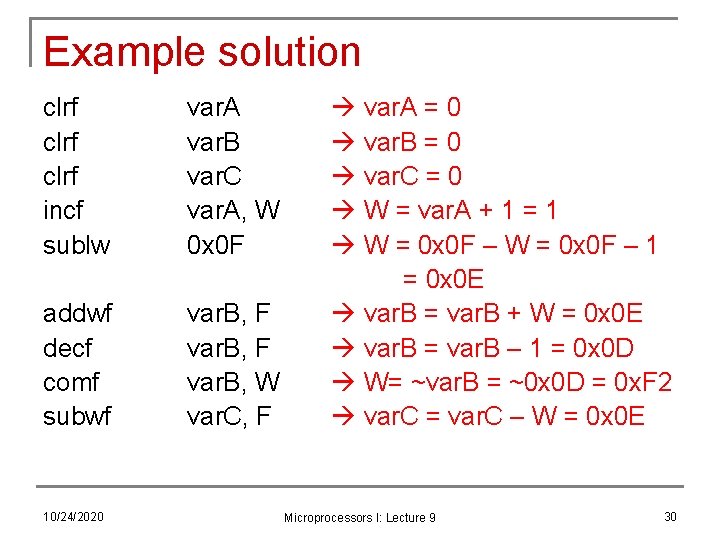

Example Show the values of all changed registers after the following sequence cblock 0 x 20 var. A var. B var. C endc n clrf incf sublw addwf decf comf subwf 10/24/2020 var. A var. B var. C var. A, W 0 x 0 F var. B, W var. C, F Microprocessors I: Lecture 9 29

Example solution clrf incf sublw var. A var. B var. C var. A, W 0 x 0 F addwf decf comf subwf var. B, F var. B, W var. C, F 10/24/2020 var. A = 0 var. B = 0 var. C = 0 W = var. A + 1 = 1 W = 0 x 0 F – 1 = 0 x 0 E var. B = var. B + W = 0 x 0 E var. B = var. B – 1 = 0 x 0 D W= ~var. B = ~0 x 0 D = 0 x. F 2 var. C = var. C – W = 0 x 0 E Microprocessors I: Lecture 9 30

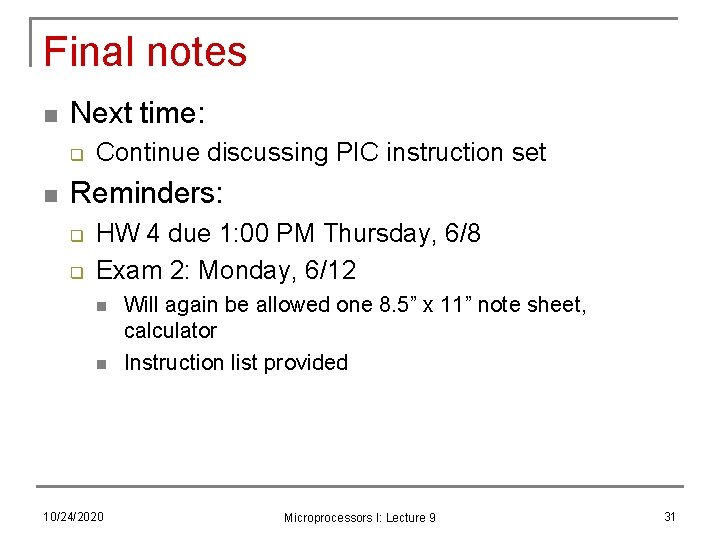

Final notes n Next time: q n Continue discussing PIC instruction set Reminders: q q HW 4 due 1: 00 PM Thursday, 6/8 Exam 2: Monday, 6/12 n n 10/24/2020 Will again be allowed one 8. 5” x 11” note sheet, calculator Instruction list provided Microprocessors I: Lecture 9 31