EE 501 Analog IC Design Instructor Contact Information

- Slides: 30

EE 501 Analog IC Design • Instructor Contact Information – Name: Degang Chen – Office: 2134 Coover Hall – Email: djchen@iastate. edu – Phone: 294 -6277 – Office Hours: after classes Or any time convenient to you – Please include "EE 501" in the subject line in all email communications to avoid autodeleting or junk-filtering

EE 501 Analog IC Design • TA Contact Information – – – Name: Voice phone: E-mail: Office hour: Hao Meng, Xu Zhang (515)708 1212, (515)708 0589 hmeng@iastate. edu; cxzhang 3102 Coover Hall TBA – Senior graduate students in 3102, 3108, 3011, 3201, and 2201 may also be able to help with your Cadence simulation questions.

Degang Chen Jerry Junkins Chair of Electrical & Computer Eng. Director of Analog and Mixed-signal Design Center Iowa State University, Ames, IA 50011 djchen@iastate. edu, 515 -294 -6277 • BS in instrumentation and automation, 1984, Tsinghua University • Ph. D in control systems, 1992, Univ. California, Santa Barbara • John Pierce Instructor, Cal Tech • ISU Professor after that

Recent Research Focuses • AMS Circuit Design Techniques – Op amp performance enhancement techniques – Matching improvement studies – Data converters, temp sensors, biosensors, LDOs • Analog Verification – Verification against undesired stuck-able operating points – Verification against undesired oscillation mode – 0 dppm analog fault coverage • Test Algorithms for Time/Cost Reduction – Linearity testing – Spectral performance testing – Jitter separation and characterization • BIST, BIST-based Calibration, and BIST for Design

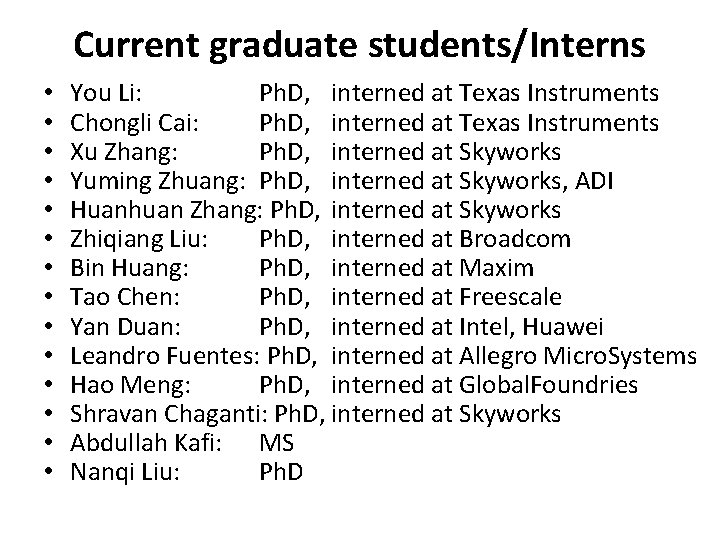

Current graduate students/Interns • • • • You Li: Ph. D, interned at Texas Instruments Chongli Cai: Ph. D, interned at Texas Instruments Xu Zhang: Ph. D, interned at Skyworks Yuming Zhuang: Ph. D, interned at Skyworks, ADI Huanhuan Zhang: Ph. D, interned at Skyworks Zhiqiang Liu: Ph. D, interned at Broadcom Bin Huang: Ph. D, interned at Maxim Tao Chen: Ph. D, interned at Freescale Yan Duan: Ph. D, interned at Intel, Huawei Leandro Fuentes: Ph. D, interned at Allegro Micro. Systems Hao Meng: Ph. D, interned at Global. Foundries Shravan Chaganti: Ph. D, interned at Skyworks Abdullah Kafi: MS Nanqi Liu: Ph. D

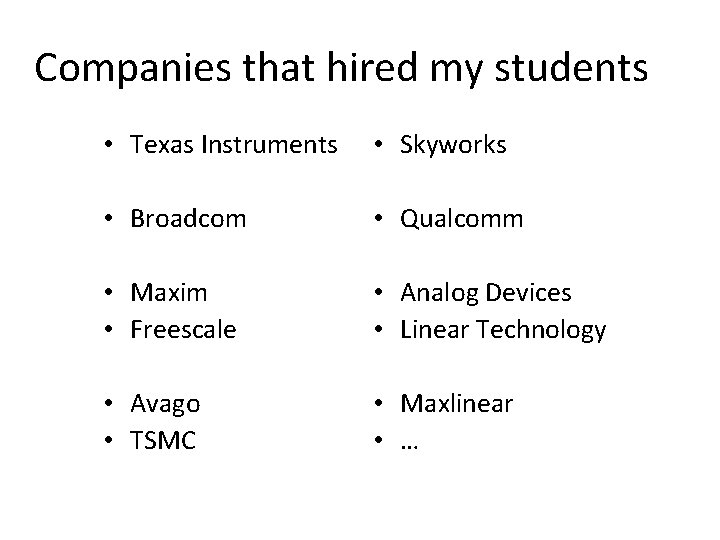

Companies that hired my students • Texas Instruments • Skyworks • Broadcom • Qualcomm • Maxim • Freescale • Analog Devices • Linear Technology • Avago • TSMC • Maxlinear • …

EE 501 Analog IC Design • Student Introduction – Email TA and me your contact information • For us to contact you – Brief intro • • • Name, and nick name if you have one Advisor Research Area MS/Ph. D? Which year IC design experience Cadence experience – Study / lab / project partners

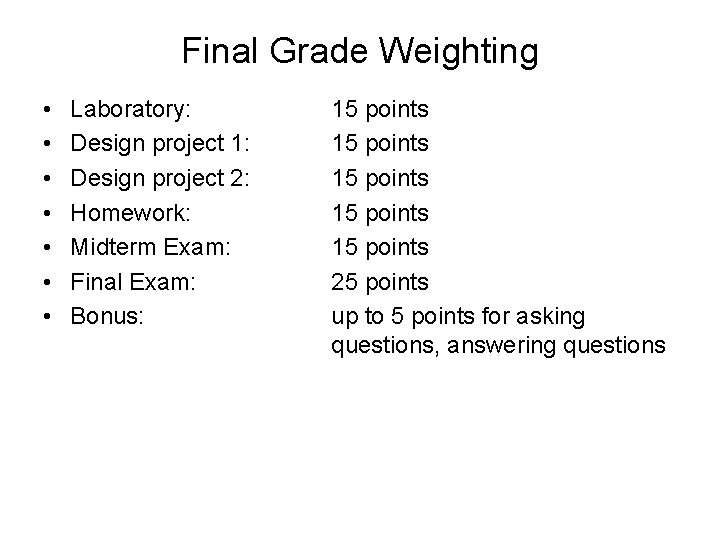

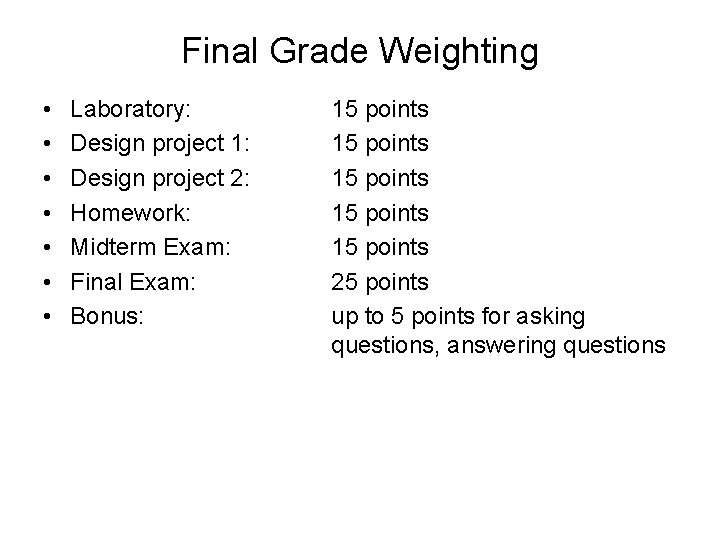

Final Grade Weighting • • Laboratory: Design project 1: Design project 2: Homework: Midterm Exam: Final Exam: Bonus: 15 points 15 points 25 points up to 5 points for asking questions, answering questions

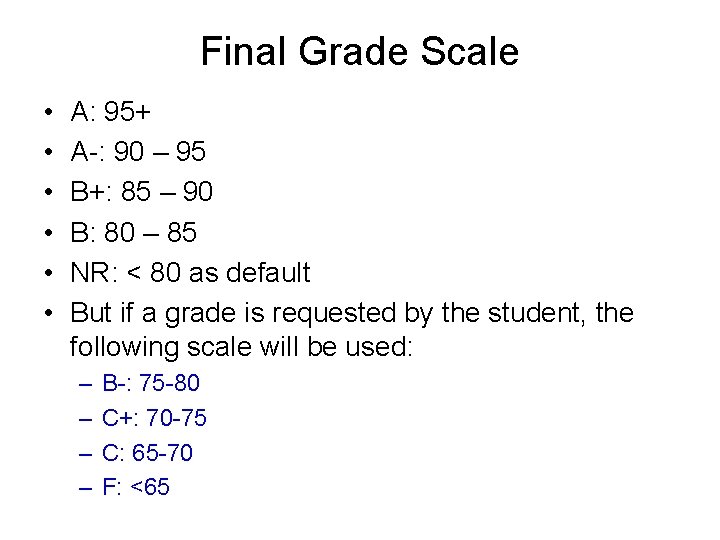

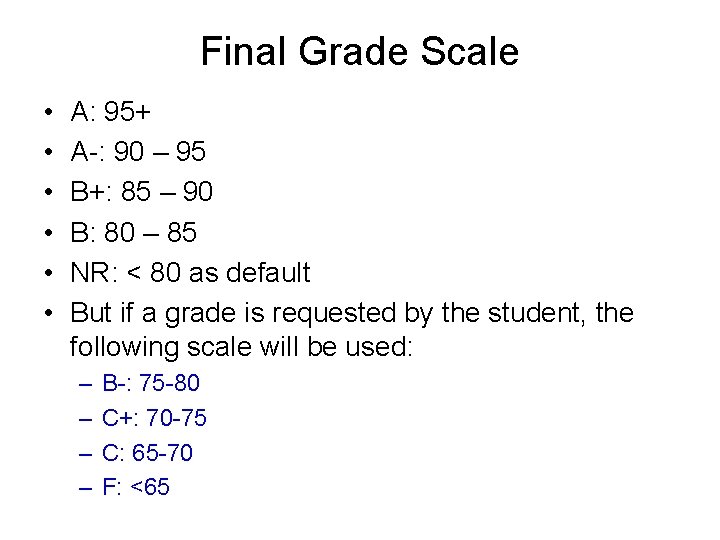

Final Grade Scale • • • A: 95+ A-: 90 – 95 B+: 85 – 90 B: 80 – 85 NR: < 80 as default But if a grade is requested by the student, the following scale will be used: – – B-: 75 -80 C+: 70 -75 C: 65 -70 F: <65

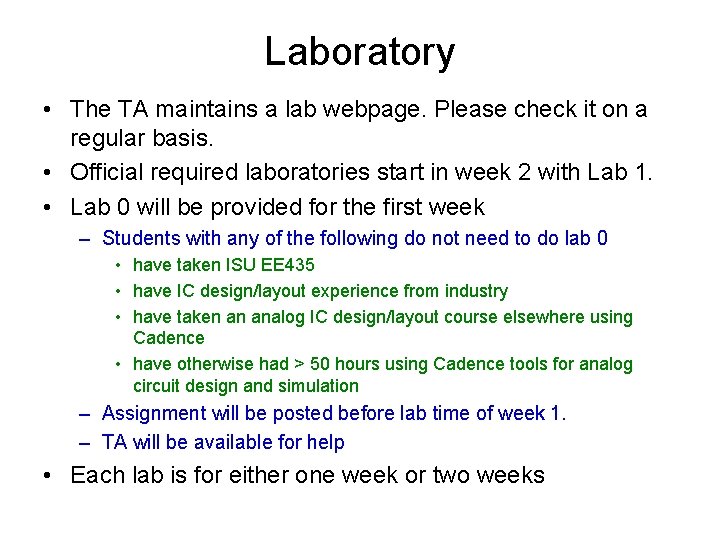

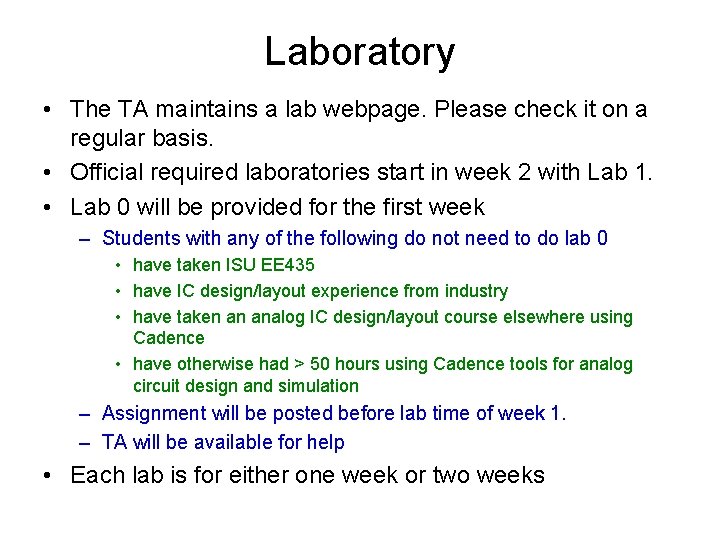

Laboratory • The TA maintains a lab webpage. Please check it on a regular basis. • Official required laboratories start in week 2 with Lab 1. • Lab 0 will be provided for the first week – Students with any of the following do not need to do lab 0 • have taken ISU EE 435 • have IC design/layout experience from industry • have taken an analog IC design/layout course elsewhere using Cadence • have otherwise had > 50 hours using Cadence tools for analog circuit design and simulation – Assignment will be posted before lab time of week 1. – TA will be available for help • Each lab is for either one week or two weeks

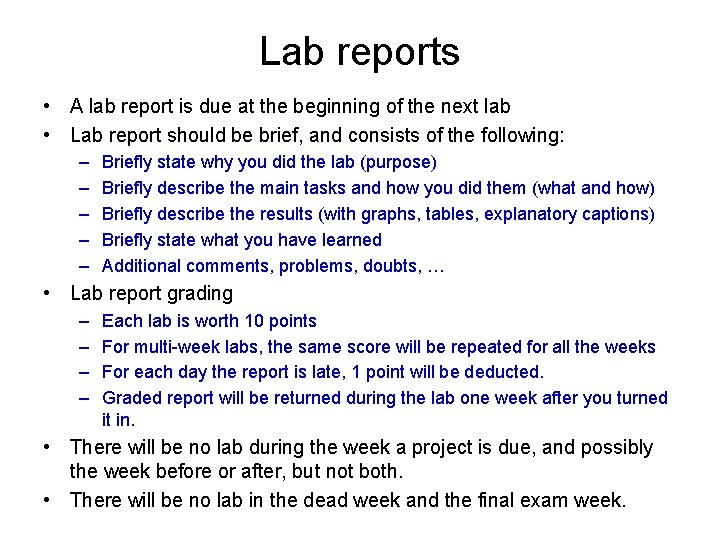

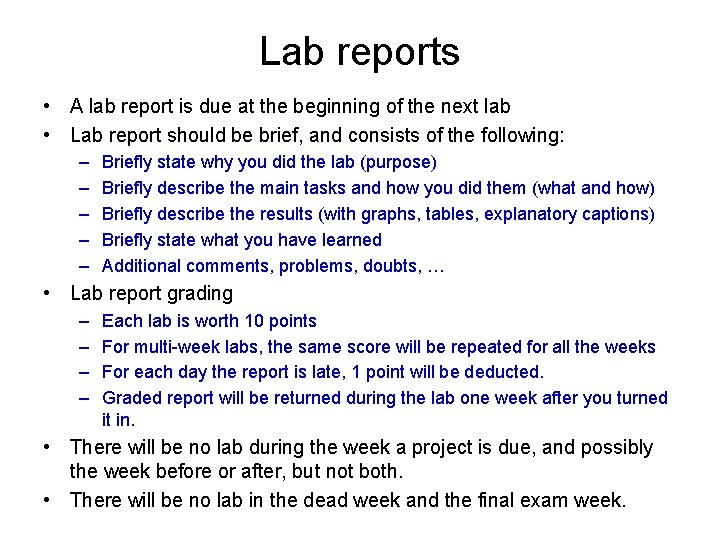

Lab reports • A lab report is due at the beginning of the next lab • Lab report should be brief, and consists of the following: – – – Briefly state why you did the lab (purpose) Briefly describe the main tasks and how you did them (what and how) Briefly describe the results (with graphs, tables, explanatory captions) Briefly state what you have learned Additional comments, problems, doubts, … • Lab report grading – – Each lab is worth 10 points For multi-week labs, the same score will be repeated for all the weeks For each day the report is late, 1 point will be deducted. Graded report will be returned during the lab one week after you turned it in. • There will be no lab during the week a project is due, and possibly the week before or after, but not both. • There will be no lab in the dead week and the final exam week.

Homework • Problems will be assigned during the lectures or by posting at the webpage • All problems are due on Wednesdays after the week they are assigned • For example, if a problem is given today which is Monday, it is due on next week’s Wednesday. • Similarly, if today is Wednesday and a problem is given in today’s lecture, it is also due on Wednesday of next week. • Late HW policy: accepted but with partial penalty.

Design Project • There will be two design projects. Details to be announced later. • Project 1: you should work in team of two. – You should form your own team, notify the TA and Instructor • Project 2: you should work in team of 3. – Your project 2 team should contain no project 1 team members.

Project report and presentation • • Preliminary report due date will be announce in class. Students will make presentations about their project. Submit your ppt files before any presentation starts. Presentation order will be randomly decided. Participate in all presentation, either as presenter or as reviewer. Reviewer are encouraged to ask questions to the presenters. After the presentation, you will be given time to make updates on your report and presentation. • The final due date for the presentation ppt and report pdf will be announced at the presentation time. • Penalty for late submission: 1 point per day for either the preliminary or final submission.

Exams • One midterm exam in week 7 or week 8 – Date to be determined by majority vote • Final exam time will be as specified by the university • Both exams will be closed-book, closednotes, for individual work, with one sheet (US letter size, both sides) of formulae allowed

Prerequisite by topics • Proficiency and fluency in using Cadence, Synopsis, and other IC design and simulation tools • Knowledge of how transistors work, including various operation regions. • Knowledge of basic building blocks such as common source, cascoding, source follower, current mirror, reference, etc. • Knowledge of basic amplifier structures, their large signal and small signal analysis, and computation of their gain, bandwidth, impedance and so on. • Knowledge of signals and systems, including poles, zeros, transfer functions, frequency response, transient response, stability, phase margins, and so on. • Knowledge of semiconductor fabrication and how transistors, resistors, capacitors, diodes, etc. are made. • Knowledge of probability, random variable, pdf’s, noise, signal to noise ratio, noise transfer, and so on.

Class Webpage • http: //class. ece. iastate. edu/djchen/ee 501/2015 • Please check the page for – Announcements – Class notes – HW assignments – Reference reading materials – Project requirements – Class policy and other info • http: //home. engineering. iastate. edu/~hme ng/EE 501 lab 2014

Accommodation/Assistance • Please let me know if you – – – Have any special needs Have disability in any form Have any medical/mental/emergency conditions Have field trips / interviews Have special requests Want me to adjust lecture contents/pace • Can also consult me if you – Would like to seek advice on any professional or personal issues – Would like to have certain confidential discussions

Text Book • Allen and Holberg, CMOS Analog Circuit Design, 3 rd Edition, Oxford, 2011 • Hastings, The Art of Analog Layout, Prentice Hall, 2 nd ed • Available at Amazon – Significant discounts vs bookstore • International editions from Taiwan or Singapore

References • • • Gray, et al, Analysis and Design of Analog Integrated Circuits, 5 th Ed. , Wiley, 2009 William Liu, Mosfet Models for Spice Simulation, Including BSIM 3 v 3 and BSIM 4, Wiley-IEEE, 2001 Daniel P. Foty, MOSFET Modeling With SPICE: Principles and Practice, Prentice Hall, 1996 Yannis Tsividis, Operation and Modeling of the MOS Transistor, Oxford University Press; 2 nd edition (May 1, 2003) Laker and Sansen, Design of Analog Integrated Circuits, Mc. Graw Hill, 1994 David Johns & Ken Martin , Analog Integrated Circuit Design, John Wiley & Sons, Inc. 1997 Behzad Razavi, Design of Analog CMOS Integrated, Circuits. Mc. Graw-Hill, 1999 Geiger, et al, VLSI Design Techniques for Analog and Digital Circuit, Mc. Graw Hill, 1990 Baker, CMOS Circuit Design, Layout and Simulation, IEEE Press, 1997 Alan B. Grebene, Bipolar and MOS Analog Integrated Circuit Design (Wiley Classics Library), 2001

Student behavior expectations • Full attendance, except with prior-notified excuses • On-time arrival • Active participation – Ask questions – Answer questions from instructor or students • Help each other • Promptly report/share problems/issues, errors/typos in slides, misspoken words by instructor, … • Email csg@iastate. edu, cc TA and me, stating you are working on a lab, and describing the issue

Prohibited behaviors • Any foul language or gestures • Comments to other students that are discriminatory in any form • Any harassments as defined by the university • Academic dishonesty • No alcohol, drugs, or any other illegal / improper substances – Snacks/drinks OK as long as you don’t spill and clean up

Lab Safety • Taken from: http: //www. ece. iastate. edu/the-department/safety/ • All personnel (faculty, staff, students, and visitors) who use laboratory facilities at Iowa State University shall follow the procedures detailed in the ISU Laboratory Safety Manual. Successful completion of appropriate safety training as specified in Safety Training Curriculum for Laboratory Personnel is required prior to beginning work in a laboratory. • At Iowa State University, laboratories are defined as, but not limited to, any location where research or teaching is conducted using hazardous chemicals, biohazardous or biological materials, radioactive materials, radiation producing devices, and/or physical hazards.

Accommodation/Assistance • Please let me know if you – – – Have any special needs Have disability in any form Have any medical/mental/emergency conditions Have field trip / interview Have special requests Want me to adjust lecture contents/pace • Can also consult me if you – Would like to seek advice on any professional or personal issues – Would like to have certain confidential discussions

Collaboration And Helping Each Other • For tasks intended for group work, you are expected to find a partner and share the tasks among the group members. In a group project, effective teamwork is critical to maximize the productivity of the whole group. In the submitted work, identify components and indicate percentage contribution by each member to each component. • For tasks not intended for group work, individual submission is required. In this case, you are encouraged to discuss among your friends on how to attack problems. However, you should write your own solution. Copying other people’s work is strictly prohibited.

Academic dishonesty • Cheating is a very serious offense. It will be dealt with in the most severe manner allowable under University regulations. If caught cheating, you can expect a failing grade and initiation of a cheating case in the University system. • Basically, it’s an insult to the instructor, the department and major program, and most importantly, to the person doing the cheating. Just don't. • If in doubt about what might constitute cheating, send email to your instructor describing the situation. If you notice anyone cheating, please report it to the instructor or the TA. Do not deal with it yourself.

Discrimination • State and Federal laws as well as Iowa State University policies prohibit any form of discrimination on the basis of race, color, age, religion, national origin, sexual orientation, gender identity, sex, marital status, disability, or status as a U. S. veteran. Language or gestures of discriminatory nature will not be tolerated. Severe cases will be reported to appropriate offices. See ISU policies at http: //www. hrs. iastate. edu/hrs/files/reaffirmation. pdf • Let us make every effort to work together and create a positive, collegial, caring, and all-supportive learning environment in our classroom, laboratory, TA office, and instructor office.

Disability accommodation • Iowa State University is committed to assuring that all educational activities are free from discrimination and harassment based on disability status. All students requesting accommodations are required to meet with staff in Student Disability Resources (SDR) to establish eligibility. A Student Academic Accommodation Request (SAAR) form will be provided to eligible students. The provision of reasonable accommodations in this course will be arranged after timely delivery of the SAAR form to the instructor. Students are encouraged to deliver completed SAAR forms as early in the semester as possible. SDR, a unit in the Dean of Students Office, is located in room 1076, Student Services Building or online at www. dso. iastate. edu/dr/. Contact SDR by e-mail at disabilityresources@iastate. edu or by phone at 515 -294 -7220 for additional information.

Accommodation for religion based conflicts • Iowa State University welcomes diversity of religious beliefs and practices, recognizing the contributions differing experiences and viewpoints can bring to the community. Students with religion based conflict should talk to the instructor and appropriate university offices to request accommodations at the earliest possible time.