EE 466 VLSI Design Instructor Amlan Ganguly TA

- Slides: 13

EE 466: VLSI Design Instructor: Amlan Ganguly TA: Souradip Sarkar Meeting: MWF, 12. 10 pm, Sloan-38

Where to find us? • • Instructor’s office: Sloan 338 Email: ganguly@eecs. wsu. edu Office hours: MF, 2: 00 – 3: 00 pm By appointment • • TA’s office: Sloan 354 Email: ssarkar@eecs. wsu. edu Phone: 509 -335 -6249 Office hours: Tu, Thus, 3: 00 -4: 00 pm

Course outline • Introduction to CMOS circuits • MOS transistor theory • Circuit Characterization – Performance evaluation & optimization • CMOS circuit logic and design • Subsystem design • Datapath design and analysis

Grading structure • • • Homework: 10% Midterm: 25% Lab Assignments: 20% Term project: 20% Final: 25%

Solid State Devices • Silicon – Doping • n-type, p-type silicon – Carriers • electrons and holes • P-N junctions – 2 terminal devices • Transistors – Bipolar Junction Transistors (BJT) – Metal Oxide Semiconductor (MOS) • 4 terminal devices • Main emphasis of this class

Integrated circuits • n. MOS and p. MOS devices • Modeled as on-off switches – But a lot goes on inside! • Complementary MOS (CMOS) circuit design methodology – Most common and widely used technique – But several other interesting techniques exist

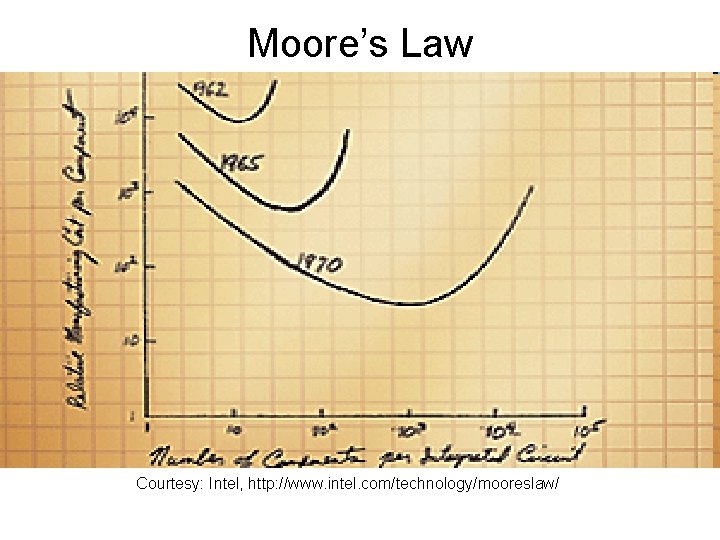

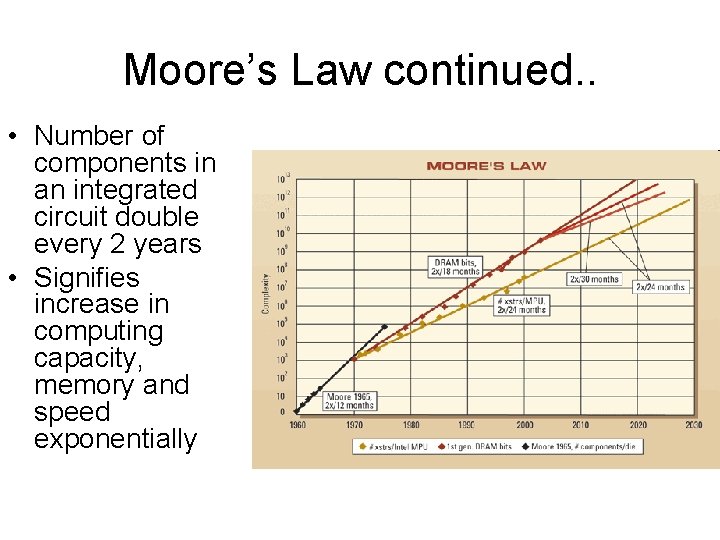

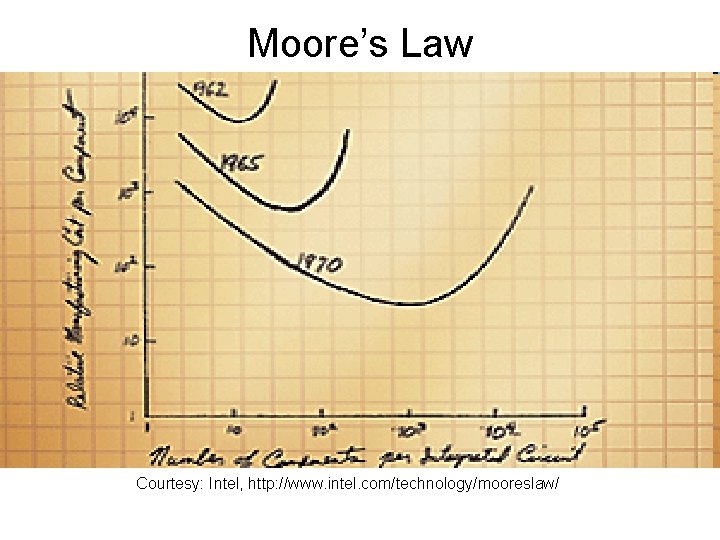

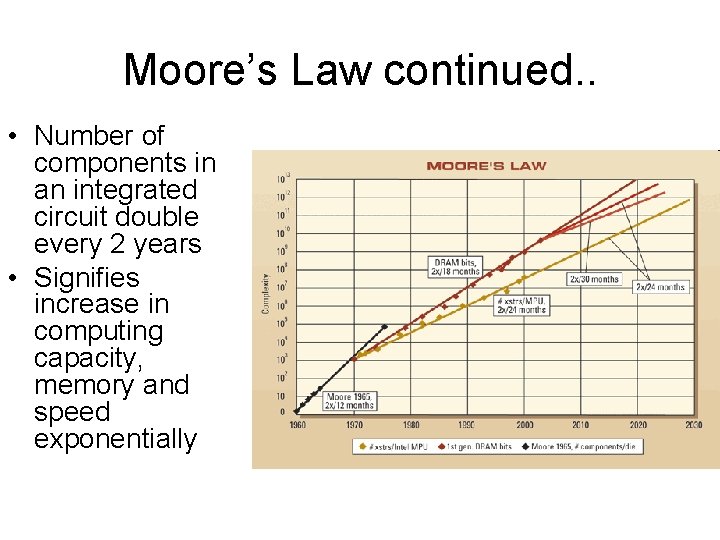

Moore’s Law Courtesy: Intel, http: //www. intel. com/technology/mooreslaw/

Moore’s Law continued. . • Number of components in an integrated circuit double every 2 years • Signifies increase in computing capacity, memory and speed exponentially

MOS structure • n-channel • p-channel

Technology nodes • Scaling – 0. 25 um, 0. 18 um, 90 nm, 65 nm, 45 nm, 32 nm… • Pitch – Gate length – Device sizes – Frequencies

Current Computing Capabilities • Intel’s 80 -core processor: ~Terra flops • Over a billion transistors per chip • 4 -5 GHz chip clock

Issues and challenges of VLSI today • High Power dissipation • Faster operation • Methodologies to address these issues

Looking ahead • CMOS technology – Stable and well understood process • Future technologies – Nanodevices – Molecular devices – Single electron devices – Quantum dots – Many more… • The future is basically yours to invent!