EE 365 Sequential PLD timing Registers Counters Shift

- Slides: 31

EE 365 Sequential PLD timing Registers Counters Shift registers 1

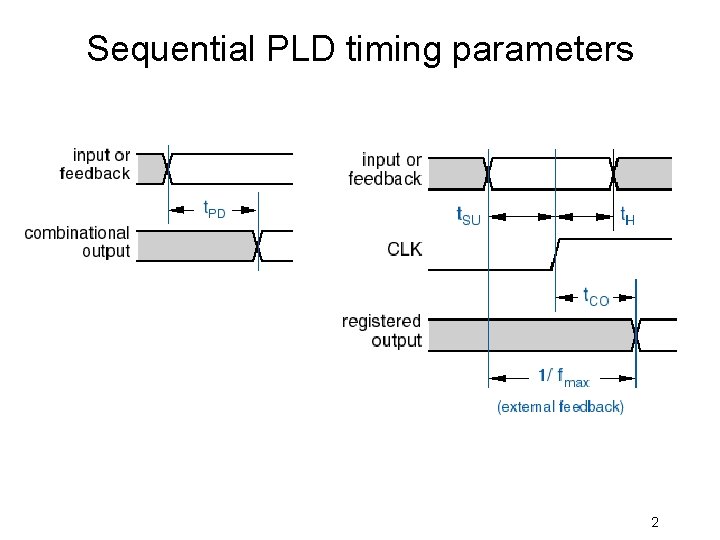

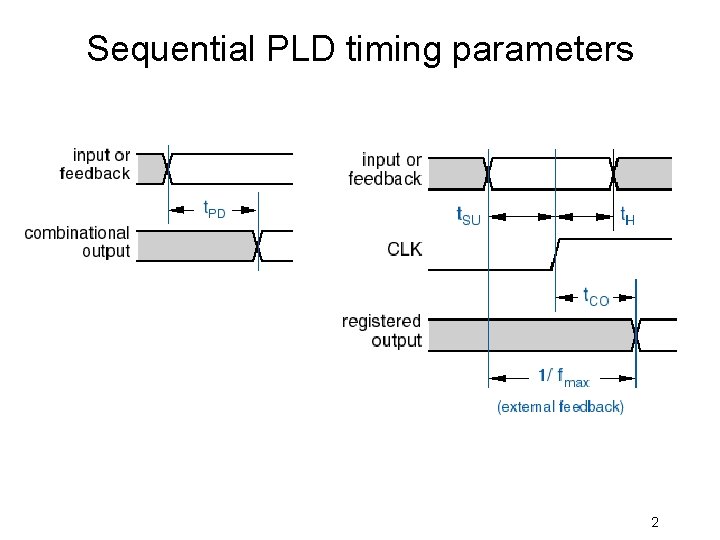

Sequential PLD timing parameters 2

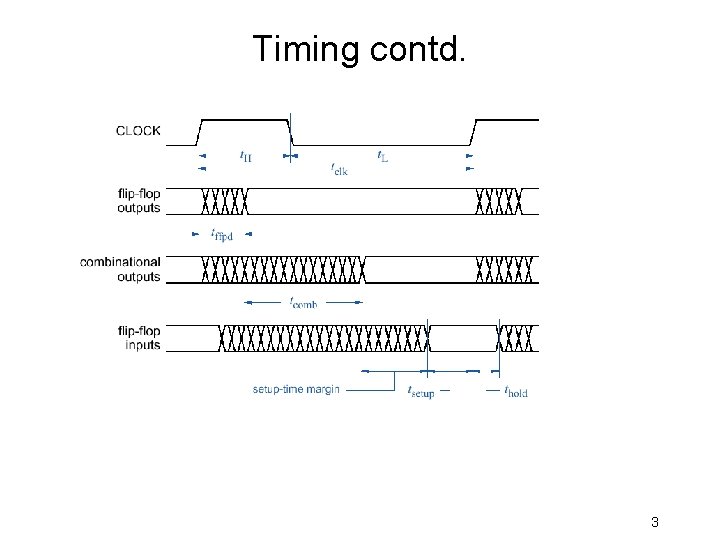

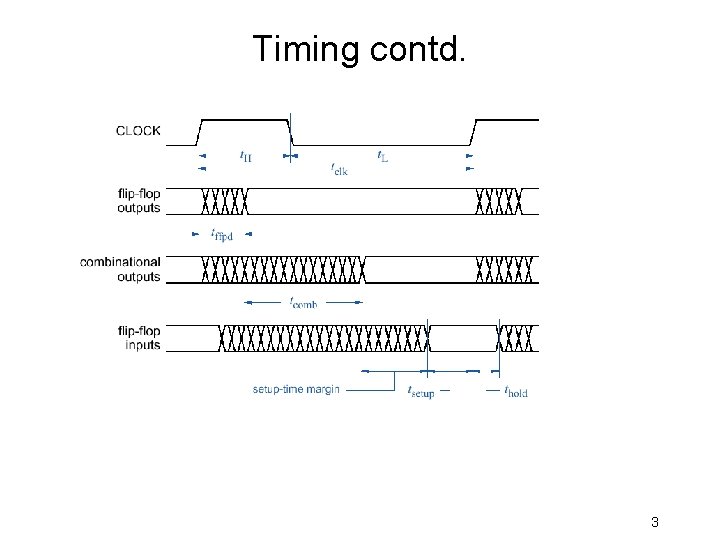

Timing contd. 3

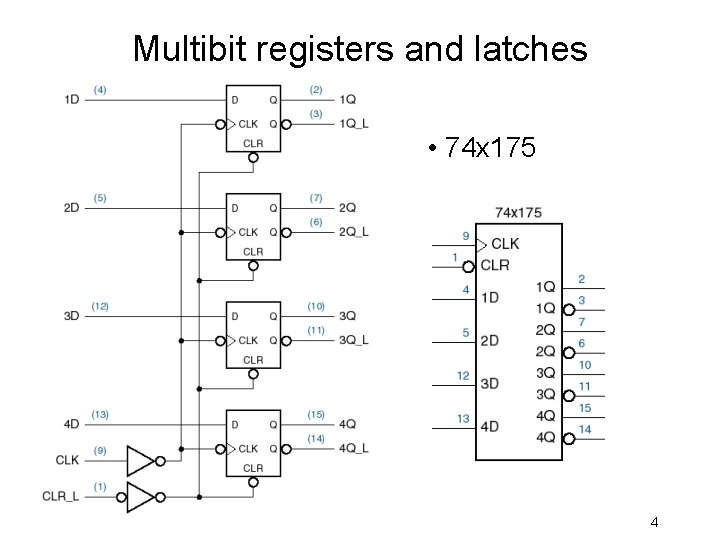

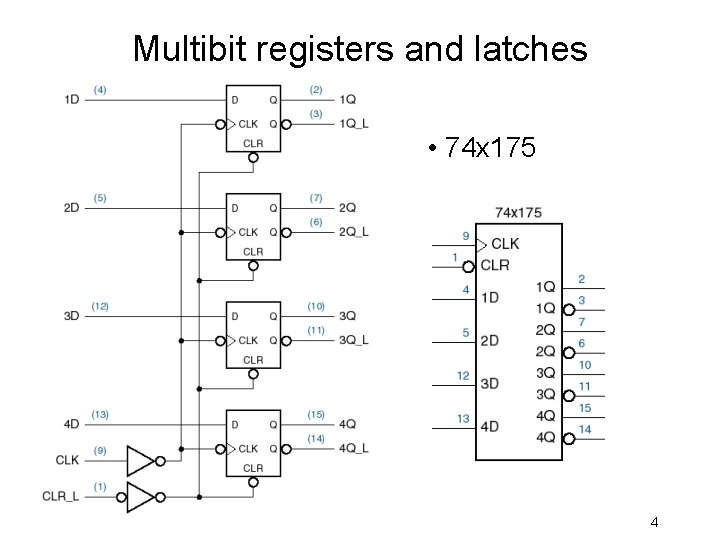

Multibit registers and latches • 74 x 175 4

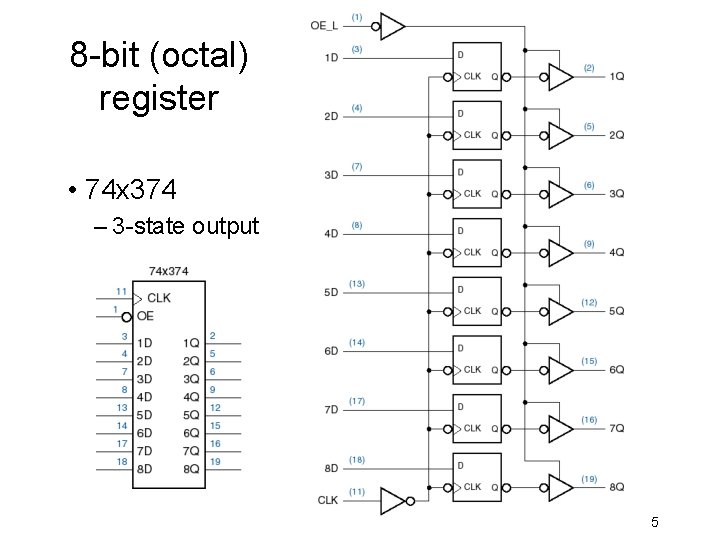

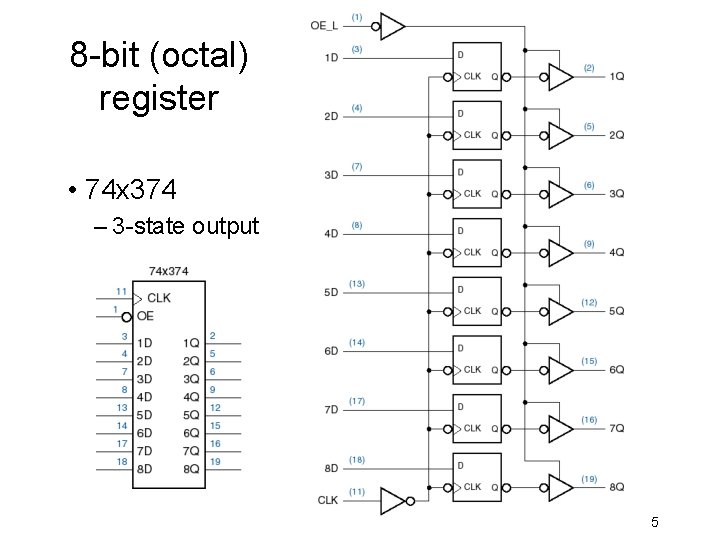

8 -bit (octal) register • 74 x 374 – 3 -state output 5

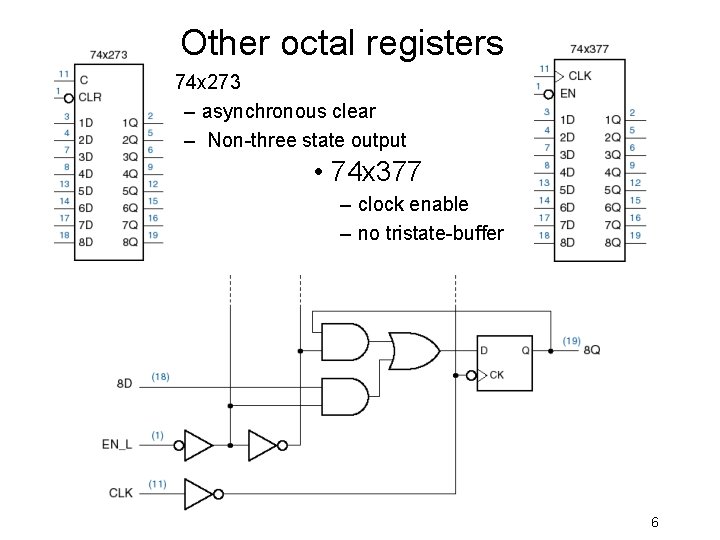

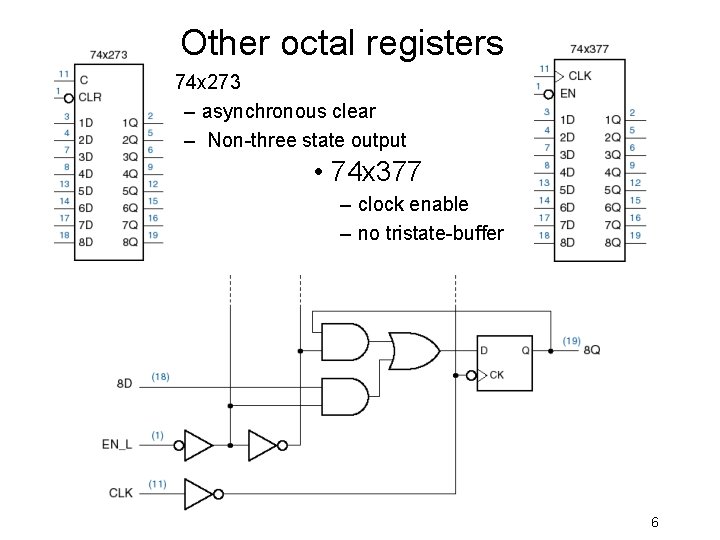

Other octal registers • 74 x 273 – asynchronous clear – Non-three state output • 74 x 377 – clock enable – no tristate-buffer 6

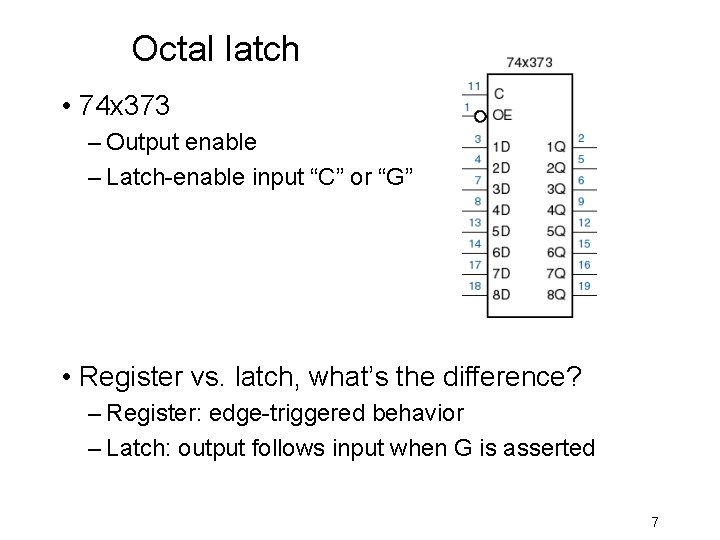

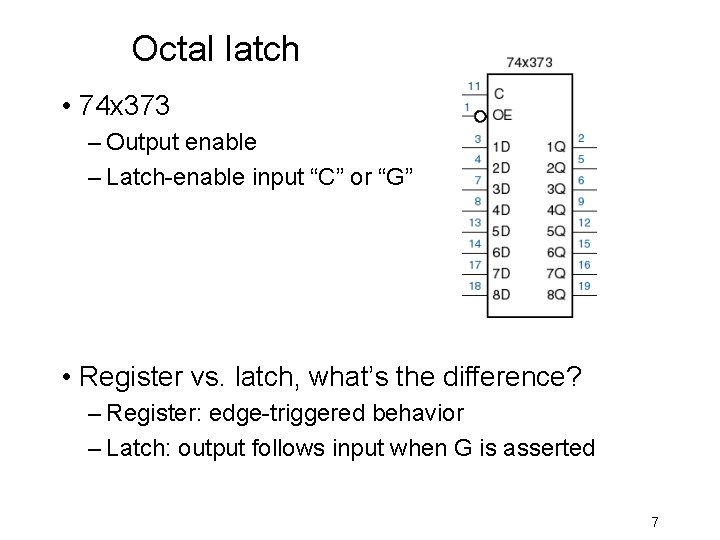

Octal latch • 74 x 373 – Output enable – Latch-enable input “C” or “G” • Register vs. latch, what’s the difference? – Register: edge-triggered behavior – Latch: output follows input when G is asserted 7

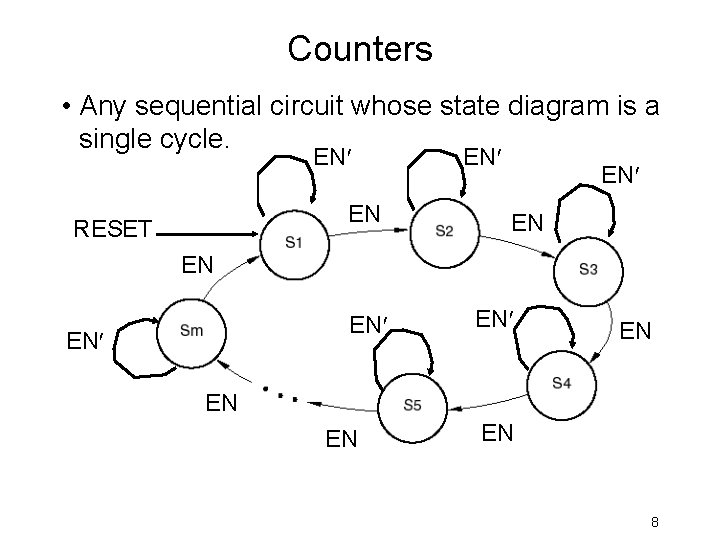

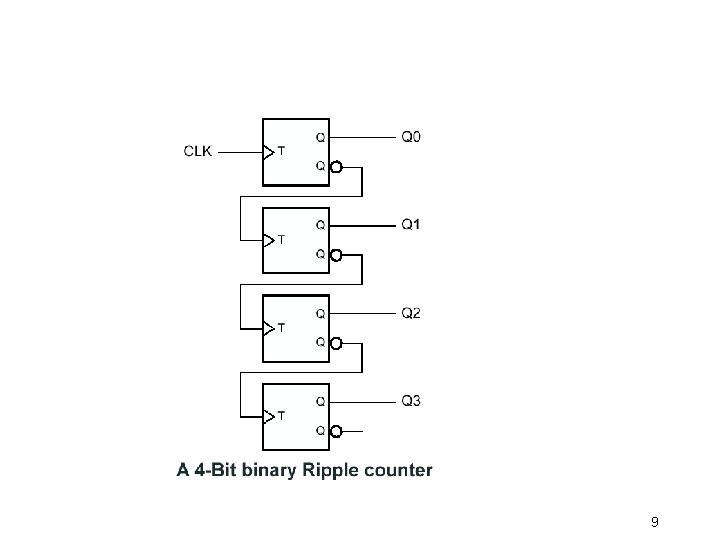

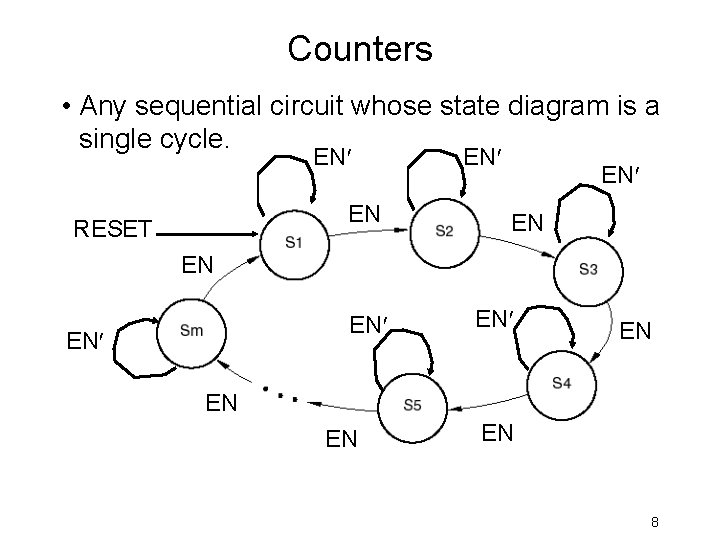

Counters • Any sequential circuit whose state diagram is a single cycle. EN RESET EN EN EN EN 8

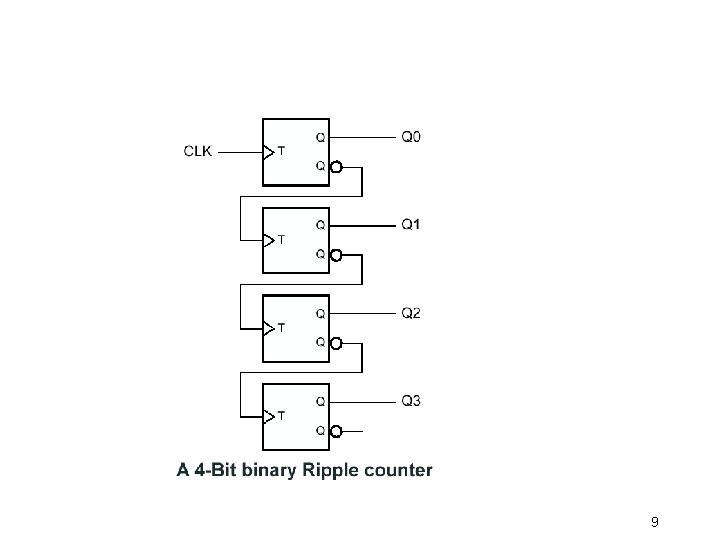

9

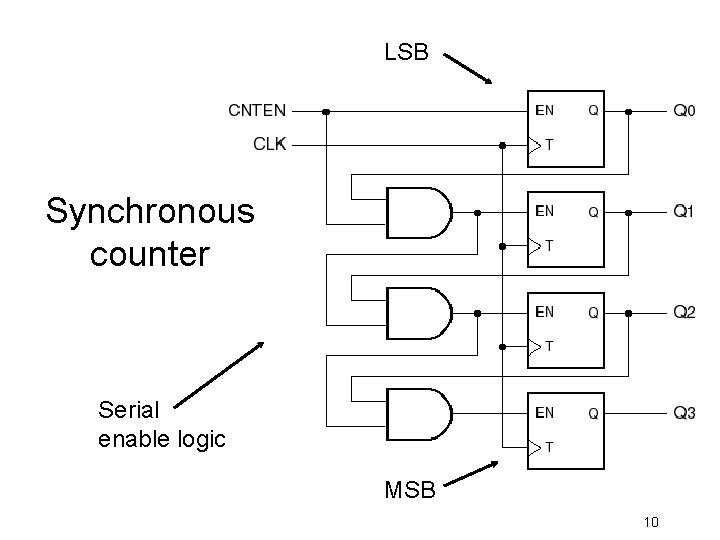

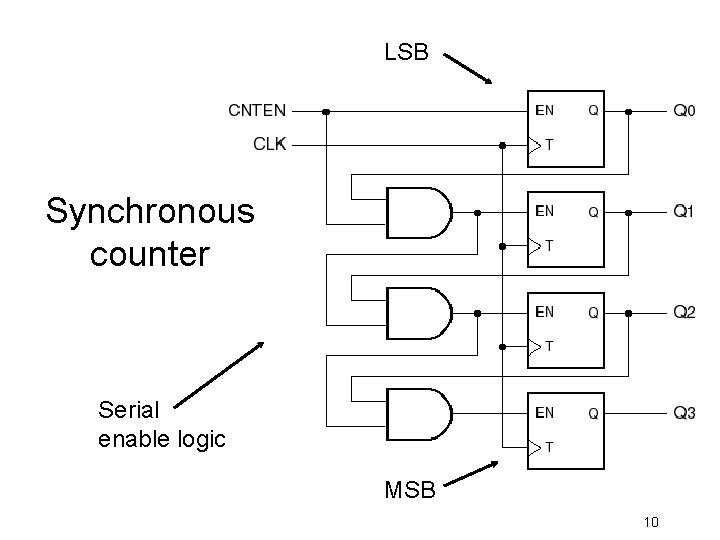

LSB Synchronous counter Serial enable logic MSB 10

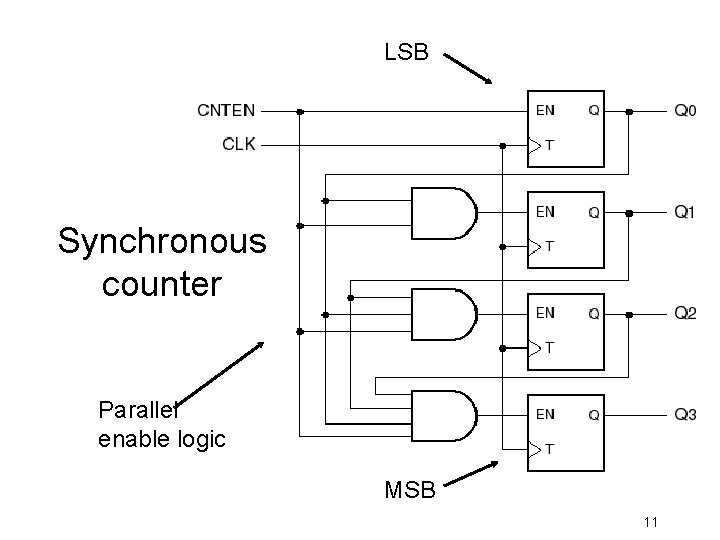

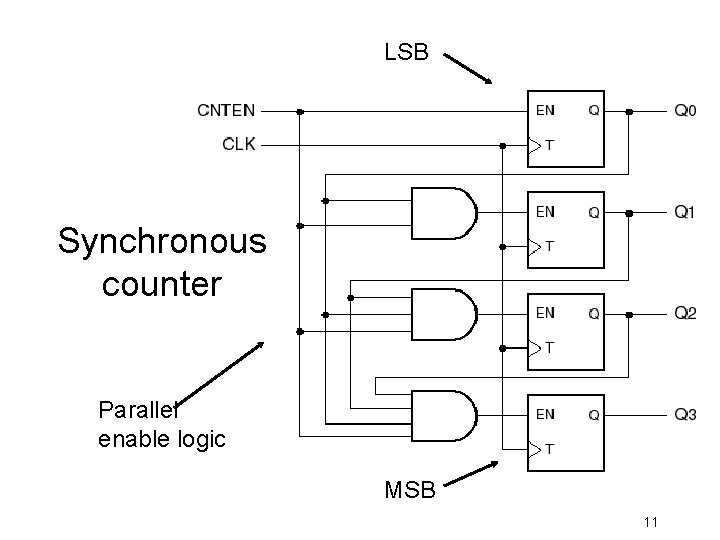

LSB Synchronous counter Parallel enable logic MSB 11

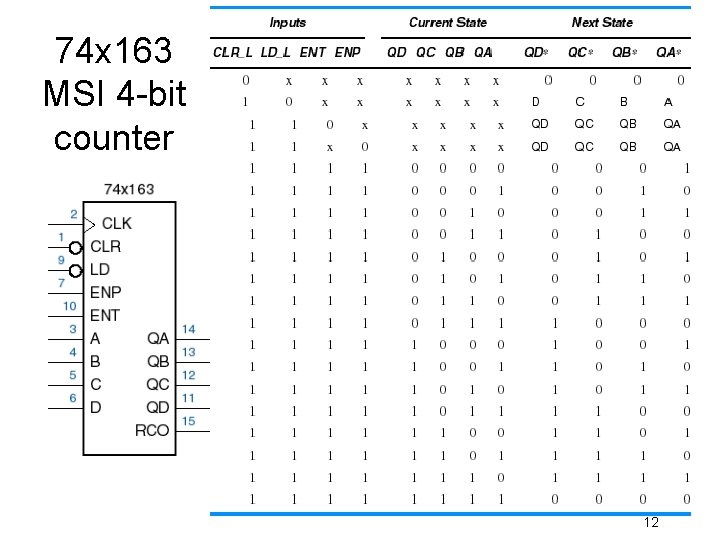

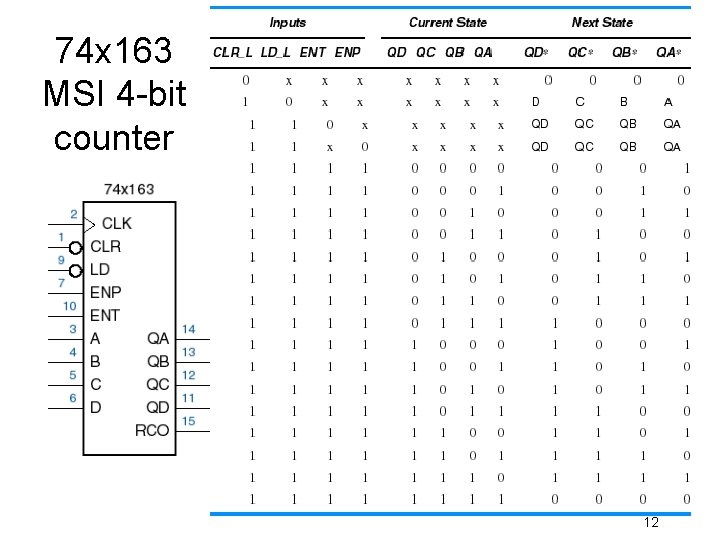

74 x 163 MSI 4 -bit counter 12

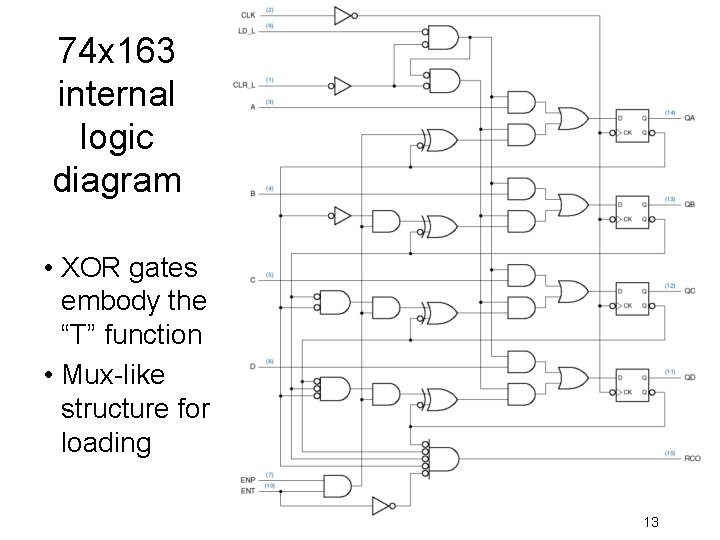

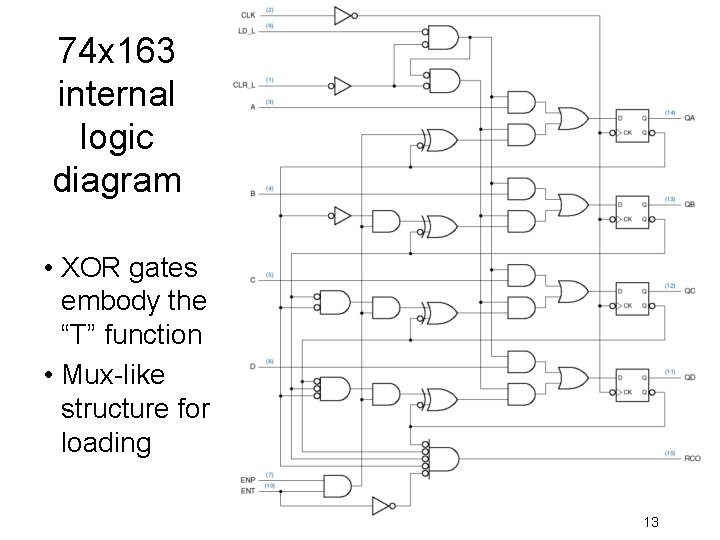

74 x 163 internal logic diagram • XOR gates embody the “T” function • Mux-like structure for loading 13

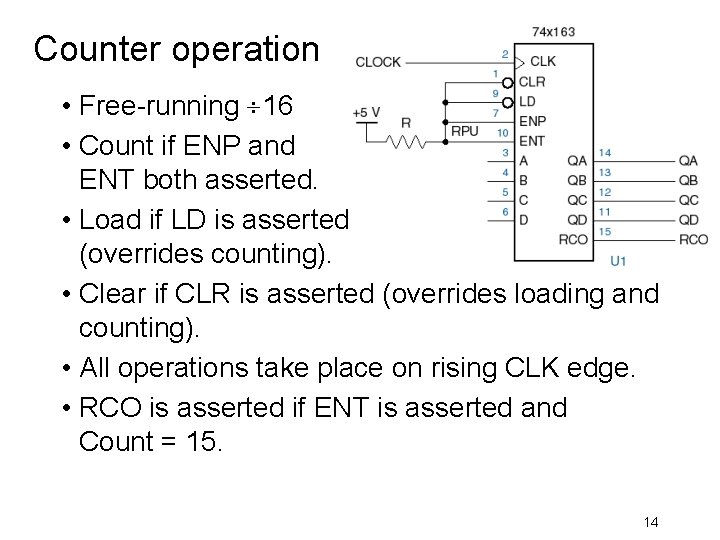

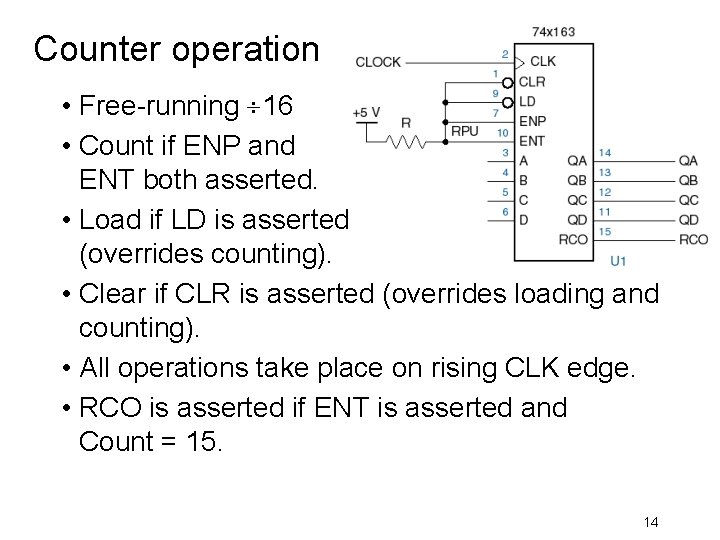

Counter operation • Free-running 16 • Count if ENP and ENT both asserted. • Load if LD is asserted (overrides counting). • Clear if CLR is asserted (overrides loading and counting). • All operations take place on rising CLK edge. • RCO is asserted if ENT is asserted and Count = 15. 14

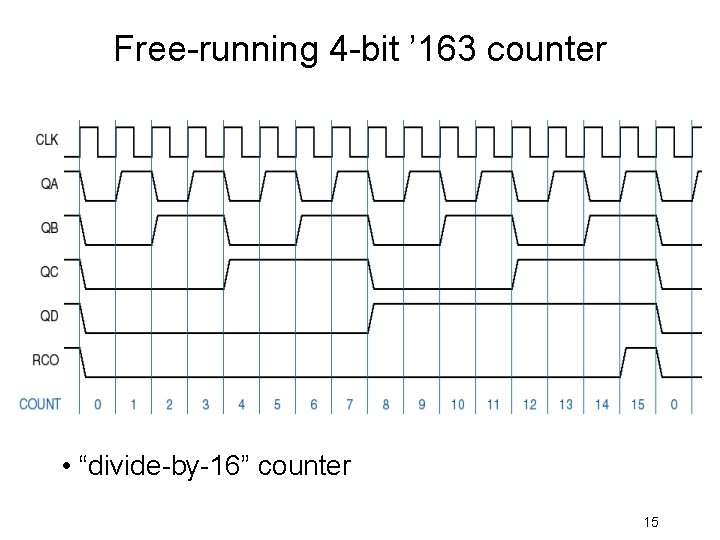

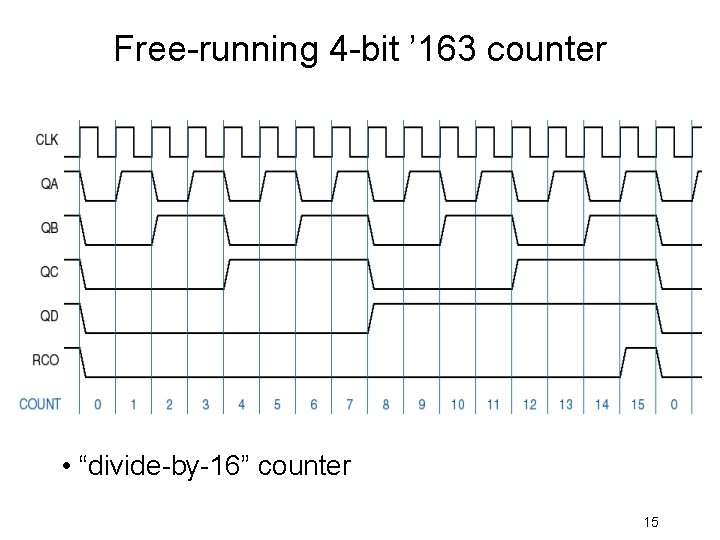

Free-running 4 -bit ’ 163 counter • “divide-by-16” counter 15

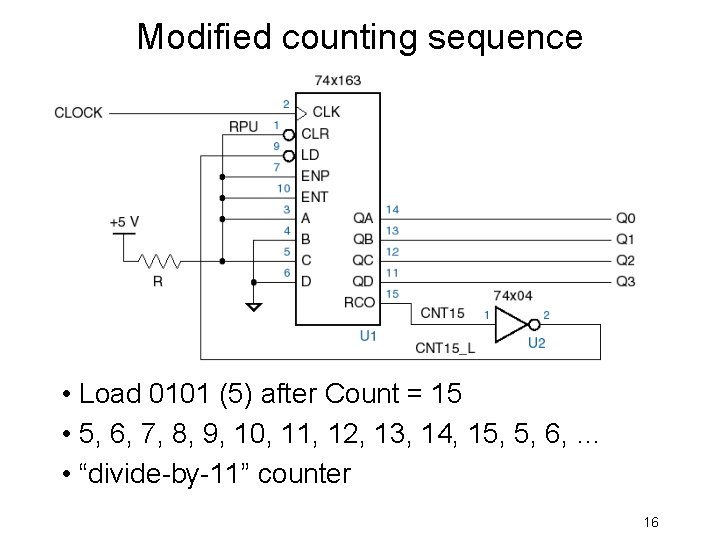

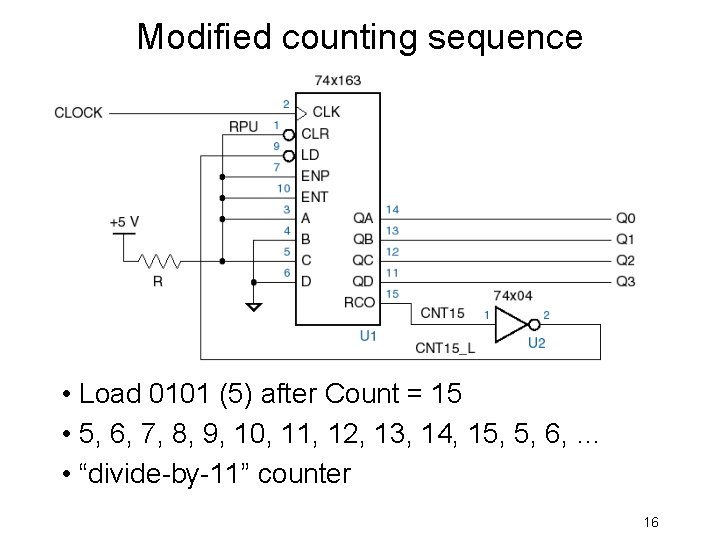

Modified counting sequence • Load 0101 (5) after Count = 15 • 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 5, 6, … • “divide-by-11” counter 16

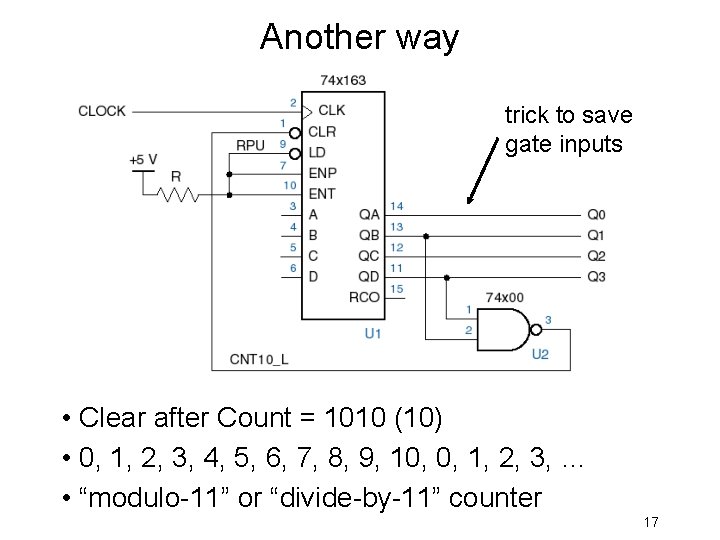

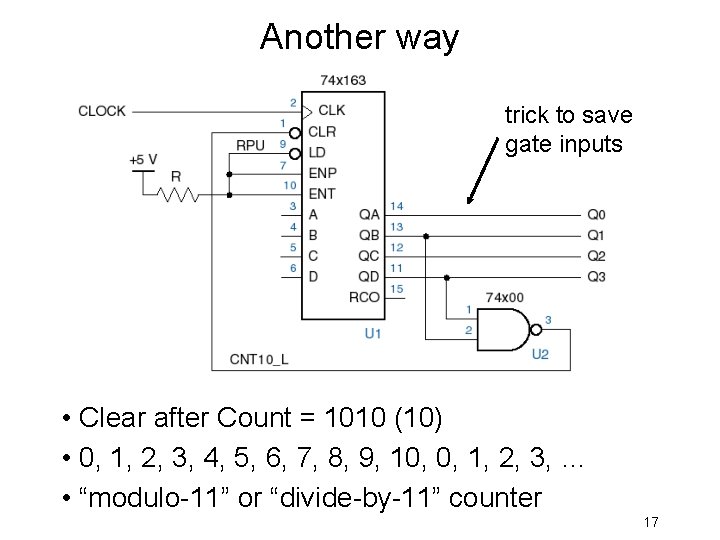

Another way trick to save gate inputs • Clear after Count = 1010 (10) • 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 0, 1, 2, 3, … • “modulo-11” or “divide-by-11” counter 17

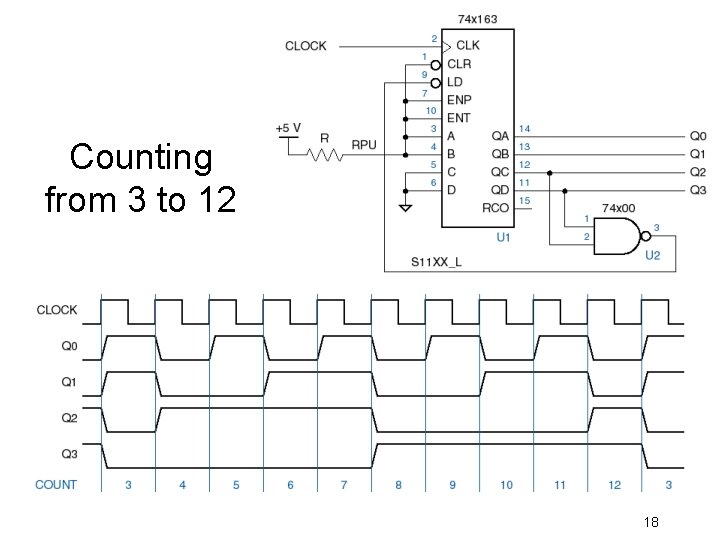

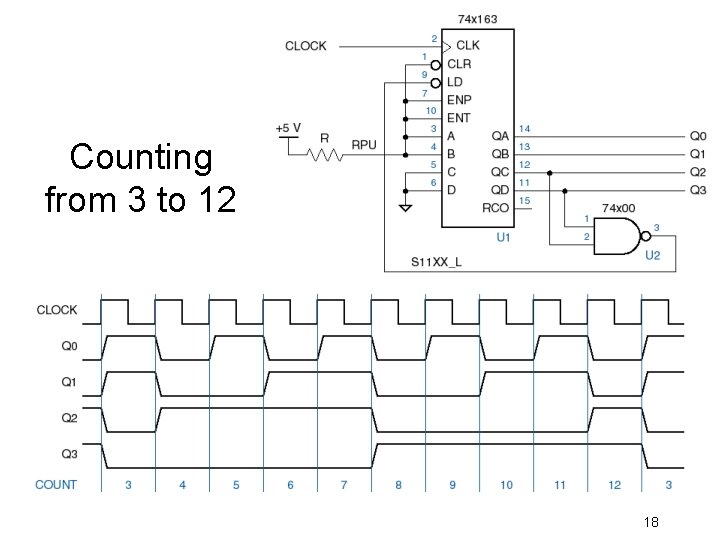

Counting from 3 to 12 18

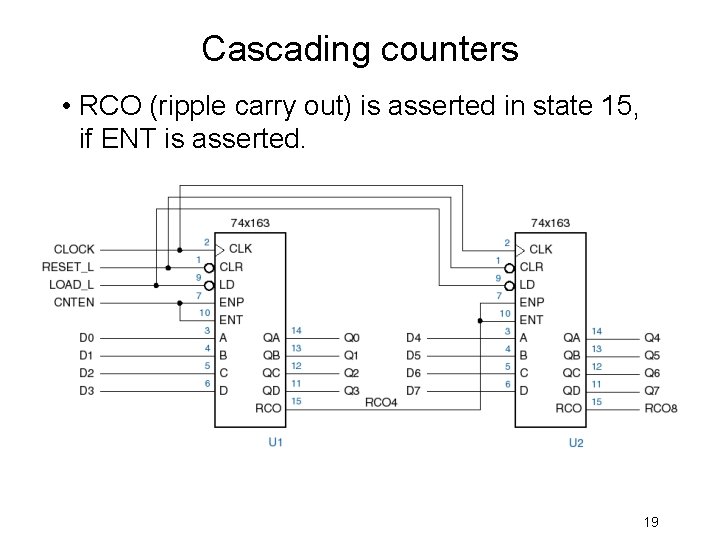

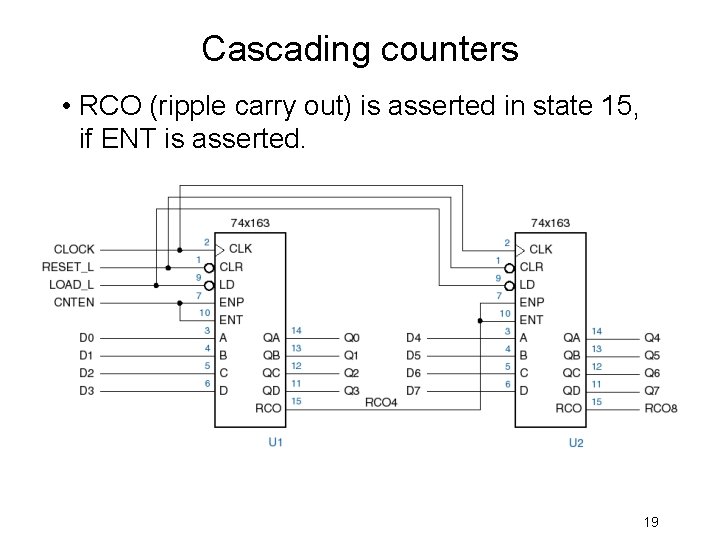

Cascading counters • RCO (ripple carry out) is asserted in state 15, if ENT is asserted. 19

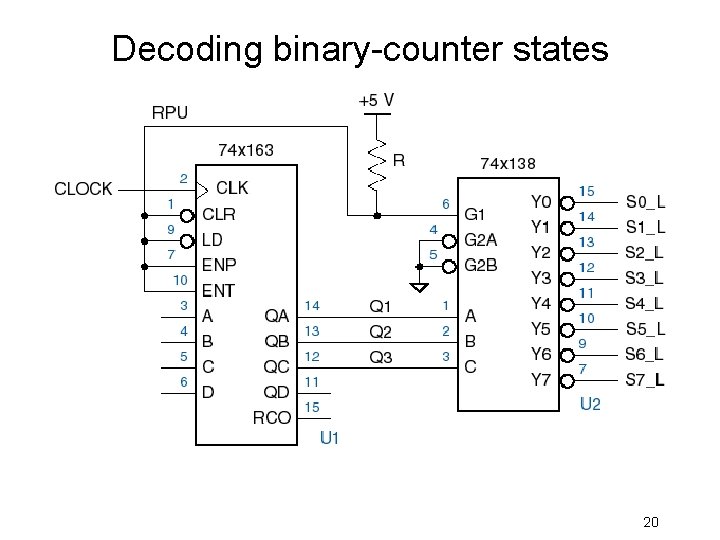

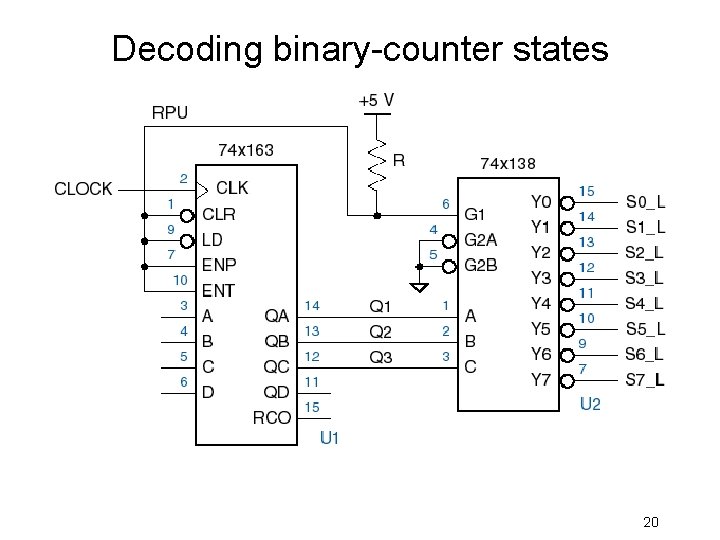

Decoding binary-counter states 20

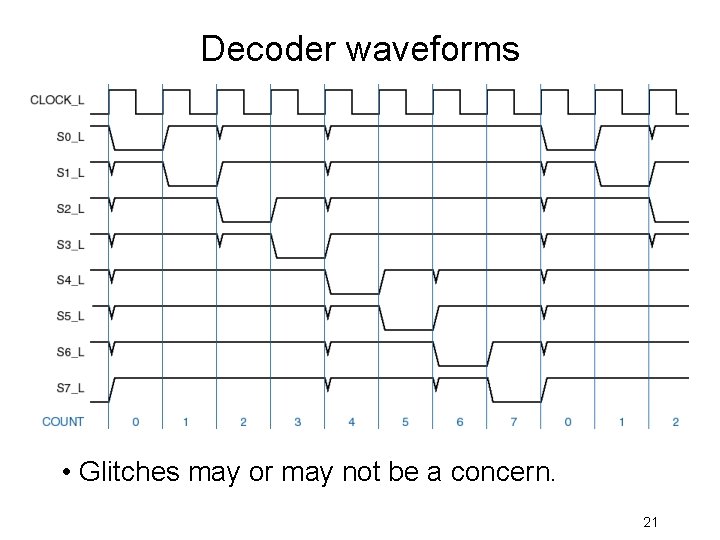

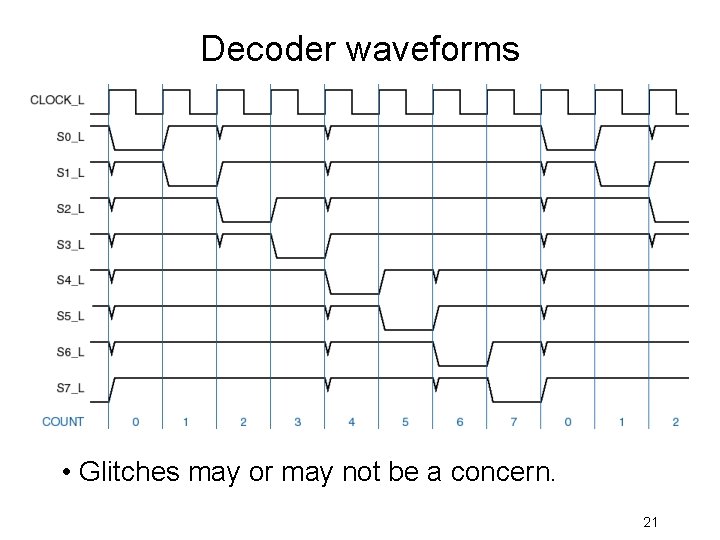

Decoder waveforms • Glitches may or may not be a concern. 21

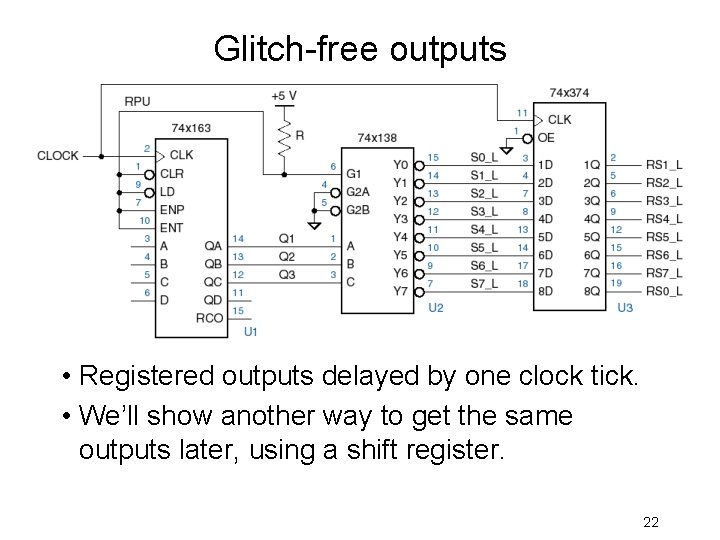

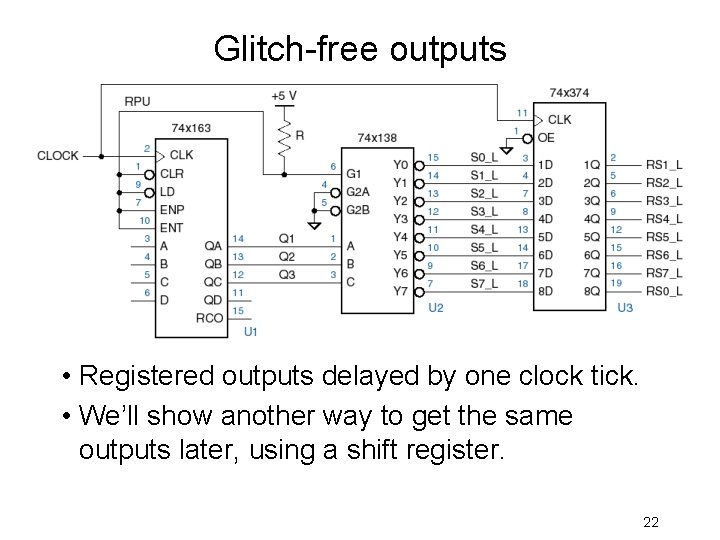

Glitch-free outputs • Registered outputs delayed by one clock tick. • We’ll show another way to get the same outputs later, using a shift register. 22

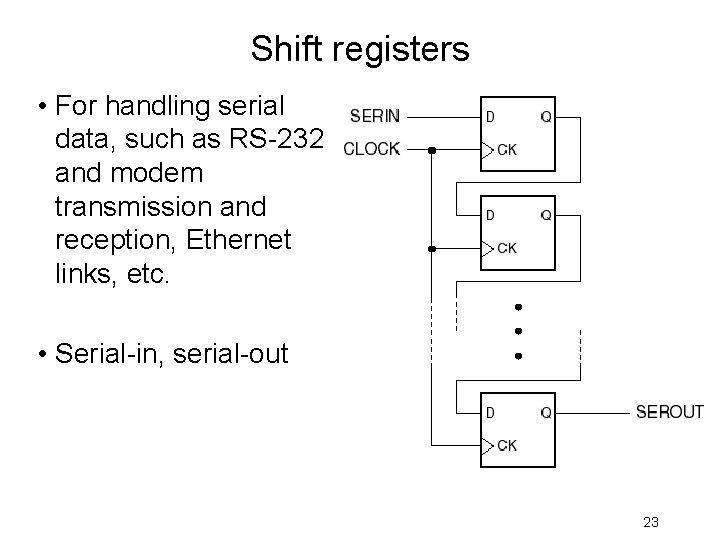

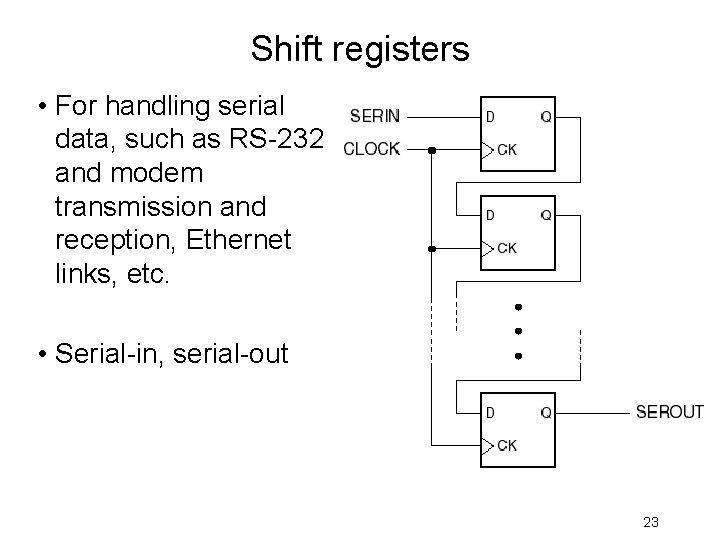

Shift registers • For handling serial data, such as RS-232 and modem transmission and reception, Ethernet links, etc. • Serial-in, serial-out 23

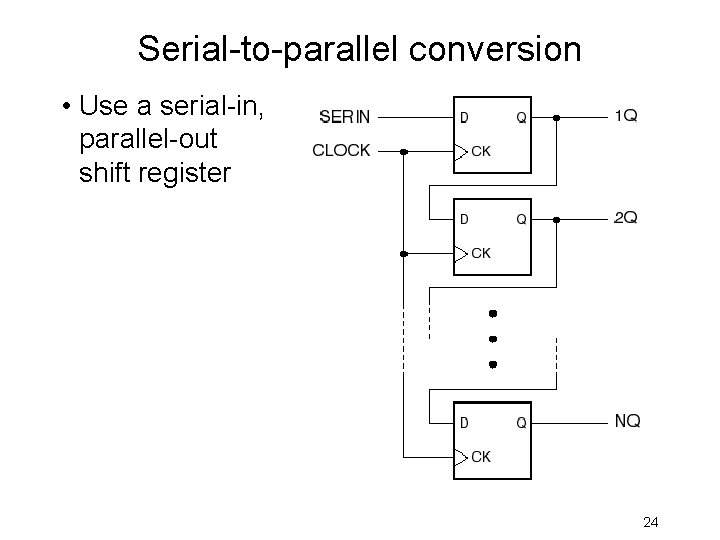

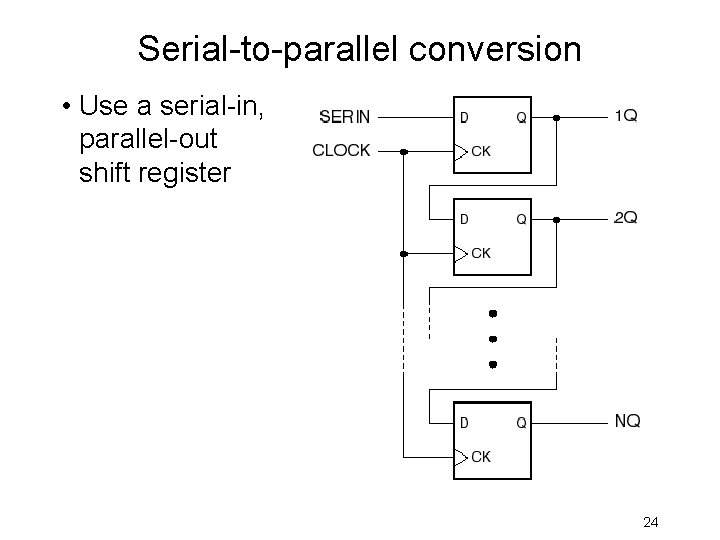

Serial-to-parallel conversion • Use a serial-in, parallel-out shift register 24

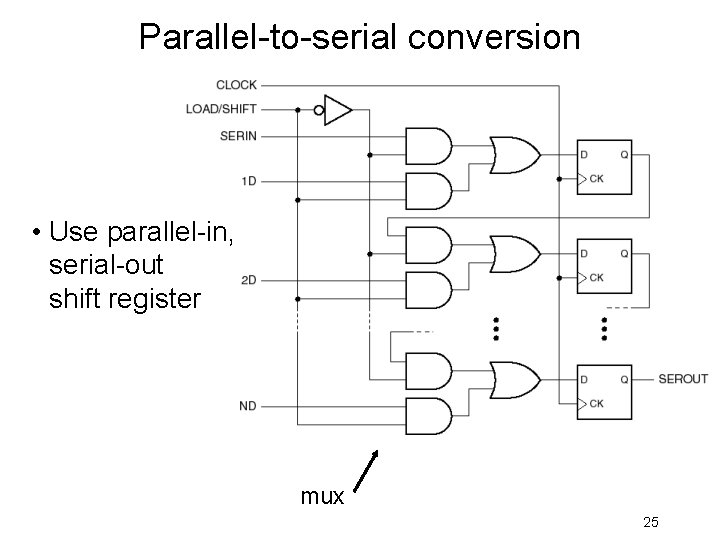

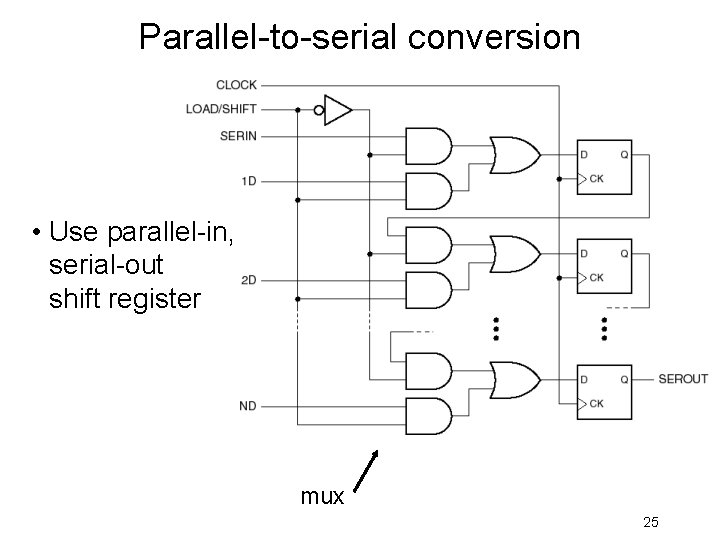

Parallel-to-serial conversion • Use parallel-in, serial-out shift register mux 25

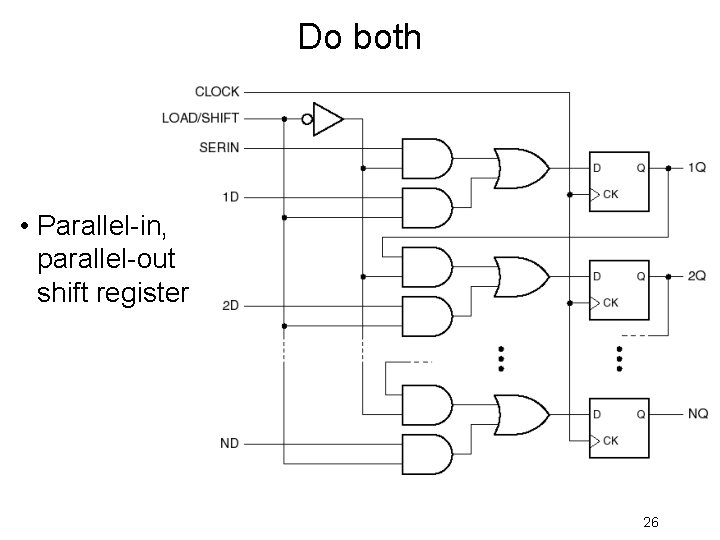

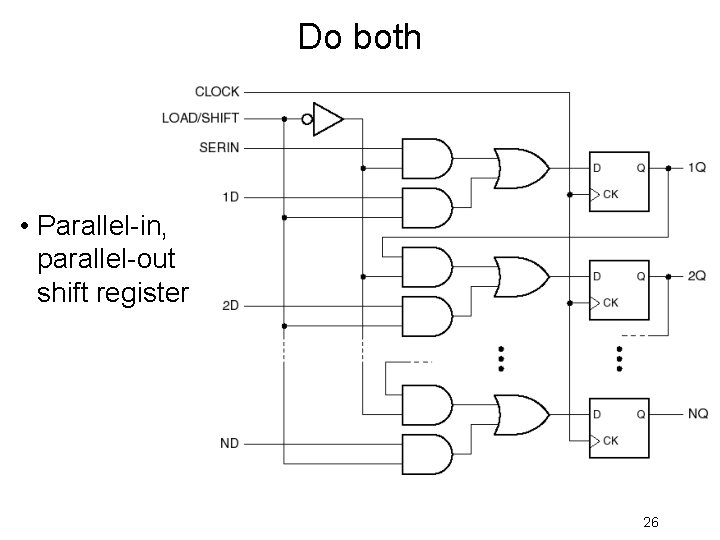

Do both • Parallel-in, parallel-out shift register 26

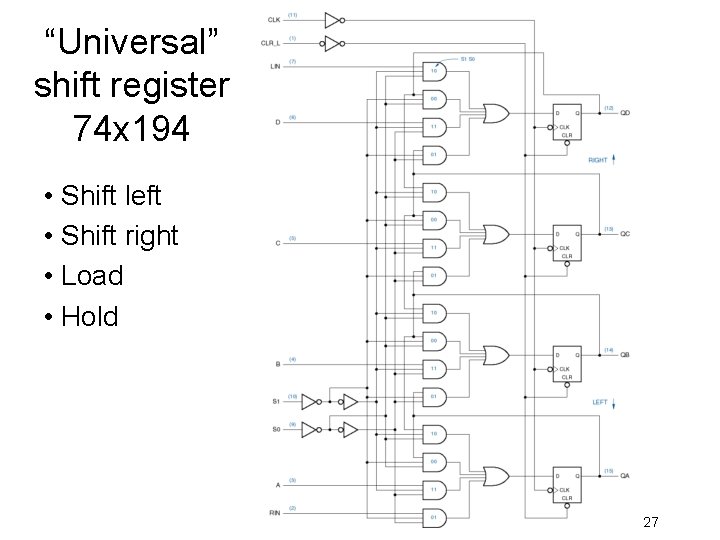

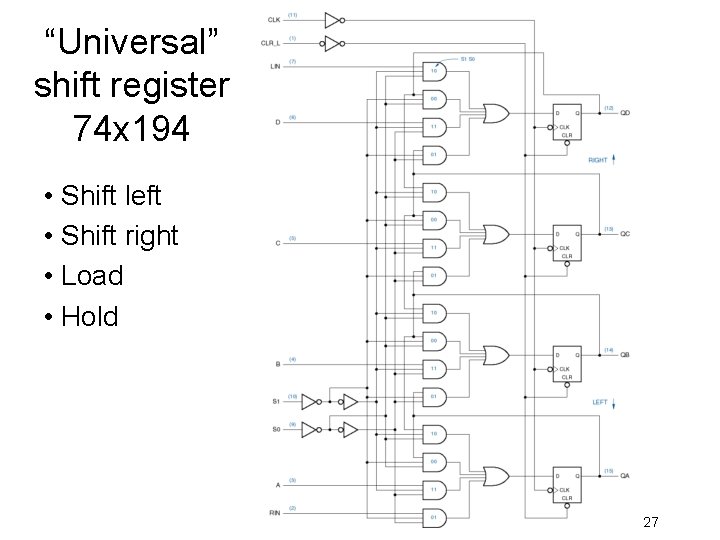

“Universal” shift register 74 x 194 • Shift left • Shift right • Load • Hold 27

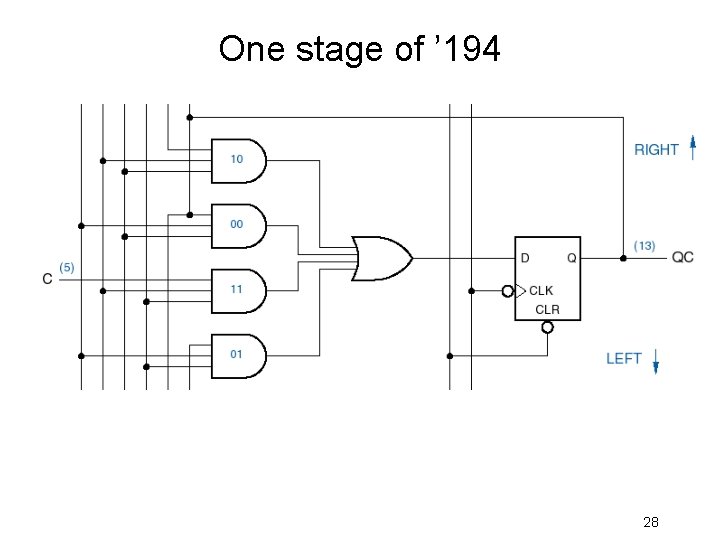

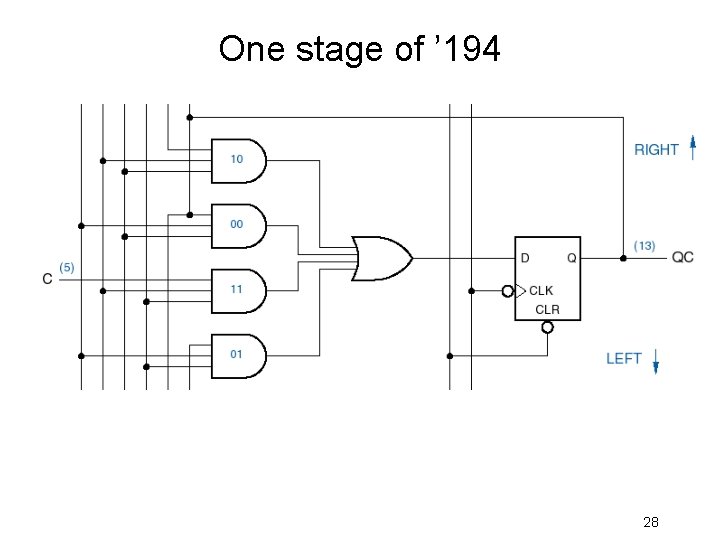

One stage of ’ 194 28

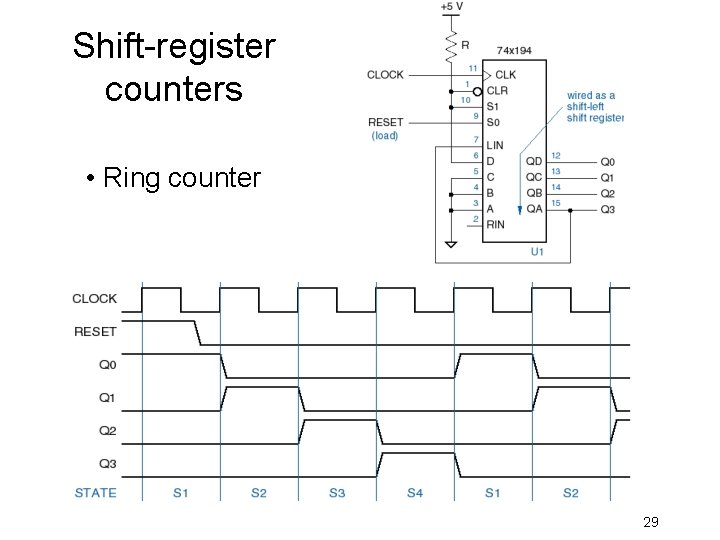

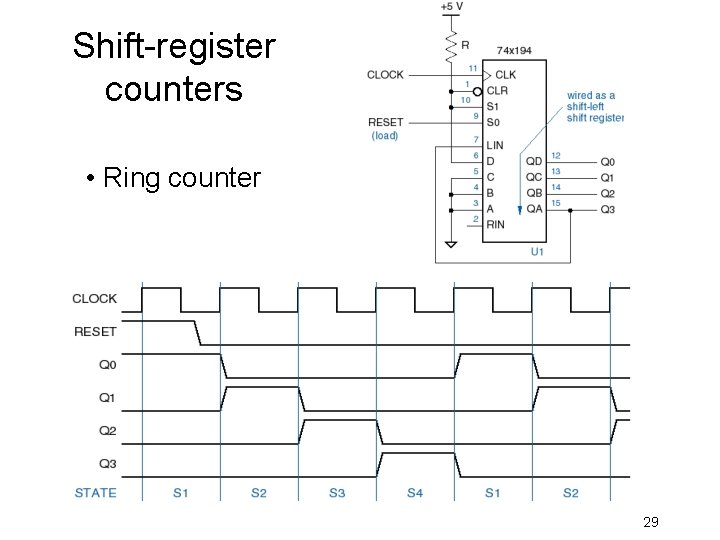

Shift-register counters • Ring counter 29

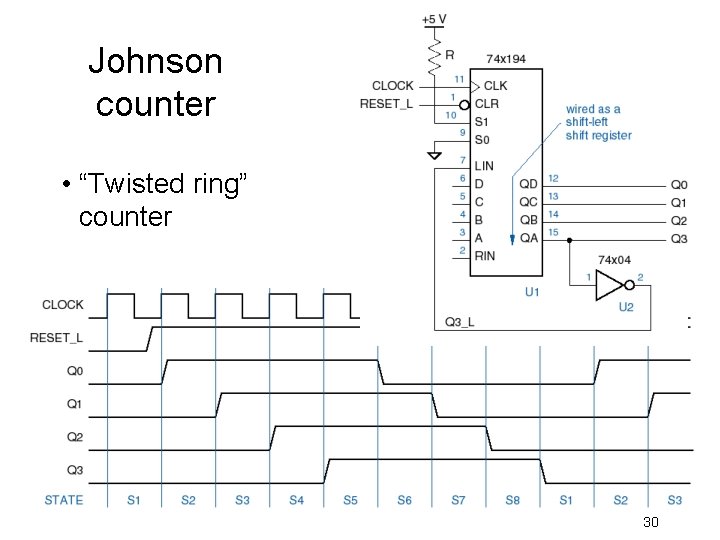

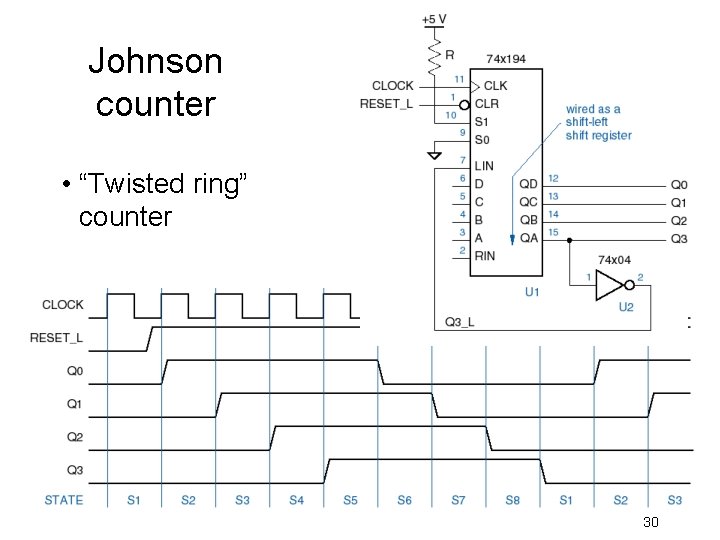

Johnson counter • “Twisted ring” counter 30

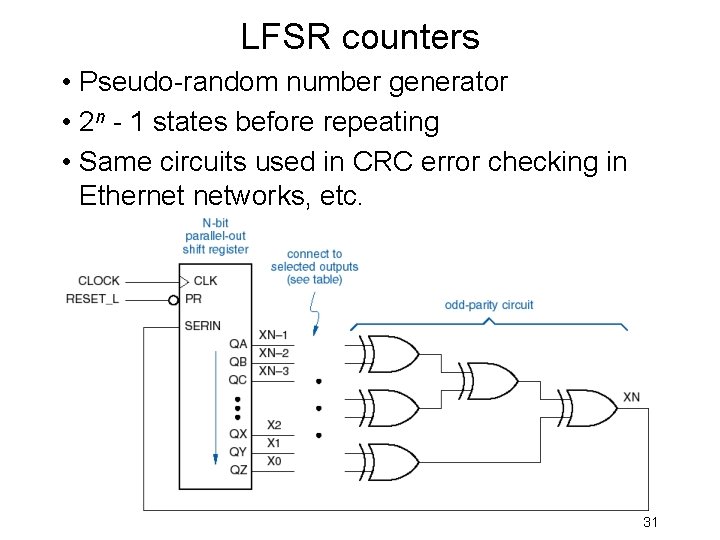

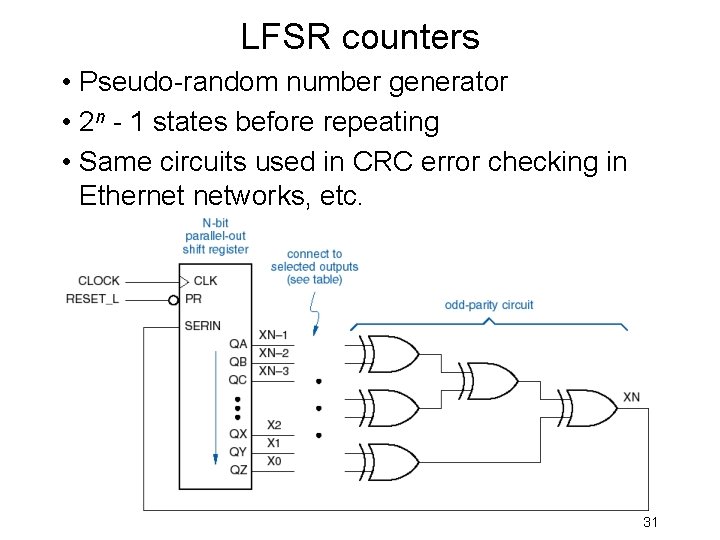

LFSR counters • Pseudo-random number generator • 2 n - 1 states before repeating • Same circuits used in CRC error checking in Ethernet networks, etc. 31