EE 319 K Introduction to Embedded Systems Lecture

EE 319 K Introduction to Embedded Systems Lecture 10: Sampling, Analog-to-Digital Conversion http: //users. ece. utexas. edu/~valvano/Volume 1/E-Book/C 13_Interactives. htm http: //users. ece. utexas. edu/~valvano/Volume 1/E-Book/C 14_Interactives. htm Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -1

Agenda q Recap v. Local Variables v. Stack frames v. Recursion v. Fixed-point numbers v. LCD device driver (Lab 7) q Outline v. Sampling, Nyquist theorem v. Analog to Digital Conversion Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -2

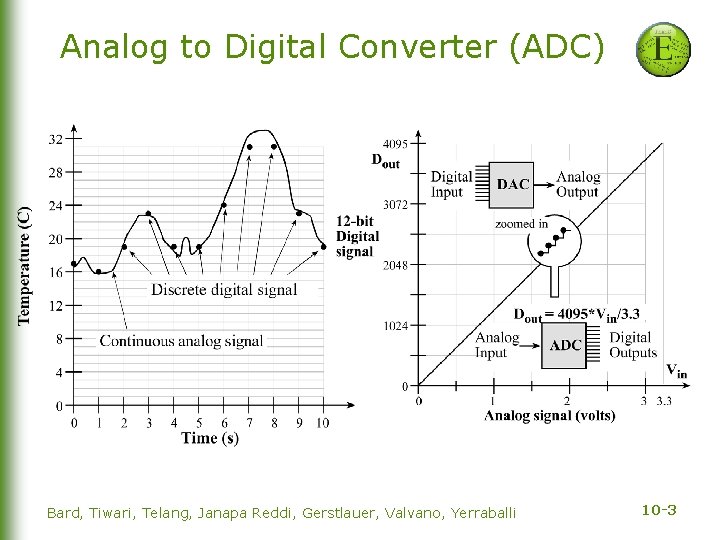

Analog to Digital Converter (ADC) Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -3

Nyquist Theorem q A bandlimited analog signal that has been sampled can be perfectly reconstructed from an infinite sequence of samples if the sampling rate fs exceeds 2 fmax samples per second, where fmax is the highest frequency in the original signal. v If the analog signal does contain frequency components larger than (1/2)fs, then there will be an aliasing error. v Aliasing is when the digital signal appears to have a different frequency than the original analog signal. q Valvano Postulate: If fmax is the largest frequency component of the analog signal, then you must sample more than ten times fmax in order for the reconstructed digital samples to look like the original signal when plotted on a voltage versus time graph. http: //users. ece. utexas. edu/~valvano/Volume 1/E-Book/C 13_Interactives. htm http: //users. ece. utexas. edu/~valvano/Volume 1/E-Book/C 14_Interactives. htm Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -4

Sampling (option 1) q 200 Hz signal sampled at 2000 Hz Look at 200 Hz 1800 Hz 2200 Hz http: //www. ece. utexas. edu/~valvano/Volume 1/Nyquist. xls Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -5

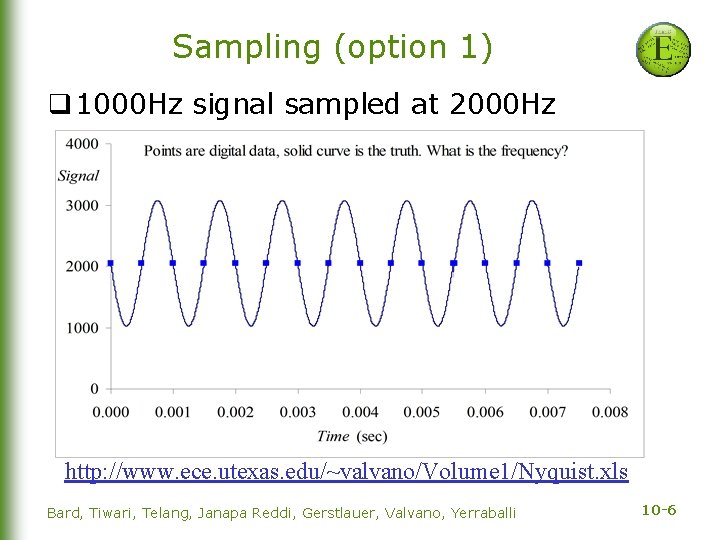

Sampling (option 1) q 1000 Hz signal sampled at 2000 Hz http: //www. ece. utexas. edu/~valvano/Volume 1/Nyquist. xls Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -6

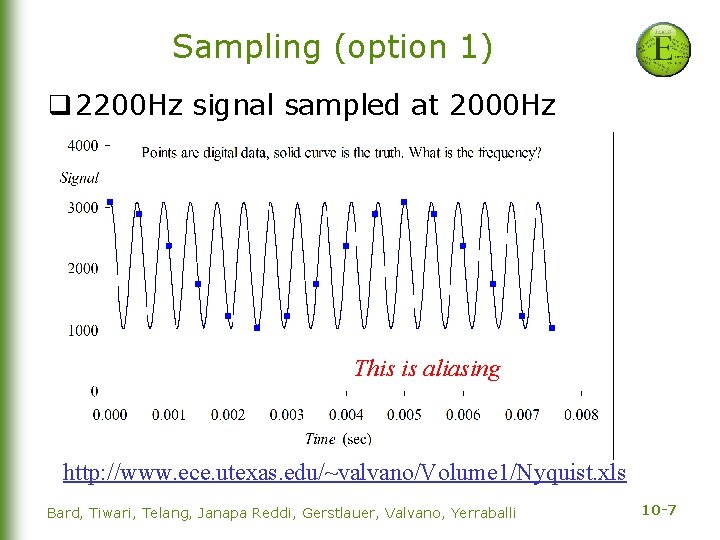

Sampling (option 1) q 2200 Hz signal sampled at 2000 Hz This is aliasing http: //www. ece. utexas. edu/~valvano/Volume 1/Nyquist. xls Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -7

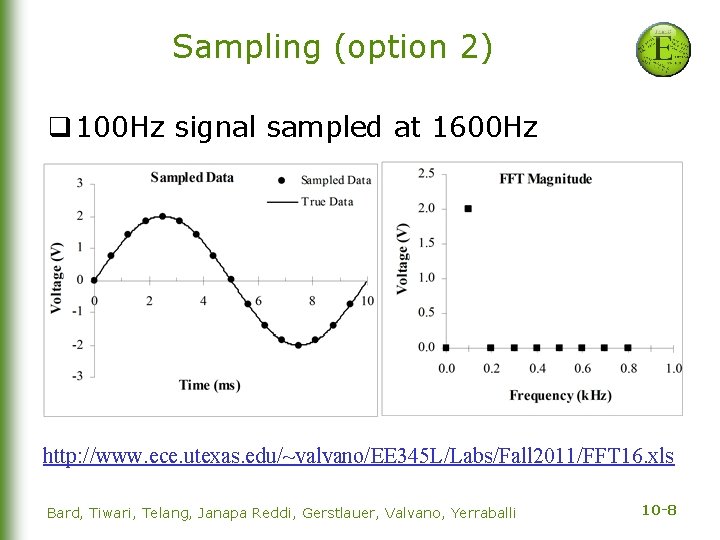

Sampling (option 2) q 100 Hz signal sampled at 1600 Hz http: //www. ece. utexas. edu/~valvano/EE 345 L/Labs/Fall 2011/FFT 16. xls Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -8

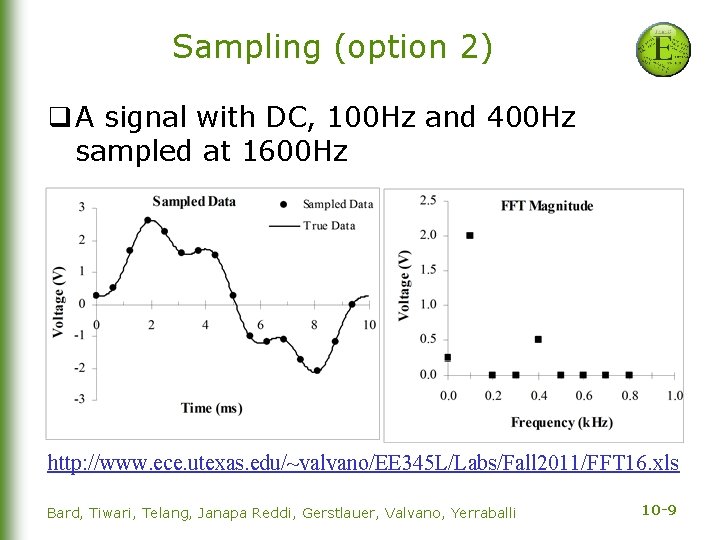

Sampling (option 2) q A signal with DC, 100 Hz and 400 Hz sampled at 1600 Hz http: //www. ece. utexas. edu/~valvano/EE 345 L/Labs/Fall 2011/FFT 16. xls Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -9

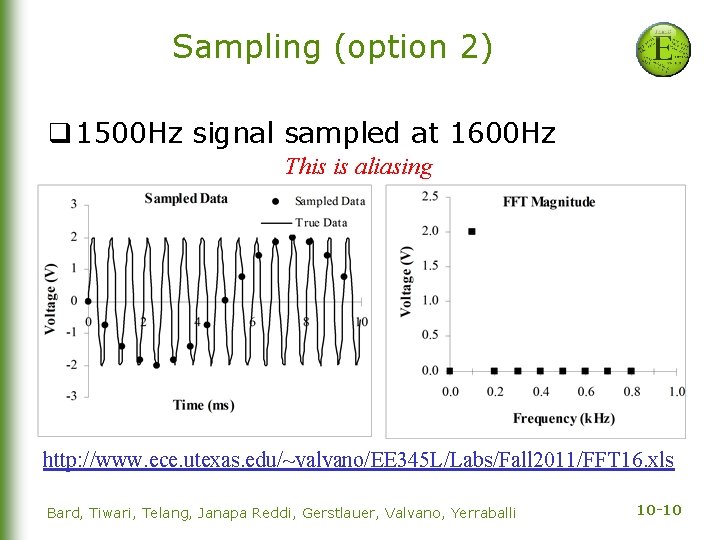

Sampling (option 2) q 1500 Hz signal sampled at 1600 Hz This is aliasing http: //www. ece. utexas. edu/~valvano/EE 345 L/Labs/Fall 2011/FFT 16. xls Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -10

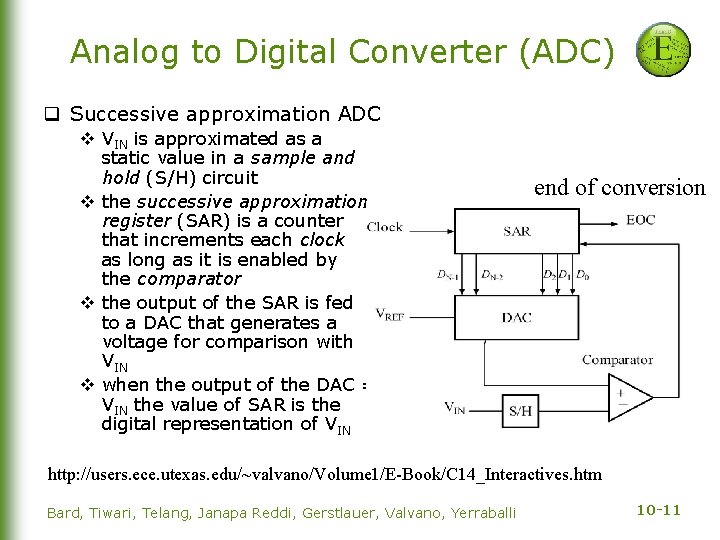

Analog to Digital Converter (ADC) q Successive approximation ADC v VIN is approximated as a static value in a sample and hold (S/H) circuit v the successive approximation register (SAR) is a counter that increments each clock as long as it is enabled by the comparator v the output of the SAR is fed to a DAC that generates a voltage for comparison with VIN v when the output of the DAC = VIN the value of SAR is the digital representation of VIN end of conversion http: //users. ece. utexas. edu/~valvano/Volume 1/E-Book/C 14_Interactives. htm Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -11

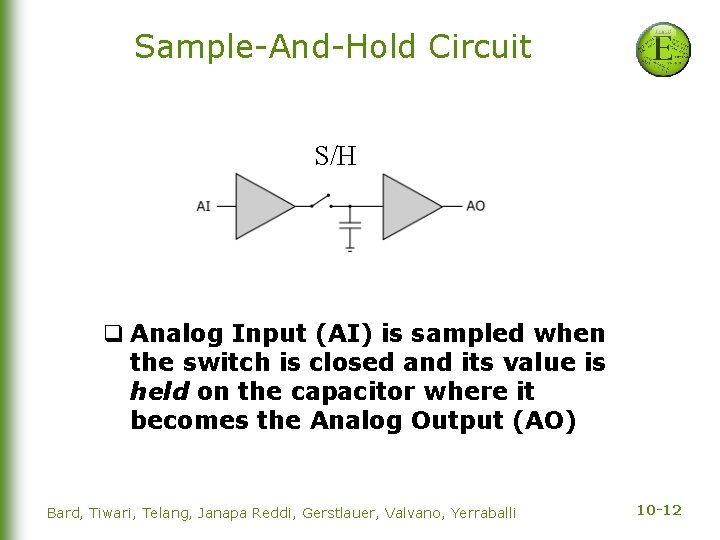

Sample-And-Hold Circuit S/H q Analog Input (AI) is sampled when the switch is closed and its value is held on the capacitor where it becomes the Analog Output (AO) Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -12

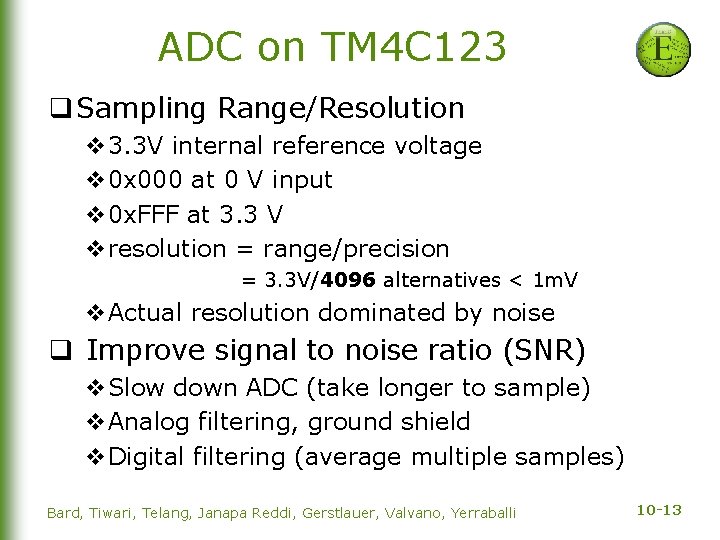

ADC on TM 4 C 123 q Sampling Range/Resolution v 3. 3 V internal reference voltage v 0 x 000 at 0 V input v 0 x. FFF at 3. 3 V vresolution = range/precision = 3. 3 V/4096 alternatives < 1 m. V v. Actual resolution dominated by noise q Improve signal to noise ratio (SNR) v. Slow down ADC (take longer to sample) v. Analog filtering, ground shield v. Digital filtering (average multiple samples) Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -13

ADC on TM 4 C 123 PE 2=Ain 1 used for Lab 8, 9, 10 Twelve analog input channels Single-ended and differential-input configurations On-chip internal temperature sensor Sample rate up to one million samples/second 40 Hz Flexible, configurable analog-to-digital conversion Four programmable sample conversion sequences from one to eight entries long, with corresponding conversion result FIFOs q Flexible trigger control q q q v v v Controller (software) Timers Analog Comparators PWM GPIO We will use software initiated trigger q Hardware averaging of up to 64 samples for improved accuracy q Converter uses an internal 3 V reference Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -14

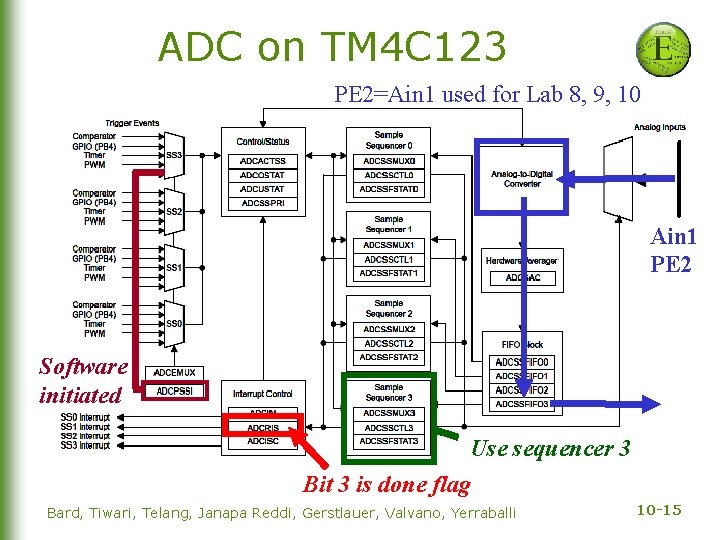

ADC on TM 4 C 123 PE 2=Ain 1 used for Lab 8, 9, 10 Ain 1 PE 2 Software initiated Use sequencer 3 Bit 3 is done flag Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -15

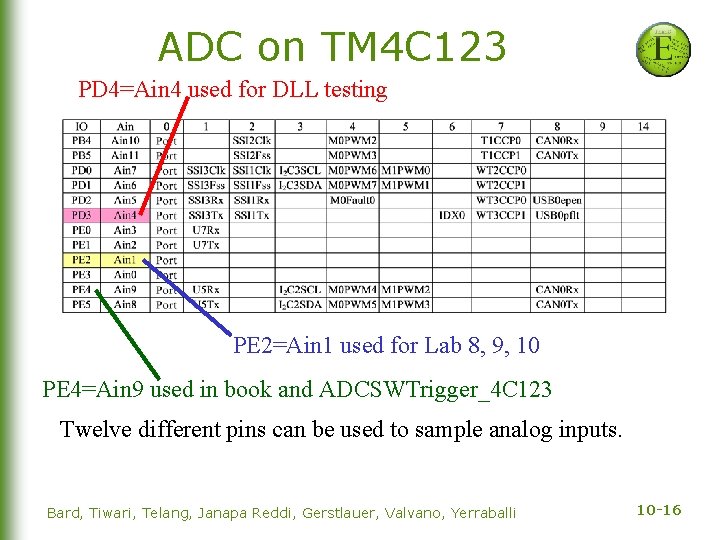

ADC on TM 4 C 123 PD 4=Ain 4 used for DLL testing PE 2=Ain 1 used for Lab 8, 9, 10 PE 4=Ain 9 used in book and ADCSWTrigger_4 C 123 Twelve different pins can be used to sample analog inputs. Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -16

ADC on TM 4 C 123 q TM 4 C ADC registers Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -17

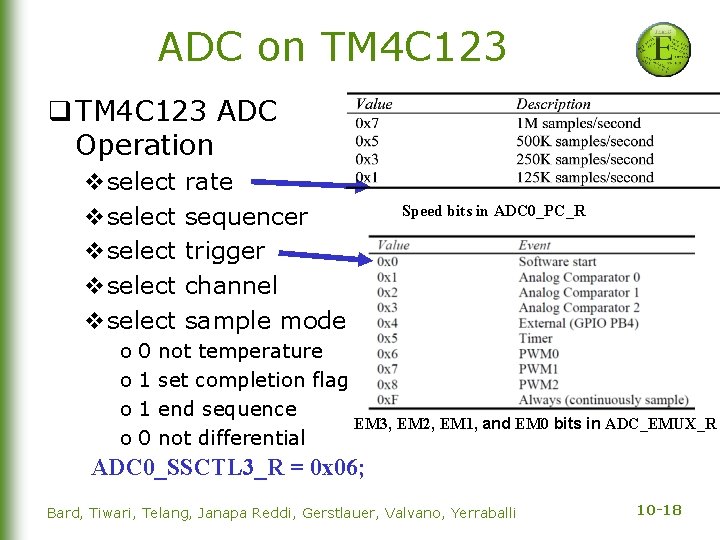

ADC on TM 4 C 123 q TM 4 C 123 ADC Operation vselect vselect o 0 o 1 o 0 rate sequencer trigger channel sample mode Speed bits in ADC 0_PC_R not temperature set completion flag end sequence EM 3, EM 2, EM 1, and EM 0 bits in ADC_EMUX_R not differential ADC 0_SSCTL 3_R = 0 x 06; Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -18

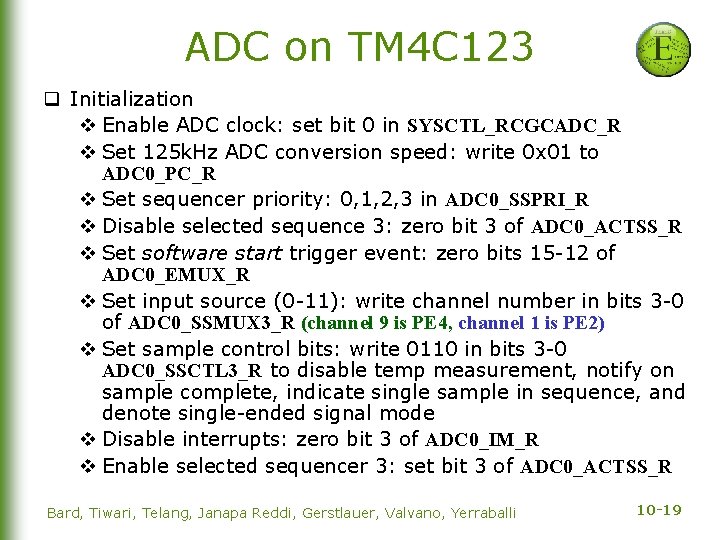

ADC on TM 4 C 123 q Initialization v Enable ADC clock: set bit 0 in SYSCTL_RCGCADC_R v Set 125 k. Hz ADC conversion speed: write 0 x 01 to ADC 0_PC_R v Set sequencer priority: 0, 1, 2, 3 in ADC 0_SSPRI_R v Disable selected sequence 3: zero bit 3 of ADC 0_ACTSS_R v Set software start trigger event: zero bits 15 -12 of ADC 0_EMUX_R v Set input source (0 -11): write channel number in bits 3 -0 of ADC 0_SSMUX 3_R (channel 9 is PE 4, channel 1 is PE 2) v Set sample control bits: write 0110 in bits 3 -0 ADC 0_SSCTL 3_R to disable temp measurement, notify on sample complete, indicate single sample in sequence, and denote single-ended signal mode v Disable interrupts: zero bit 3 of ADC 0_IM_R v Enable selected sequencer 3: set bit 3 of ADC 0_ACTSS_R Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -19

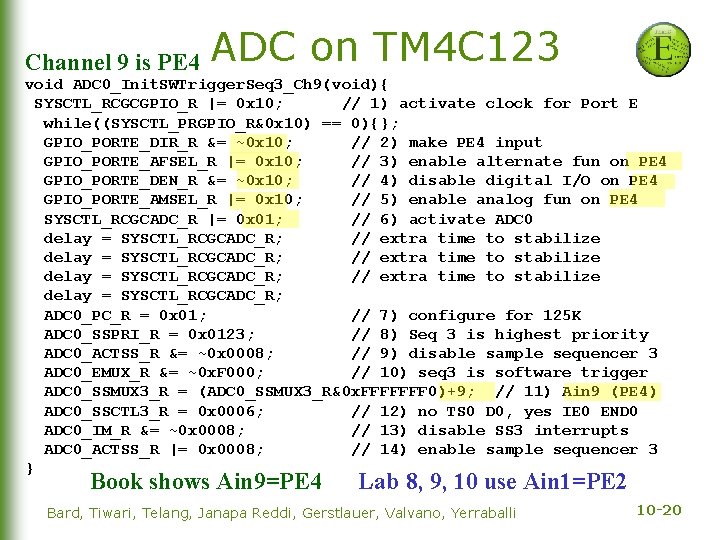

Channel 9 is PE 4 ADC on TM 4 C 123 void ADC 0_Init. SWTrigger. Seq 3_Ch 9(void){ SYSCTL_RCGCGPIO_R |= 0 x 10; // 1) activate clock for Port E while((SYSCTL_PRGPIO_R&0 x 10) == 0){}; GPIO_PORTE_DIR_R &= ~0 x 10; // 2) make PE 4 input GPIO_PORTE_AFSEL_R |= 0 x 10; // 3) enable alternate fun on PE 4 GPIO_PORTE_DEN_R &= ~0 x 10; // 4) disable digital I/O on PE 4 GPIO_PORTE_AMSEL_R |= 0 x 10; // 5) enable analog fun on PE 4 SYSCTL_RCGCADC_R |= 0 x 01; // 6) activate ADC 0 delay = SYSCTL_RCGCADC_R; // extra time to stabilize delay = SYSCTL_RCGCADC_R; ADC 0_PC_R = 0 x 01; // 7) configure for 125 K ADC 0_SSPRI_R = 0 x 0123; // 8) Seq 3 is highest priority ADC 0_ACTSS_R &= ~0 x 0008; // 9) disable sample sequencer 3 ADC 0_EMUX_R &= ~0 x. F 000; // 10) seq 3 is software trigger ADC 0_SSMUX 3_R = (ADC 0_SSMUX 3_R&0 x. FFFFFFF 0)+9; // 11) Ain 9 (PE 4) ADC 0_SSCTL 3_R = 0 x 0006; // 12) no TS 0 D 0, yes IE 0 END 0 ADC 0_IM_R &= ~0 x 0008; // 13) disable SS 3 interrupts ADC 0_ACTSS_R |= 0 x 0008; // 14) enable sample sequencer 3 } Book shows Ain 9=PE 4 Lab 8, 9, 10 use Ain 1=PE 2 Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -20

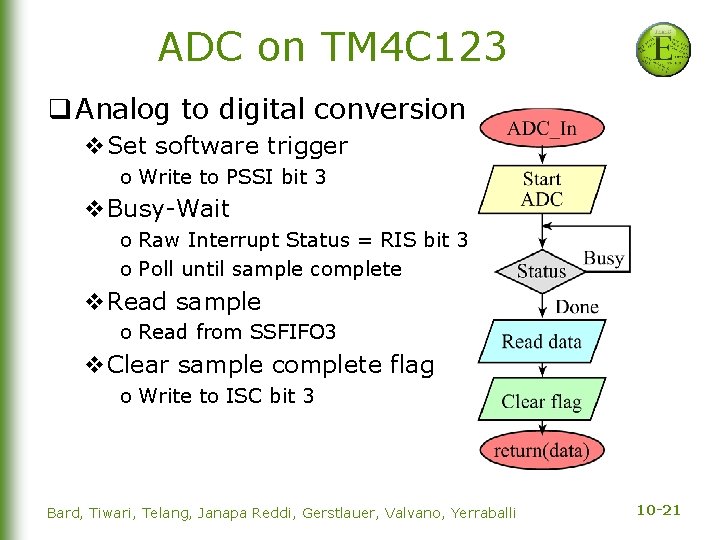

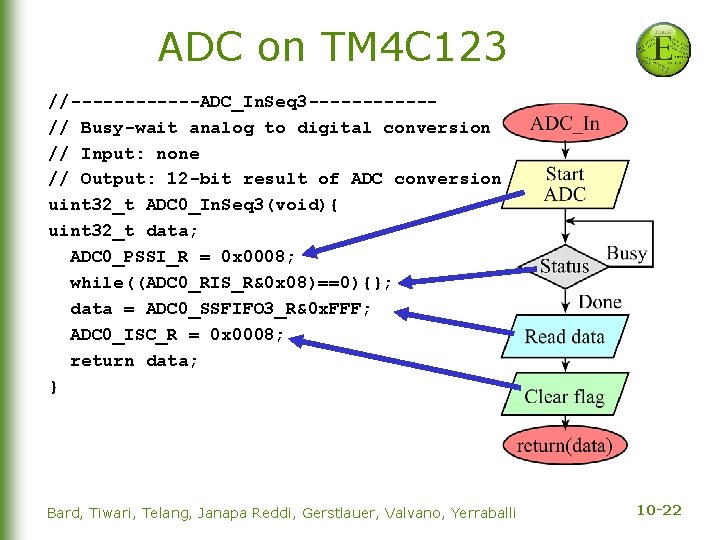

ADC on TM 4 C 123 q Analog to digital conversion v. Set software trigger o Write to PSSI bit 3 v. Busy-Wait o Raw Interrupt Status = RIS bit 3 o Poll until sample complete v. Read sample o Read from SSFIFO 3 v. Clear sample complete flag o Write to ISC bit 3 Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -21

ADC on TM 4 C 123 //------ADC_In. Seq 3 ------// Busy-wait analog to digital conversion // Input: none // Output: 12 -bit result of ADC conversion uint 32_t ADC 0_In. Seq 3(void){ uint 32_t data; ADC 0_PSSI_R = 0 x 0008; while((ADC 0_RIS_R&0 x 08)==0){}; data = ADC 0_SSFIFO 3_R&0 x. FFF; ADC 0_ISC_R = 0 x 0008; return data; } Bard, Tiwari, Telang, Janapa Reddi, Gerstlauer, Valvano, Yerraballi 10 -22

- Slides: 22