ECE 667 Synthesis and Verification of Digital Circuits

![Linear Programming – example • Variables: x = [x 1, x 2]T • Objective Linear Programming – example • Variables: x = [x 1, x 2]T • Objective](https://slidetodoc.com/presentation_image_h/754df173f2a8197899ab95a5f0b1d132/image-4.jpg)

![Example 3 – Min. Resources under Latency Constraint • Let c = [5, 1] Example 3 – Min. Resources under Latency Constraint • Let c = [5, 1]](https://slidetodoc.com/presentation_image_h/754df173f2a8197899ab95a5f0b1d132/image-21.jpg)

- Slides: 24

ECE 667 Synthesis and Verification of Digital Circuits Scheduling Algorithms Analytical approach - ILP 1 ECE 667 - Synthesis & Verification - LP Scheduling

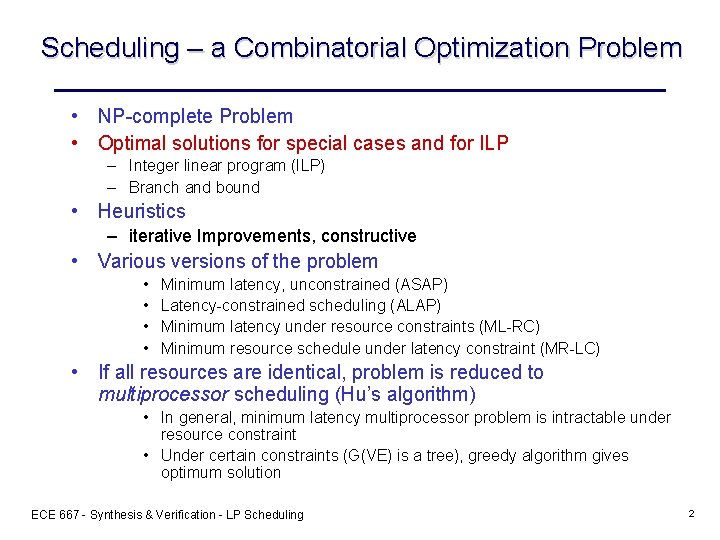

Scheduling – a Combinatorial Optimization Problem • NP-complete Problem • Optimal solutions for special cases and for ILP – Integer linear program (ILP) – Branch and bound • Heuristics – iterative Improvements, constructive • Various versions of the problem • • Minimum latency, unconstrained (ASAP) Latency-constrained scheduling (ALAP) Minimum latency under resource constraints (ML-RC) Minimum resource schedule under latency constraint (MR-LC) • If all resources are identical, problem is reduced to multiprocessor scheduling (Hu’s algorithm) • In general, minimum latency multiprocessor problem is intractable under resource constraint • Under certain constraints (G(VE) is a tree), greedy algorithm gives optimum solution ECE 667 - Synthesis & Verification - LP Scheduling 2

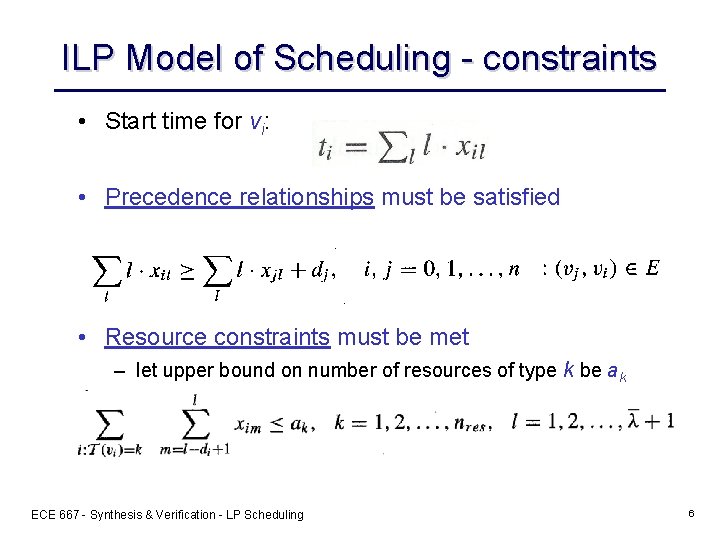

Integer Linear Programming (ILP) • Given: – integer-valued matrix Am x n – variables: x = ( x 1, x 2, … , xn )T – constants: b = ( b 1, b 2, … , bm )T and c = ( c 1, c 2, … , cn )T • Minimize: c. T x subject to: Ax b x = ( x 1, x 2, … , xn ) is an integer-valued vector • If all variables are continuous, the problem is called linear (LP) • Problem is called Integer LP (ILP) if some variables x are integer – special case: 0, 1 (binary) ILP ECE 667 - Synthesis & Verification - LP Scheduling 3

![Linear Programming example Variables x x 1 x 2T Objective Linear Programming – example • Variables: x = [x 1, x 2]T • Objective](https://slidetodoc.com/presentation_image_h/754df173f2a8197899ab95a5f0b1d132/image-4.jpg)

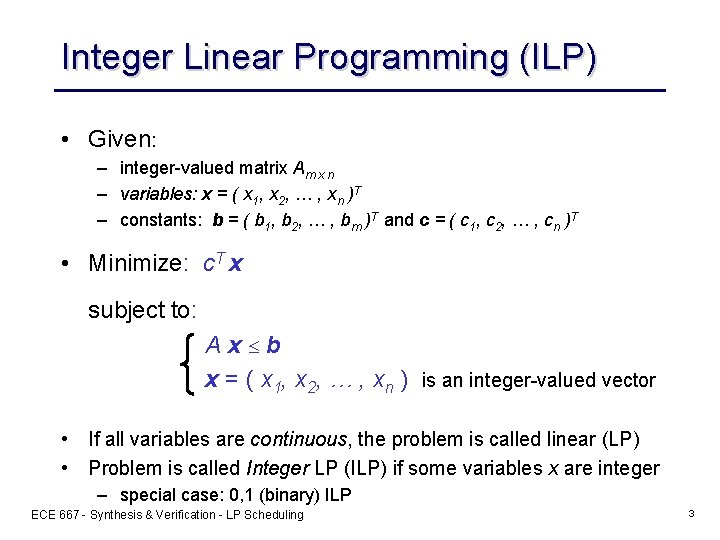

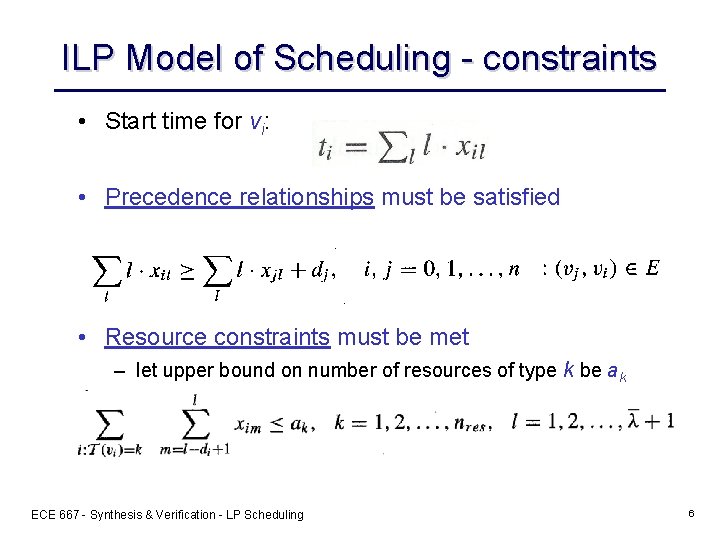

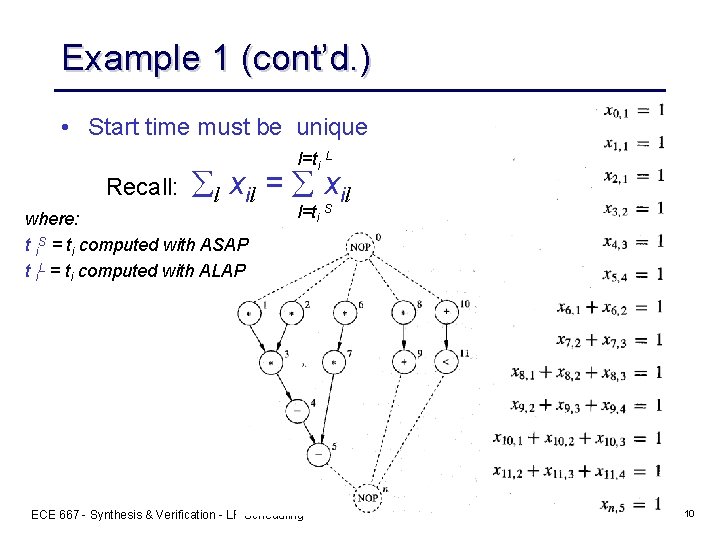

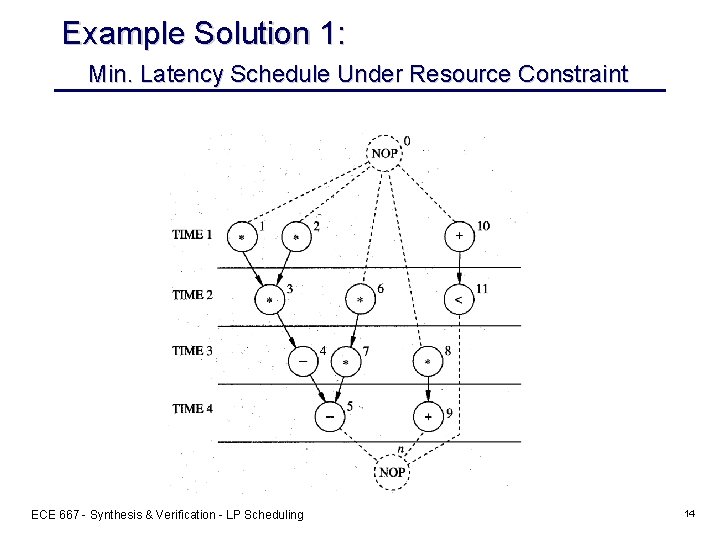

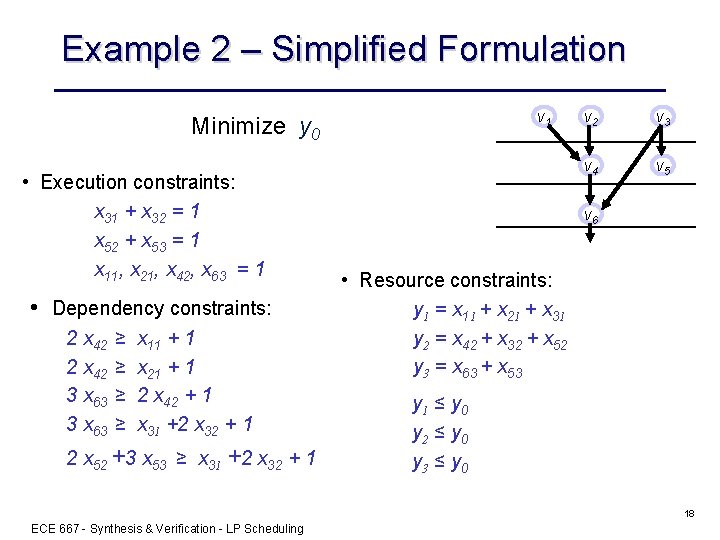

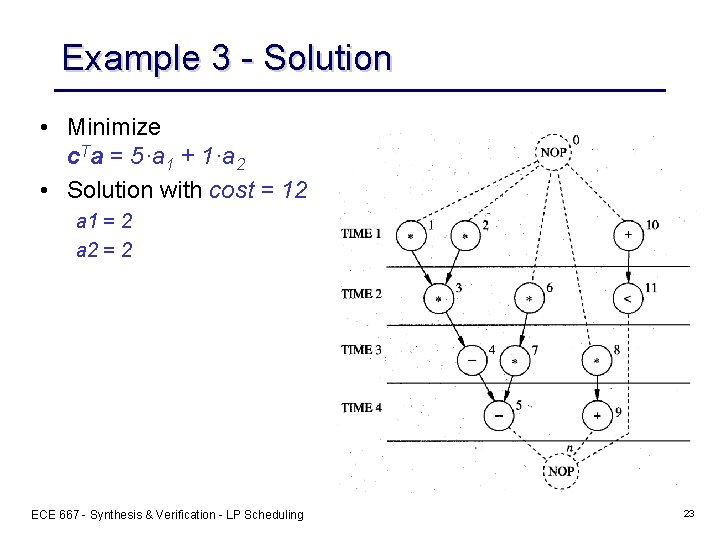

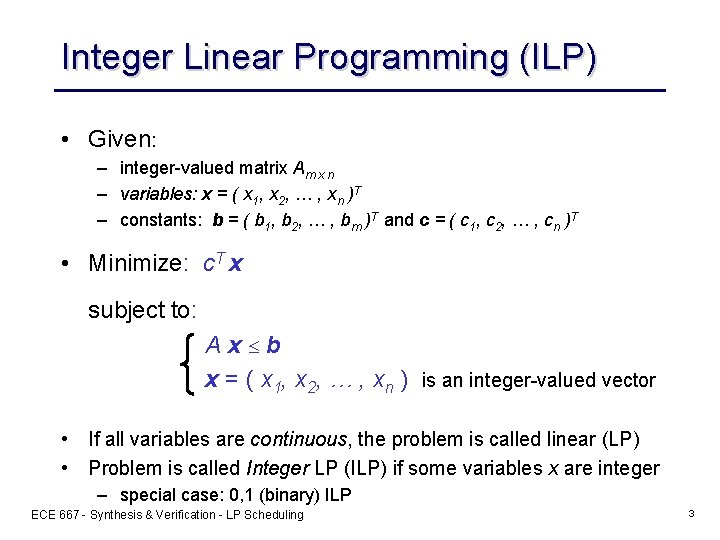

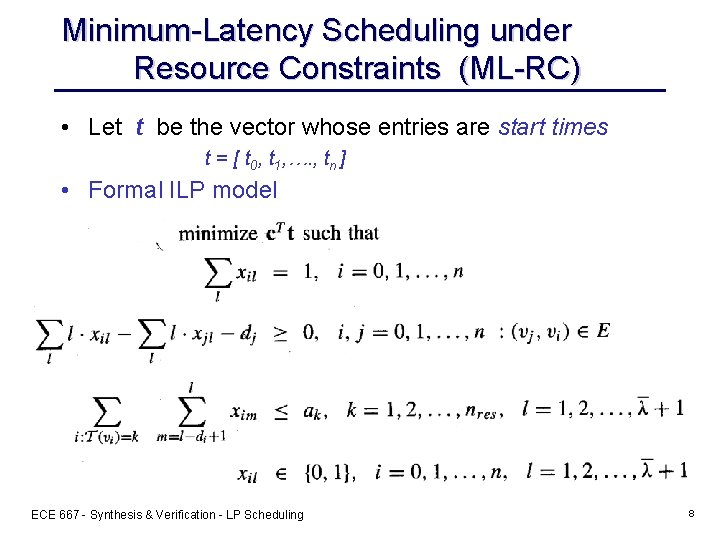

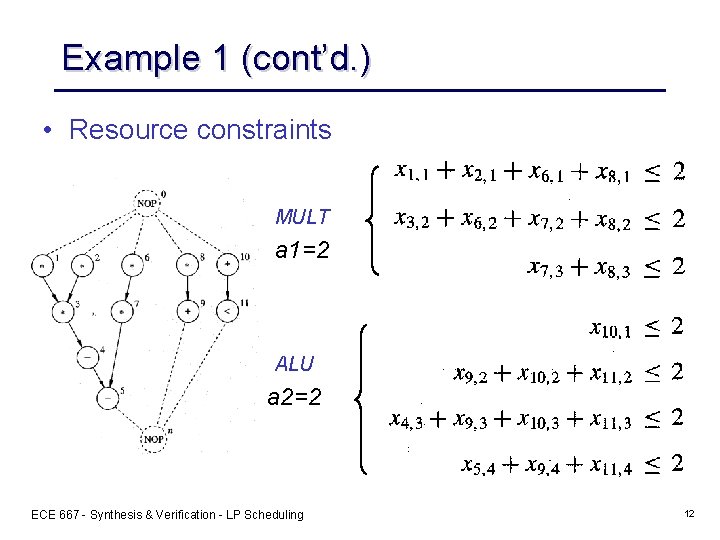

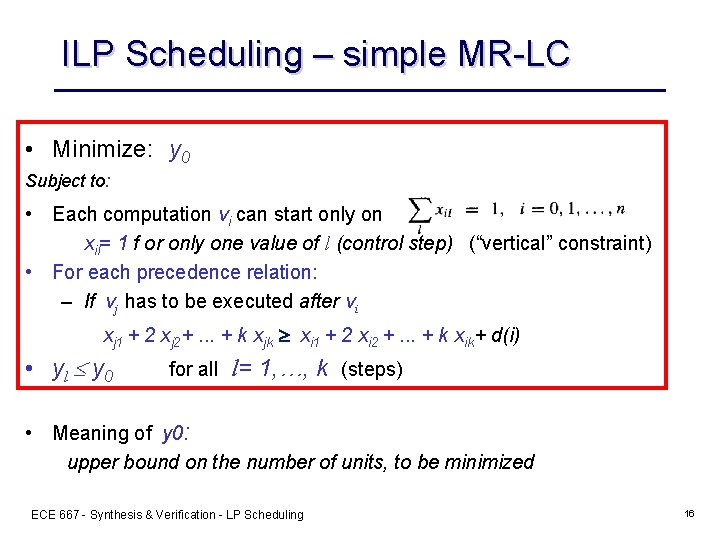

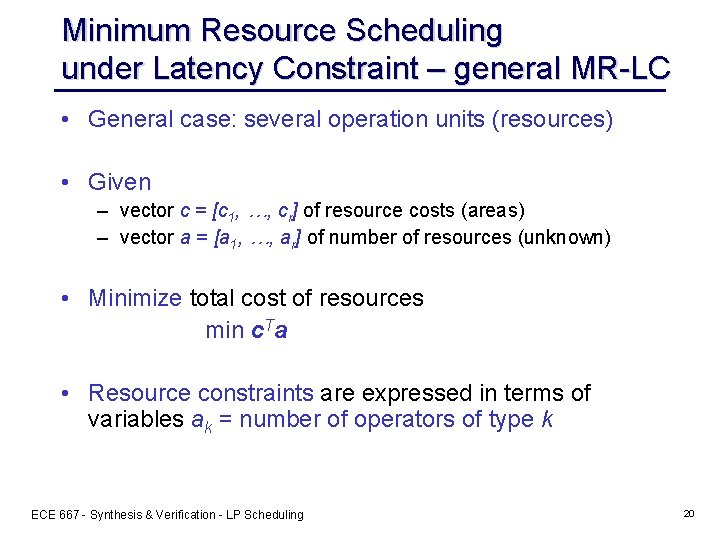

Linear Programming – example • Variables: x = [x 1, x 2]T • Objective function: max F = -x 1 + x 2 = [-1 1] [x 1, x 2]T • Constraints: -2 x 1 + x 2 1 x 2 x 1 + 2 x 2 5 F * =1. 6 3 F=1 F=0 F *= 1. 6 (x 1=0. 6, x 2=2. 2) 2 1 x 1 1 2 ECE 667 - Synthesis & Verification - LP Scheduling 3 4 5 4

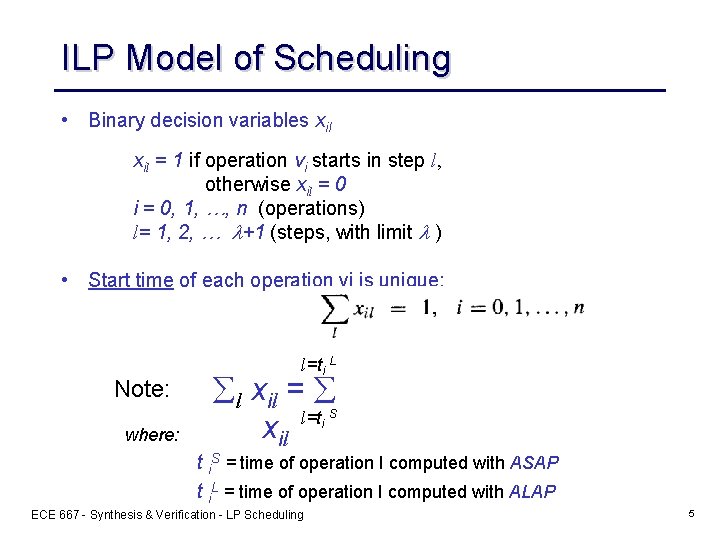

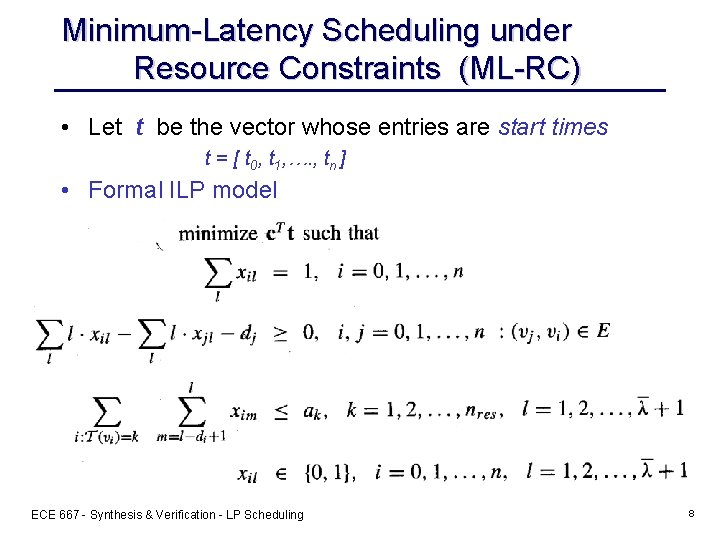

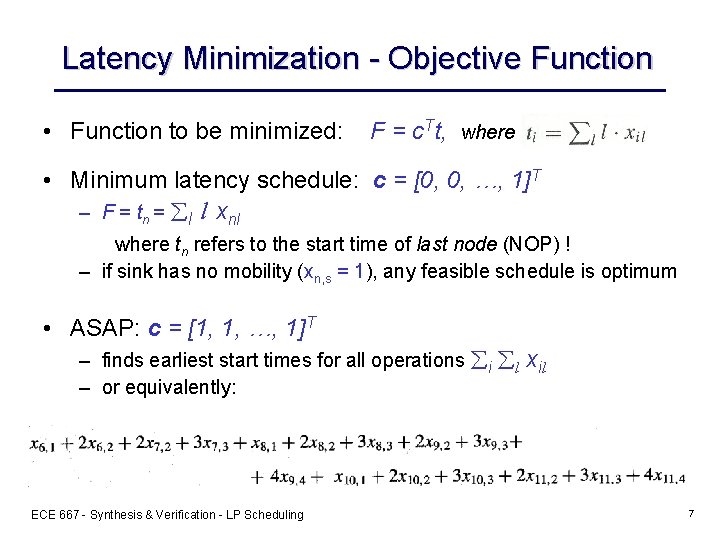

ILP Model of Scheduling • Binary decision variables xil = 1 if operation vi starts in step l, otherwise xil = 0 i = 0, 1, …, n (operations) l= 1, 2, … +1 (steps, with limit ) • Start time of each operation vi is unique: Note: where: l=ti L l xil = l=t xil i S t i. S = time of operation I computed with ASAP t i. L = time of operation I computed with ALAP ECE 667 - Synthesis & Verification - LP Scheduling 5

ILP Model of Scheduling - constraints • Start time for vi: • Precedence relationships must be satisfied • Resource constraints must be met – let upper bound on number of resources of type k be ak ECE 667 - Synthesis & Verification - LP Scheduling 6

Latency Minimization - Objective Function • Function to be minimized: F = c. Tt, where • Minimum latency schedule: c = [0, 0, …, 1]T – F = tn = l l xnl where tn refers to the start time of last node (NOP) ! – if sink has no mobility (xn, s = 1), any feasible schedule is optimum • ASAP: c = [1, 1, …, 1]T – finds earliest start times for all operations i l xil – or equivalently: ECE 667 - Synthesis & Verification - LP Scheduling 7

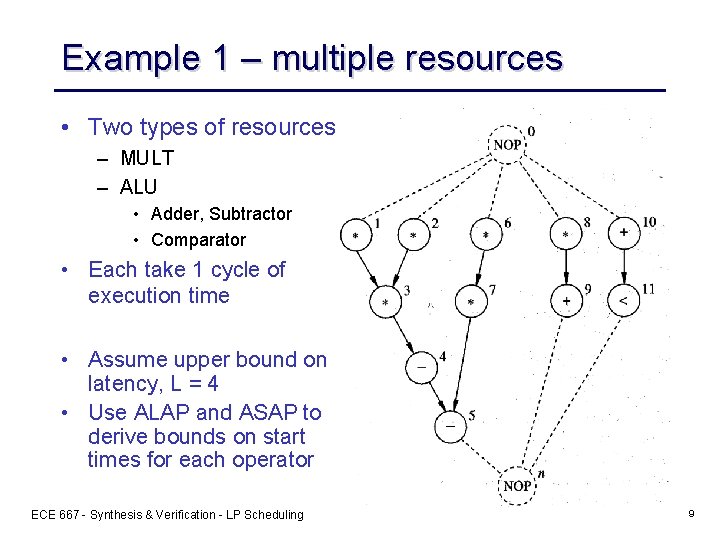

Minimum-Latency Scheduling under Resource Constraints (ML-RC) • Let t be the vector whose entries are start times t = [ t 0, t 1, …. , tn ] • Formal ILP model ECE 667 - Synthesis & Verification - LP Scheduling 8

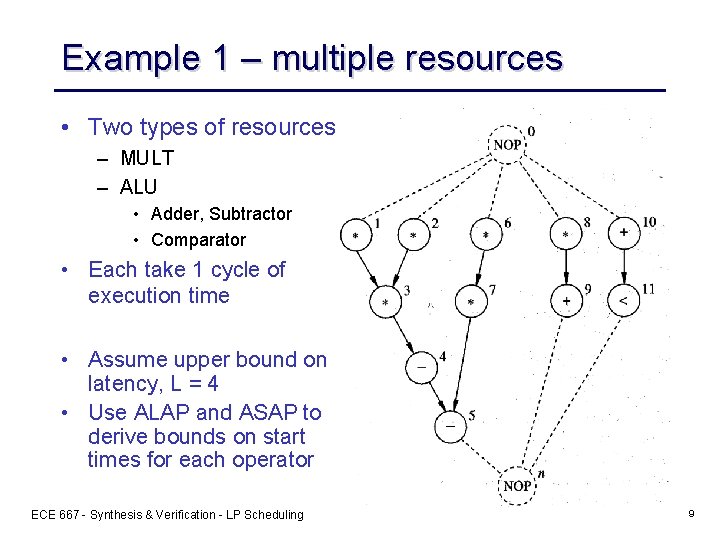

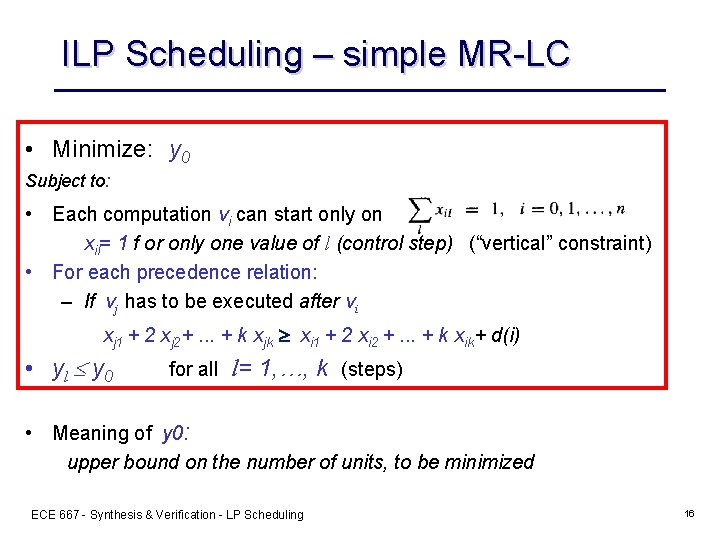

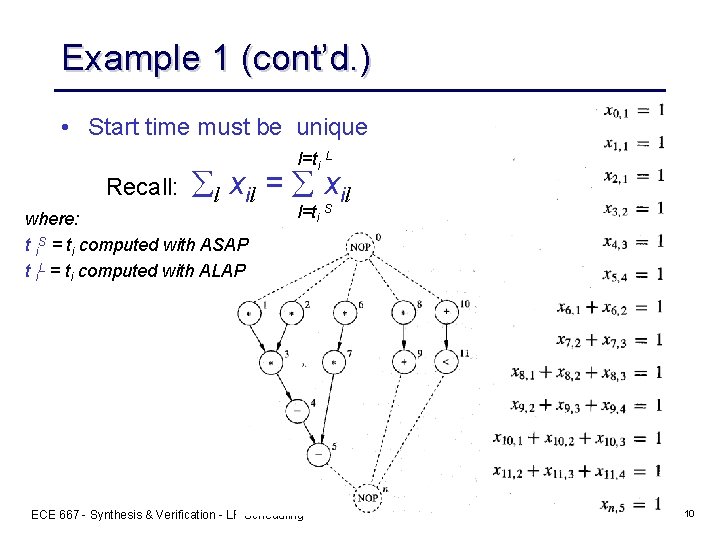

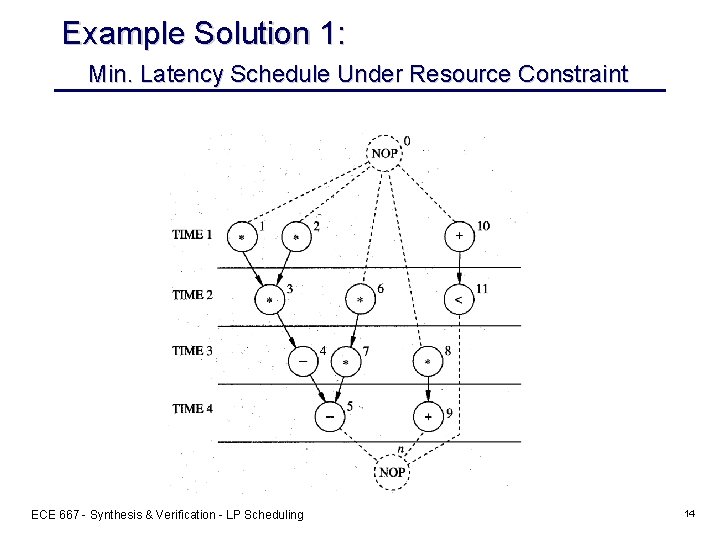

Example 1 – multiple resources • Two types of resources – MULT – ALU • Adder, Subtractor • Comparator • Each take 1 cycle of execution time • Assume upper bound on latency, L = 4 • Use ALAP and ASAP to derive bounds on start times for each operator ECE 667 - Synthesis & Verification - LP Scheduling 9

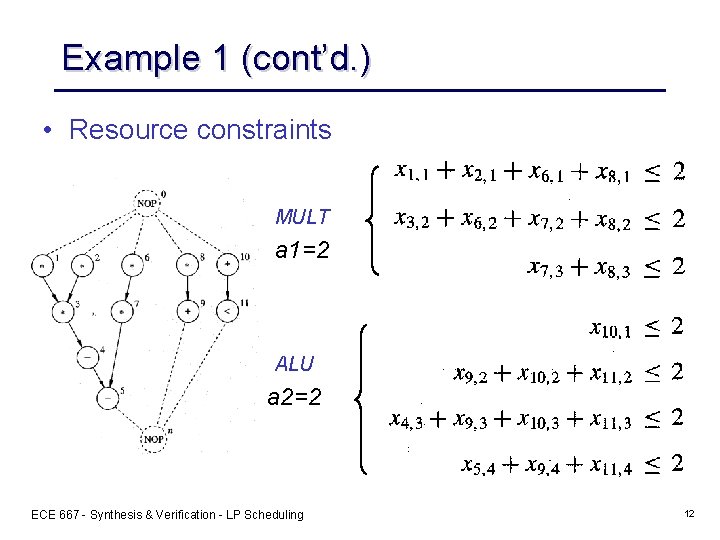

Example 1 (cont’d. ) • Start time must be unique l=ti L Recall: l xil = xil where: t i. S = ti computed with ASAP t i. L = ti computed with ALAP l=ti S ECE 667 - Synthesis & Verification - LP Scheduling 10

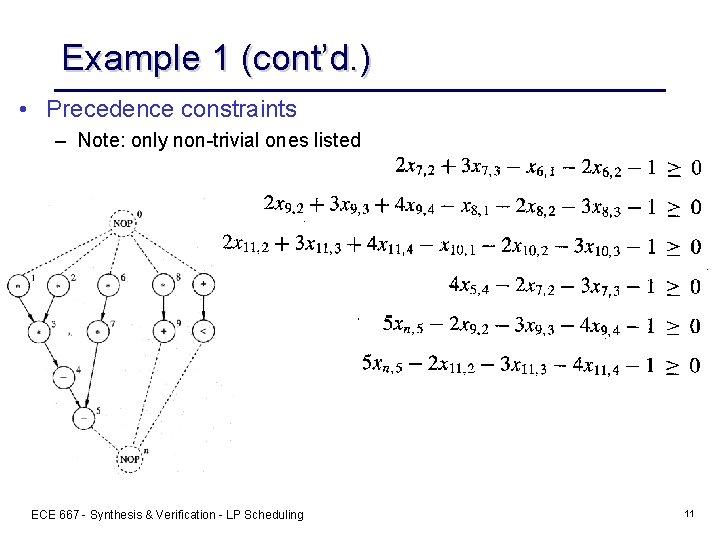

Example 1 (cont’d. ) • Precedence constraints – Note: only non-trivial ones listed ECE 667 - Synthesis & Verification - LP Scheduling 11

Example 1 (cont’d. ) • Resource constraints MULT a 1=2 ALU a 2=2 ECE 667 - Synthesis & Verification - LP Scheduling 12

Example 1 (cont’d. ) • Objective function (some possibilities): F = c. Tt • F 1: c = [0, 0, …, 1]T – where last entry refers to the last node (NOP) ! – Minimum latency schedule – since sink has no mobility (xn, 5 = 1), any feasible schedule is optimum • F 2: c = [1, 1, …, 1] T – finds earliest start times for all operations i l xil – or equivalently: ECE 667 - Synthesis & Verification - LP Scheduling 13

Example Solution 1: Min. Latency Schedule Under Resource Constraint ECE 667 - Synthesis & Verification - LP Scheduling 14

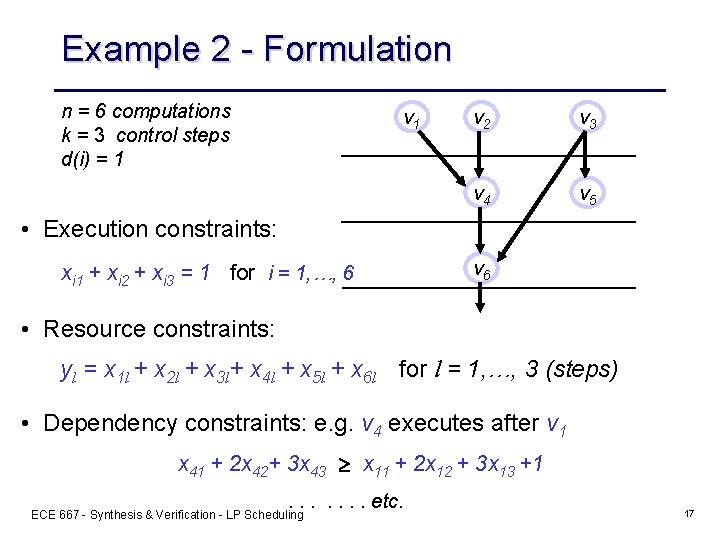

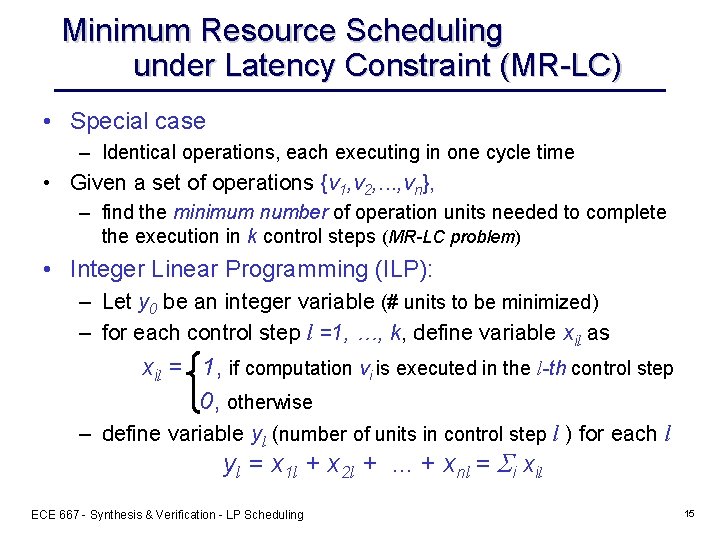

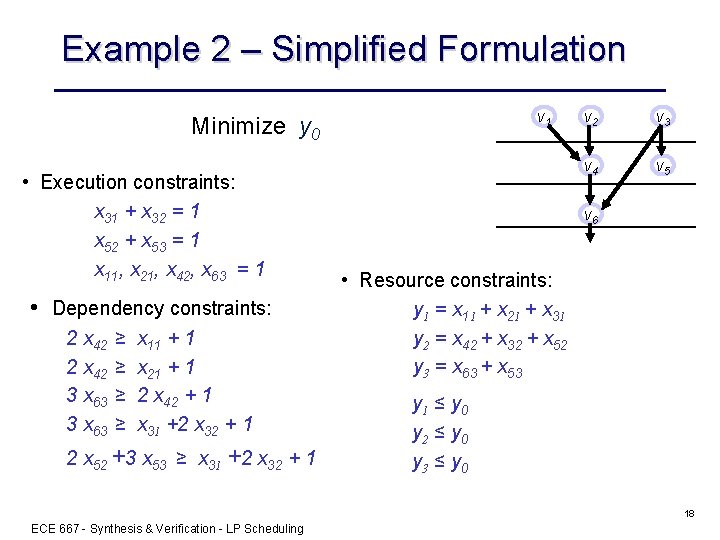

Minimum Resource Scheduling under Latency Constraint (MR-LC) • Special case – Identical operations, each executing in one cycle time • Given a set of operations {v 1, v 2, . . . , vn}, – find the minimum number of operation units needed to complete the execution in k control steps (MR-LC problem) • Integer Linear Programming (ILP): – Let y 0 be an integer variable (# units to be minimized) – for each control step l =1, …, k, define variable xil as xil = 1, if computation vi is executed in the l-th control step 0, otherwise – define variable yl (number of units in control step l ) for each l yl = x 1 l + x 2 l +. . . + xnl = i xil ECE 667 - Synthesis & Verification - LP Scheduling 15

ILP Scheduling – simple MR-LC • Minimize: y 0 Subject to: • Each computation vi can start only once: xil= 1 f or only one value of l (control step) (“vertical” constraint) • For each precedence relation: – If vj has to be executed after vi xj 1 + 2 xj 2+. . . + k xjk xi 1 + 2 xi 2 +. . . + k xik+ d(i) • yl y 0 for all l= 1, …, k (steps) • Meaning of y 0: upper bound on the number of units, to be minimized ECE 667 - Synthesis & Verification - LP Scheduling 16

Example 2 - Formulation n = 6 computations k = 3 control steps d(i) = 1 v 2 v 3 v 4 v 5 • Execution constraints: xi 1 + xi 2 + xi 3 = 1 for i = 1, …, 6 v 6 • Resource constraints: yl = x 1 l + x 2 l + x 3 l+ x 4 l + x 5 l + x 6 l for l = 1, …, 3 (steps) • Dependency constraints: e. g. v 4 executes after v 1 x 41 + 2 x 42+ 3 x 43 x 11 + 2 x 12 + 3 x 13 +1. . . . etc. ECE 667 - Synthesis & Verification - LP Scheduling 17

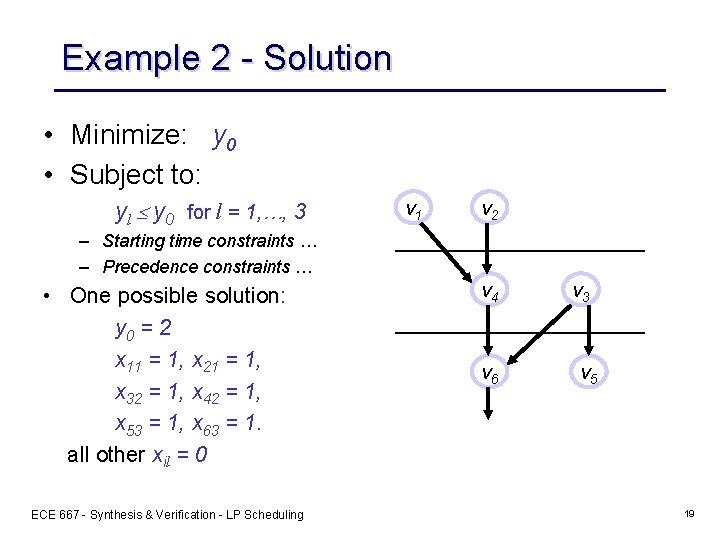

Example 2 – Simplified Formulation v 1 Minimize y 0 • Execution constraints: x 31 + x 32 = 1 x 52 + x 53 = 1 x 11, x 21, x 42, x 63 = 1 • Dependency constraints: 2 x 42 3 x 63 ≥ ≥ x 11 + 1 x 21 + 1 2 x 42 + 1 x 31 +2 x 32 + 1 2 x 52 +3 x 53 ≥ x 31 +2 x 32 + 1 v 2 v 3 v 4 v 5 v 6 • Resource constraints: y 1 = x 11 + x 21 + x 31 y 2 = x 42 + x 32 + x 52 y 3 = x 63 + x 53 y 1 ≤ y 0 y 2 ≤ y 0 y 3 ≤ y 0 18 ECE 667 - Synthesis & Verification - LP Scheduling

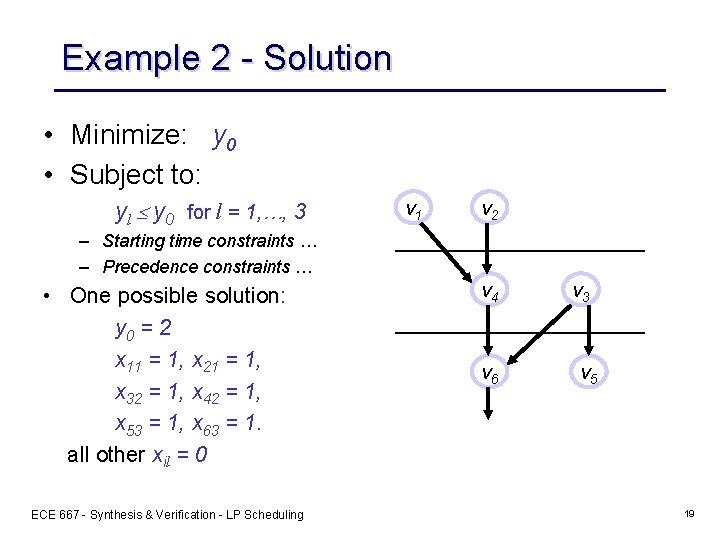

Example 2 - Solution • Minimize: y 0 • Subject to: yl y 0 for l = 1, …, 3 v 1 v 2 – Starting time constraints … – Precedence constraints … • One possible solution: y 0 = 2 x 11 = 1, x 21 = 1, x 32 = 1, x 42 = 1, x 53 = 1, x 63 = 1. all other xil = 0 ECE 667 - Synthesis & Verification - LP Scheduling v 4 v 6 v 3 v 5 19

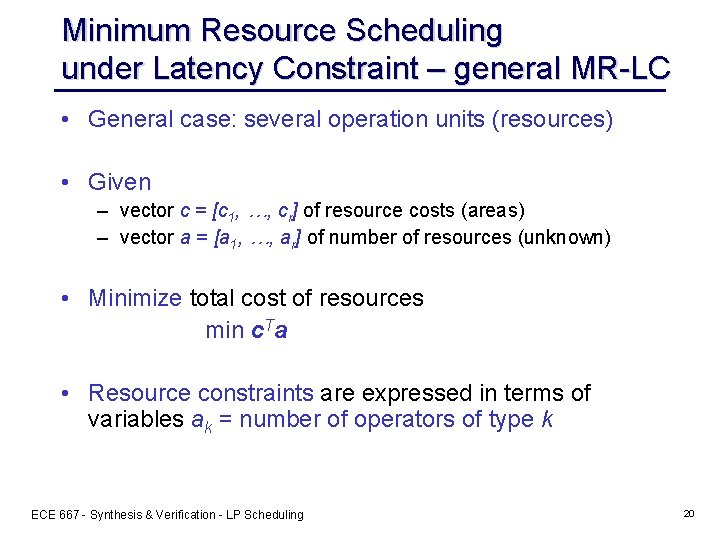

Minimum Resource Scheduling under Latency Constraint – general MR-LC • General case: several operation units (resources) • Given – vector c = [c 1, …, cr] of resource costs (areas) – vector a = [a 1, …, ar] of number of resources (unknown) • Minimize total cost of resources min c. Ta • Resource constraints are expressed in terms of variables ak = number of operators of type k ECE 667 - Synthesis & Verification - LP Scheduling 20

![Example 3 Min Resources under Latency Constraint Let c 5 1 Example 3 – Min. Resources under Latency Constraint • Let c = [5, 1]](https://slidetodoc.com/presentation_image_h/754df173f2a8197899ab95a5f0b1d132/image-21.jpg)

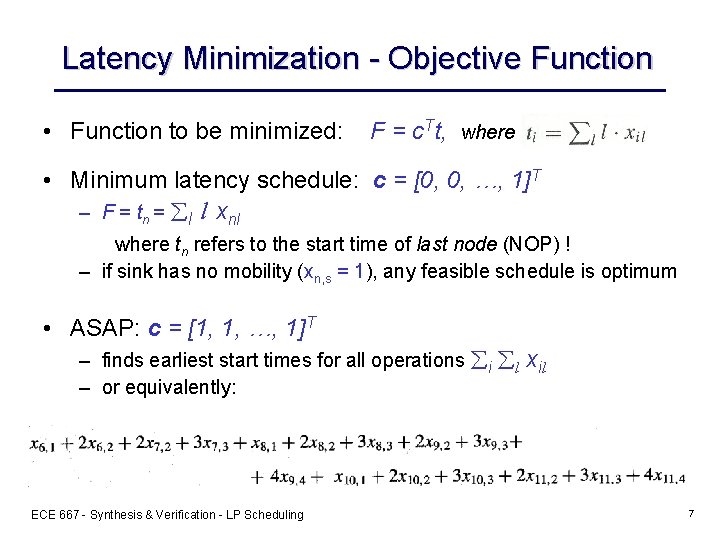

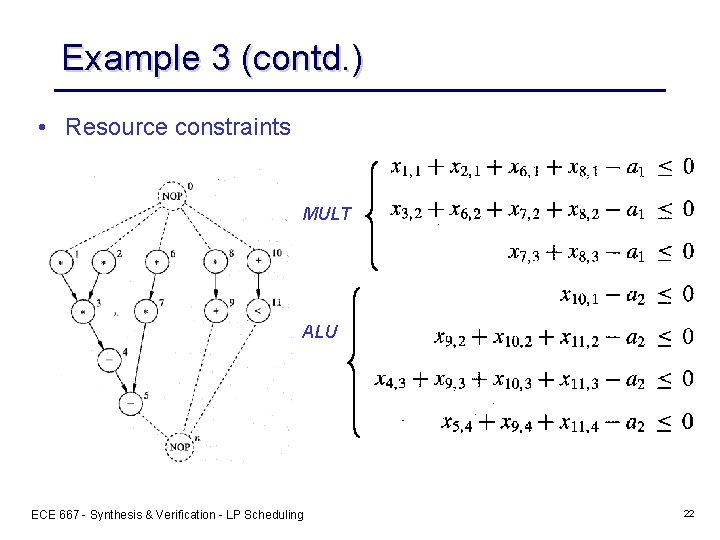

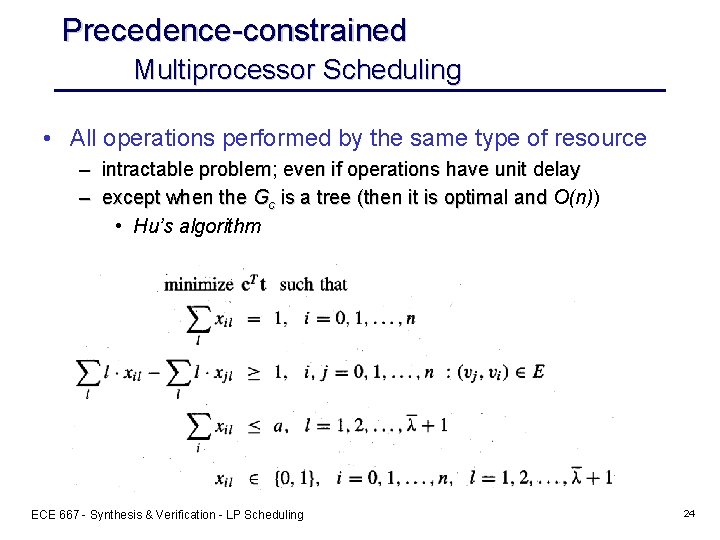

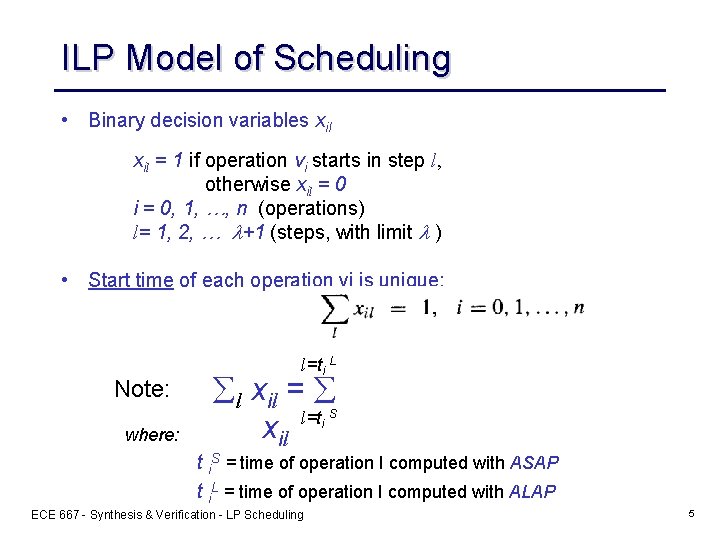

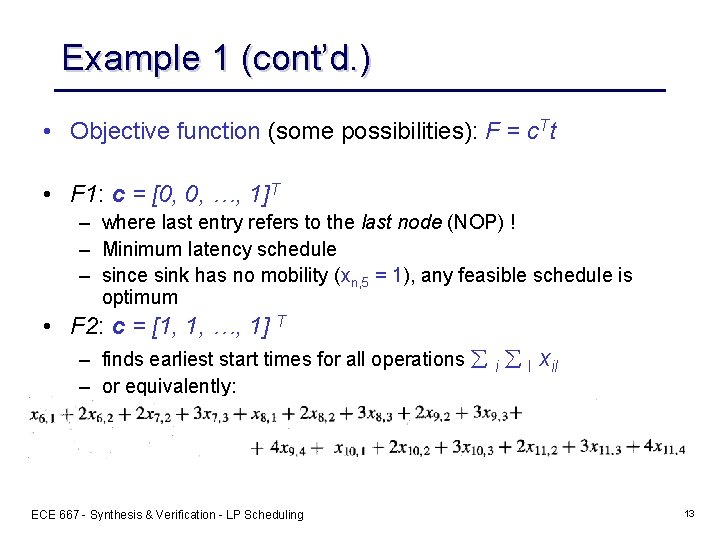

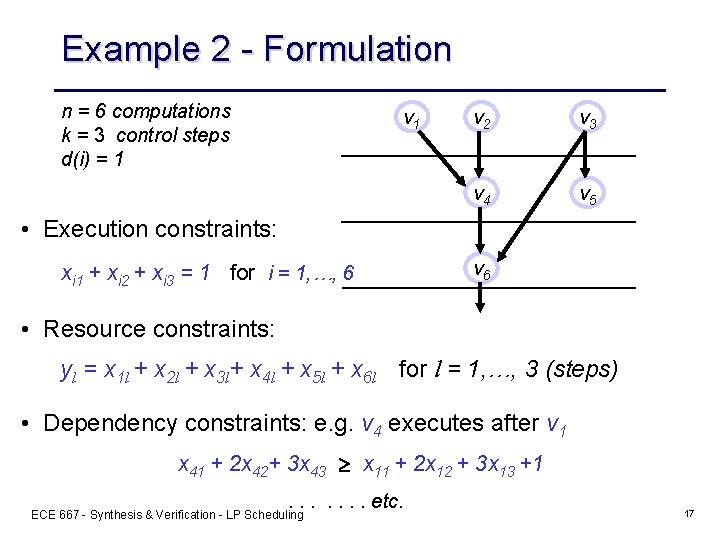

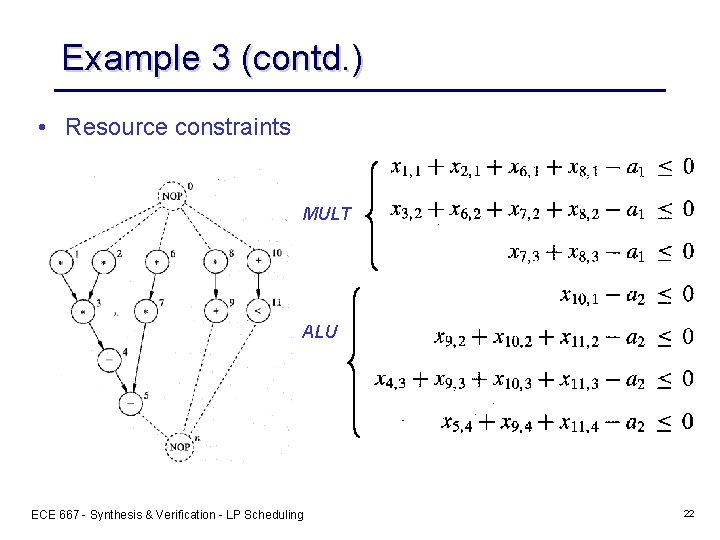

Example 3 – Min. Resources under Latency Constraint • Let c = [5, 1] – MULT costs = 5 units of area, c 1 = 5 – ALU costs = 1 unit of area, c 2 = 1 • Starting time constraint – as before • Sequencing constraints - as before • Resource constraints – similar to ML-RC, but expressed in terms of unknown variables a 1 and a 2 a 1 = number of multipliers a 2 = number of ALUs (add/sub) • Objective function: c. Ta = 5·a 1 + 1·a 2 ECE 667 - Synthesis & Verification - LP Scheduling 21

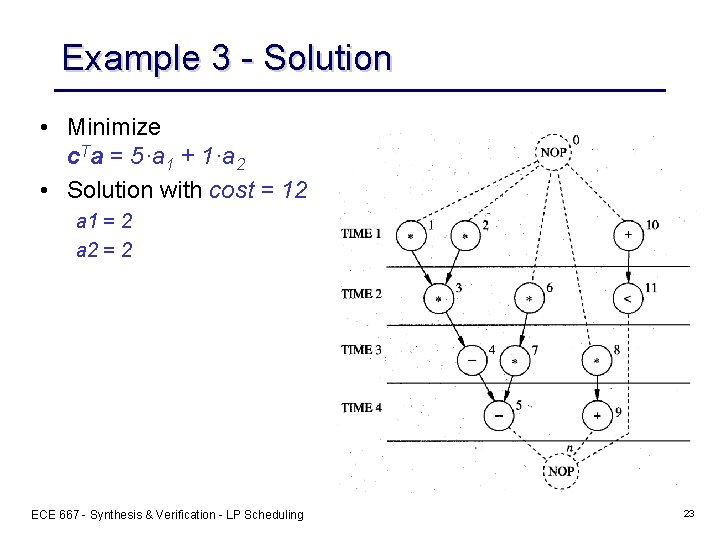

Example 3 (contd. ) • Resource constraints MULT ALU ECE 667 - Synthesis & Verification - LP Scheduling 22

Example 3 - Solution • Minimize c. Ta = 5·a 1 + 1·a 2 • Solution with cost = 12 a 1 = 2 a 2 = 2 ECE 667 - Synthesis & Verification - LP Scheduling 23

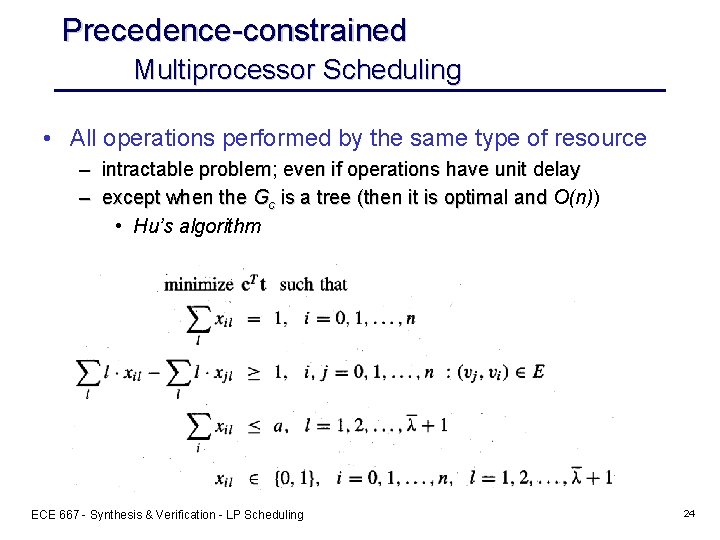

Precedence-constrained Multiprocessor Scheduling • All operations performed by the same type of resource – intractable problem; even if operations have unit delay – except when the Gc is a tree (then it is optimal and O(n)) • Hu’s algorithm ECE 667 - Synthesis & Verification - LP Scheduling 24