ECE 667 Spring 2011 Synthesis and Verification of

- Slides: 27

ECE 667 Spring 2011 Synthesis and Verification of Digital Circuits High-Level (Architectural) Synthesis 1

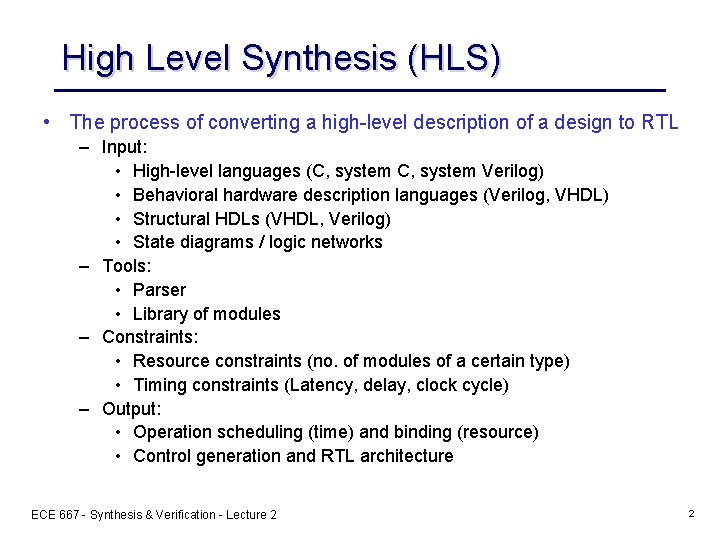

High Level Synthesis (HLS) • The process of converting a high-level description of a design to RTL – Input: • High-level languages (C, system Verilog) • Behavioral hardware description languages (Verilog, VHDL) • Structural HDLs (VHDL, Verilog) • State diagrams / logic networks – Tools: • Parser • Library of modules – Constraints: • Resource constraints (no. of modules of a certain type) • Timing constraints (Latency, delay, clock cycle) – Output: • Operation scheduling (time) and binding (resource) • Control generation and RTL architecture ECE 667 - Synthesis & Verification - Lecture 2 2

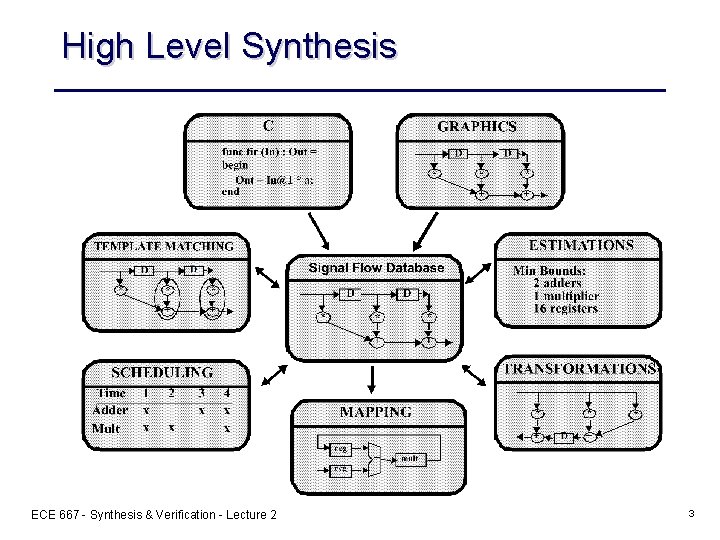

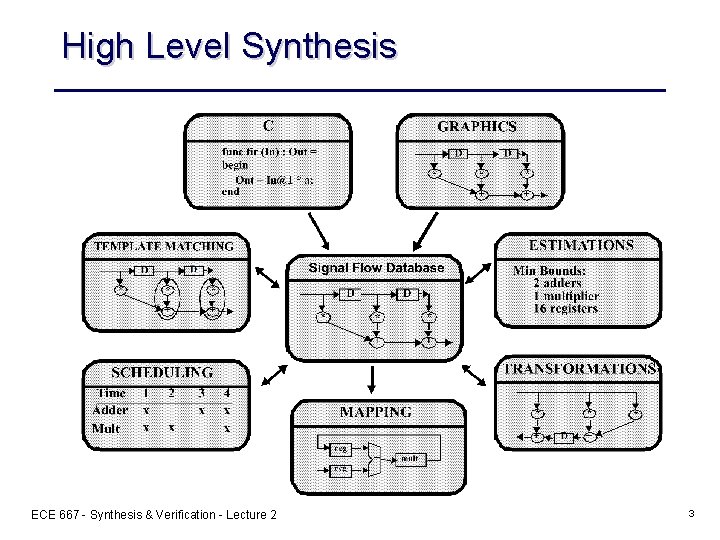

High Level Synthesis ECE 667 - Synthesis & Verification - Lecture 2 3

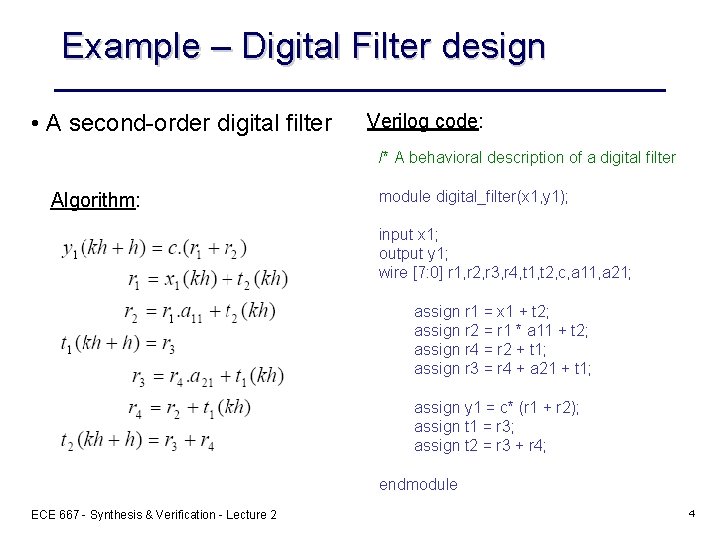

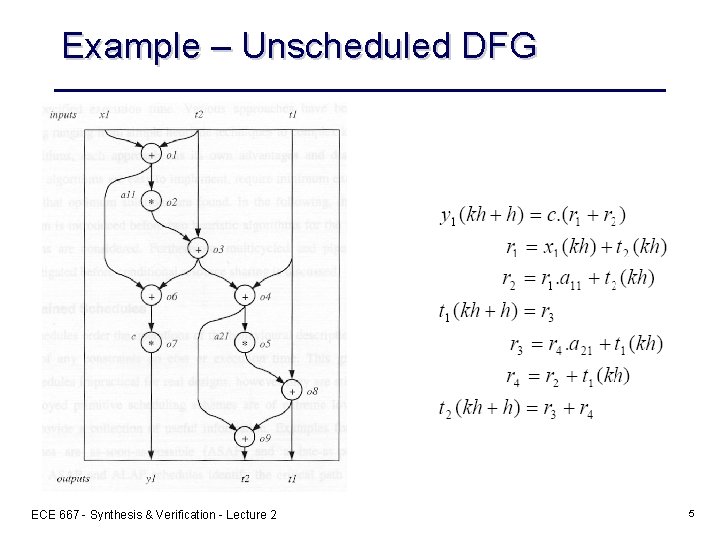

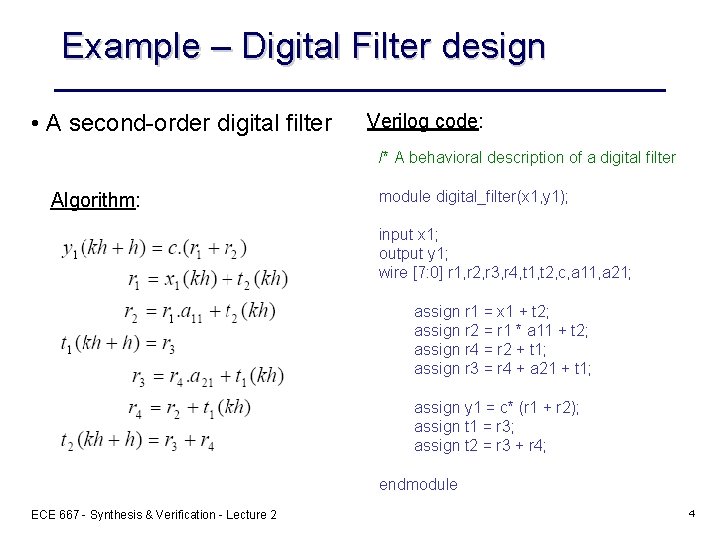

Example – Digital Filter design • A second-order digital filter Verilog code: /* A behavioral description of a digital filter Algorithm: module digital_filter(x 1, y 1); input x 1; output y 1; wire [7: 0] r 1, r 2, r 3, r 4, t 1, t 2, c, a 11, a 21; assign r 1 = x 1 + t 2; assign r 2 = r 1 * a 11 + t 2; assign r 4 = r 2 + t 1; assign r 3 = r 4 + a 21 + t 1; assign y 1 = c* (r 1 + r 2); assign t 1 = r 3; assign t 2 = r 3 + r 4; endmodule ECE 667 - Synthesis & Verification - Lecture 2 4

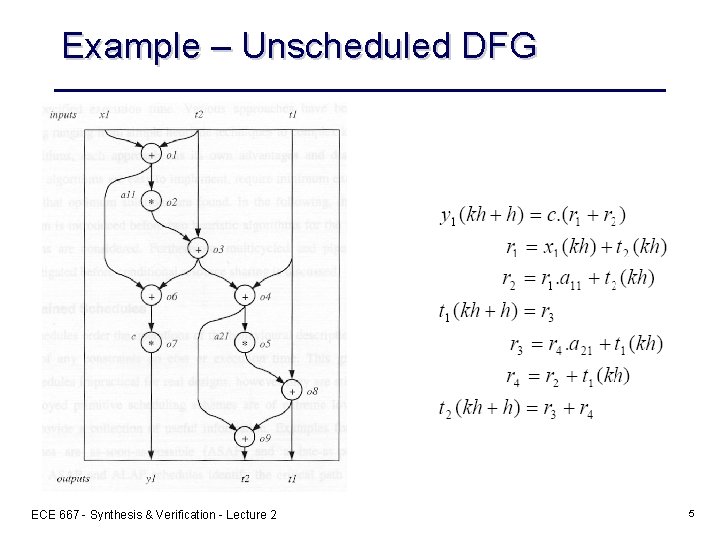

Example – Unscheduled DFG ECE 667 - Synthesis & Verification - Lecture 2 5

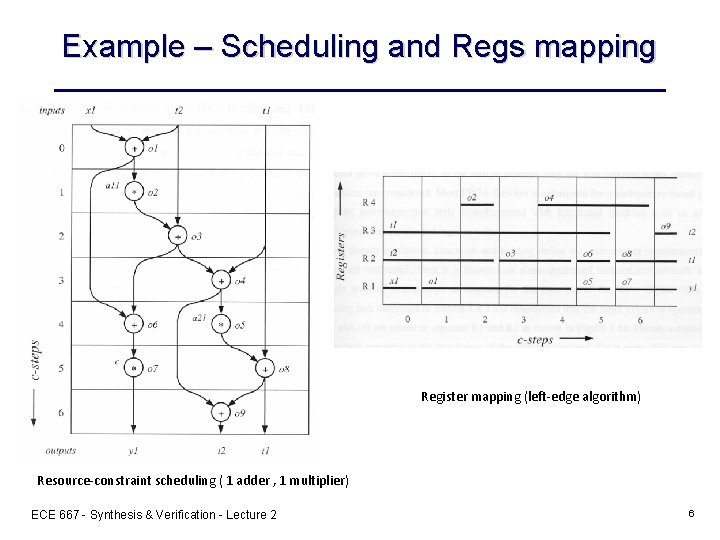

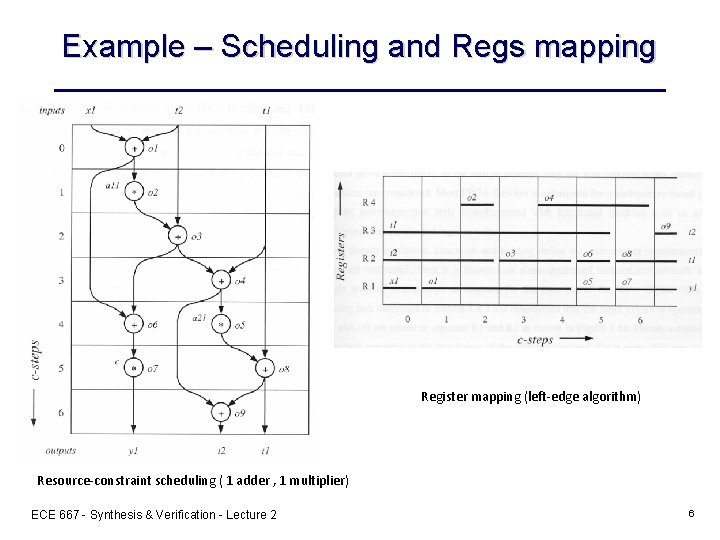

Example – Scheduling and Regs mapping Register mapping (left-edge algorithm) Resource-constraint scheduling ( 1 adder , 1 multiplier) ECE 667 - Synthesis & Verification - Lecture 2 6

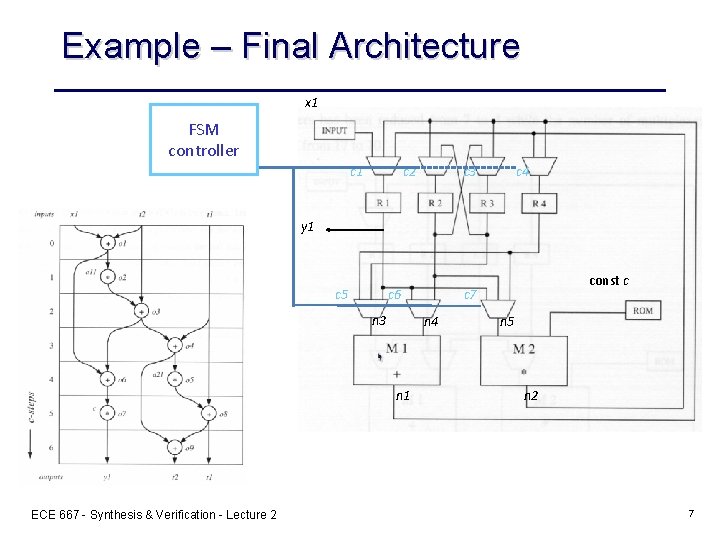

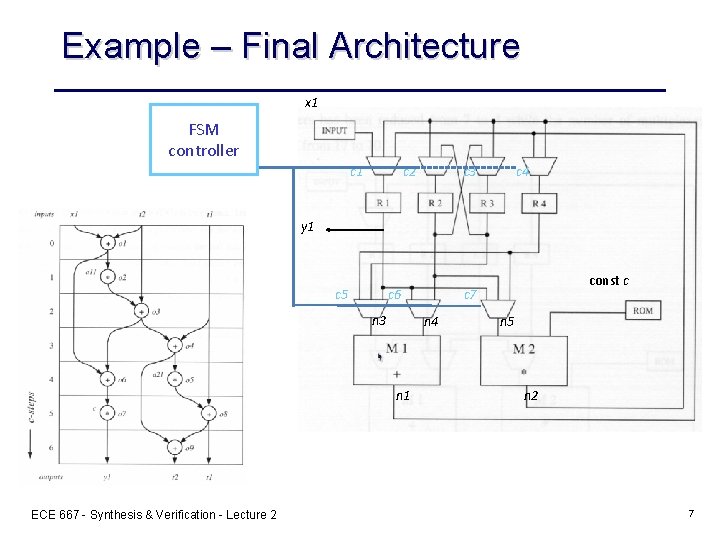

Example – Final Architecture x 1 FSM controller c 1 c 2 c 3 c 4 y 1 c 5 c 6 n 3 n 4 n 1 ECE 667 - Synthesis & Verification - Lecture 2 const c c 7 n 5 n 2 7

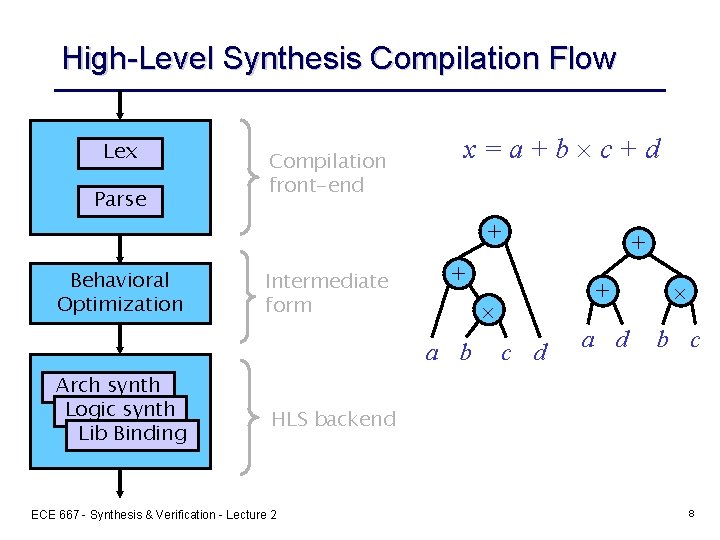

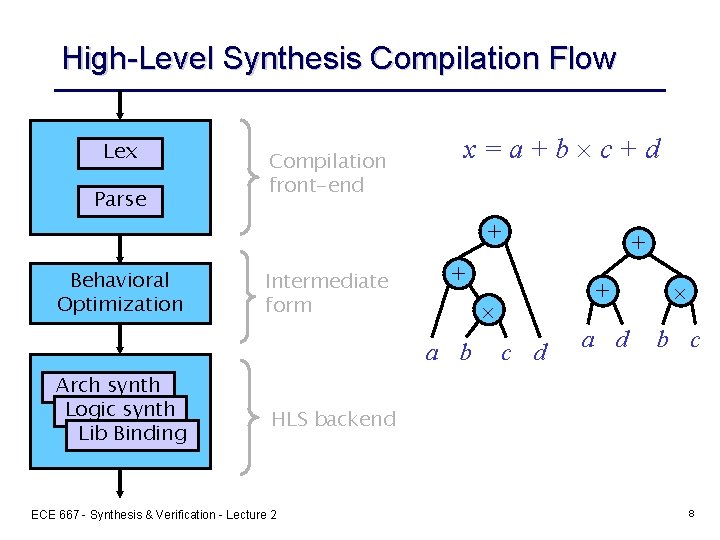

High-Level Synthesis Compilation Flow Lex Parse Behavioral Optimization Compilation front-end x=a+b c+d + Intermediate form + a b Arch synth Logic synth Lib Binding c d + + a d b c HLS backend ECE 667 - Synthesis & Verification - Lecture 2 8

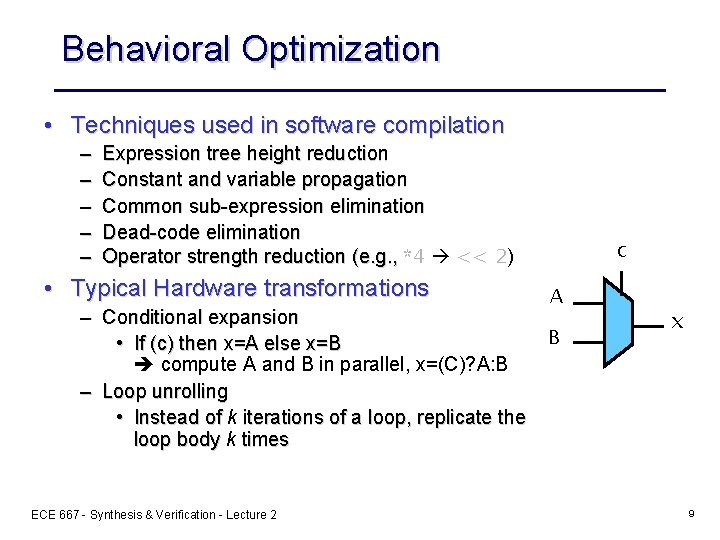

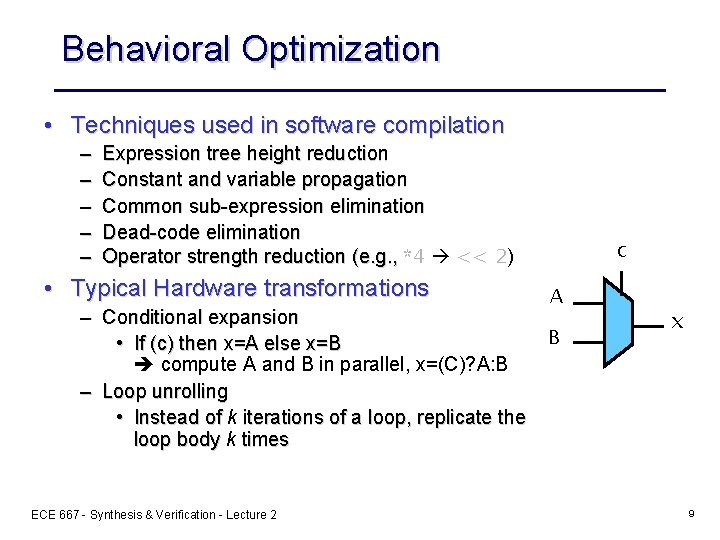

Behavioral Optimization • Techniques used in software compilation – – – Expression tree height reduction Constant and variable propagation Common sub-expression elimination Dead-code elimination Operator strength reduction (e. g. , *4 << 2) • Typical Hardware transformations – Conditional expansion • If (c) then x=A else x=B compute A and B in parallel, x=(C)? A: B – Loop unrolling • Instead of k iterations of a loop, replicate the loop body k times ECE 667 - Synthesis & Verification - Lecture 2 c A B x 9

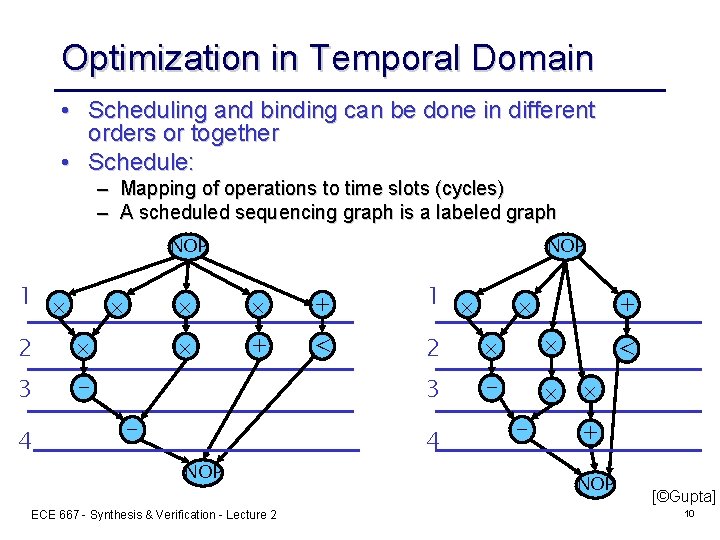

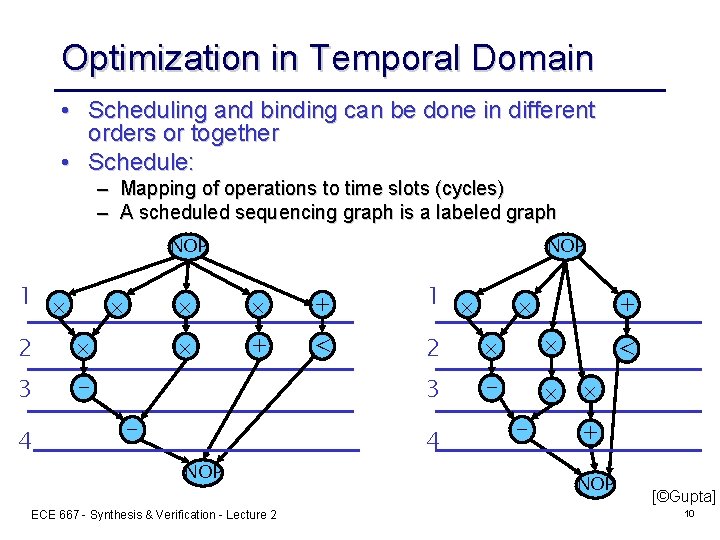

Optimization in Temporal Domain • Scheduling and binding can be done in different orders or together • Schedule: – Mapping of operations to time slots (cycles) – A scheduled sequencing graph is a labeled graph NOP 1 2 3 - 4 NOP + 1 + < 2 3 - NOP ECE 667 - Synthesis & Verification - Lecture 2 4 + - < + NOP [©Gupta] 10

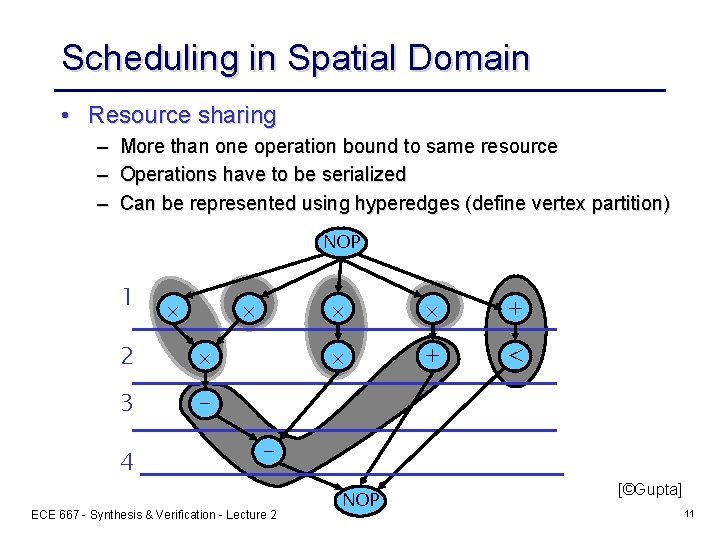

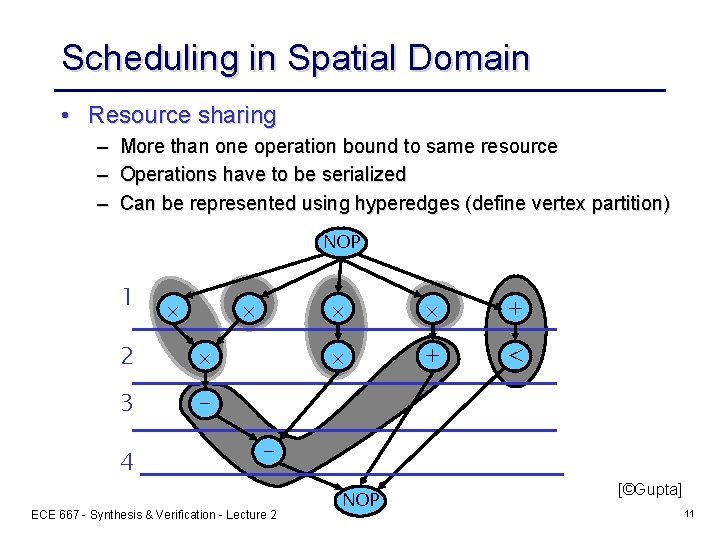

Scheduling in Spatial Domain • Resource sharing – More than one operation bound to same resource – Operations have to be serialized – Can be represented using hyperedges (define vertex partition) NOP 1 2 3 - 4 + + < - ECE 667 - Synthesis & Verification - Lecture 2 NOP [©Gupta] 11

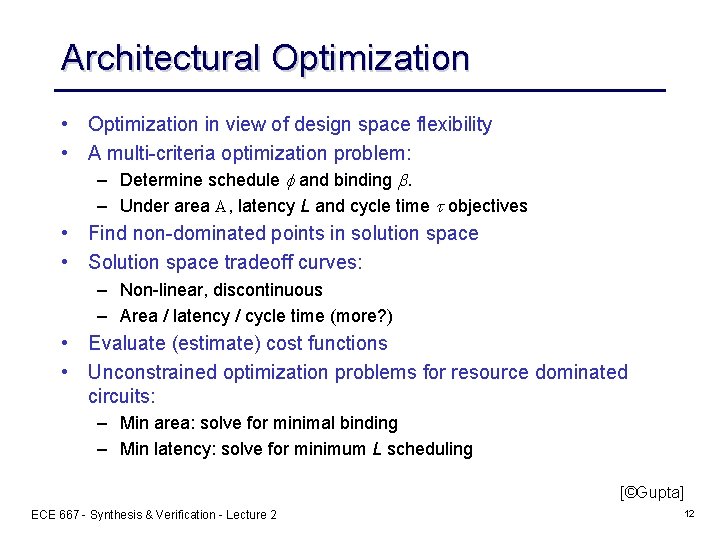

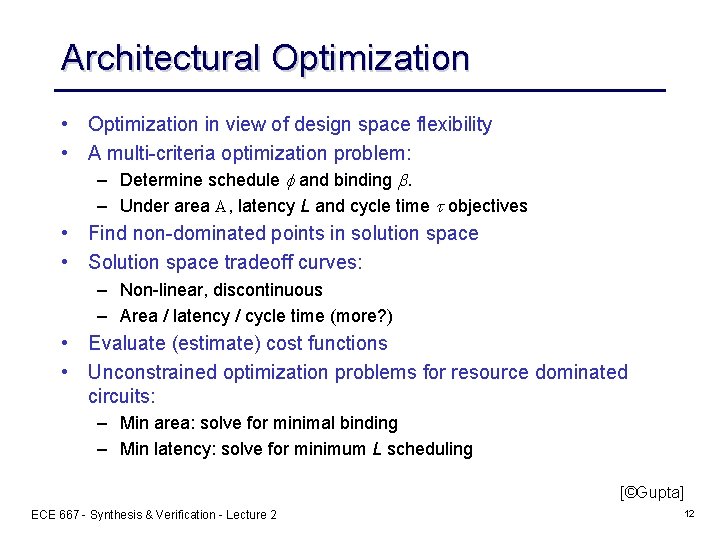

Architectural Optimization • Optimization in view of design space flexibility • A multi-criteria optimization problem: – Determine schedule f and binding b. – Under area A, latency L and cycle time t objectives • Find non-dominated points in solution space • Solution space tradeoff curves: – Non-linear, discontinuous – Area / latency / cycle time (more? ) • Evaluate (estimate) cost functions • Unconstrained optimization problems for resource dominated circuits: – Min area: solve for minimal binding – Min latency: solve for minimum L scheduling [©Gupta] ECE 667 - Synthesis & Verification - Lecture 2 12

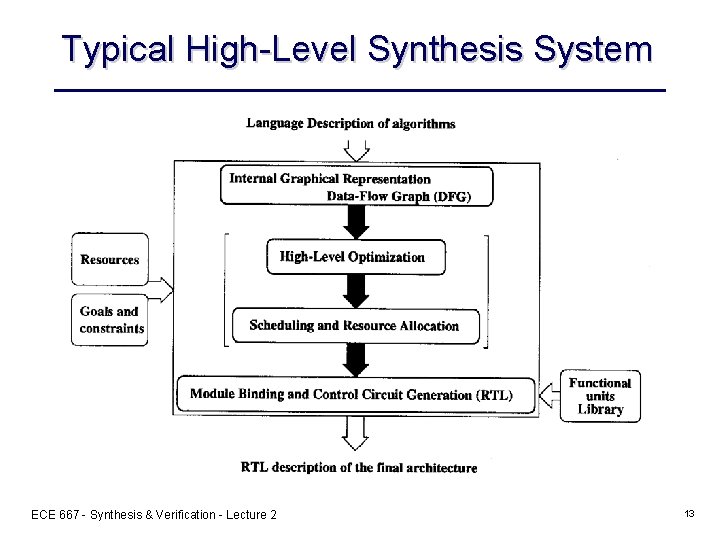

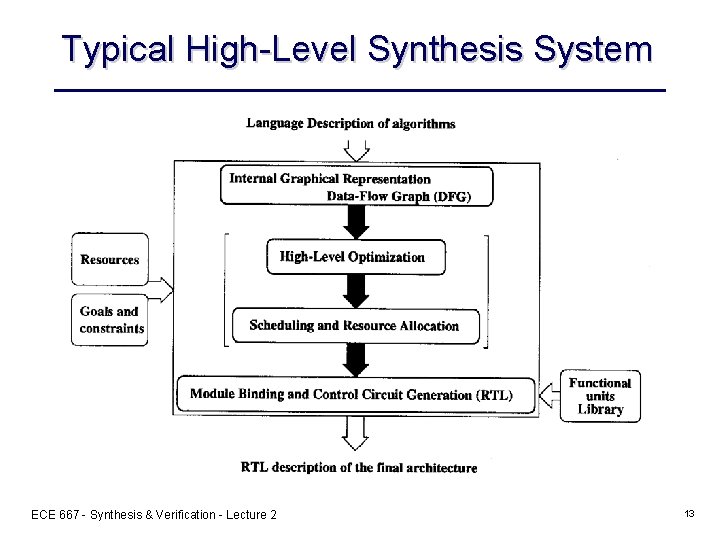

Typical High-Level Synthesis System ECE 667 - Synthesis & Verification - Lecture 2 13

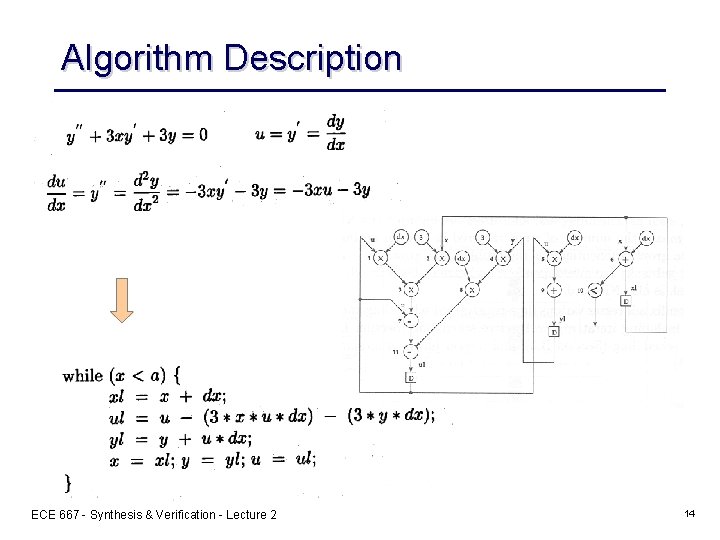

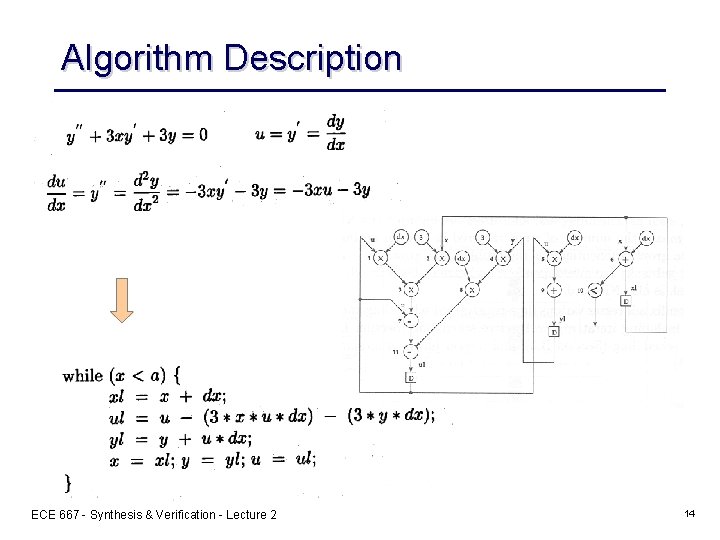

Algorithm Description ECE 667 - Synthesis & Verification - Lecture 2 14

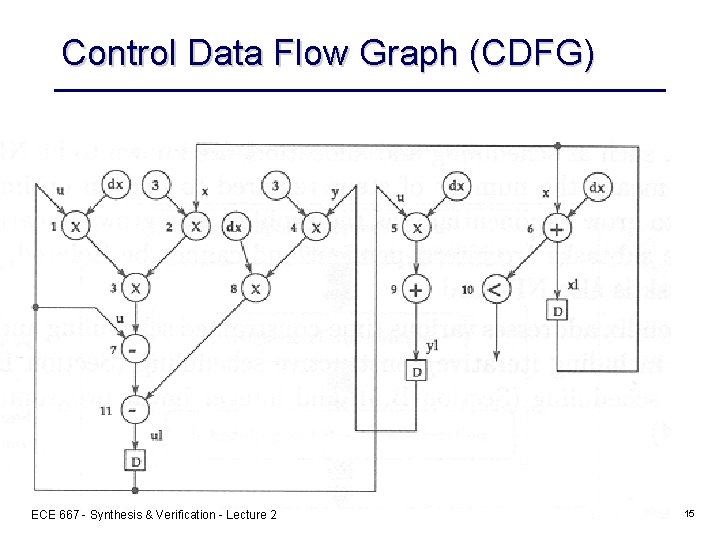

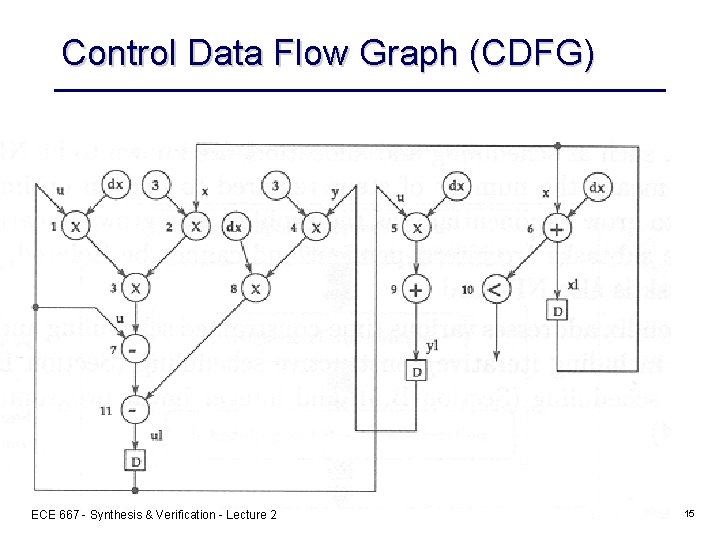

Control Data Flow Graph (CDFG) ECE 667 - Synthesis & Verification - Lecture 2 15

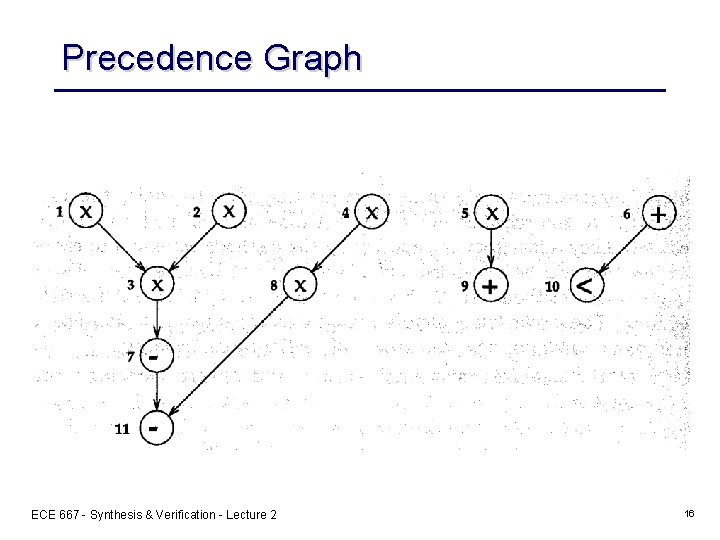

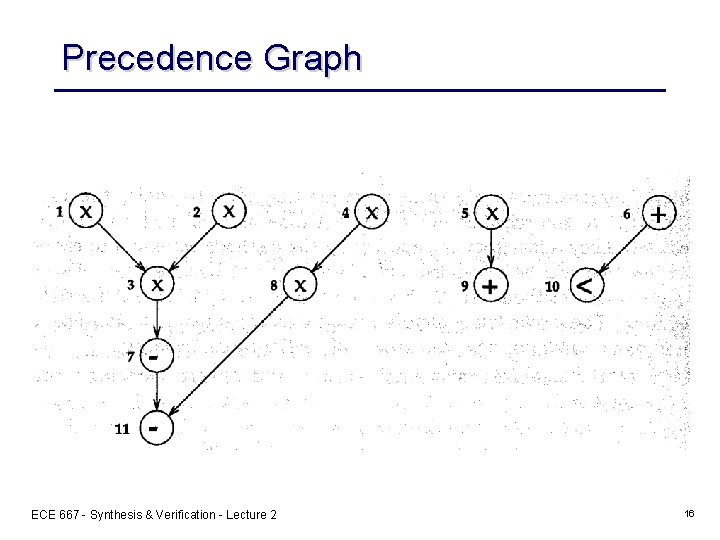

Precedence Graph ECE 667 - Synthesis & Verification - Lecture 2 16

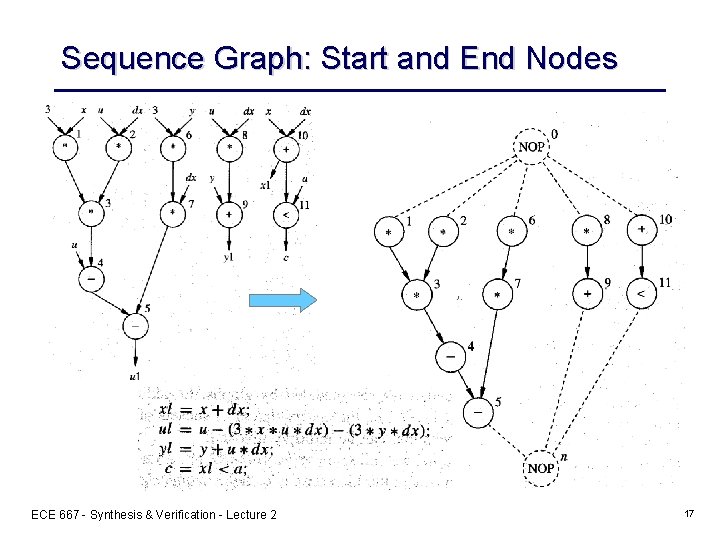

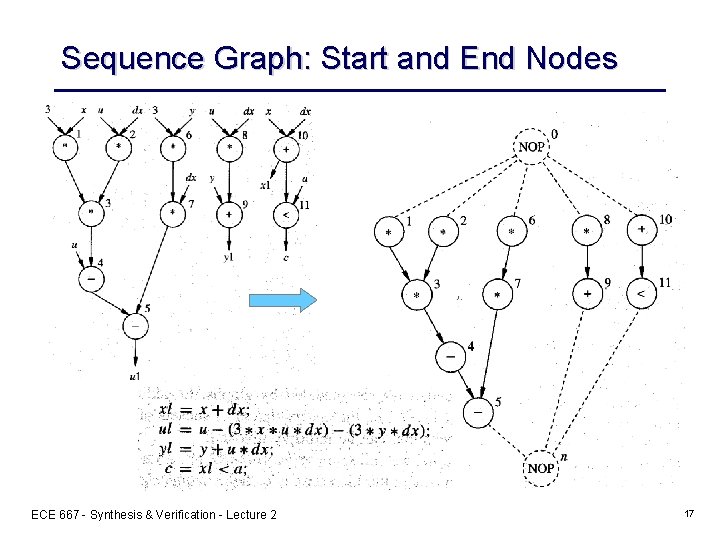

Sequence Graph: Start and End Nodes ECE 667 - Synthesis & Verification - Lecture 2 17

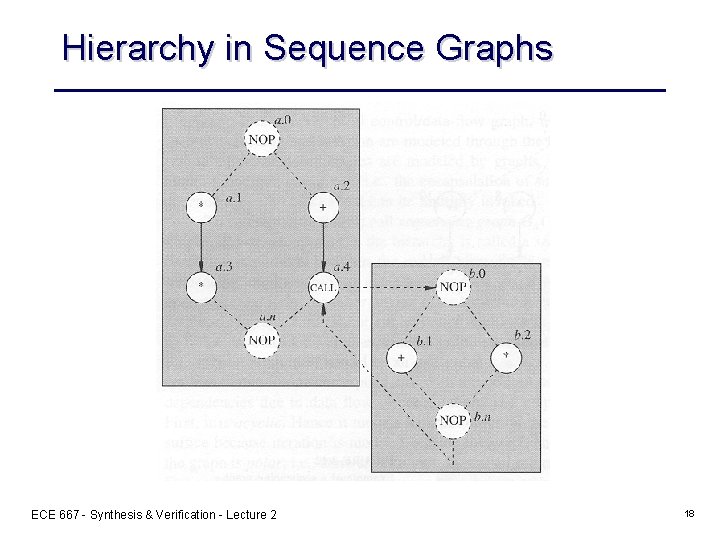

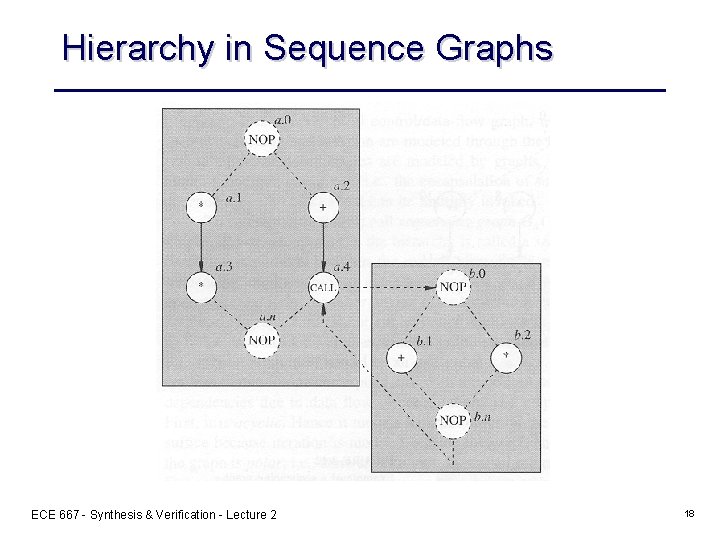

Hierarchy in Sequence Graphs ECE 667 - Synthesis & Verification - Lecture 2 18

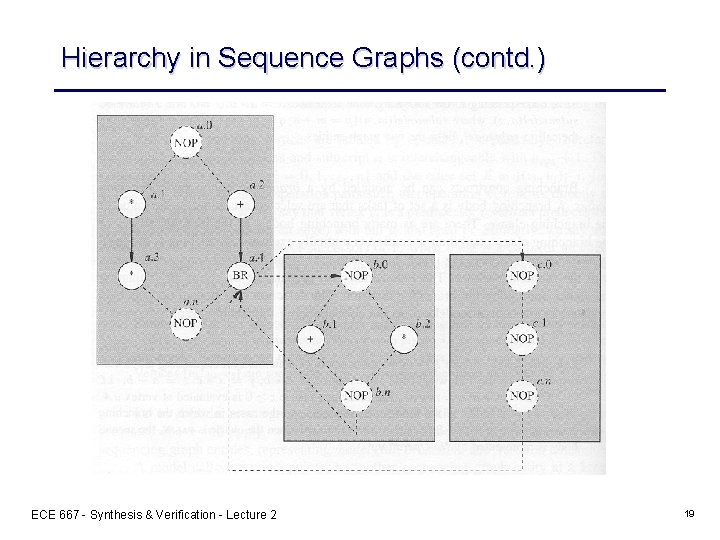

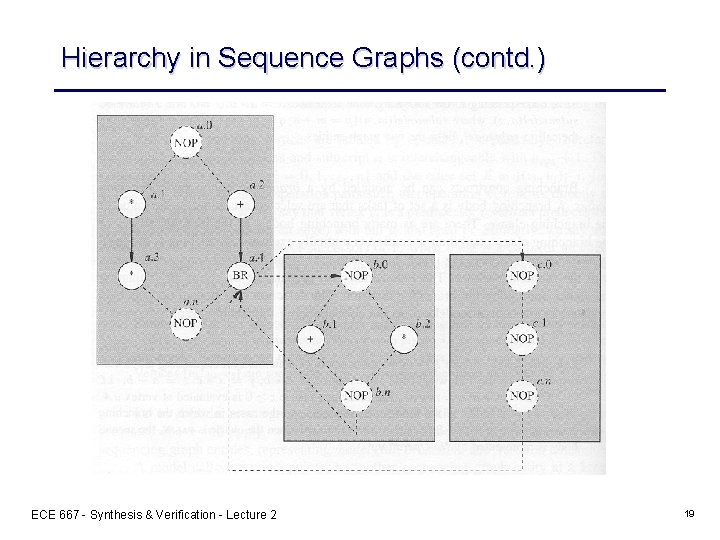

Hierarchy in Sequence Graphs (contd. ) ECE 667 - Synthesis & Verification - Lecture 2 19

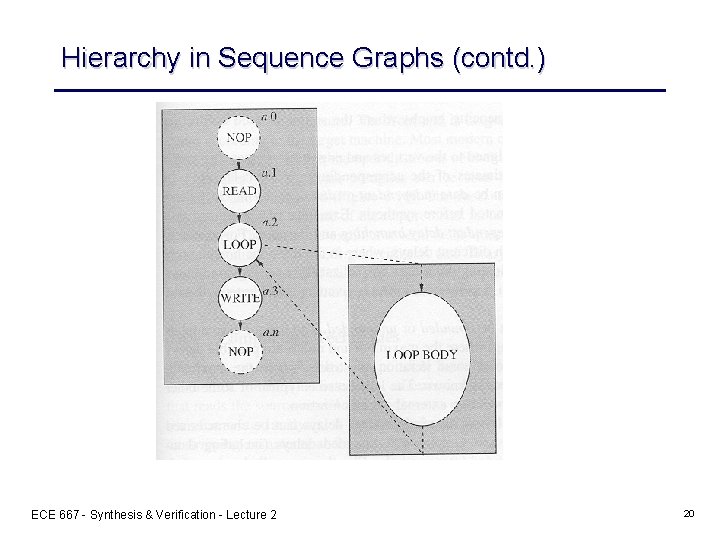

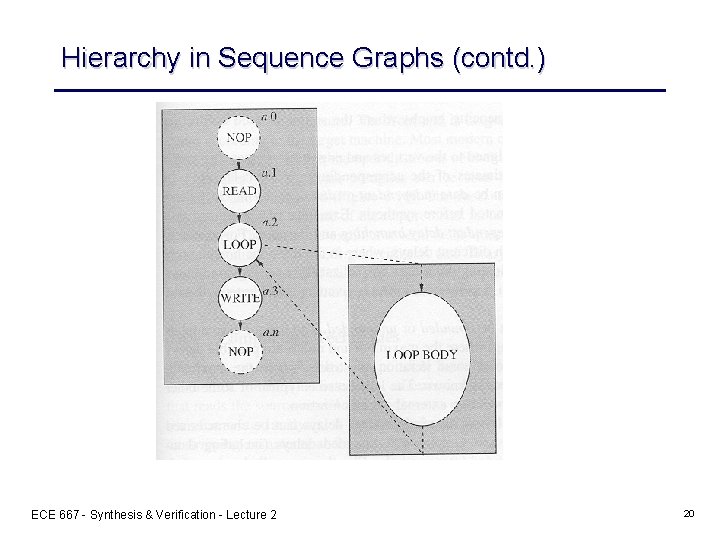

Hierarchy in Sequence Graphs (contd. ) ECE 667 - Synthesis & Verification - Lecture 2 20

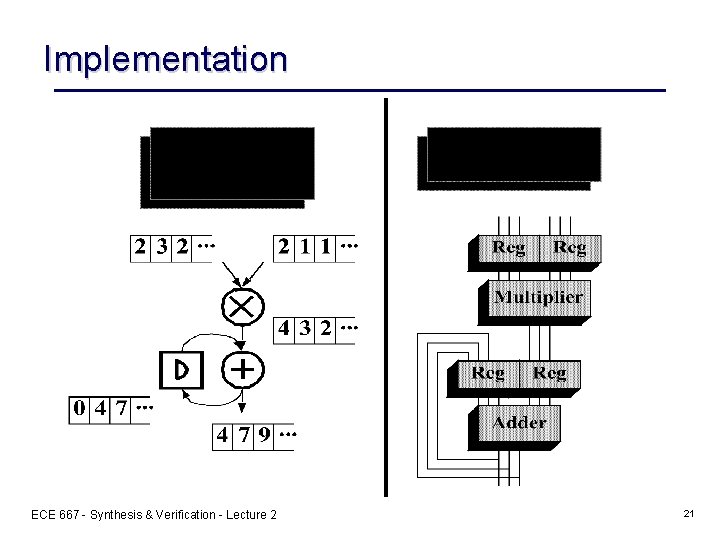

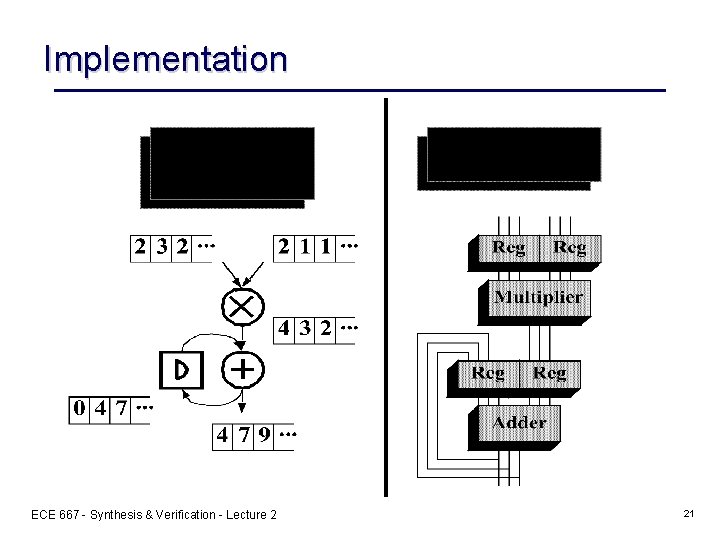

Implementation ECE 667 - Synthesis & Verification - Lecture 2 21

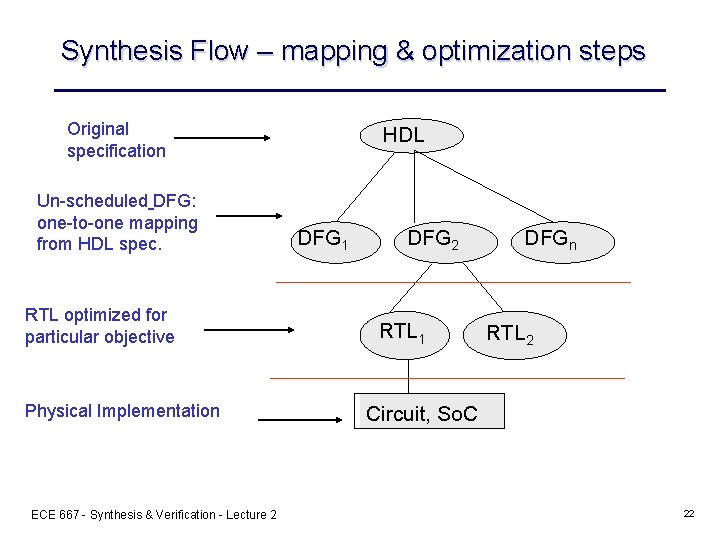

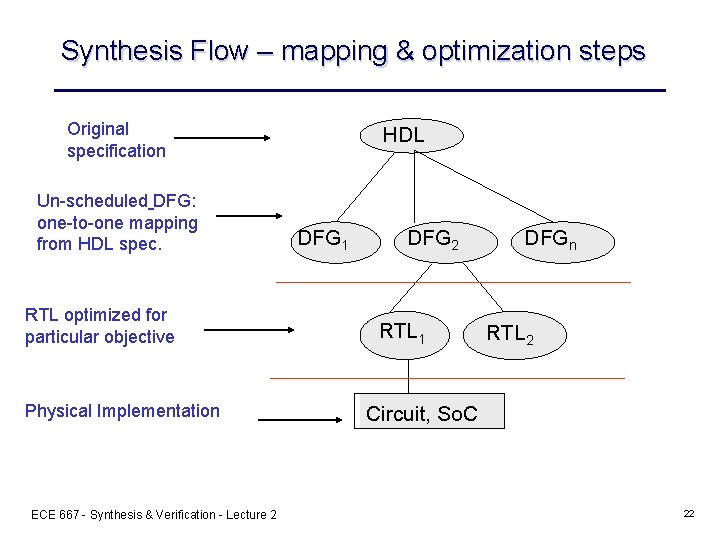

Synthesis Flow – mapping & optimization steps Original specification Un-scheduled DFG: one-to-one mapping from HDL spec. RTL optimized for particular objective Physical Implementation ECE 667 - Synthesis & Verification - Lecture 2 HDL DFG 1 DFG 2 RTL 1 DFGn RTL 2 Circuit, So. C 22

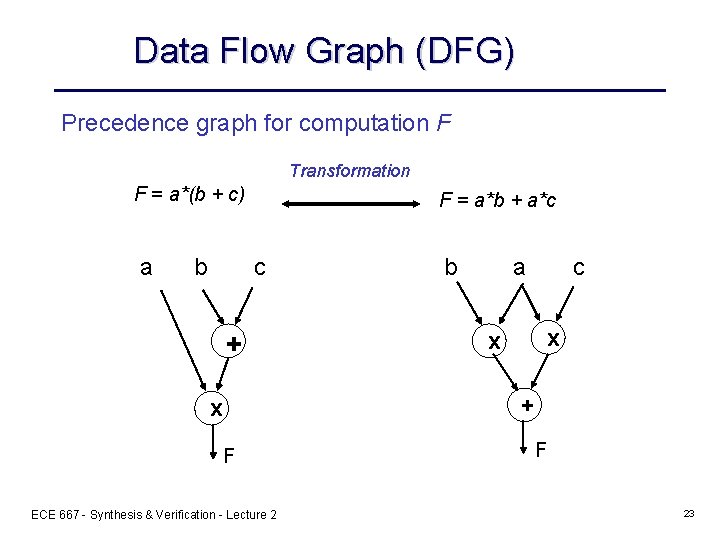

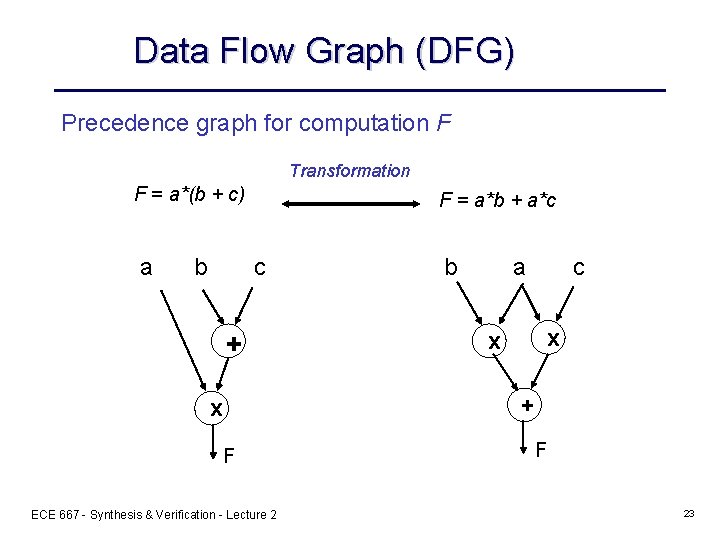

Data Flow Graph (DFG) Precedence graph for computation F Transformation F = a*(b + c) a b F = a*b + a*c c + b a c x x + x F ECE 667 - Synthesis & Verification - Lecture 2 F 23

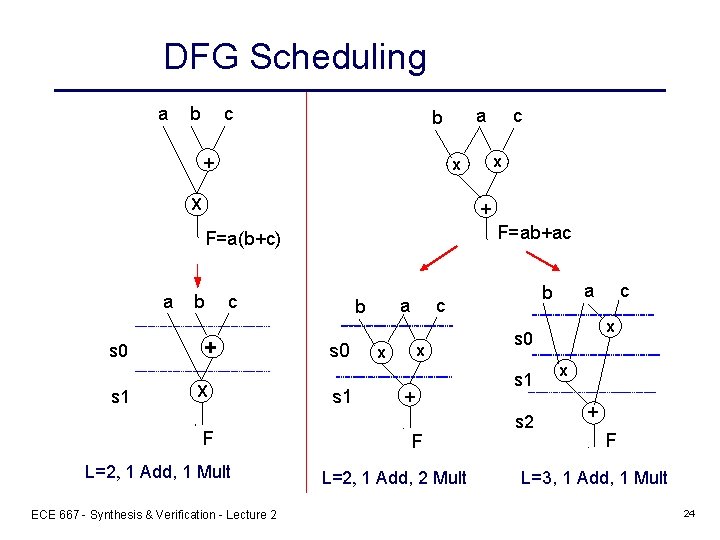

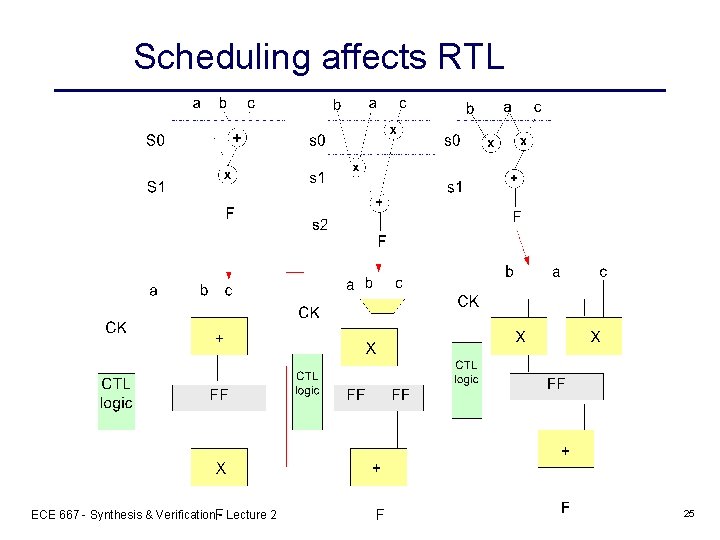

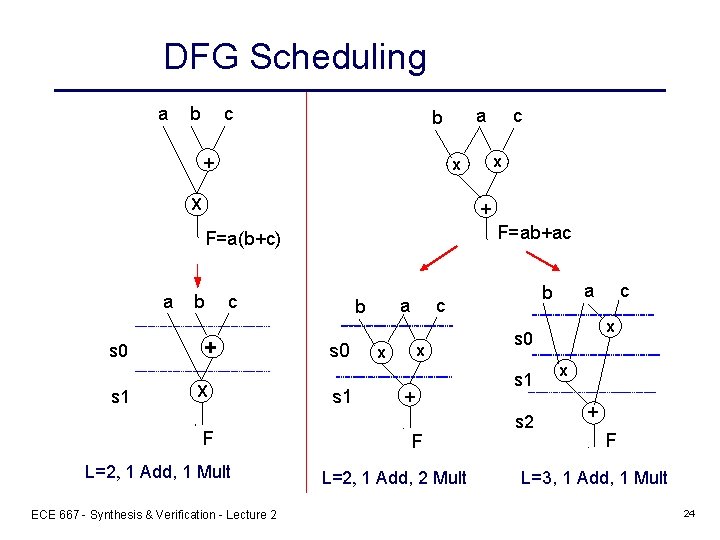

DFG Scheduling a b c a b + + F=ab+ac F=a(b+c) a s 0 s 1 x x X c b c + X F L=2, 1 Add, 1 Mult ECE 667 - Synthesis & Verification - Lecture 2 a b s 0 s 1 x x + F L=2, 1 Add, 2 Mult a b c x s 0 s 1 s 2 c x + F L=3, 1 Add, 1 Mult 24

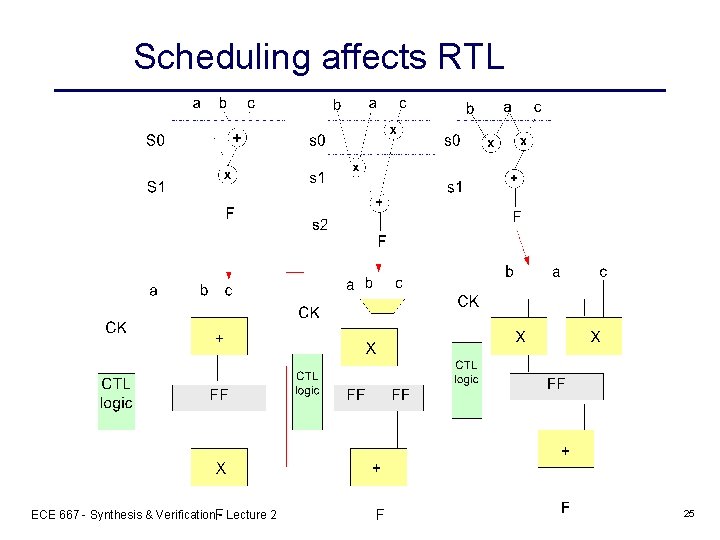

Scheduling affects RTL ECE 667 - Synthesis & Verification - Lecture 2 25

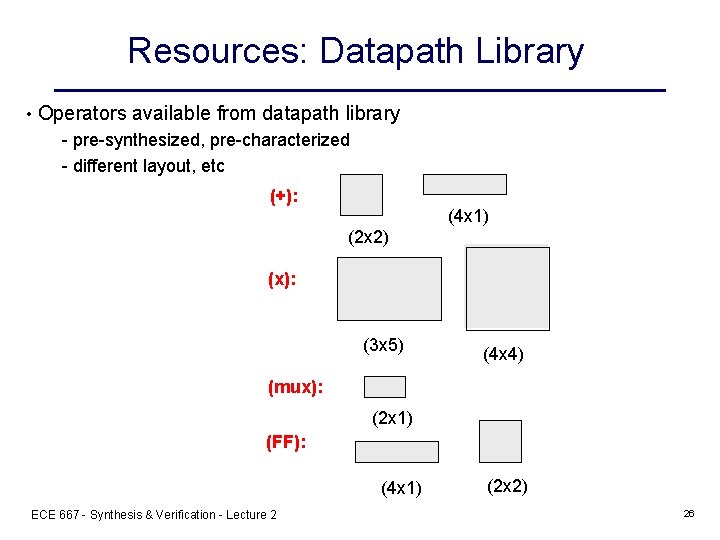

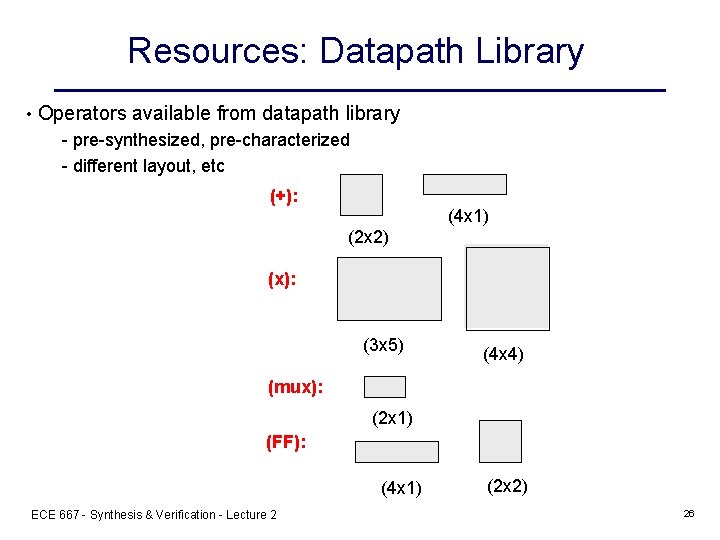

Resources: Datapath Library • Operators available from datapath library - pre-synthesized, pre-characterized - different layout, etc (+): (4 x 1) (2 x 2) (x): (3 x 5) (4 x 4) (mux): (2 x 1) (FF): (4 x 1) ECE 667 - Synthesis & Verification - Lecture 2 (2 x 2) 26

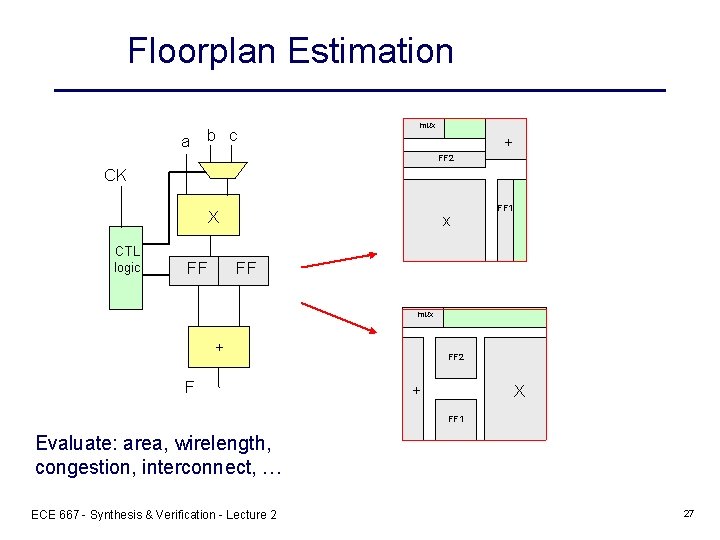

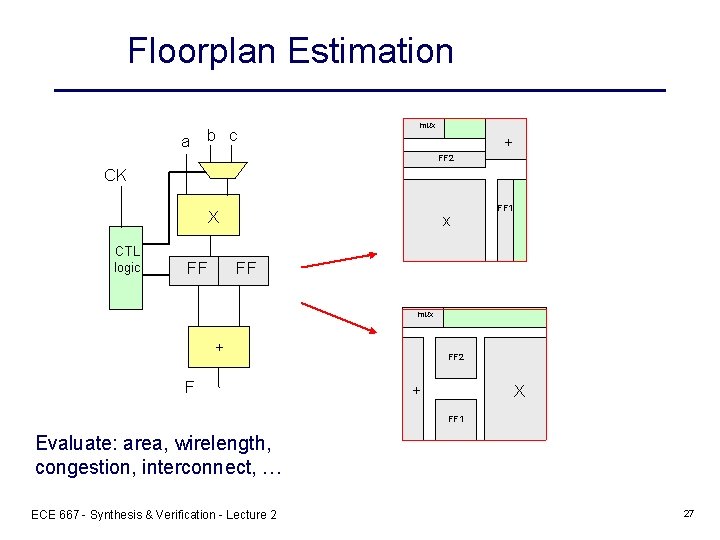

Floorplan Estimation a b c mux + FF 2 CK X CTL logic FF x FF 1 FF mux + F FF 2 + X FF 1 Evaluate: area, wirelength, congestion, interconnect, … ECE 667 - Synthesis & Verification - Lecture 2 27