ECE 667 Spring 2007 Synthesis and Verification of

- Slides: 20

ECE 667 Spring 2007 Synthesis and Verification of Digital Circuits Design Implementation 1

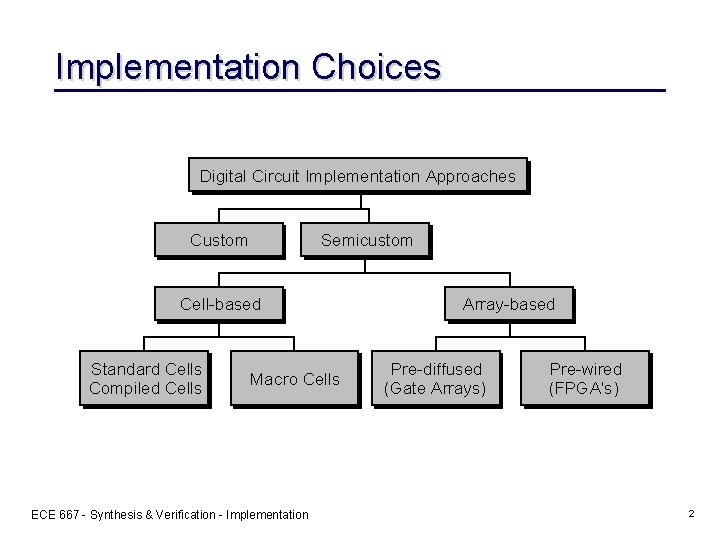

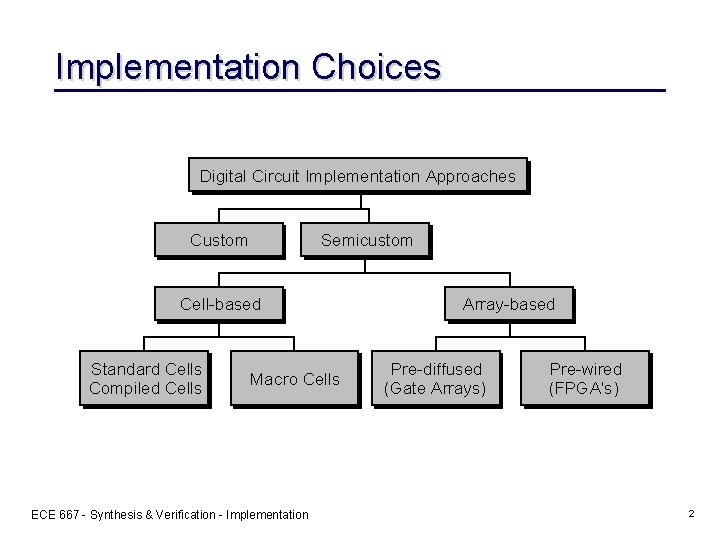

Implementation Choices Digital Circuit Implementation Approaches Custom Semicustom Cell-based Standard Cells Compiled Cells Macro Cells ECE 667 - Synthesis & Verification - Implementation Array-based Pre-diffused (Gate Arrays) Pre-wired (FPGA's) 2

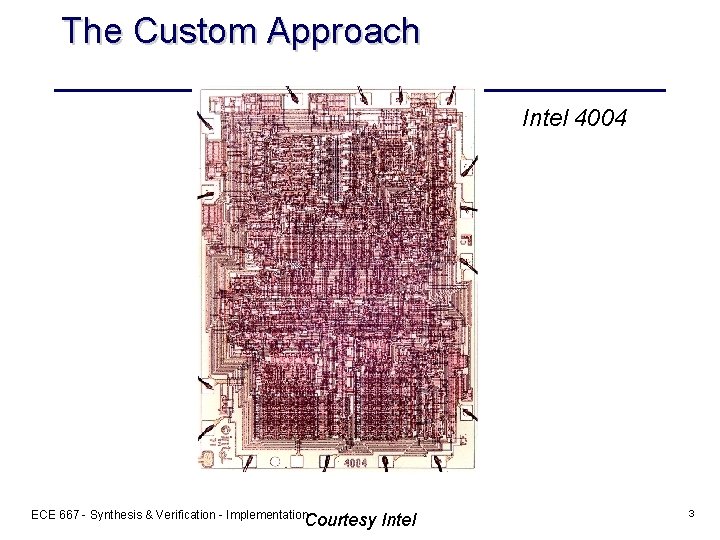

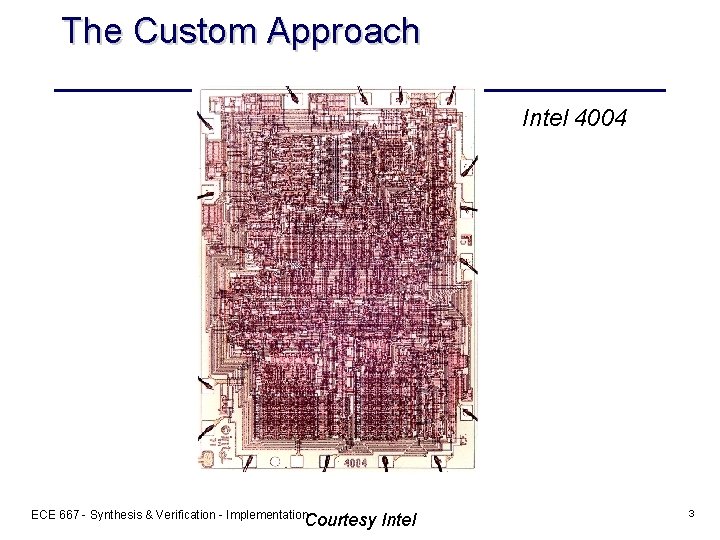

The Custom Approach Intel 4004 ECE 667 - Synthesis & Verification - Implementation Courtesy Intel 3

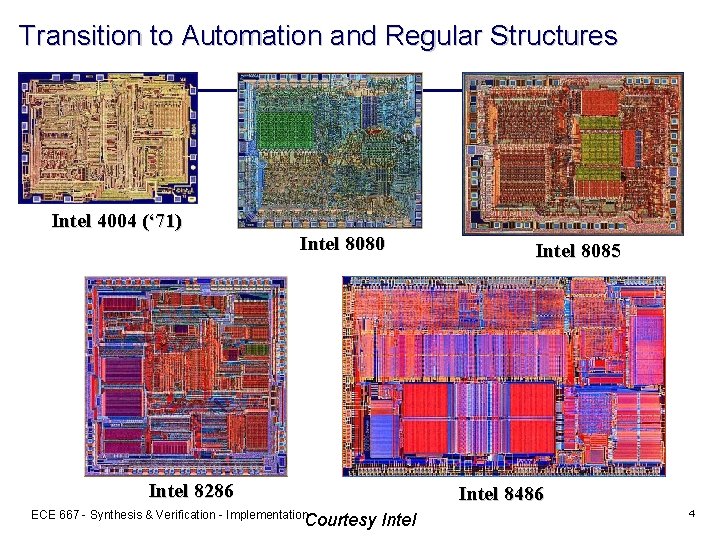

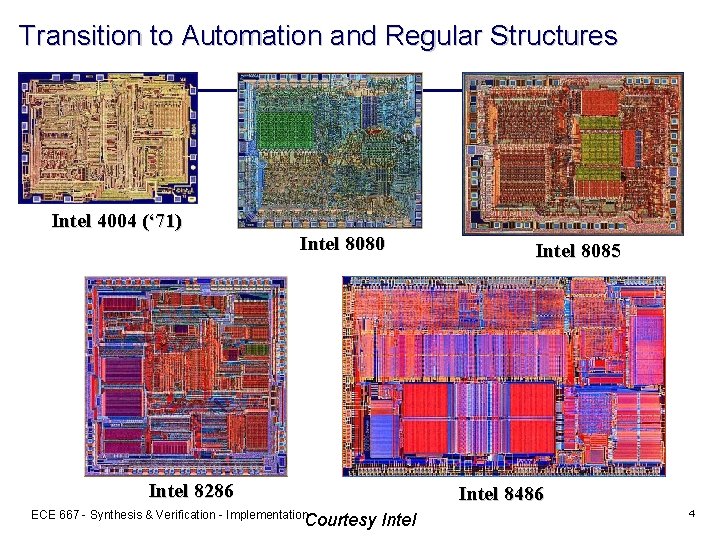

Transition to Automation and Regular Structures Intel 4004 (‘ 71) Intel 8080 Intel 8286 Intel 8085 Intel 8486 ECE 667 - Synthesis & Verification - Implementation Courtesy Intel 4

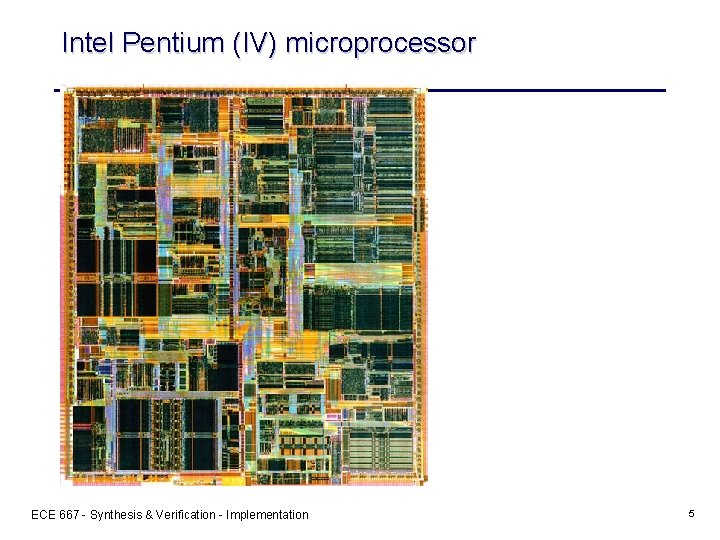

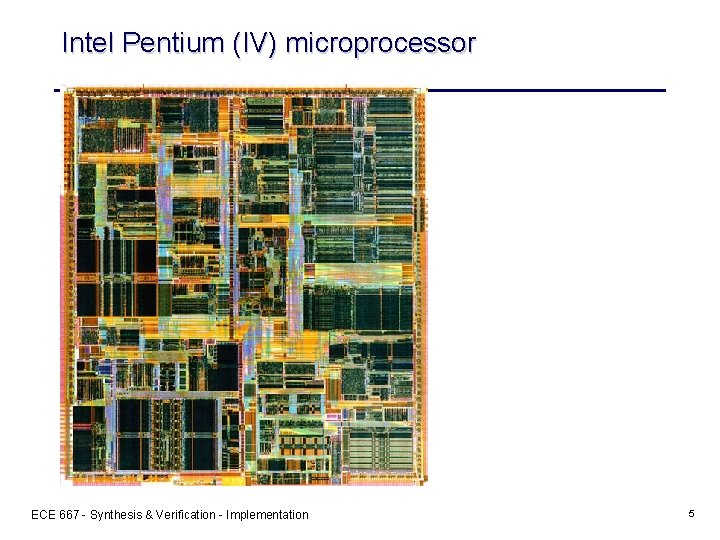

Intel Pentium (IV) microprocessor ECE 667 - Synthesis & Verification - Implementation 5

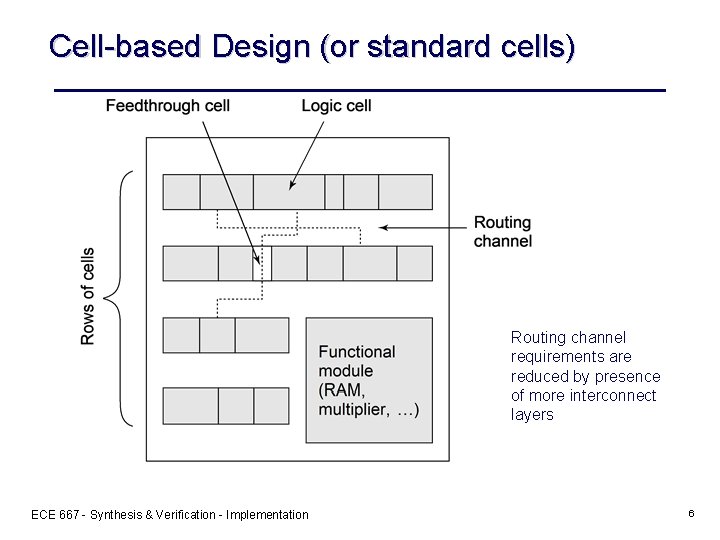

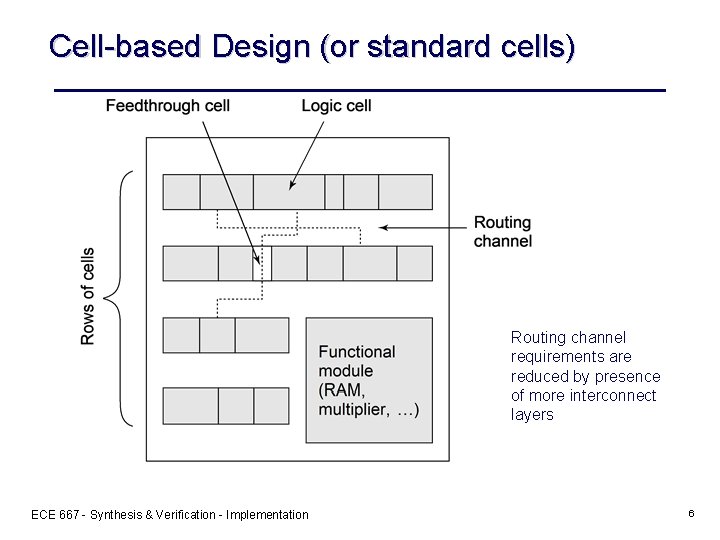

Cell-based Design (or standard cells) Routing channel requirements are reduced by presence of more interconnect layers ECE 667 - Synthesis & Verification - Implementation 6

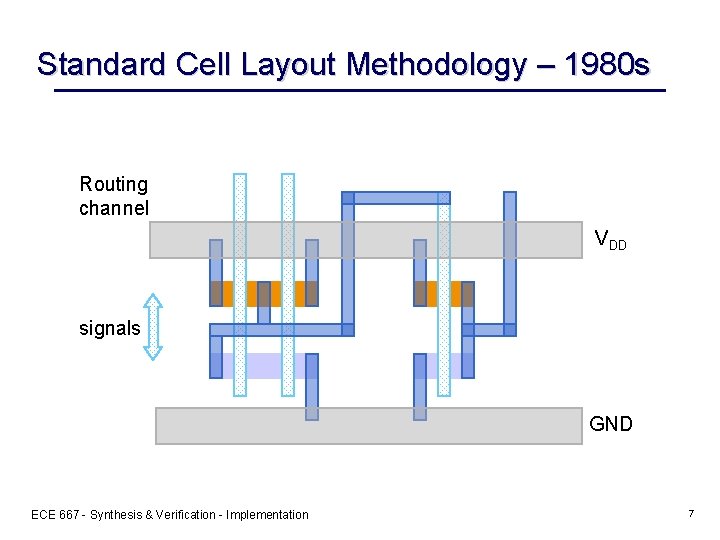

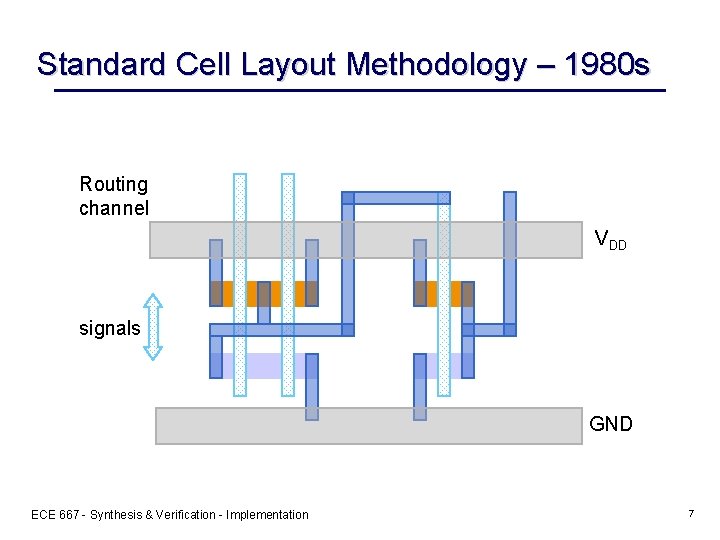

Standard Cell Layout Methodology – 1980 s Routing channel VDD signals GND ECE 667 - Synthesis & Verification - Implementation 7

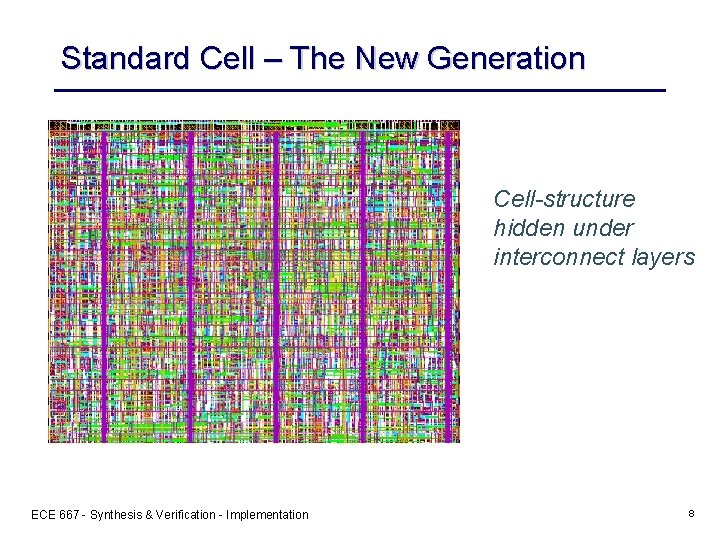

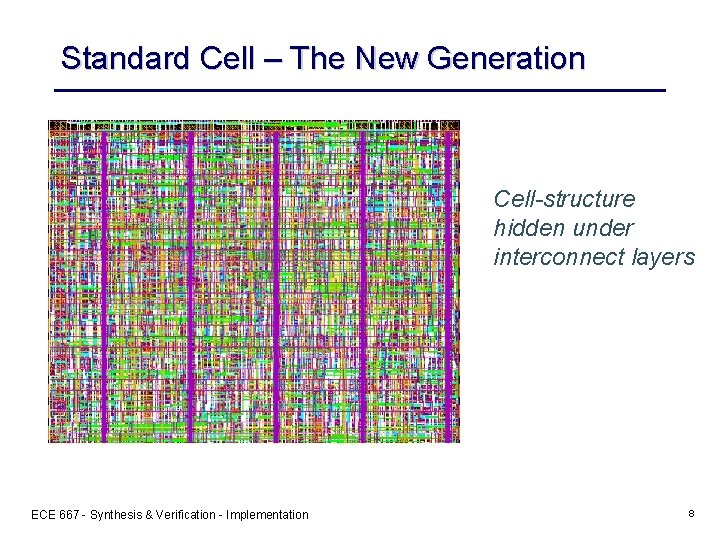

Standard Cell – The New Generation Cell-structure hidden under interconnect layers ECE 667 - Synthesis & Verification - Implementation 8

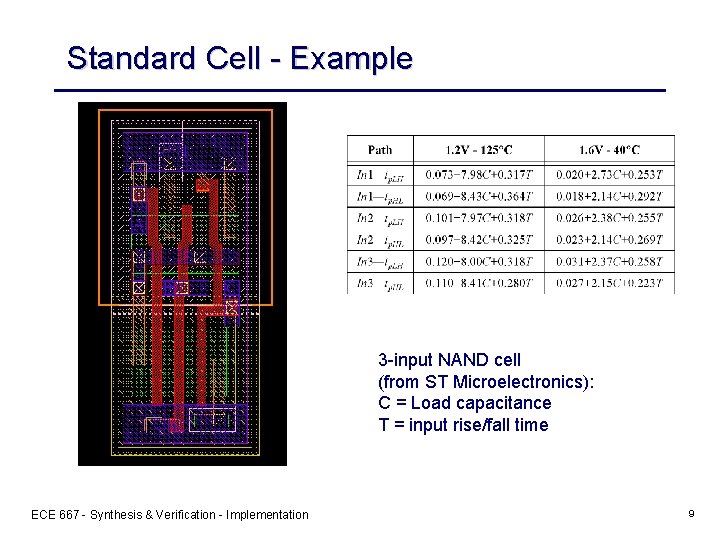

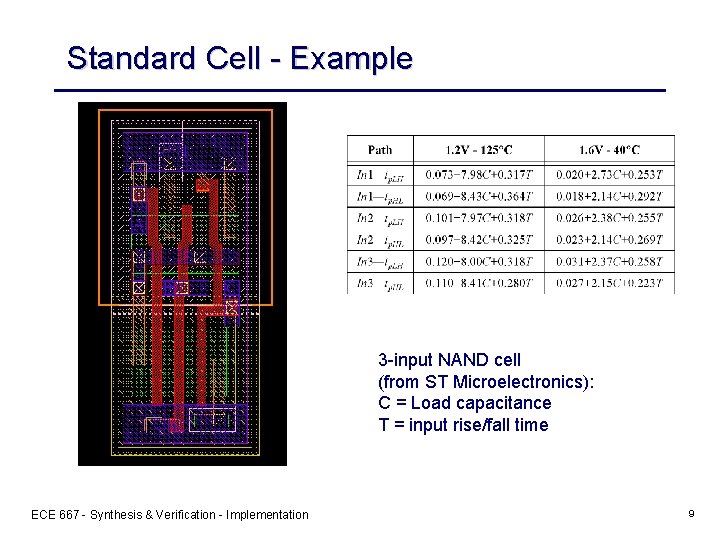

Standard Cell - Example 3 -input NAND cell (from ST Microelectronics): C = Load capacitance T = input rise/fall time ECE 667 - Synthesis & Verification - Implementation 9

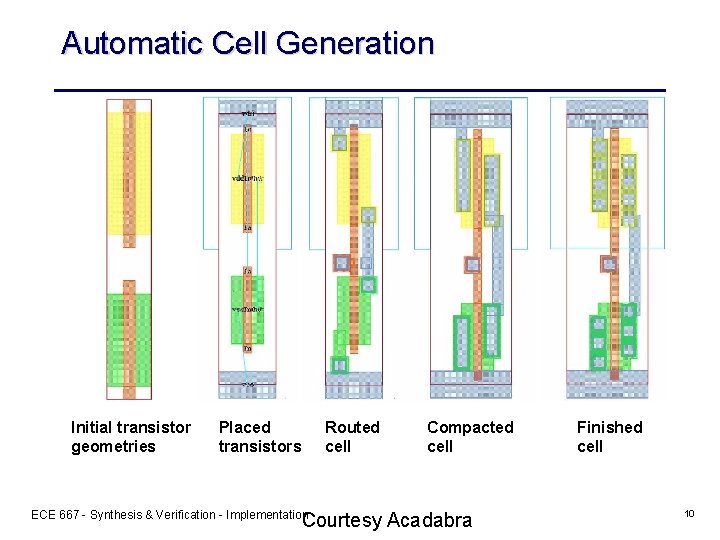

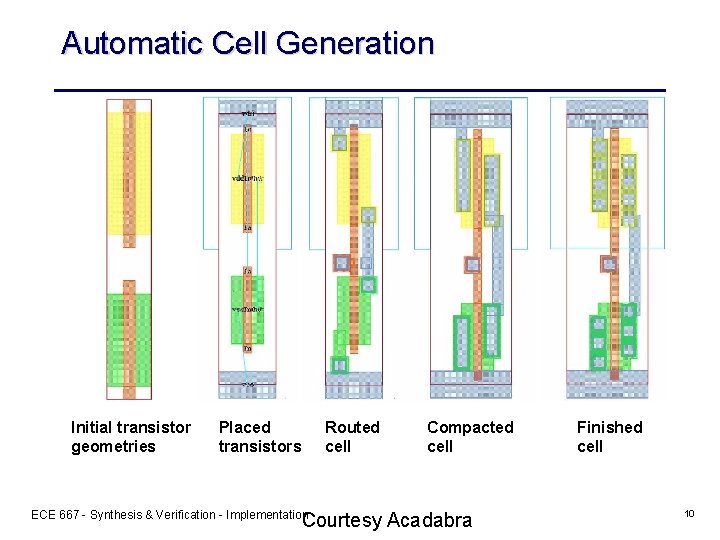

Automatic Cell Generation Initial transistor geometries Placed transistors Routed cell ECE 667 - Synthesis & Verification - Implementation Compacted cell Courtesy Acadabra Finished cell 10

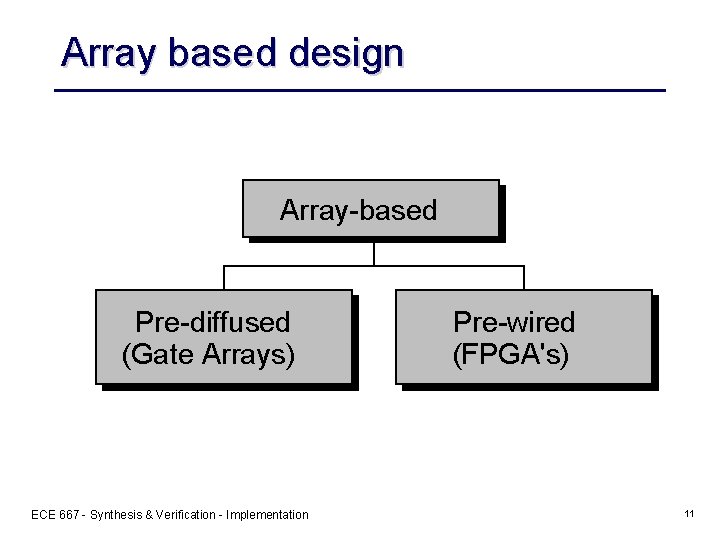

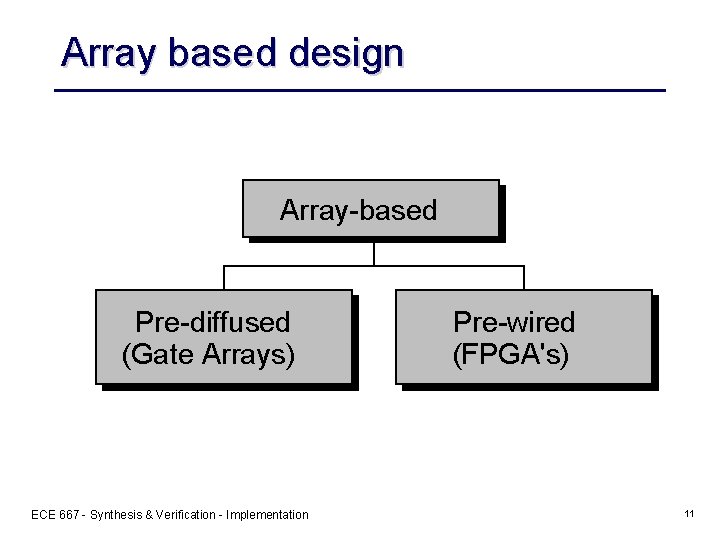

Array based design Array-based Pre-diffused (Gate Arrays) ECE 667 - Synthesis & Verification - Implementation Pre-wired (FPGA's) 11

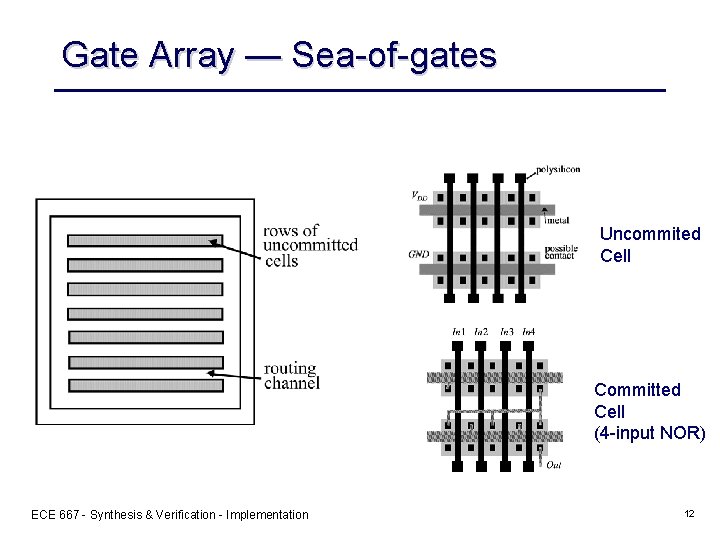

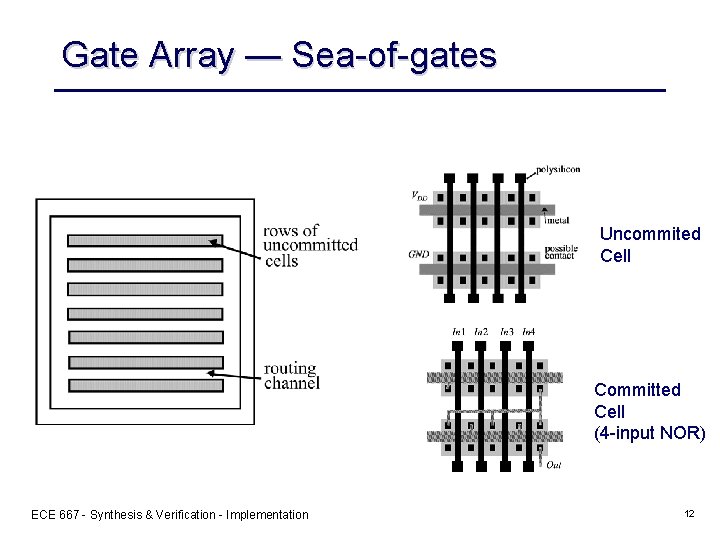

Gate Array — Sea-of-gates Uncommited Cell Committed Cell (4 -input NOR) ECE 667 - Synthesis & Verification - Implementation 12

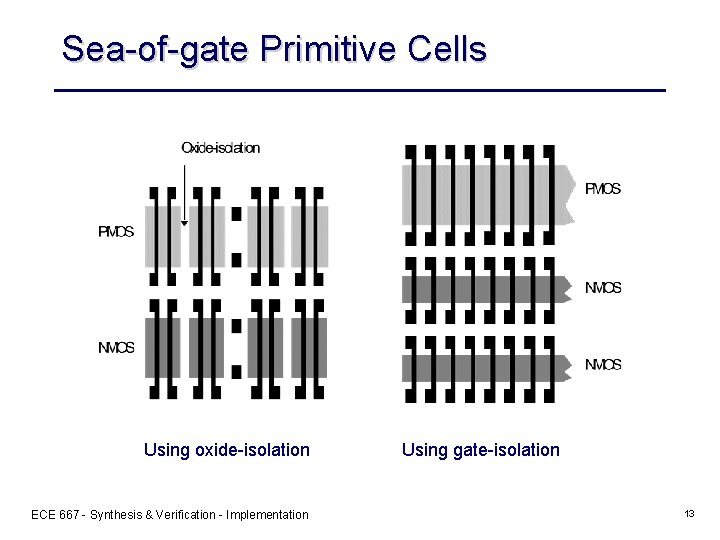

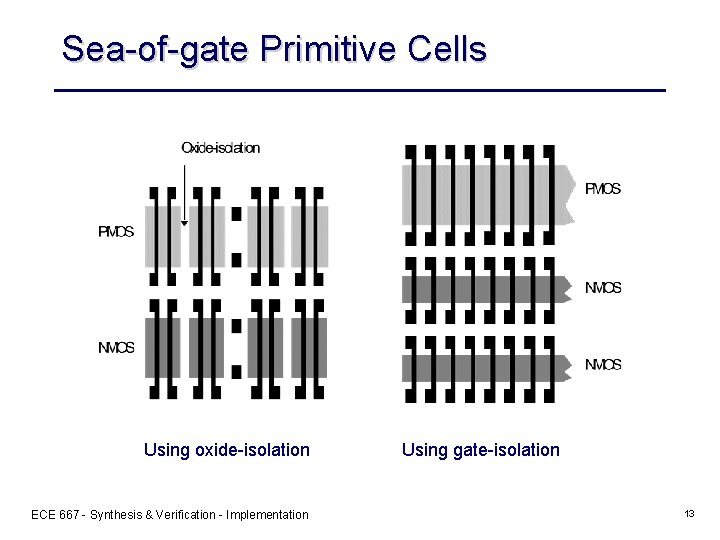

Sea-of-gate Primitive Cells Using oxide-isolation ECE 667 - Synthesis & Verification - Implementation Using gate-isolation 13

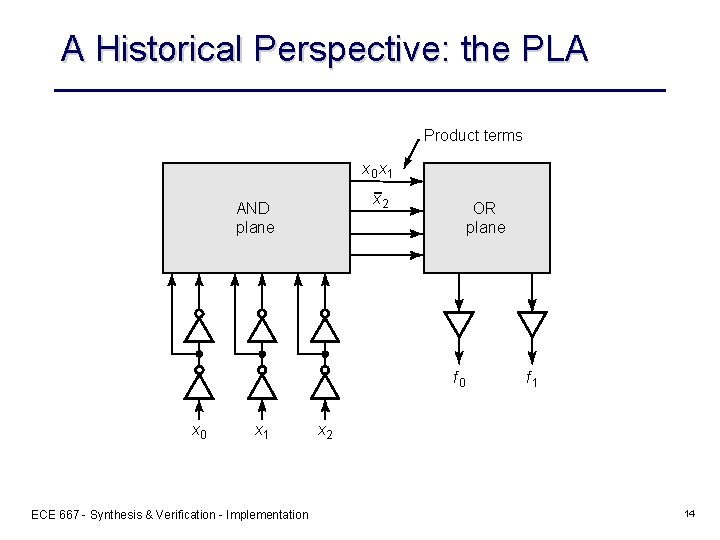

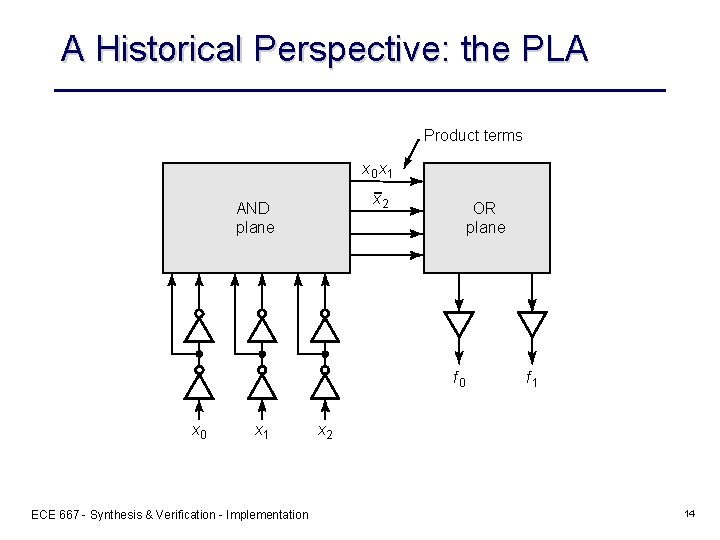

A Historical Perspective: the PLA Product terms x 0 x 1 x 2 AND plane OR plane f 0 x 1 ECE 667 - Synthesis & Verification - Implementation f 1 x 2 14

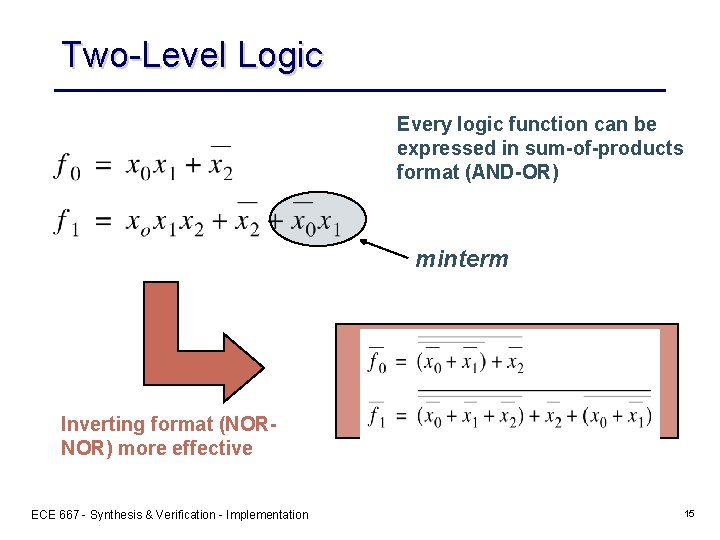

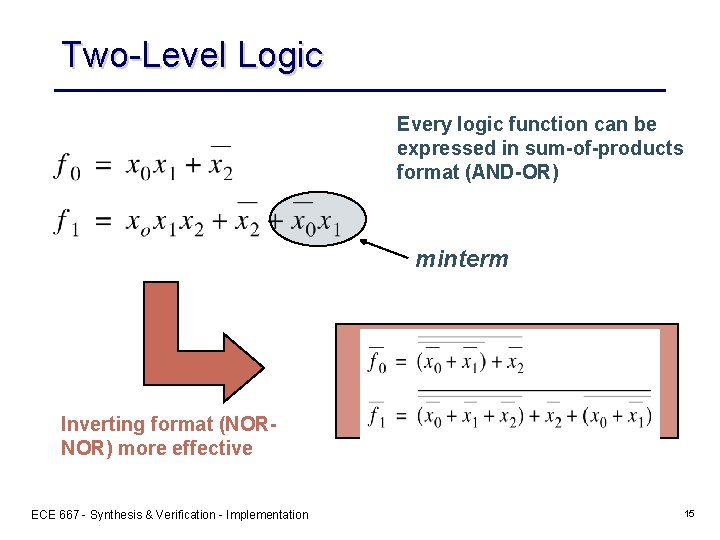

Two-Level Logic Every logic function can be expressed in sum-of-products format (AND-OR) minterm Inverting format (NORNOR) more effective ECE 667 - Synthesis & Verification - Implementation 15

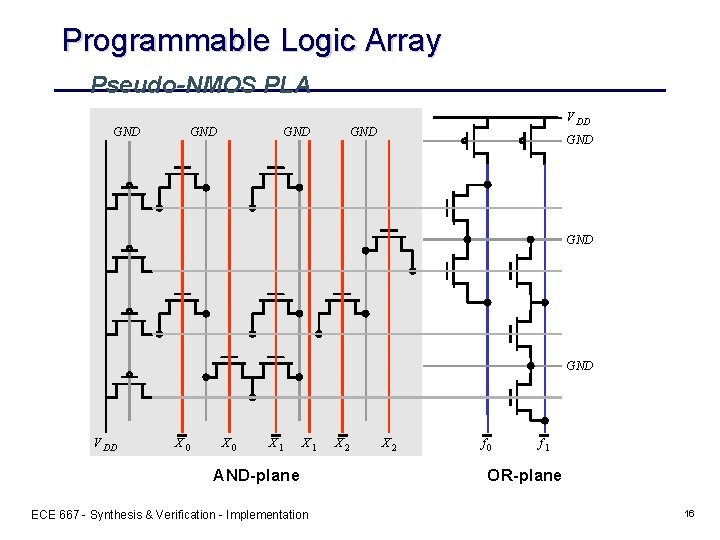

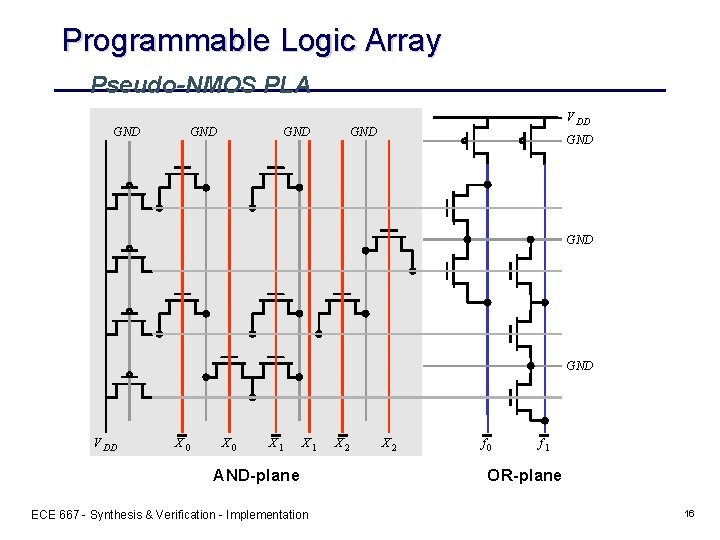

Programmable Logic Array Pseudo-NMOS PLA GND GND V DD X 0 X 1 AND-plane ECE 667 - Synthesis & Verification - Implementation X 2 f 0 f 1 OR-plane 16

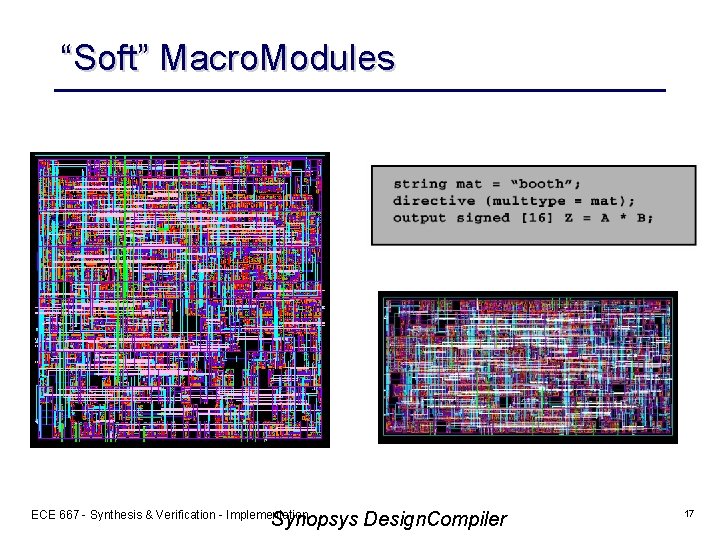

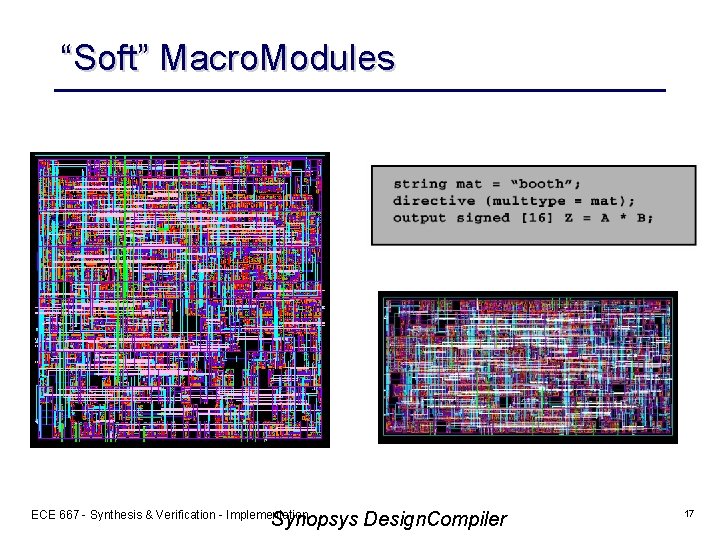

“Soft” Macro. Modules Synopsys Design. Compiler ECE 667 - Synthesis & Verification - Implementation 17

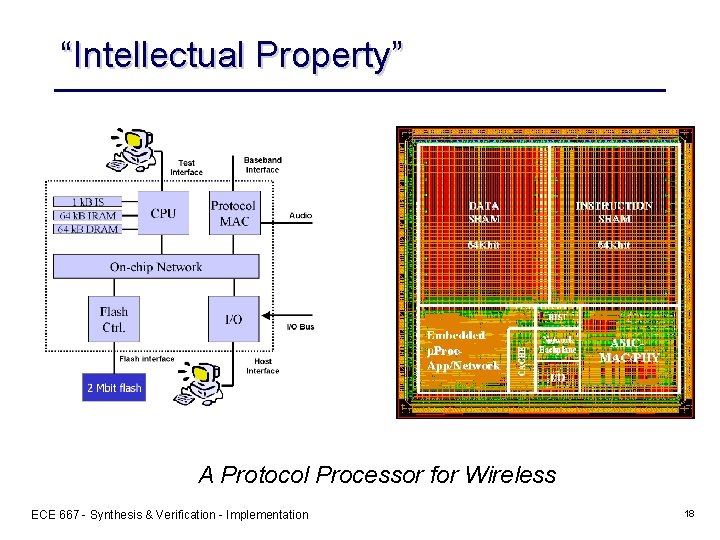

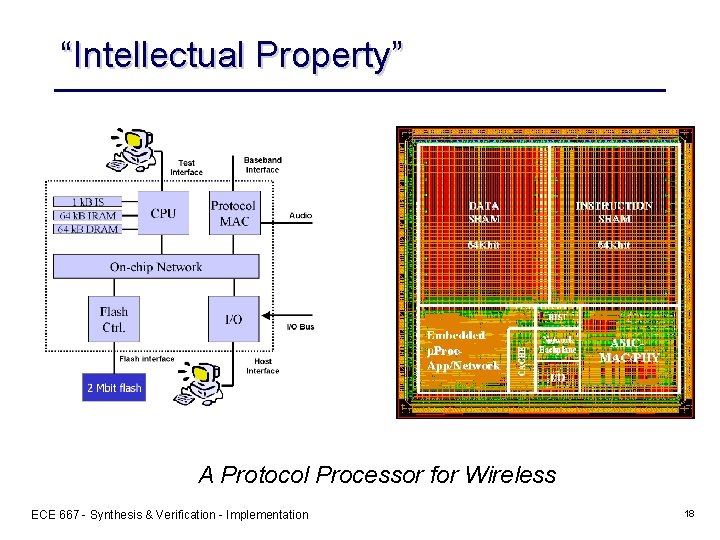

“Intellectual Property” A Protocol Processor for Wireless ECE 667 - Synthesis & Verification - Implementation 18

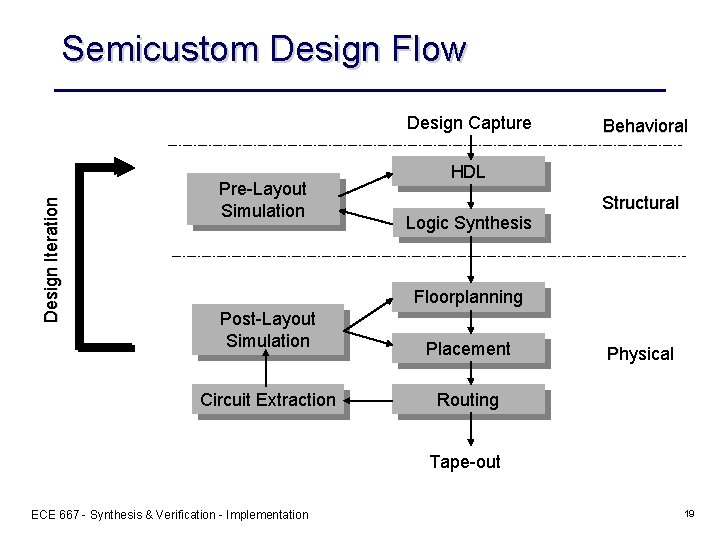

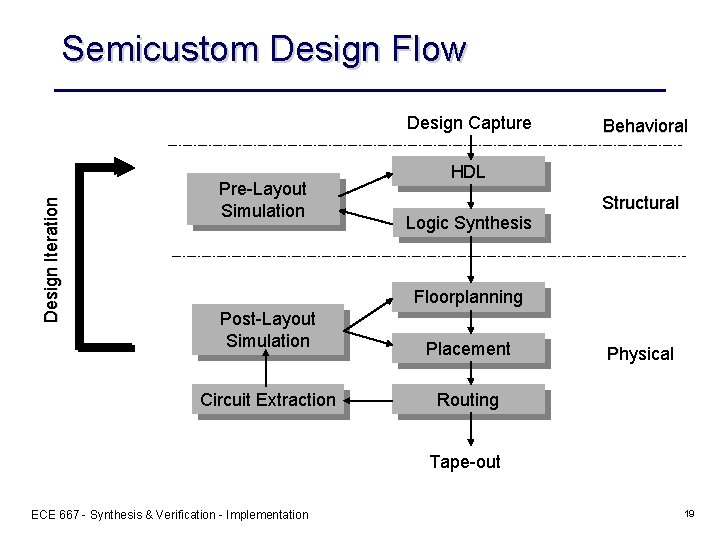

Semicustom Design Flow Design Iteration Design Capture Pre-Layout Simulation Behavioral HDL Logic Synthesis Structural Floorplanning Post-Layout Simulation Placement Circuit Extraction Routing Physical Tape-out ECE 667 - Synthesis & Verification - Implementation 19

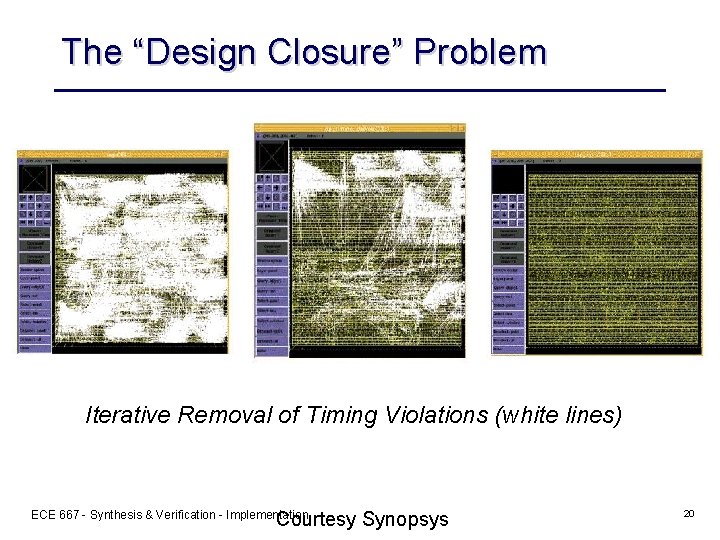

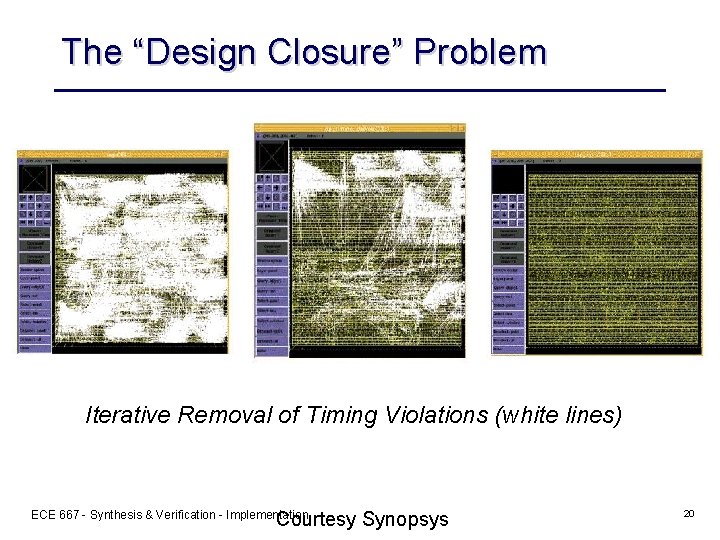

The “Design Closure” Problem Iterative Removal of Timing Violations (white lines) Courtesy Synopsys ECE 667 - Synthesis & Verification - Implementation 20