ECE 448 Lecture 3 CombinationalCircuit Building Blocks Data

ECE 448 Lecture 3 Combinational-Circuit Building Blocks Data Flow Modeling of Combinational Logic ECE 448 – FPGA and ASIC Design with VHDL George Mason University

Reading Required • P. Chu, FPGA Prototyping by VHDL Examples Chapter 3, RT-level combinational circuit Sections 3. 1, 3. 2, 3. 3, 3. 6, 3. 7. 1, 3. 7. 3. Recommended • S. Brown and Z. Vranesic, Fundamentals of Digital Logic with VHDL Design Chapter 6, Combinational-Circuit Building Blocks Chapter 5. 5, Design of Arithmetic Circuits Using CAD Tools ECE 448 – FPGA and ASIC Design with VHDL 2

Types of VHDL Description (Modeling Styles) ECE 448 – FPGA and ASIC Design with VHDL 3

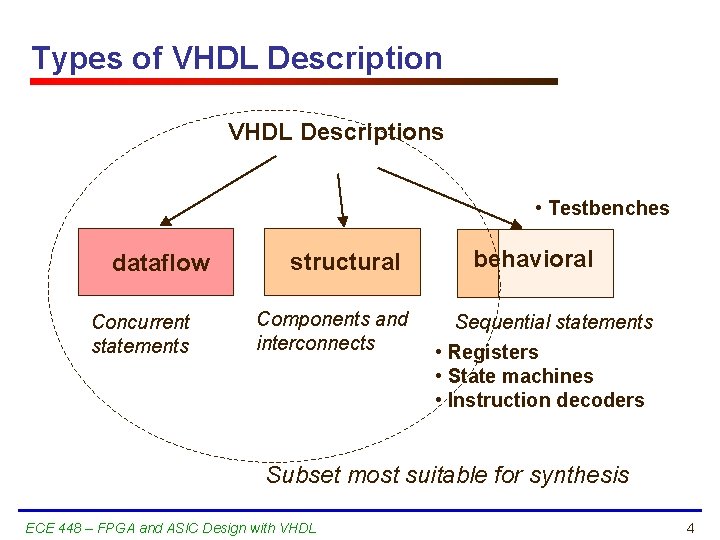

Types of VHDL Descriptions • Testbenches dataflow Concurrent statements structural Components and interconnects behavioral Sequential statements • Registers • State machines • Instruction decoders Subset most suitable for synthesis ECE 448 – FPGA and ASIC Design with VHDL 4

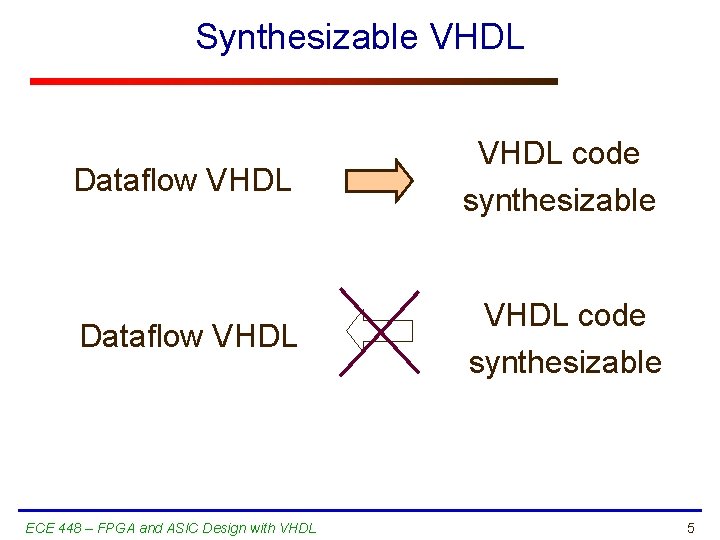

Synthesizable VHDL Dataflow VHDL code synthesizable ECE 448 – FPGA and ASIC Design with VHDL 5

Data-Flow VHDL Concurrent Statements • concurrent signal assignment ( ) • conditional concurrent signal assignment (when-else) • selected concurrent signal assignment (with-select-when) ECE 448 – FPGA and ASIC Design with VHDL 6

Concurrent signal assignment <= target_signal <= expression; ECE 448 – FPGA and ASIC Design with VHDL 7

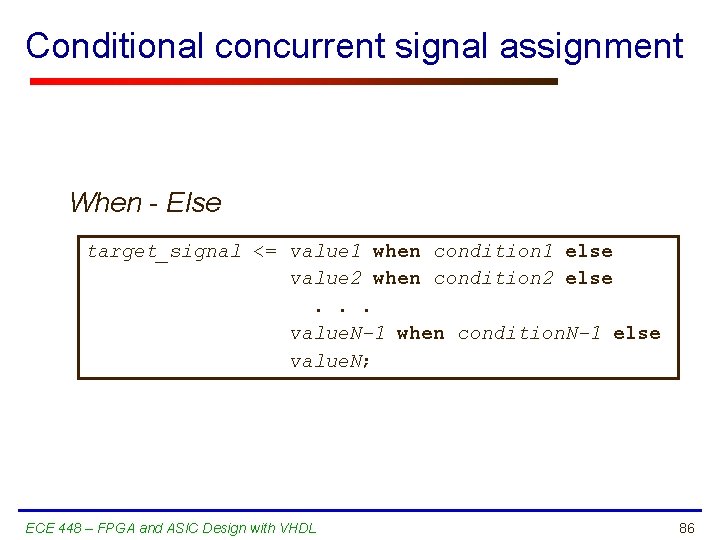

Conditional concurrent signal assignment When - Else target_signal <= value 1 when condition 1 else value 2 when condition 2 else. . . value. N-1 when condition. N-1 else value. N; ECE 448 – FPGA and ASIC Design with VHDL 8

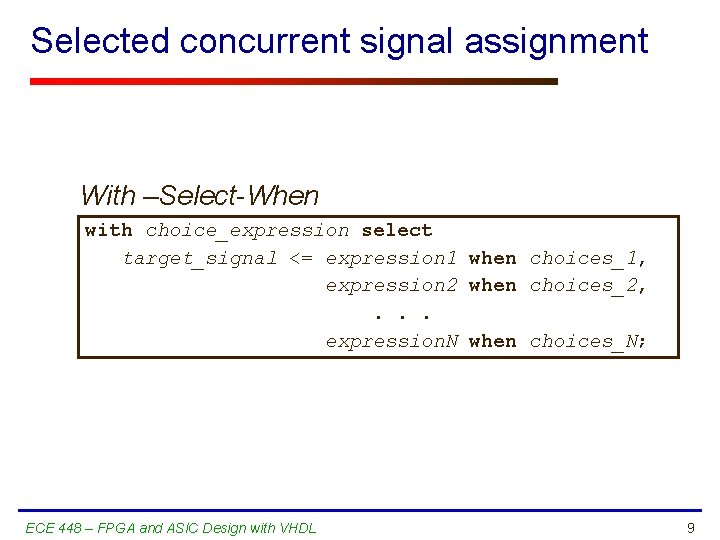

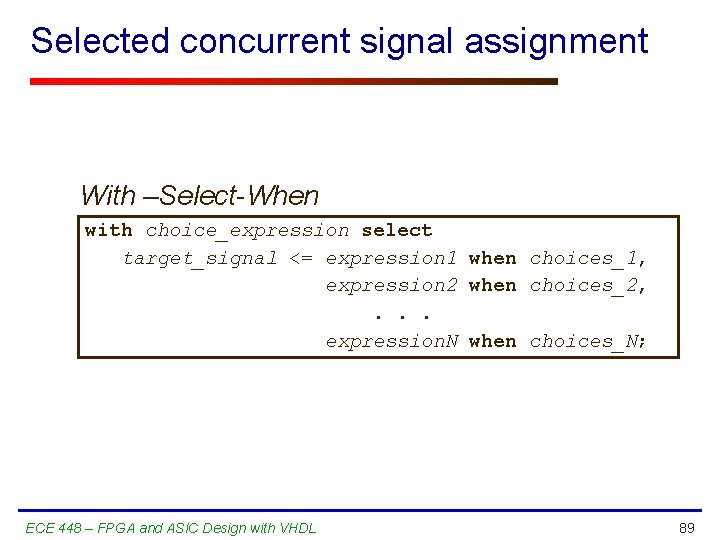

Selected concurrent signal assignment With –Select-When with choice_expression select target_signal <= expression 1 when choices_1, expression 2 when choices_2, . . . expression. N when choices_N; ECE 448 – FPGA and ASIC Design with VHDL 9

Modeling Wires and Buses ECE 448 – FPGA and ASIC Design with VHDL 10

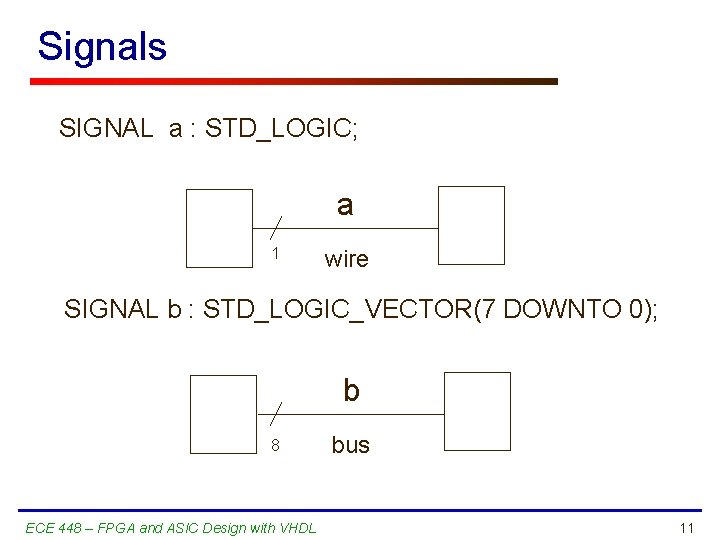

Signals SIGNAL a : STD_LOGIC; a 1 wire SIGNAL b : STD_LOGIC_VECTOR(7 DOWNTO 0); b 8 ECE 448 – FPGA and ASIC Design with VHDL bus 11

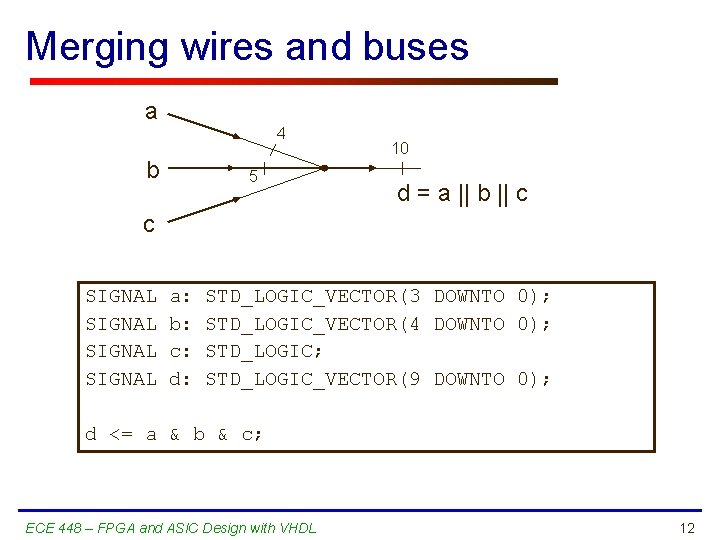

Merging wires and buses a 4 b 5 10 d = a || b || c c SIGNAL a: b: c: d: STD_LOGIC_VECTOR(3 DOWNTO 0); STD_LOGIC_VECTOR(4 DOWNTO 0); STD_LOGIC_VECTOR(9 DOWNTO 0); d <= a & b & c; ECE 448 – FPGA and ASIC Design with VHDL 12

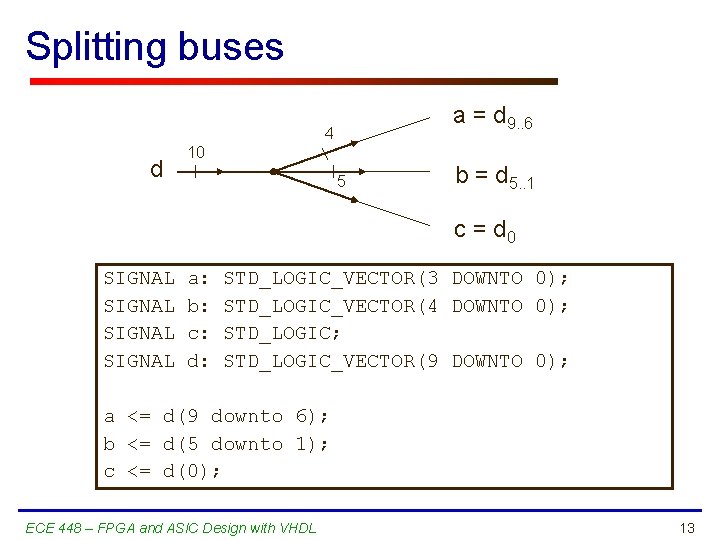

Splitting buses a = d 9. . 6 4 d 10 5 b = d 5. . 1 c = d 0 SIGNAL a: b: c: d: STD_LOGIC_VECTOR(3 DOWNTO 0); STD_LOGIC_VECTOR(4 DOWNTO 0); STD_LOGIC_VECTOR(9 DOWNTO 0); a <= d(9 downto 6); b <= d(5 downto 1); c <= d(0); ECE 448 – FPGA and ASIC Design with VHDL 13

Combinational-Circuit Building Blocks ECE 448 – FPGA and ASIC Design with VHDL 14

Fixed Shifters & Rotators ECE 448 – FPGA and ASIC Design with VHDL 15

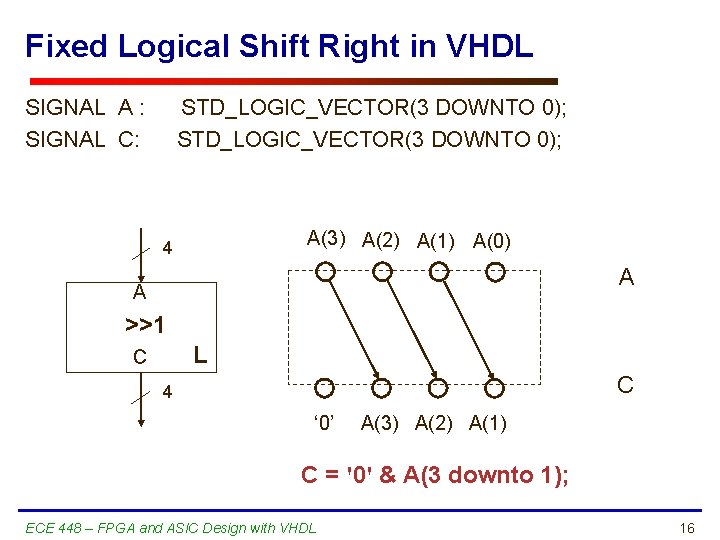

Fixed Logical Shift Right in VHDL SIGNAL A : SIGNAL C: STD_LOGIC_VECTOR(3 DOWNTO 0); A(3) A(2) A(1) A(0) 4 A A >>1 L C C 4 ‘ 0’ A(3) A(2) A(1) C = '0' & A(3 downto 1); ECE 448 – FPGA and ASIC Design with VHDL 16

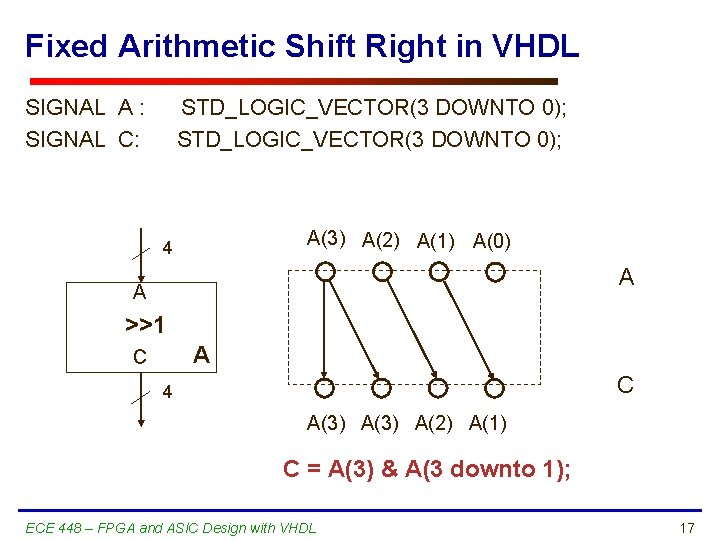

Fixed Arithmetic Shift Right in VHDL SIGNAL A : SIGNAL C: STD_LOGIC_VECTOR(3 DOWNTO 0); A(3) A(2) A(1) A(0) 4 A A >>1 A C C 4 A(3) A(2) A(1) C = A(3) & A(3 downto 1); ECE 448 – FPGA and ASIC Design with VHDL 17

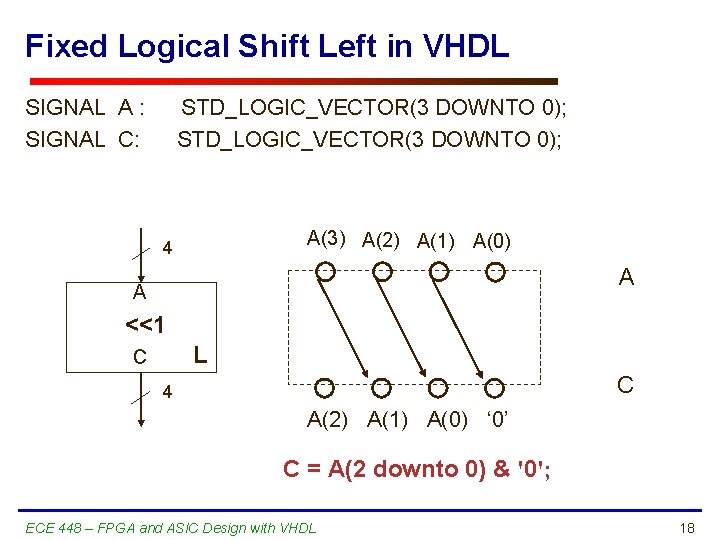

Fixed Logical Shift Left in VHDL SIGNAL A : SIGNAL C: STD_LOGIC_VECTOR(3 DOWNTO 0); A(3) A(2) A(1) A(0) 4 A A <<1 L C C 4 A(2) A(1) A(0) ‘ 0’ C = A(2 downto 0) & '0'; ECE 448 – FPGA and ASIC Design with VHDL 18

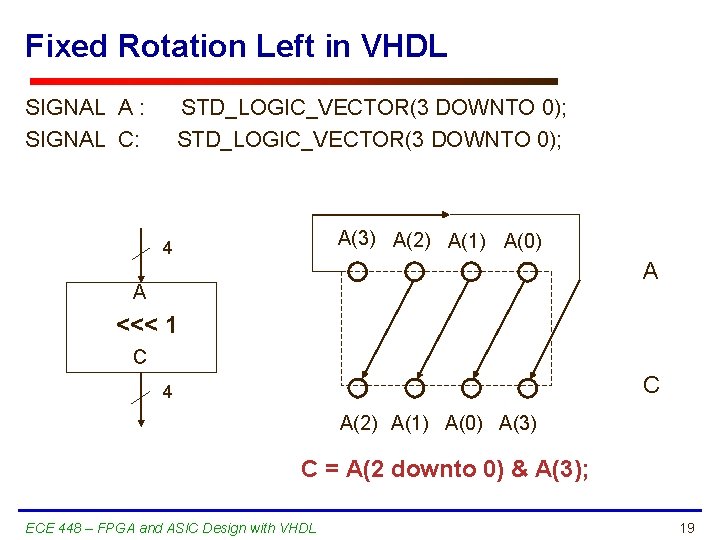

Fixed Rotation Left in VHDL SIGNAL A : SIGNAL C: STD_LOGIC_VECTOR(3 DOWNTO 0); A(3) A(2) A(1) A(0) 4 A A <<< 1 C C 4 A(2) A(1) A(0) A(3) C = A(2 downto 0) & A(3); ECE 448 – FPGA and ASIC Design with VHDL 19

Variable Rotators ECE 448 – FPGA and ASIC Design with VHDL 20

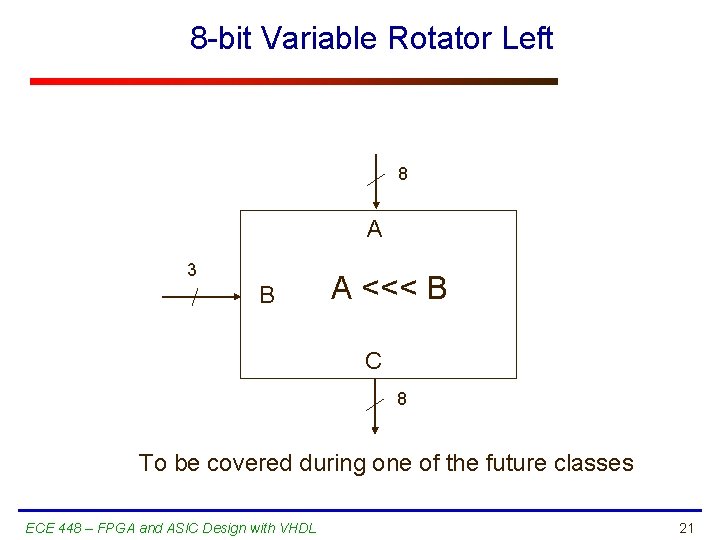

8 -bit Variable Rotator Left 8 A 3 B A <<< B C 8 To be covered during one of the future classes ECE 448 – FPGA and ASIC Design with VHDL 21

Gates ECE 448 – FPGA and ASIC Design with VHDL 22

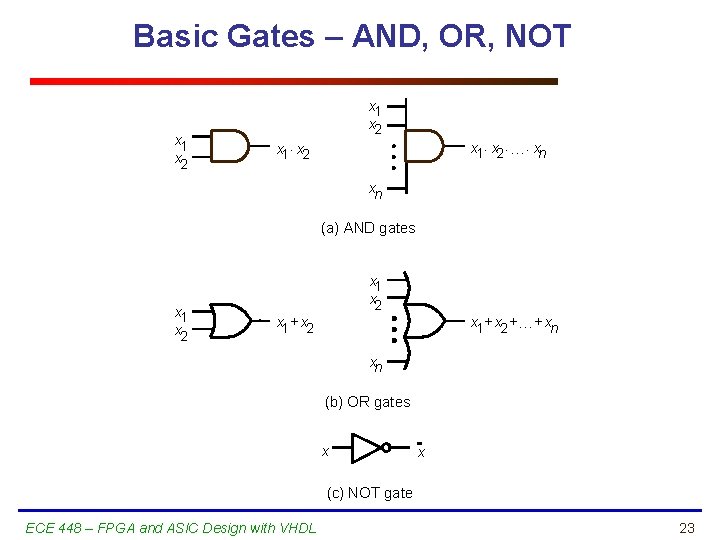

Basic Gates – AND, OR, NOT x 1 x 2 x 1 × x 2 × ¼× xn x 1 × x 2 xn (a) AND gates x 1 x 2 x 1 + x 2 + ¼+ xn x 1 + x 2 xn (b) OR gates x x (c) NOT gate ECE 448 – FPGA and ASIC Design with VHDL 23

Basic Gates – NAND, NOR … … ECE 448 – FPGA and ASIC Design with VHDL 24

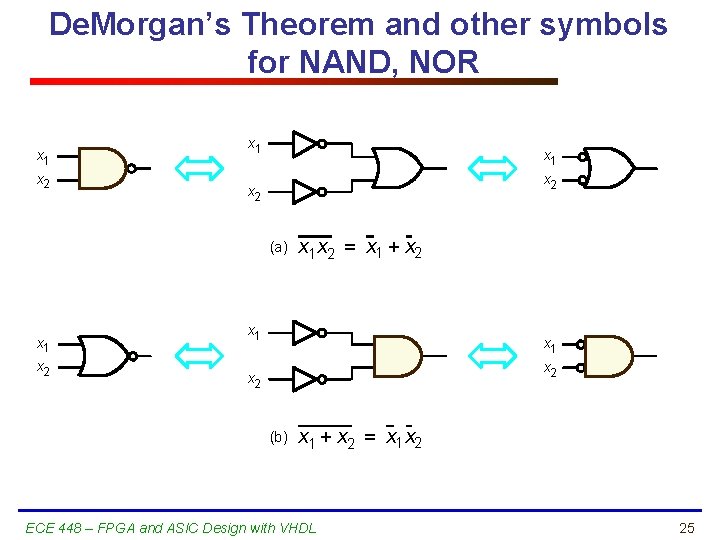

De. Morgan’s Theorem and other symbols for NAND, NOR x 1 x 2 (a) x 1 x 2 = x 1 + x 2 x 1 x 2 (b) x 1 + x 2 = x 1 x 2 ECE 448 – FPGA and ASIC Design with VHDL 25

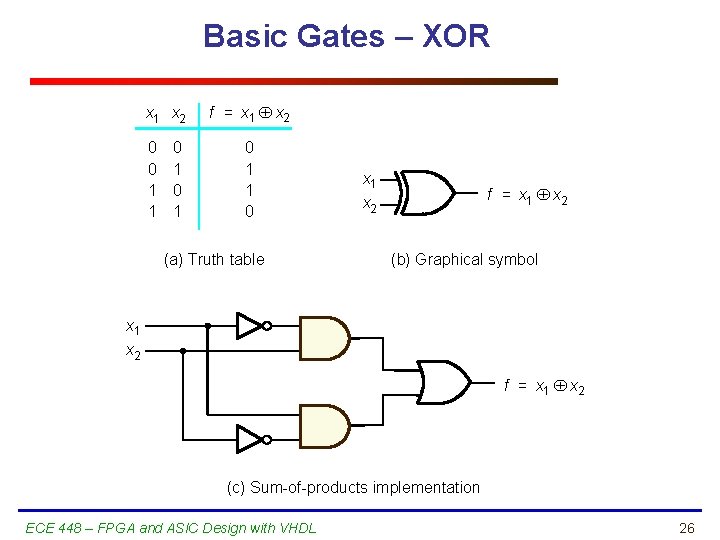

Basic Gates – XOR x 1 x 2 0 0 1 1 0 1 f = x 1 Å x 2 0 1 1 0 (a) Truth table x 1 f = x 1 Å x 2 (b) Graphical symbol x 1 x 2 f = x 1 Å x 2 (c) Sum-of-products implementation ECE 448 – FPGA and ASIC Design with VHDL 26

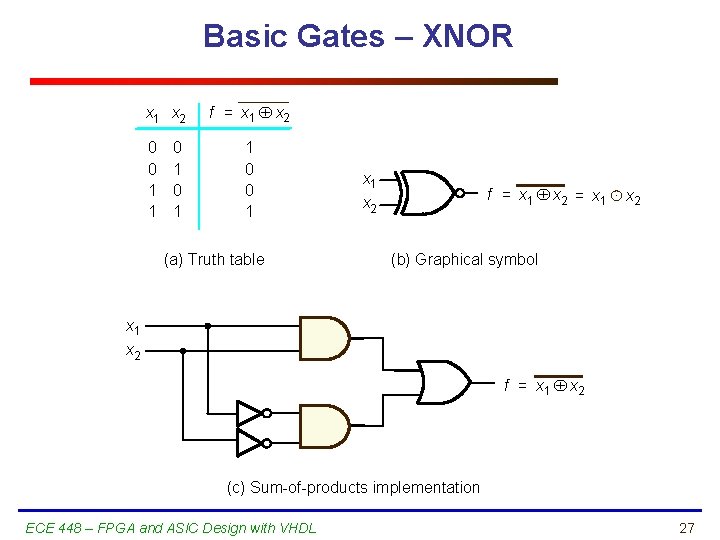

Basic Gates – XNOR x 1 x 2 0 0 1 1 0 1 f = x 1 Å x 2 1 0 0 1 (a) Truth table x 1 f = x 1 Å x 2 = x 1. x 2 (b) Graphical symbol x 1 x 2 f = x 1 Å x 2 (c) Sum-of-products implementation ECE 448 – FPGA and ASIC Design with VHDL 27

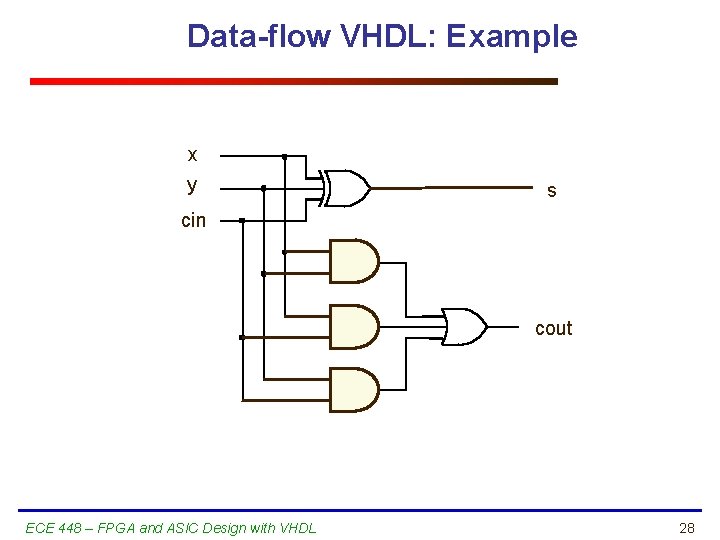

Data-flow VHDL: Example x y s cin cout ECE 448 – FPGA and ASIC Design with VHDL 28

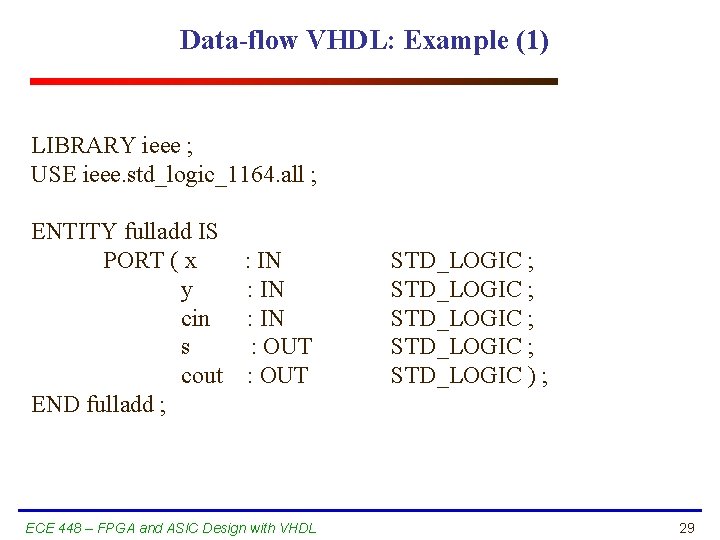

Data-flow VHDL: Example (1) LIBRARY ieee ; USE ieee. std_logic_1164. all ; ENTITY fulladd IS PORT ( x : IN y : IN cin : IN s : OUT cout : OUT END fulladd ; ECE 448 – FPGA and ASIC Design with VHDL STD_LOGIC ; STD_LOGIC ) ; 29

Data-flow VHDL: Example (2) ARCHITECTURE dataflow OF fulladd IS BEGIN s <= x XOR y XOR cin ; cout <= (x AND y) OR (cin AND x) OR (cin AND y) ; END dataflow ; ECE 448 – FPGA and ASIC Design with VHDL 30

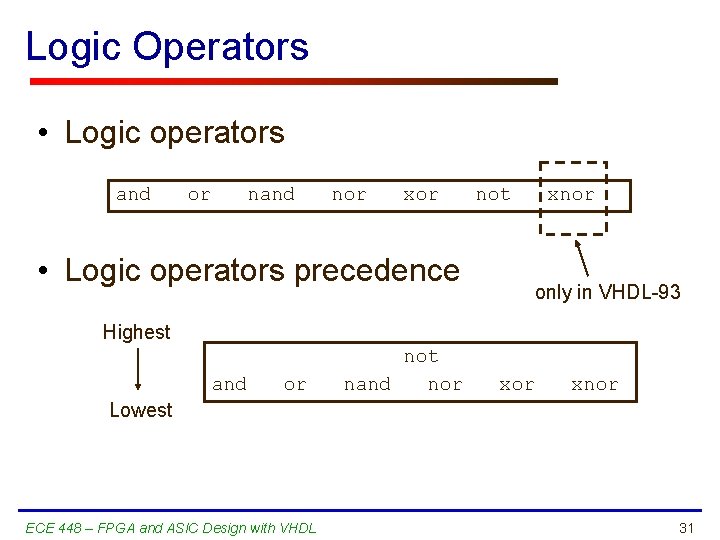

Logic Operators • Logic operators and or nand nor xor not • Logic operators precedence xnor only in VHDL-93 Highest and or not nand nor xnor Lowest ECE 448 – FPGA and ASIC Design with VHDL 31

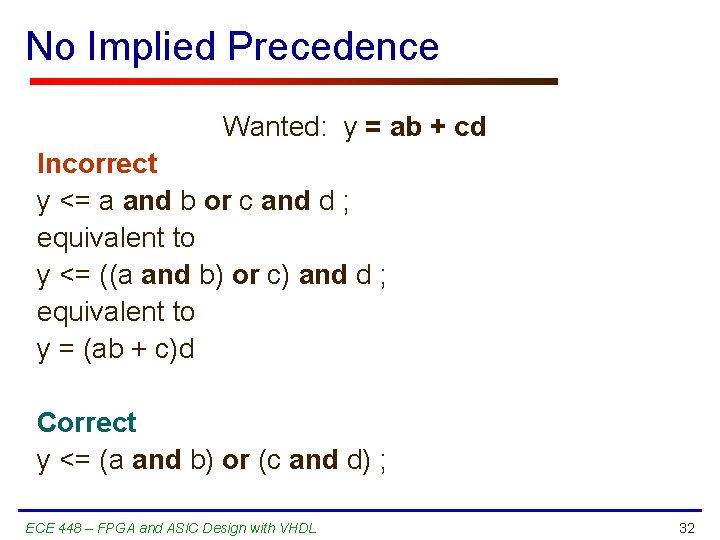

No Implied Precedence Wanted: y = ab + cd Incorrect y <= a and b or c and d ; equivalent to y <= ((a and b) or c) and d ; equivalent to y = (ab + c)d Correct y <= (a and b) or (c and d) ; ECE 448 – FPGA and ASIC Design with VHDL 32

Multiplexers ECE 448 – FPGA and ASIC Design with VHDL 33

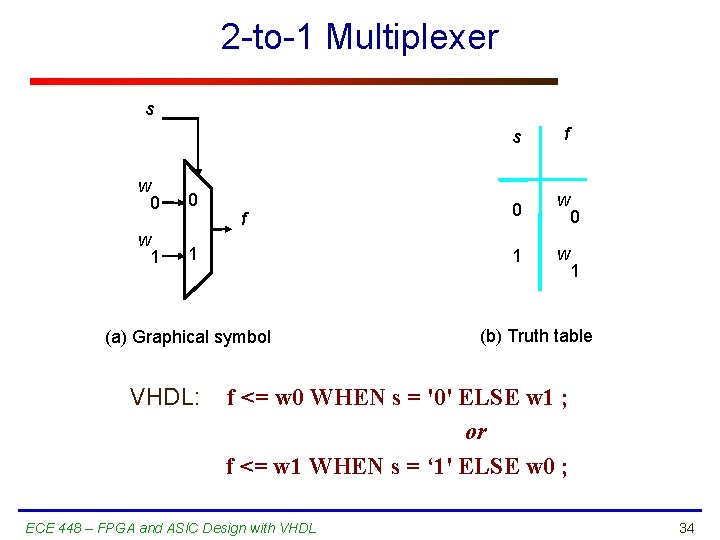

2 -to-1 Multiplexer s w 0 0 w 1 1 f (a) Graphical symbol VHDL: s f 0 w 0 1 w 1 (b) Truth table f <= w 0 WHEN s = '0' ELSE w 1 ; or f <= w 1 WHEN s = ‘ 1' ELSE w 0 ; ECE 448 – FPGA and ASIC Design with VHDL 34

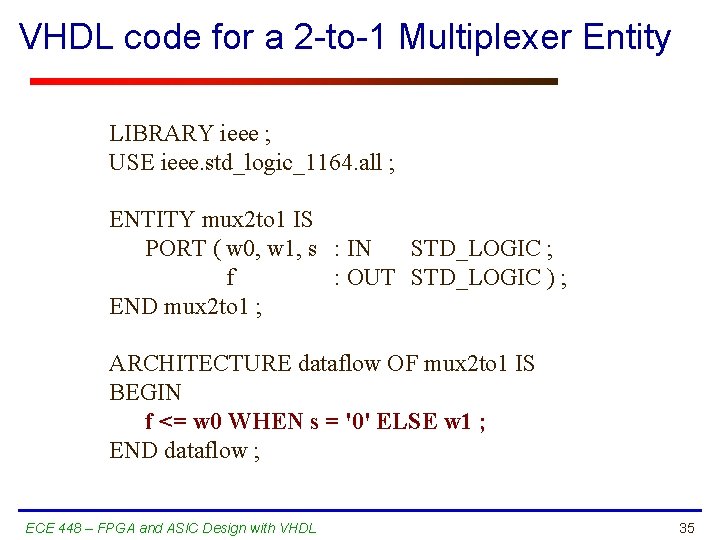

VHDL code for a 2 -to-1 Multiplexer Entity LIBRARY ieee ; USE ieee. std_logic_1164. all ; ENTITY mux 2 to 1 IS PORT ( w 0, w 1, s : IN STD_LOGIC ; f : OUT STD_LOGIC ) ; END mux 2 to 1 ; ARCHITECTURE dataflow OF mux 2 to 1 IS BEGIN f <= w 0 WHEN s = '0' ELSE w 1 ; END dataflow ; ECE 448 – FPGA and ASIC Design with VHDL 35

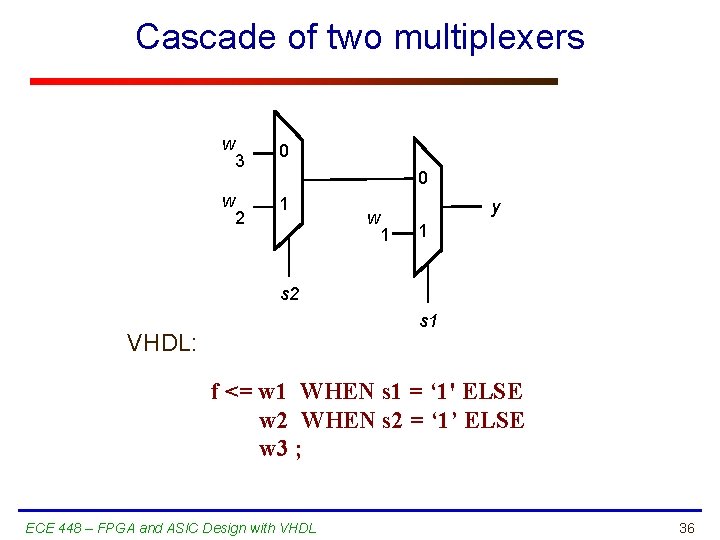

Cascade of two multiplexers w 3 0 w 2 1 0 w 1 y 1 s 2 s 1 VHDL: f <= w 1 WHEN s 1 = ‘ 1' ELSE w 2 WHEN s 2 = ‘ 1’ ELSE w 3 ; ECE 448 – FPGA and ASIC Design with VHDL 36

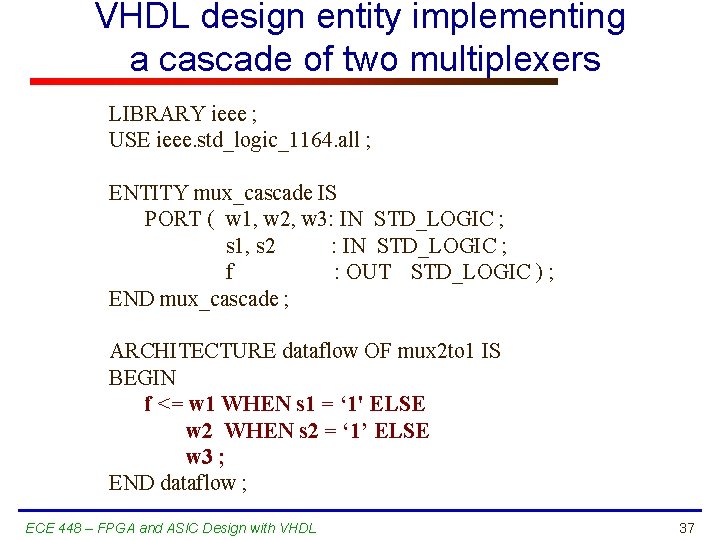

VHDL design entity implementing a cascade of two multiplexers LIBRARY ieee ; USE ieee. std_logic_1164. all ; ENTITY mux_cascade IS PORT ( w 1, w 2, w 3: IN STD_LOGIC ; s 1, s 2 : IN STD_LOGIC ; f : OUT STD_LOGIC ) ; END mux_cascade ; ARCHITECTURE dataflow OF mux 2 to 1 IS BEGIN f <= w 1 WHEN s 1 = ‘ 1' ELSE w 2 WHEN s 2 = ‘ 1’ ELSE w 3 ; END dataflow ; ECE 448 – FPGA and ASIC Design with VHDL 37

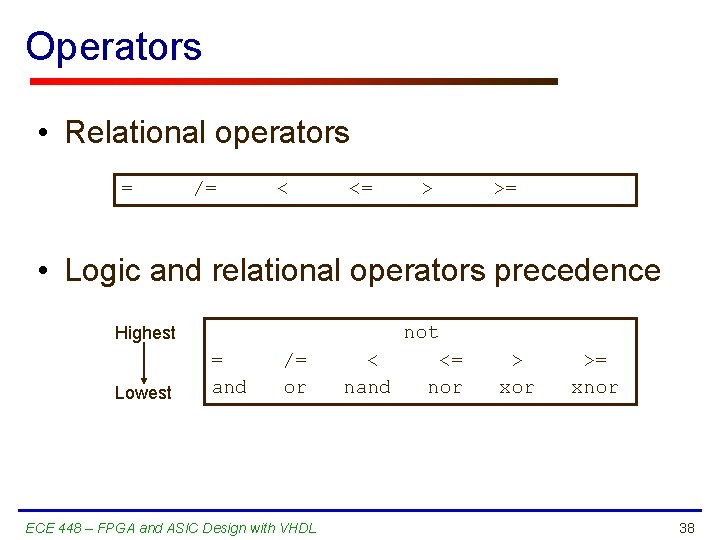

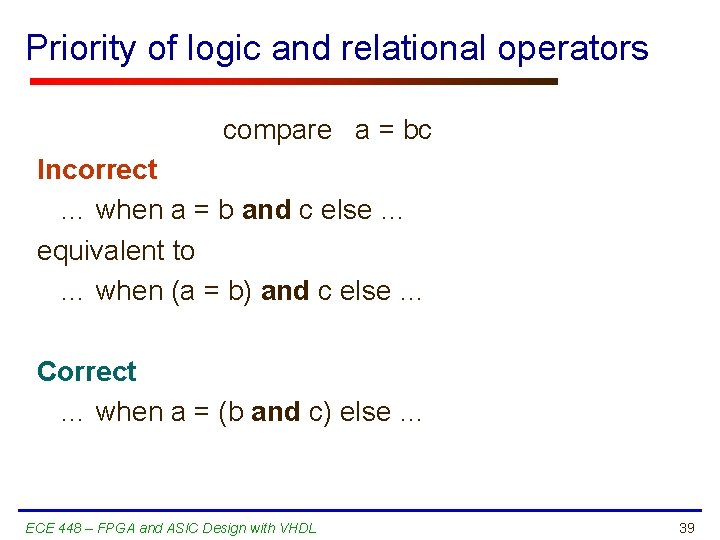

Operators • Relational operators = /= < <= > >= • Logic and relational operators precedence not Highest Lowest = and /= or ECE 448 – FPGA and ASIC Design with VHDL < nand <= nor > xor >= xnor 38

Priority of logic and relational operators compare a = bc Incorrect … when a = b and c else … equivalent to … when (a = b) and c else … Correct … when a = (b and c) else … ECE 448 – FPGA and ASIC Design with VHDL 39

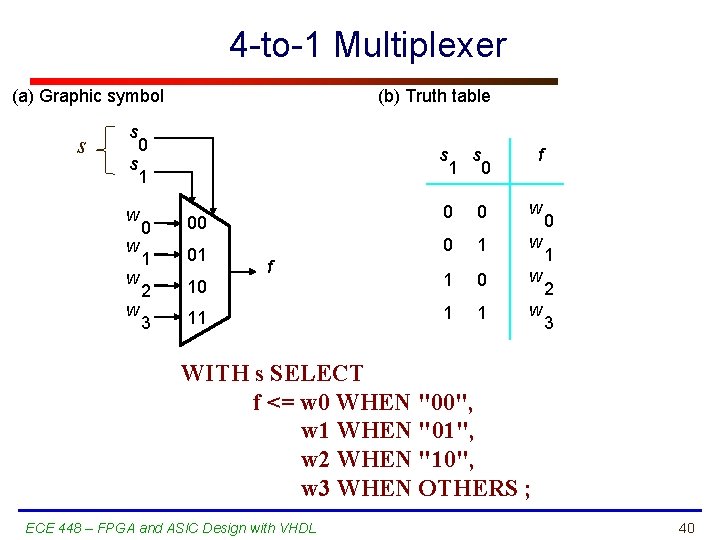

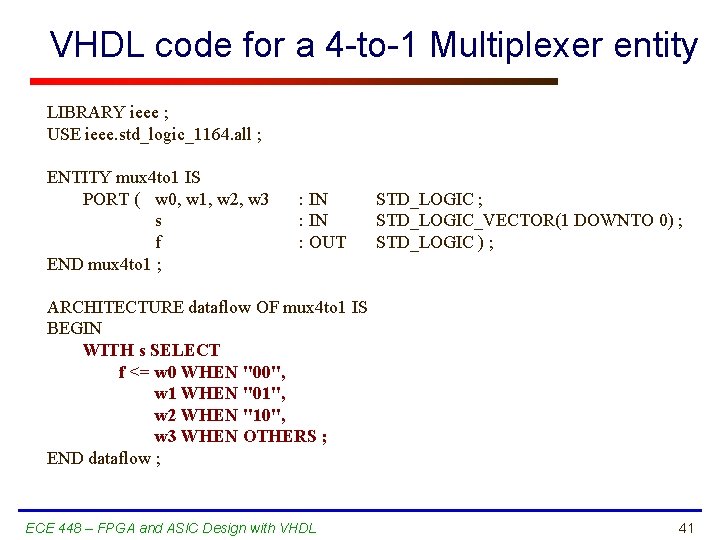

4 -to-1 Multiplexer (a) Graphic symbol s (b) Truth table s 0 s s 1 s 0 f w 0 0 w 0 1 w 1 0 w 1 1 w w w 0 00 1 01 2 10 3 11 f 0 1 2 3 WITH s SELECT f <= w 0 WHEN "00", w 1 WHEN "01", w 2 WHEN "10", w 3 WHEN OTHERS ; ECE 448 – FPGA and ASIC Design with VHDL 40

VHDL code for a 4 -to-1 Multiplexer entity LIBRARY ieee ; USE ieee. std_logic_1164. all ; ENTITY mux 4 to 1 IS PORT ( w 0, w 1, w 2, w 3 s f END mux 4 to 1 ; : IN : OUT STD_LOGIC ; STD_LOGIC_VECTOR(1 DOWNTO 0) ; STD_LOGIC ) ; ARCHITECTURE dataflow OF mux 4 to 1 IS BEGIN WITH s SELECT f <= w 0 WHEN "00", w 1 WHEN "01", w 2 WHEN "10", w 3 WHEN OTHERS ; END dataflow ; ECE 448 – FPGA and ASIC Design with VHDL 41

Decoders ECE 448 – FPGA and ASIC Design with VHDL 42

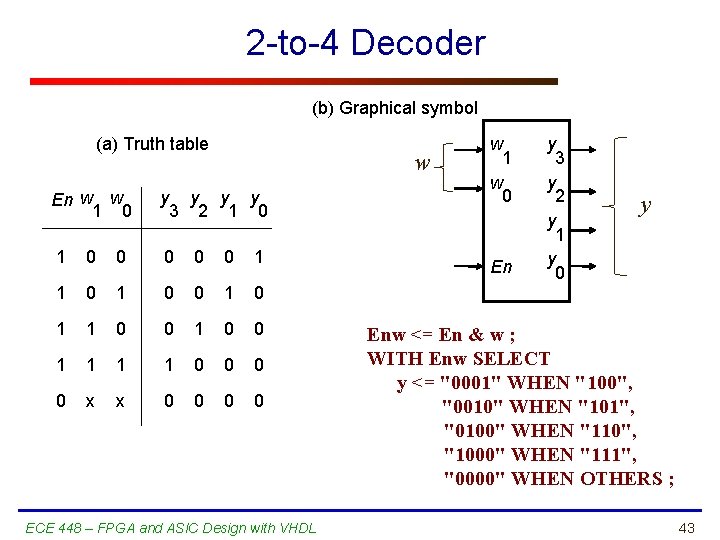

2 -to-4 Decoder (b) Graphical symbol (a) Truth table En w w 1 0 w y y 3 2 1 0 0 0 1 1 0 0 1 1 0 0 x x 0 0 ECE 448 – FPGA and ASIC Design with VHDL w 1 w 0 En y 3 y 2 y 1 y 0 y Enw <= En & w ; WITH Enw SELECT y <= "0001" WHEN "100", "0010" WHEN "101", "0100" WHEN "110", "1000" WHEN "111", "0000" WHEN OTHERS ; 43

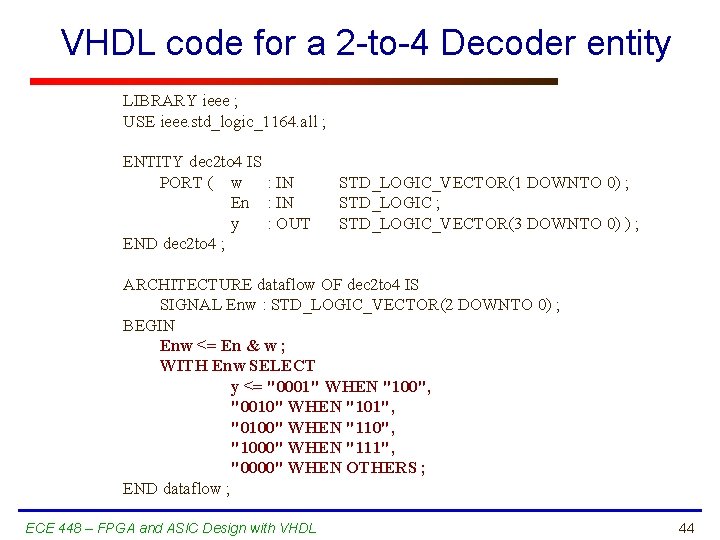

VHDL code for a 2 -to-4 Decoder entity LIBRARY ieee ; USE ieee. std_logic_1164. all ; ENTITY dec 2 to 4 IS PORT ( w : IN En : IN y : OUT END dec 2 to 4 ; STD_LOGIC_VECTOR(1 DOWNTO 0) ; STD_LOGIC_VECTOR(3 DOWNTO 0) ) ; ARCHITECTURE dataflow OF dec 2 to 4 IS SIGNAL Enw : STD_LOGIC_VECTOR(2 DOWNTO 0) ; BEGIN Enw <= En & w ; WITH Enw SELECT y <= "0001" WHEN "100", "0010" WHEN "101", "0100" WHEN "110", "1000" WHEN "111", "0000" WHEN OTHERS ; END dataflow ; ECE 448 – FPGA and ASIC Design with VHDL 44

Encoders ECE 448 – FPGA and ASIC Design with VHDL 45

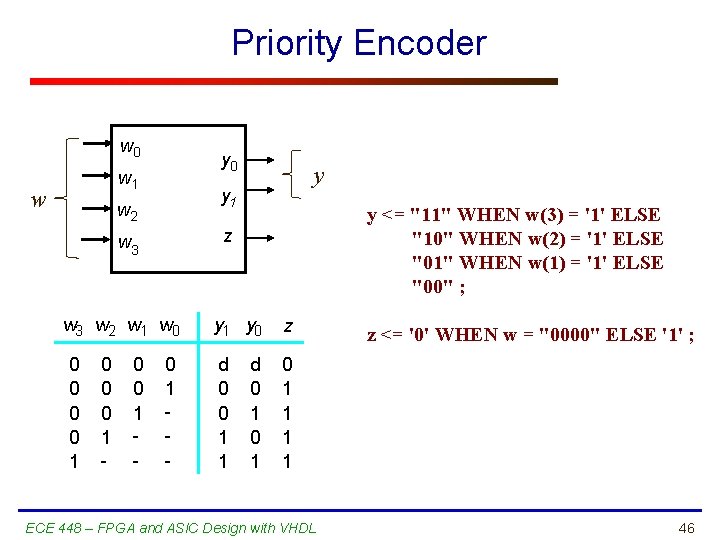

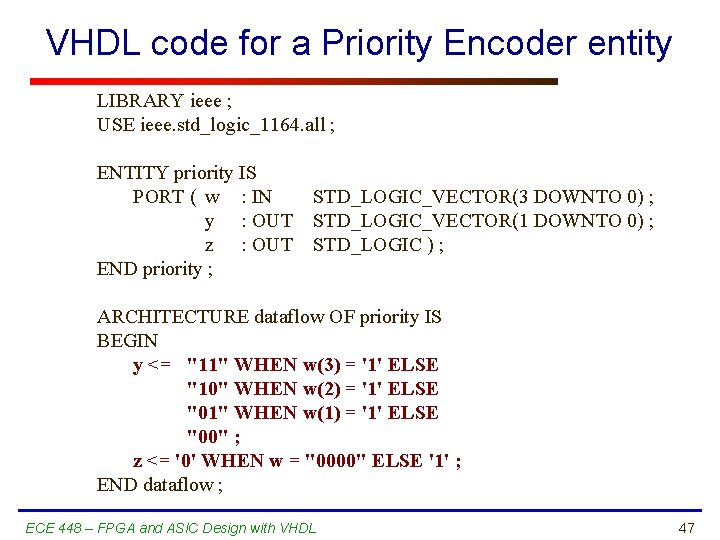

Priority Encoder w 0 y 0 w 1 w y 1 w 2 w 3 w 2 w 1 w 0 0 1 - y <= "11" WHEN w(3) = '1' ELSE "10" WHEN w(2) = '1' ELSE "01" WHEN w(1) = '1' ELSE "00" ; z w 3 0 0 1 y 0 1 - y 1 y 0 z d 0 0 1 1 1 1 d 0 1 ECE 448 – FPGA and ASIC Design with VHDL z <= '0' WHEN w = "0000" ELSE '1' ; 46

VHDL code for a Priority Encoder entity LIBRARY ieee ; USE ieee. std_logic_1164. all ; ENTITY priority IS PORT ( w : IN y : OUT z : OUT END priority ; STD_LOGIC_VECTOR(3 DOWNTO 0) ; STD_LOGIC_VECTOR(1 DOWNTO 0) ; STD_LOGIC ) ; ARCHITECTURE dataflow OF priority IS BEGIN y <= "11" WHEN w(3) = '1' ELSE "10" WHEN w(2) = '1' ELSE "01" WHEN w(1) = '1' ELSE "00" ; z <= '0' WHEN w = "0000" ELSE '1' ; END dataflow ; ECE 448 – FPGA and ASIC Design with VHDL 47

Adders ECE 448 – FPGA and ASIC Design with VHDL 48

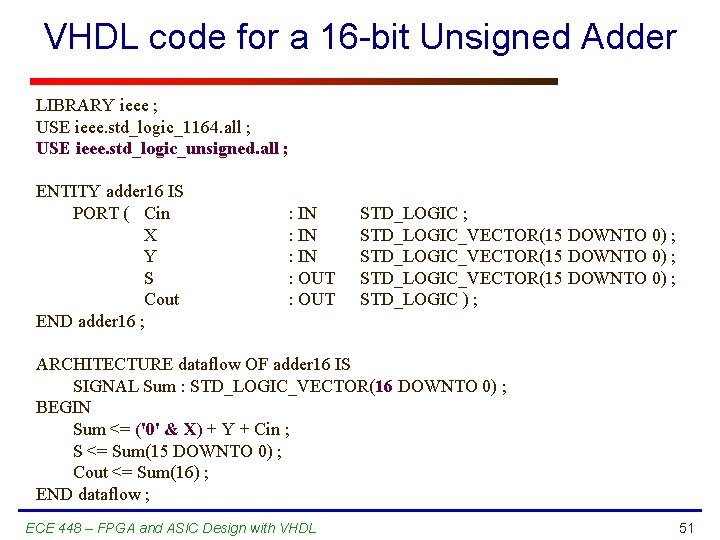

16 -bit Unsigned Adder 16 16 X + Cout Y Cin S 16 ECE 448 – FPGA and ASIC Design with VHDL 49

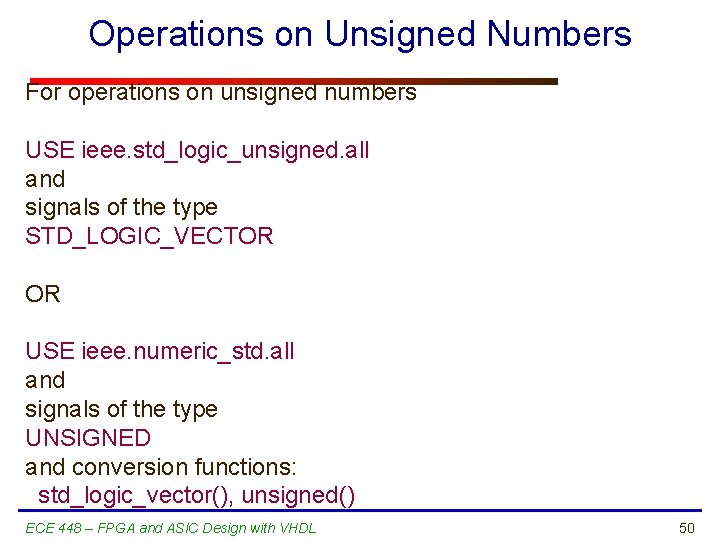

Operations on Unsigned Numbers For operations on unsigned numbers USE ieee. std_logic_unsigned. all and signals of the type STD_LOGIC_VECTOR OR USE ieee. numeric_std. all and signals of the type UNSIGNED and conversion functions: std_logic_vector(), unsigned() ECE 448 – FPGA and ASIC Design with VHDL 50

VHDL code for a 16 -bit Unsigned Adder LIBRARY ieee ; USE ieee. std_logic_1164. all ; USE ieee. std_logic_unsigned. all ; ENTITY adder 16 IS PORT ( Cin X Y S Cout END adder 16 ; : IN : OUT STD_LOGIC ; STD_LOGIC_VECTOR(15 DOWNTO 0) ; STD_LOGIC ) ; ARCHITECTURE dataflow OF adder 16 IS SIGNAL Sum : STD_LOGIC_VECTOR(16 DOWNTO 0) ; BEGIN Sum <= ('0' & X) + Y + Cin ; S <= Sum(15 DOWNTO 0) ; Cout <= Sum(16) ; END dataflow ; ECE 448 – FPGA and ASIC Design with VHDL 51

Addition of Unsigned Numbers (1) LIBRARY ieee ; USE ieee. std_logic_1164. all ; USE ieee. numeric_std. all ; ENTITY adder 16 IS PORT ( Cin X Y S Cout END adder 16 ; : IN : OUT ECE 448 – FPGA and ASIC Design with VHDL STD_LOGIC ; STD_LOGIC_VECTOR(15 DOWNTO 0) ; STD_LOGIC ) ; 52

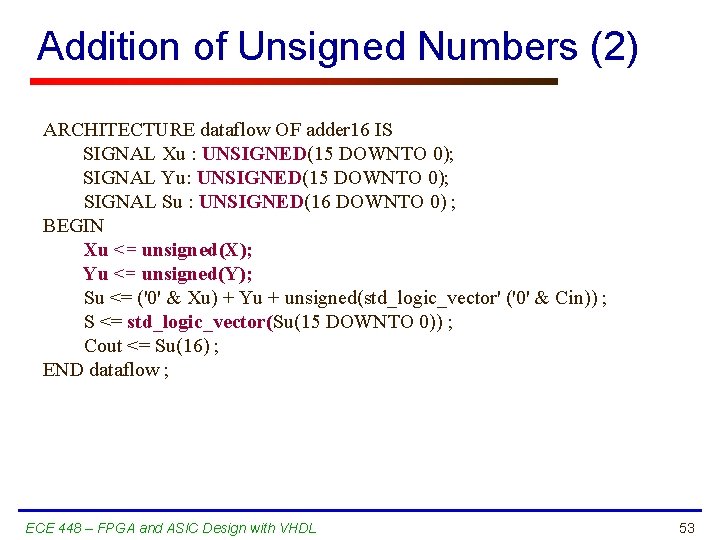

Addition of Unsigned Numbers (2) ARCHITECTURE dataflow OF adder 16 IS SIGNAL Xu : UNSIGNED(15 DOWNTO 0); SIGNAL Yu: UNSIGNED(15 DOWNTO 0); SIGNAL Su : UNSIGNED(16 DOWNTO 0) ; BEGIN Xu <= unsigned(X); Yu <= unsigned(Y); Su <= ('0' & Xu) + Yu + unsigned(std_logic_vector' ('0' & Cin)) ; S <= std_logic_vector(Su(15 DOWNTO 0)) ; Cout <= Su(16) ; END dataflow ; ECE 448 – FPGA and ASIC Design with VHDL 53

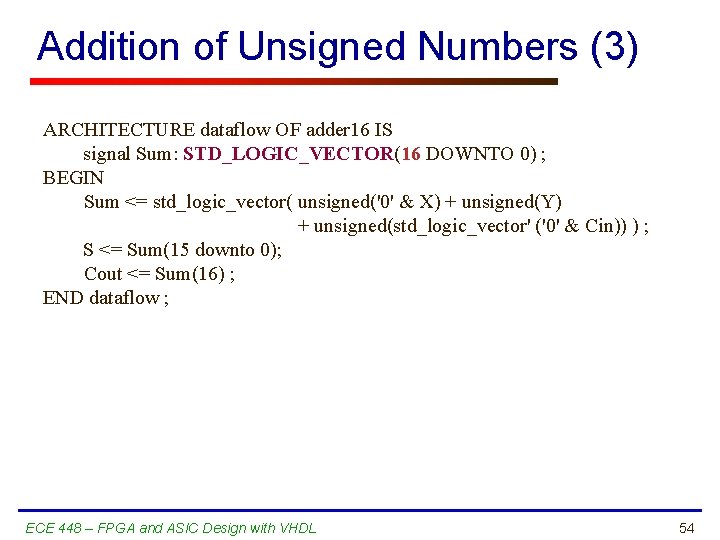

Addition of Unsigned Numbers (3) ARCHITECTURE dataflow OF adder 16 IS signal Sum: STD_LOGIC_VECTOR(16 DOWNTO 0) ; BEGIN Sum <= std_logic_vector( unsigned('0' & X) + unsigned(Y) + unsigned(std_logic_vector' ('0' & Cin)) ) ; S <= Sum(15 downto 0); Cout <= Sum(16) ; END dataflow ; ECE 448 – FPGA and ASIC Design with VHDL 54

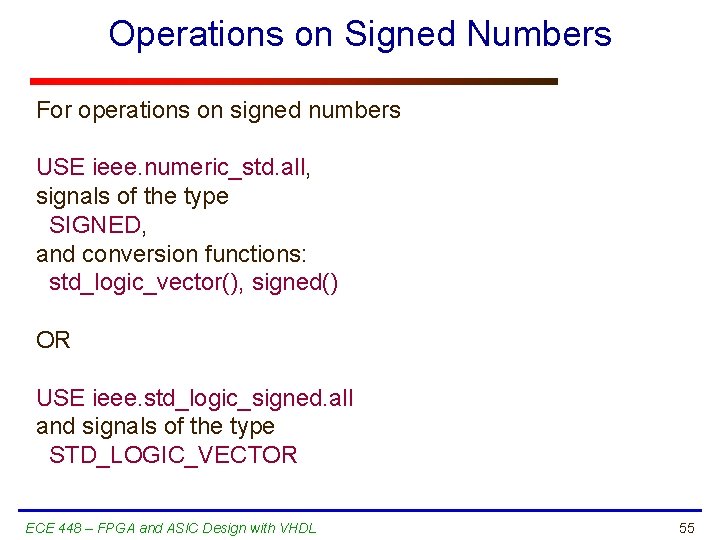

Operations on Signed Numbers For operations on signed numbers USE ieee. numeric_std. all, signals of the type SIGNED, and conversion functions: std_logic_vector(), signed() OR USE ieee. std_logic_signed. all and signals of the type STD_LOGIC_VECTOR ECE 448 – FPGA and ASIC Design with VHDL 55

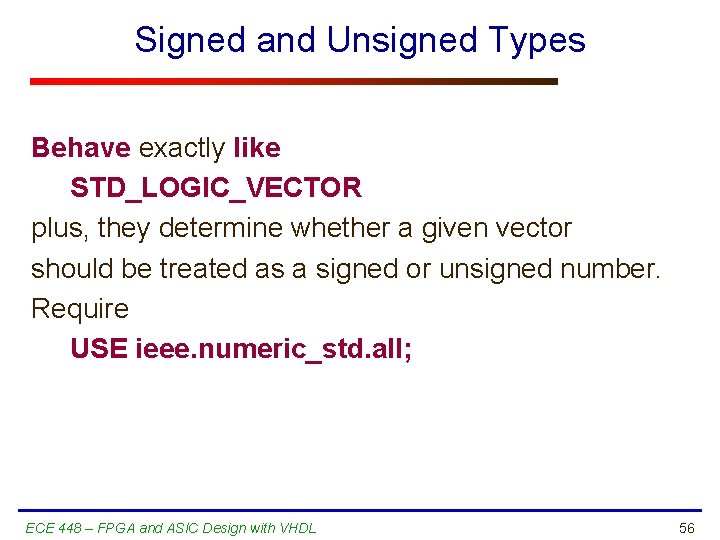

Signed and Unsigned Types Behave exactly like STD_LOGIC_VECTOR plus, they determine whether a given vector should be treated as a signed or unsigned number. Require USE ieee. numeric_std. all; ECE 448 – FPGA and ASIC Design with VHDL 56

Multipliers ECE 448 – FPGA and ASIC Design with VHDL 57

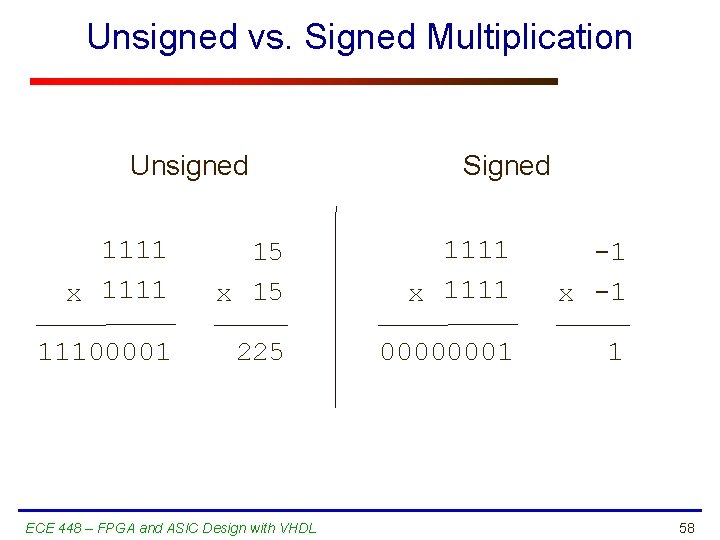

Unsigned vs. Signed Multiplication Unsigned Signed 1111 x 1111 15 x 15 1111 x 1111 -1 x -1 11100001 225 00000001 1 ECE 448 – FPGA and ASIC Design with VHDL 58

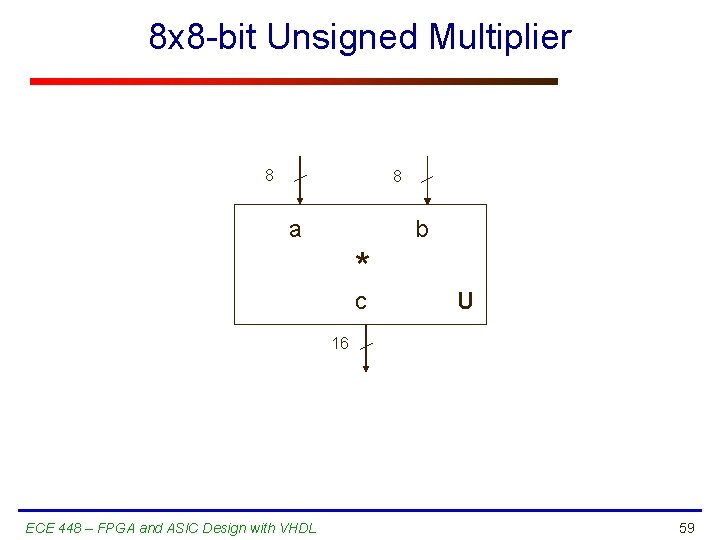

8 x 8 -bit Unsigned Multiplier 8 8 a b * c U 16 ECE 448 – FPGA and ASIC Design with VHDL 59

Multiplication of unsigned numbers LIBRARY ieee; USE ieee. std_logic_1164. all; USE ieee. std_logic_unsigned. all ; entity multiply is port( a : in STD_LOGIC_VECTOR(7 downto 0); b : in STD_LOGIC_VECTOR(7 downto 0); c : out STD_LOGIC_VECTOR(15 downto 0) ); end multiply; architecture dataflow of multiply is begin c <= a * b; end dataflow; ECE 448 – FPGA and ASIC Design with VHDL 60

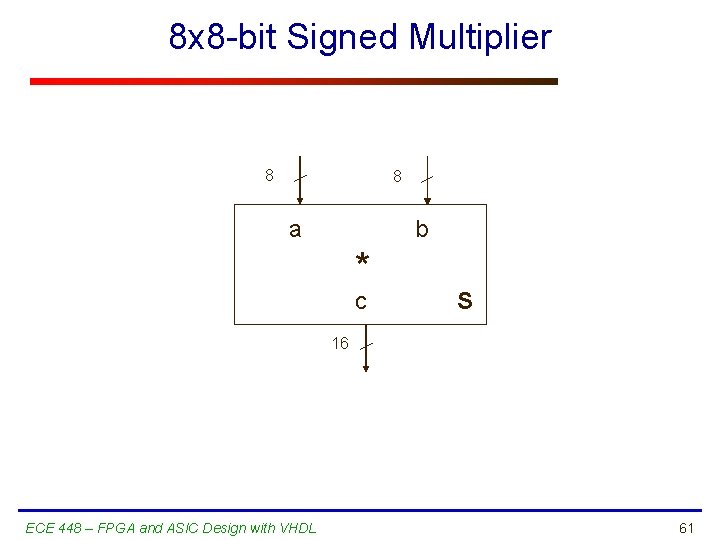

8 x 8 -bit Signed Multiplier 8 8 a b * c S 16 ECE 448 – FPGA and ASIC Design with VHDL 61

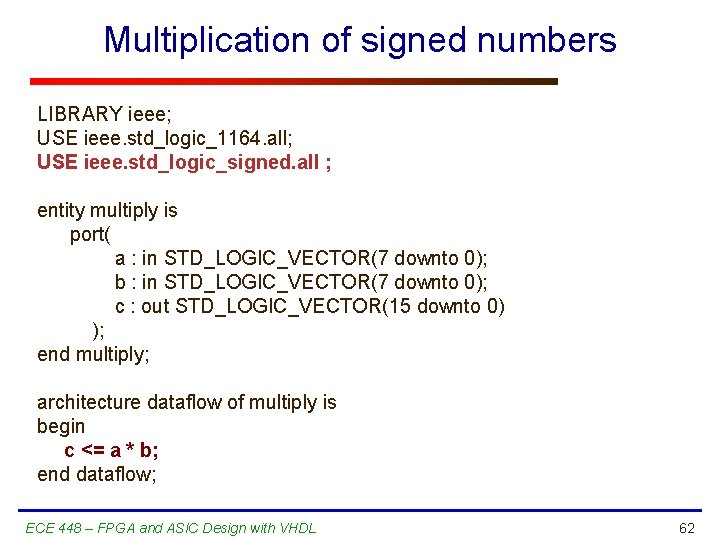

Multiplication of signed numbers LIBRARY ieee; USE ieee. std_logic_1164. all; USE ieee. std_logic_signed. all ; entity multiply is port( a : in STD_LOGIC_VECTOR(7 downto 0); b : in STD_LOGIC_VECTOR(7 downto 0); c : out STD_LOGIC_VECTOR(15 downto 0) ); end multiply; architecture dataflow of multiply is begin c <= a * b; end dataflow; ECE 448 – FPGA and ASIC Design with VHDL 62

8 x 8 -bit Unsigned and Signed Multiplier 8 8 a cu 16 ECE 448 – FPGA and ASIC Design with VHDL b * cs 16 63

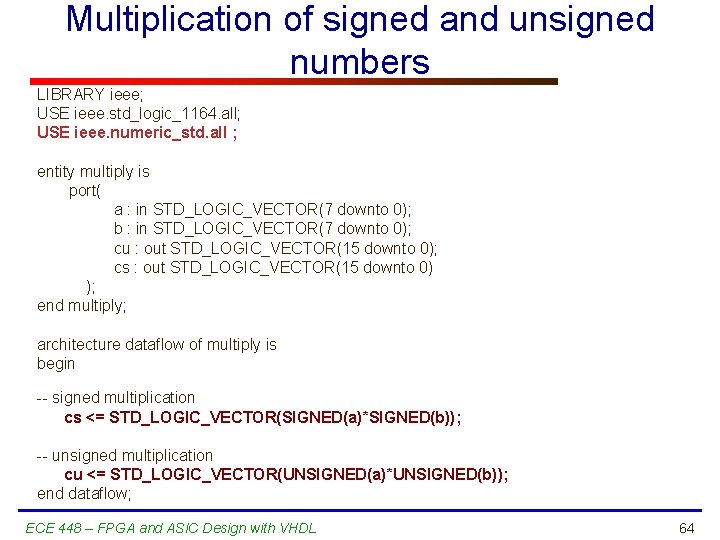

Multiplication of signed and unsigned numbers LIBRARY ieee; USE ieee. std_logic_1164. all; USE ieee. numeric_std. all ; entity multiply is port( a : in STD_LOGIC_VECTOR(7 downto 0); b : in STD_LOGIC_VECTOR(7 downto 0); cu : out STD_LOGIC_VECTOR(15 downto 0); cs : out STD_LOGIC_VECTOR(15 downto 0) ); end multiply; architecture dataflow of multiply is begin -- signed multiplication cs <= STD_LOGIC_VECTOR(SIGNED(a)*SIGNED(b)); -- unsigned multiplication cu <= STD_LOGIC_VECTOR(UNSIGNED(a)*UNSIGNED(b)); end dataflow; ECE 448 – FPGA and ASIC Design with VHDL 64

Comparators ECE 448 – FPGA and ASIC Design with VHDL 65

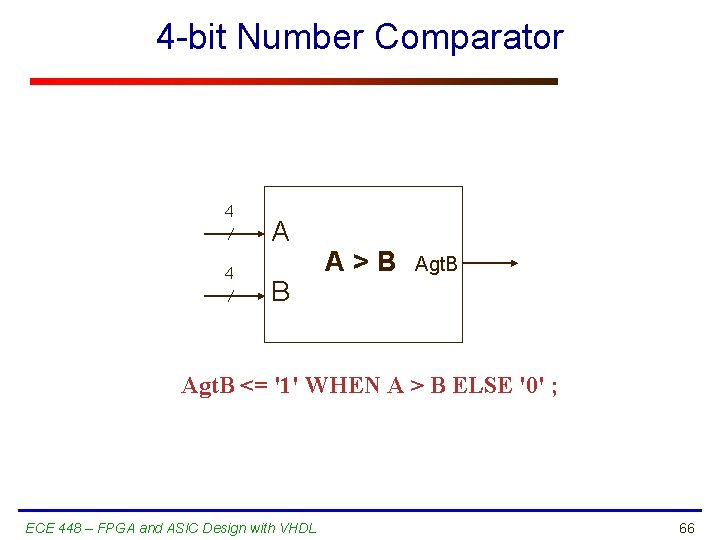

4 -bit Number Comparator 4 4 A B A>B Agt. B <= '1' WHEN A > B ELSE '0' ; ECE 448 – FPGA and ASIC Design with VHDL 66

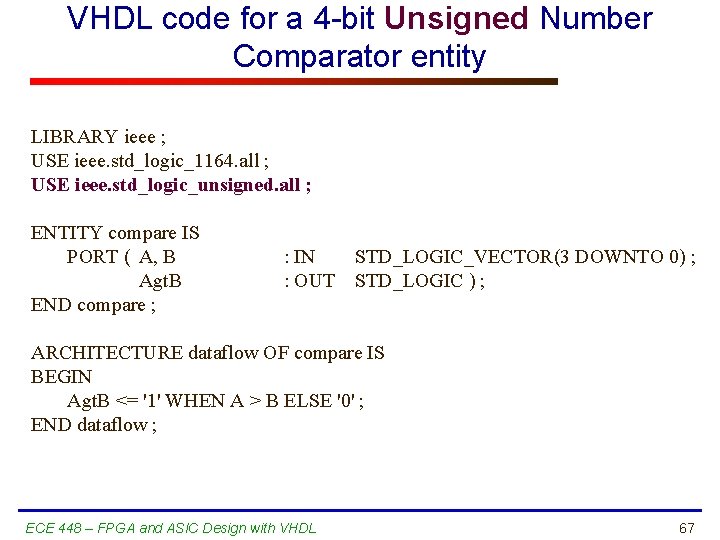

VHDL code for a 4 -bit Unsigned Number Comparator entity LIBRARY ieee ; USE ieee. std_logic_1164. all ; USE ieee. std_logic_unsigned. all ; ENTITY compare IS PORT ( A, B Agt. B END compare ; : IN STD_LOGIC_VECTOR(3 DOWNTO 0) ; : OUT STD_LOGIC ) ; ARCHITECTURE dataflow OF compare IS BEGIN Agt. B <= '1' WHEN A > B ELSE '0' ; END dataflow ; ECE 448 – FPGA and ASIC Design with VHDL 67

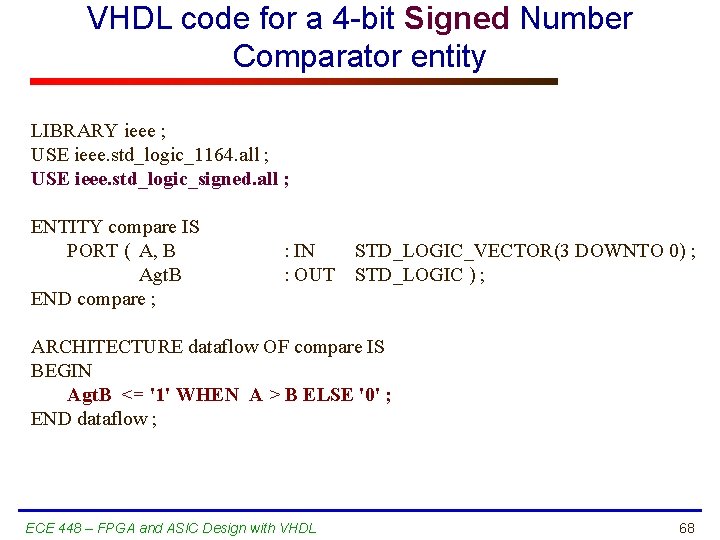

VHDL code for a 4 -bit Signed Number Comparator entity LIBRARY ieee ; USE ieee. std_logic_1164. all ; USE ieee. std_logic_signed. all ; ENTITY compare IS PORT ( A, B Agt. B END compare ; : IN STD_LOGIC_VECTOR(3 DOWNTO 0) ; : OUT STD_LOGIC ) ; ARCHITECTURE dataflow OF compare IS BEGIN Agt. B <= '1' WHEN A > B ELSE '0' ; END dataflow ; ECE 448 – FPGA and ASIC Design with VHDL 68

Buffers ECE 448 – FPGA and ASIC Design with VHDL 69

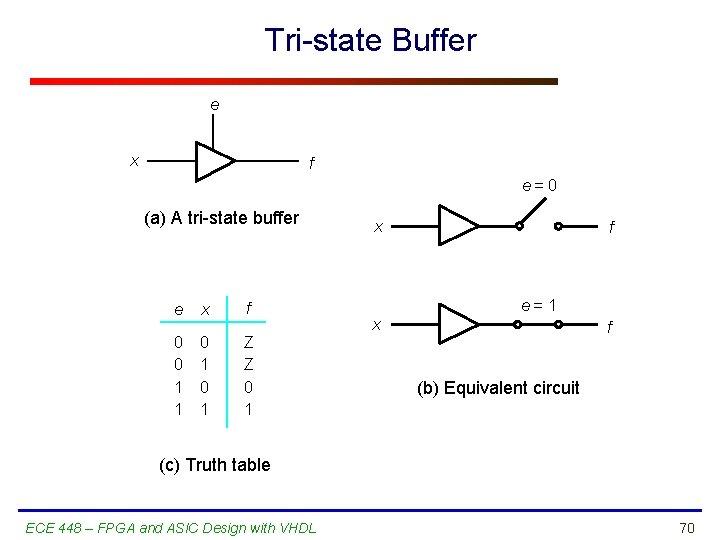

Tri-state Buffer e x f e= 0 (a) A tri-state buffer e x f 0 0 1 1 Z Z 0 1 0 1 x x f e= 1 f (b) Equivalent circuit (c) Truth table ECE 448 – FPGA and ASIC Design with VHDL 70

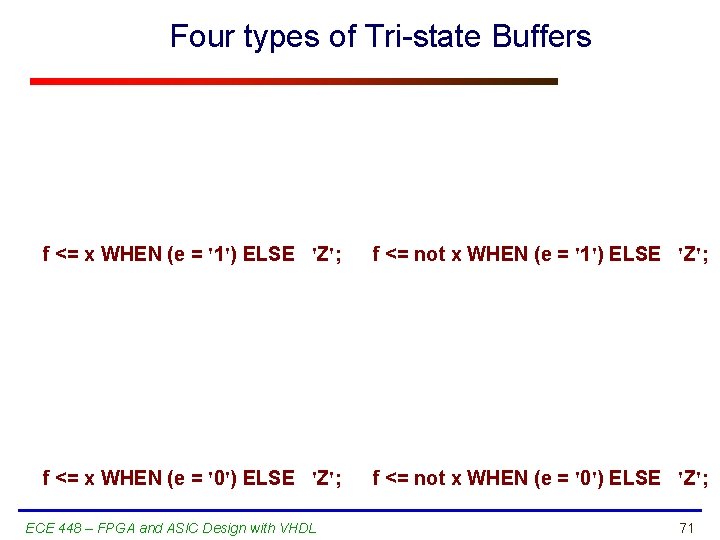

Four types of Tri-state Buffers f <= x WHEN (e = '1') ELSE 'Z'; f <= not x WHEN (e = '1') ELSE 'Z'; f <= x WHEN (e = '0') ELSE 'Z'; f <= not x WHEN (e = '0') ELSE 'Z'; ECE 448 – FPGA and ASIC Design with VHDL 71

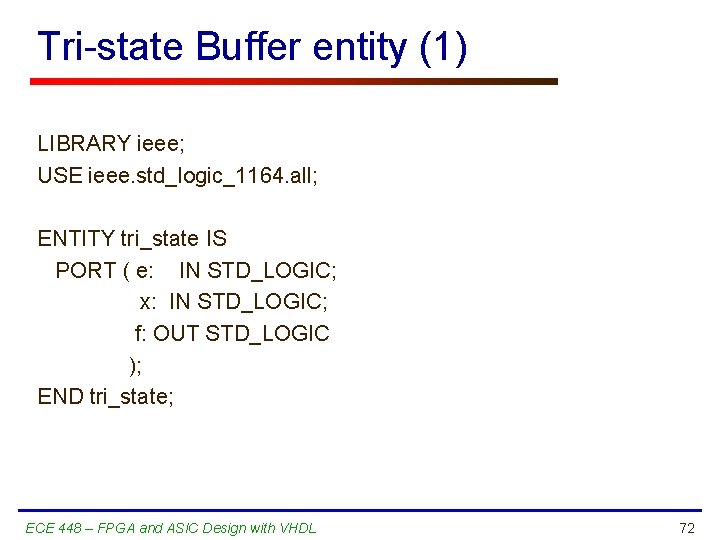

Tri-state Buffer entity (1) LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY tri_state IS PORT ( e: IN STD_LOGIC; x: IN STD_LOGIC; f: OUT STD_LOGIC ); END tri_state; ECE 448 – FPGA and ASIC Design with VHDL 72

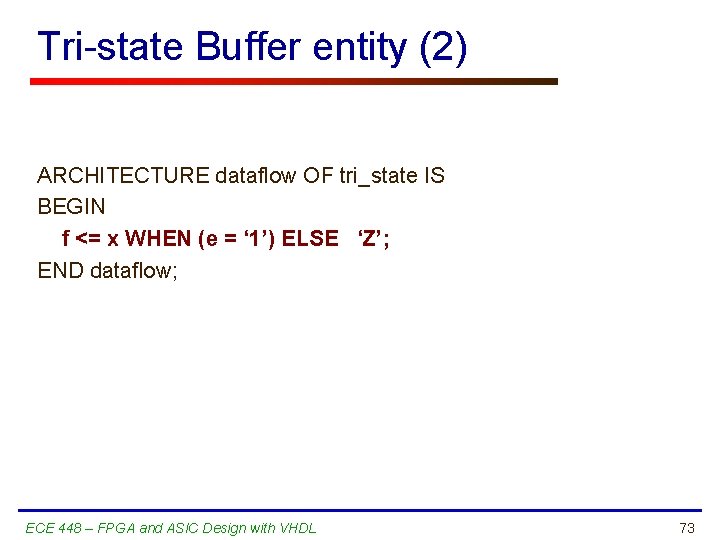

Tri-state Buffer entity (2) ARCHITECTURE dataflow OF tri_state IS BEGIN f <= x WHEN (e = ‘ 1’) ELSE ‘Z’; END dataflow; ECE 448 – FPGA and ASIC Design with VHDL 73

ROM ECE 448 – FPGA and ASIC Design with VHDL 74

ROM 8 x 16 example (1) 3 Addr 8 x 16 ROM Dout 16 C ECE 448 – FPGA and ASIC Design with VHDL 75

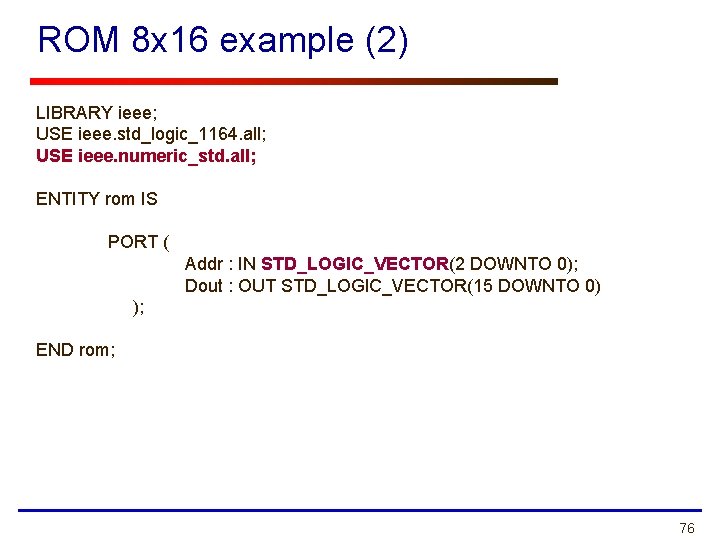

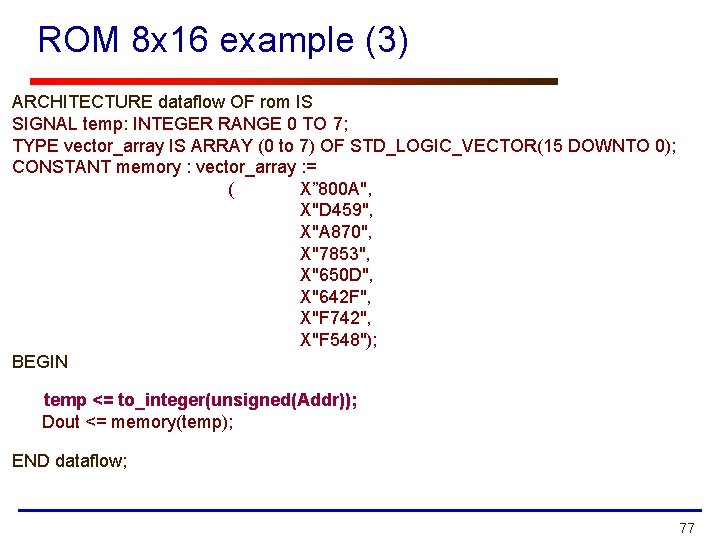

ROM 8 x 16 example (2) LIBRARY ieee; USE ieee. std_logic_1164. all; USE ieee. numeric_std. all; ENTITY rom IS PORT ( Addr : IN STD_LOGIC_VECTOR(2 DOWNTO 0); Dout : OUT STD_LOGIC_VECTOR(15 DOWNTO 0) ); END rom; 76

ROM 8 x 16 example (3) ARCHITECTURE dataflow OF rom IS SIGNAL temp: INTEGER RANGE 0 TO 7; TYPE vector_array IS ARRAY (0 to 7) OF STD_LOGIC_VECTOR(15 DOWNTO 0); CONSTANT memory : vector_array : = ( X” 800 A", X"D 459", X"A 870", X"7853", X"650 D", X"642 F", X"F 742", X"F 548"); BEGIN temp <= to_integer(unsigned(Addr)); Dout <= memory(temp); END dataflow; 77

Describing Combinational Logic Using Dataflow Design Style ECE 448 – FPGA and ASIC Design with VHDL 78

MLU Example ECE 448 – FPGA and ASIC Design with VHDL 79

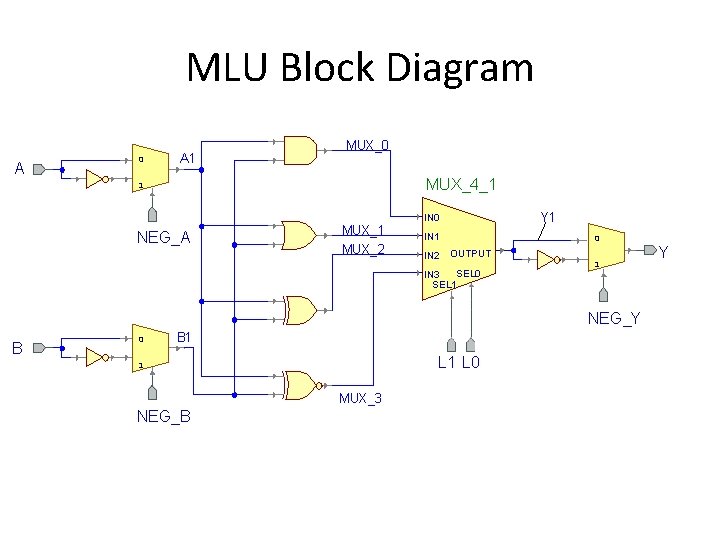

MLU Block Diagram A 0 A 1 MUX_0 MUX_4_1 1 NEG_A MUX_1 MUX_2 Y 1 IN 0 IN 1 IN 2 0 OUTPUT SEL 0 IN 3 SEL 1 1 NEG_Y B 0 B 1 L 0 1 MUX_3 NEG_B Y

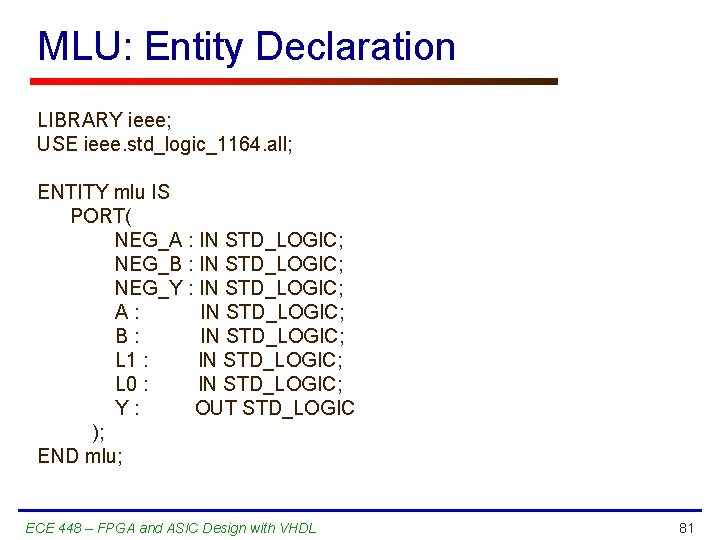

MLU: Entity Declaration LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY mlu IS PORT( NEG_A : IN STD_LOGIC; NEG_B : IN STD_LOGIC; NEG_Y : IN STD_LOGIC; A: IN STD_LOGIC; B: IN STD_LOGIC; L 1 : IN STD_LOGIC; L 0 : IN STD_LOGIC; Y: OUT STD_LOGIC ); END mlu; ECE 448 – FPGA and ASIC Design with VHDL 81

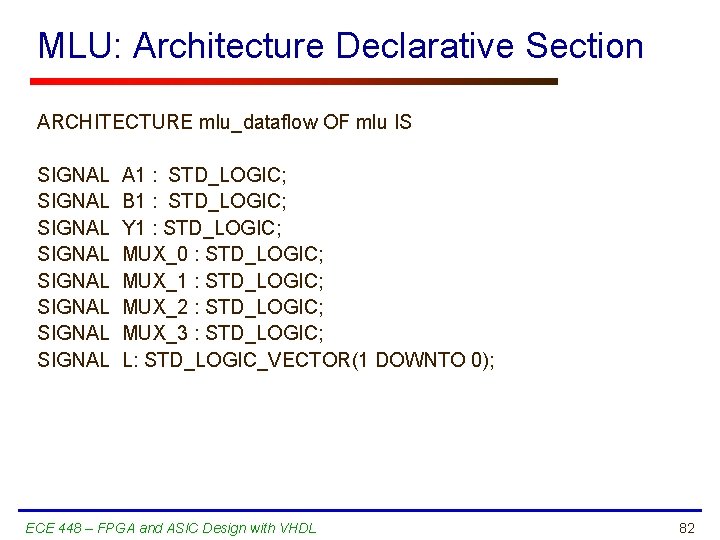

MLU: Architecture Declarative Section ARCHITECTURE mlu_dataflow OF mlu IS SIGNAL SIGNAL A 1 : STD_LOGIC; B 1 : STD_LOGIC; Y 1 : STD_LOGIC; MUX_0 : STD_LOGIC; MUX_1 : STD_LOGIC; MUX_2 : STD_LOGIC; MUX_3 : STD_LOGIC; L: STD_LOGIC_VECTOR(1 DOWNTO 0); ECE 448 – FPGA and ASIC Design with VHDL 82

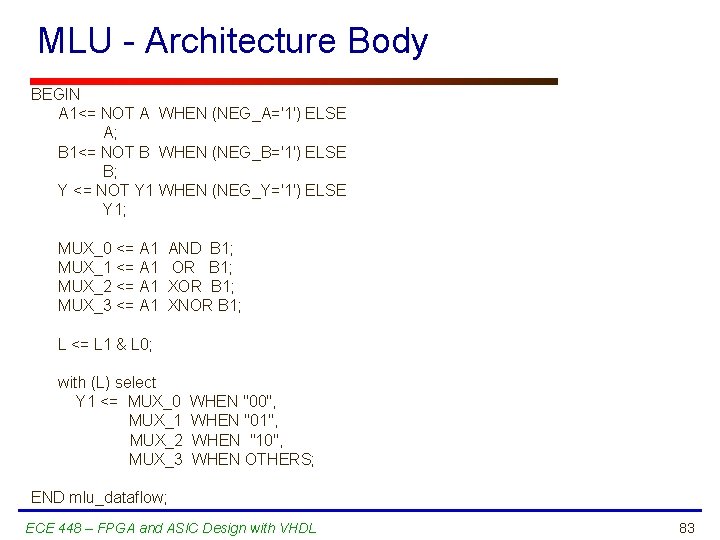

MLU - Architecture Body BEGIN A 1<= NOT A WHEN (NEG_A='1') ELSE A; B 1<= NOT B WHEN (NEG_B='1') ELSE B; Y <= NOT Y 1 WHEN (NEG_Y='1') ELSE Y 1; MUX_0 <= A 1 MUX_1 <= A 1 MUX_2 <= A 1 MUX_3 <= A 1 AND B 1; OR B 1; XNOR B 1; L <= L 1 & L 0; with (L) select Y 1 <= MUX_0 MUX_1 MUX_2 MUX_3 WHEN "00", WHEN "01", WHEN "10", WHEN OTHERS; END mlu_dataflow; ECE 448 – FPGA and ASIC Design with VHDL 83

Logic Implied Most Often by Conditional and Selected Concurrent Signal Assignments ECE 448 – FPGA and ASIC Design with VHDL 84

Data-flow VHDL Major instructions Concurrent statements • • • concurrent signal assignment ( ) conditional concurrent signal assignment (when-else) selected concurrent signal assignment (with-select-when) ECE 448 – FPGA and ASIC Design with VHDL 85

Conditional concurrent signal assignment When - Else target_signal <= value 1 when condition 1 else value 2 when condition 2 else. . . value. N-1 when condition. N-1 else value. N; ECE 448 – FPGA and ASIC Design with VHDL 86

Most often implied structure When - Else target_signal <= value 1 when condition 1 else value 2 when condition 2 else. . . value. N-1 when condition. N-1 else value. N; Value N-1 0 1 . … … 0 1 Value 2 Target Signal Value 1 Condition N-1 Condition 2 Condition 1 ECE 448 – FPGA and ASIC Design with VHDL 87

Data-flow VHDL Major instructions Concurrent statements • • • concurrent signal assignment ( ) conditional concurrent signal assignment (when-else) selected concurrent signal assignment (with-select-when) ECE 448 – FPGA and ASIC Design with VHDL 88

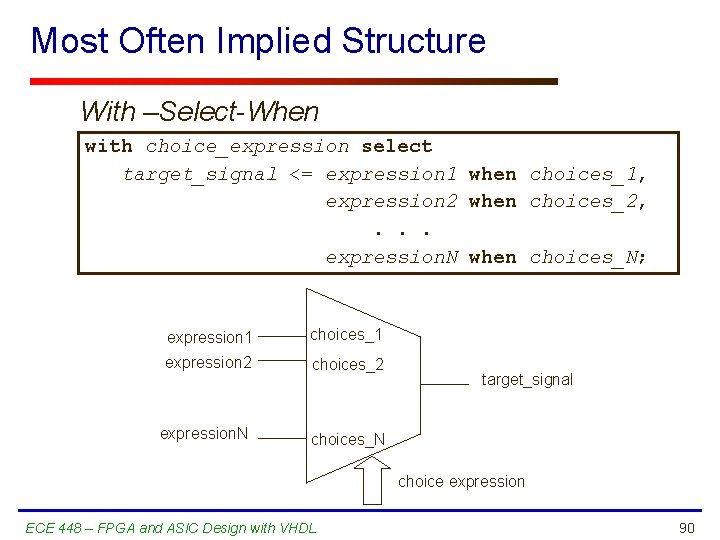

Selected concurrent signal assignment With –Select-When with choice_expression select target_signal <= expression 1 when choices_1, expression 2 when choices_2, . . . expression. N when choices_N; ECE 448 – FPGA and ASIC Design with VHDL 89

Most Often Implied Structure With –Select-When with choice_expression select target_signal <= expression 1 when choices_1, expression 2 when choices_2, . . . expression. N when choices_N; expression 1 choices_1 expression 2 choices_2 expression. N choices_N target_signal choice expression ECE 448 – FPGA and ASIC Design with VHDL 90

Allowed formats of choices_k WHEN value_1 | value_2 |. . | value N WHEN OTHERS ECE 448 – FPGA and ASIC Design with VHDL 91

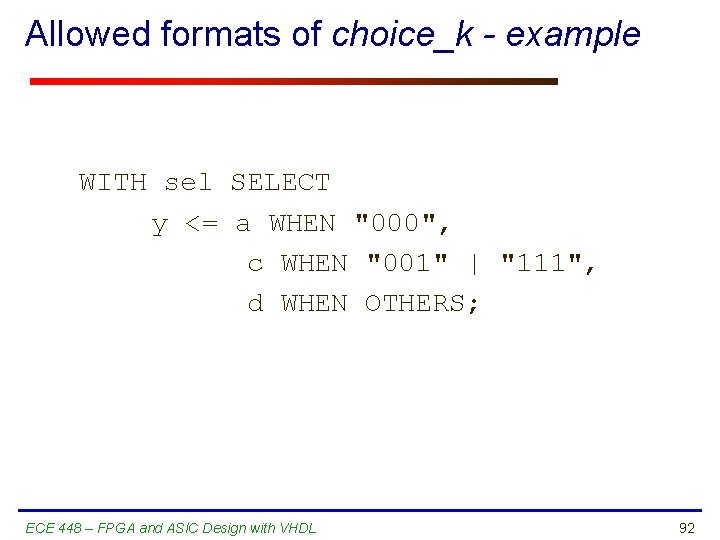

Allowed formats of choice_k - example WITH sel SELECT y <= a WHEN "000", c WHEN "001" | "111", d WHEN OTHERS; ECE 448 – FPGA and ASIC Design with VHDL 92

when-else vs. with-select-when (1) "when-else" should be used when: 1) there is only one condition (and thus, only one else), as in the 2 -to-1 MUX 2) conditions are independent of each other (e. g. , they test values of different signals) 3) conditions reflect priority (as in priority encoder); one with the highest priority need to be tested first. ECE 448 – FPGA and ASIC Design with VHDL 93

when-else vs. with-select-when (2) "with-select-when" should be used when there is 1) more than one condition 2) conditions are closely related to each other (e. g. , represent different ranges of values of the same signal) 3) all conditions have the same priority (as in the 4 -to-1 MUX). ECE 448 – FPGA and ASIC Design with VHDL 94

- Slides: 94