ECE 448 Lecture 17 ASIC vs FPGA ECE

- Slides: 35

ECE 448 Lecture 17 ASIC vs. FPGA ECE 448 – FPGA and ASIC Design with VHDL George Mason University

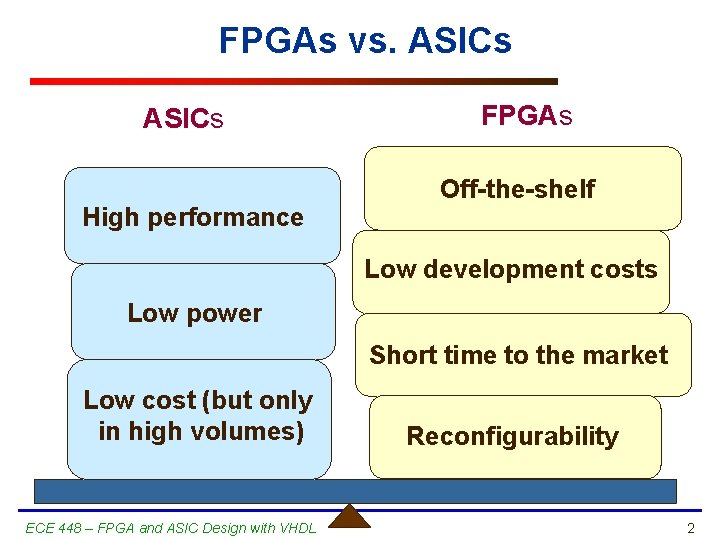

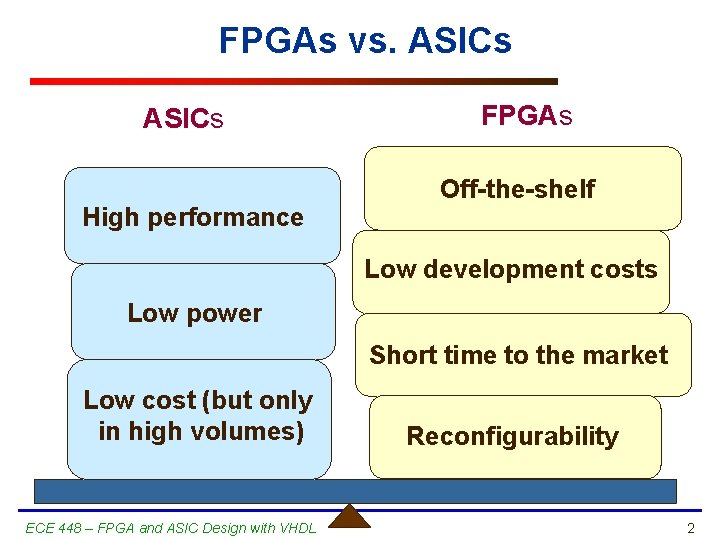

FPGAs vs. ASICs High performance FPGAs Off-the-shelf Low development costs Low power Short time to the market Low cost (but only in high volumes) ECE 448 – FPGA and ASIC Design with VHDL Reconfigurability 2

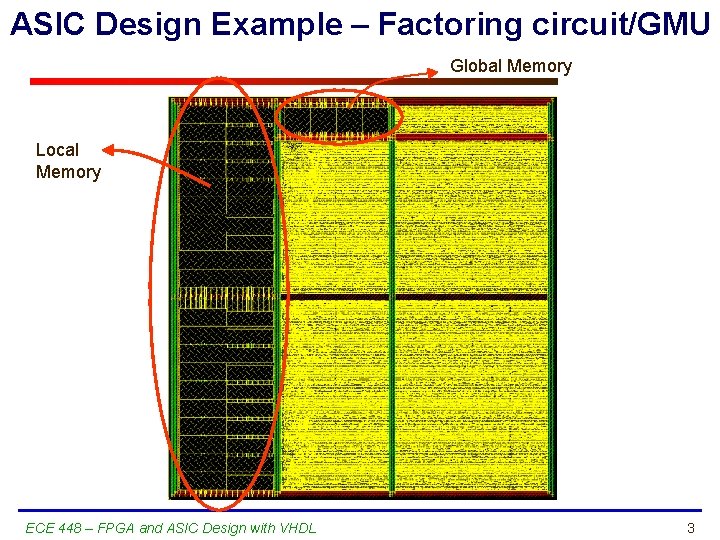

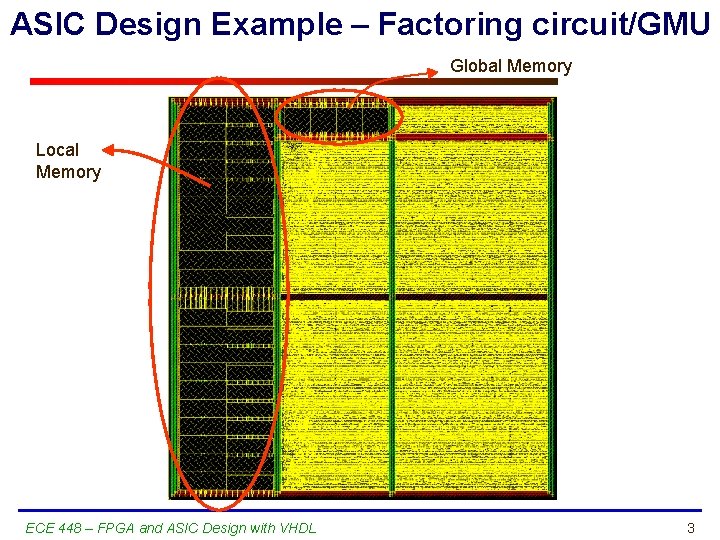

ASIC Design Example – Factoring circuit/GMU Global Memory Local Memory ECE 448 – FPGA and ASIC Design with VHDL 3

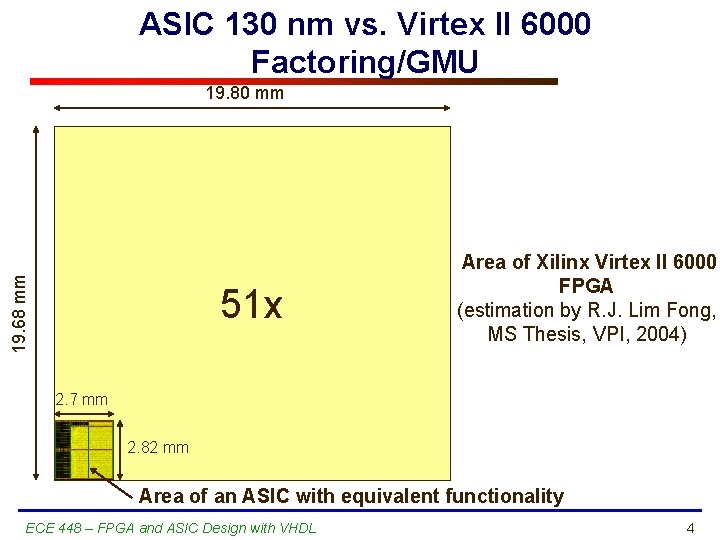

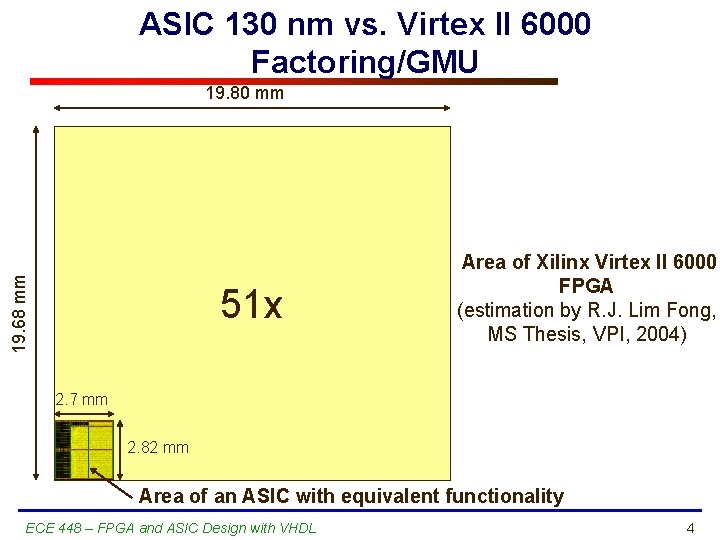

ASIC 130 nm vs. Virtex II 6000 Factoring/GMU 19. 68 mm 19. 80 mm 51 x Area of Xilinx Virtex II 6000 FPGA (estimation by R. J. Lim Fong, MS Thesis, VPI, 2004) 2. 7 mm 2. 82 mm Area of an ASIC with equivalent functionality ECE 448 – FPGA and ASIC Design with VHDL 4

ASICs vs. FPGAs Source: I. Kuon, J. Rose, University of Toronto “Measuring the Gap Between FPGAs and ASICs” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 62, no. 2, Feb 2007. ECE 448 – FPGA and ASIC Design with VHDL 5

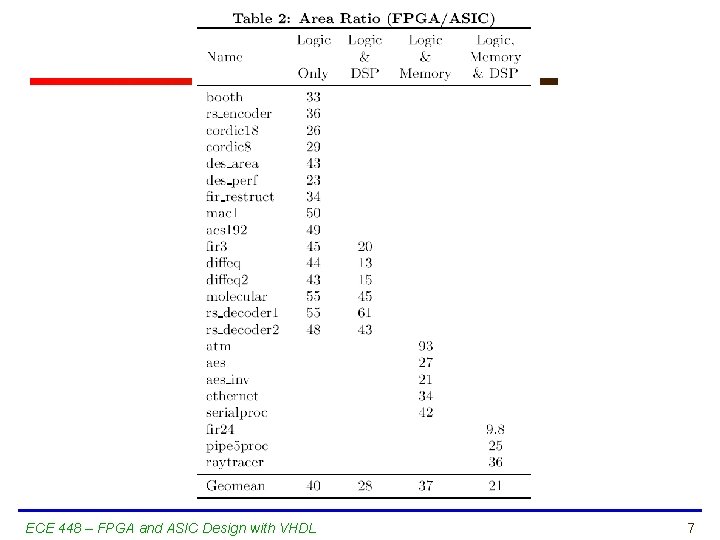

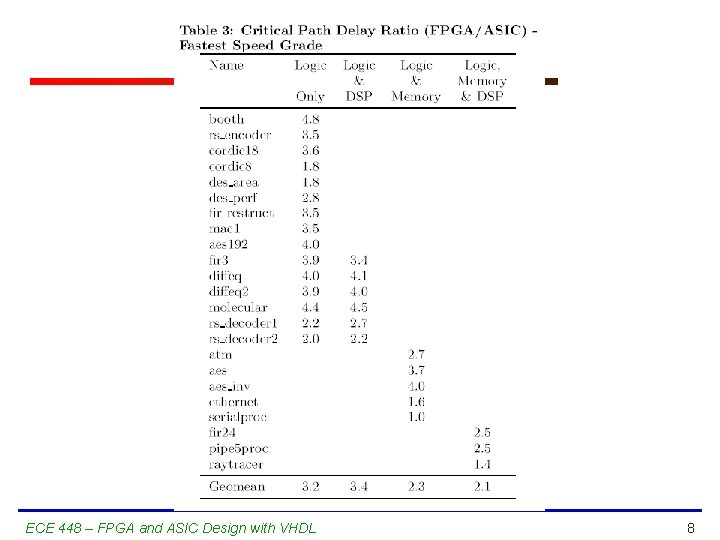

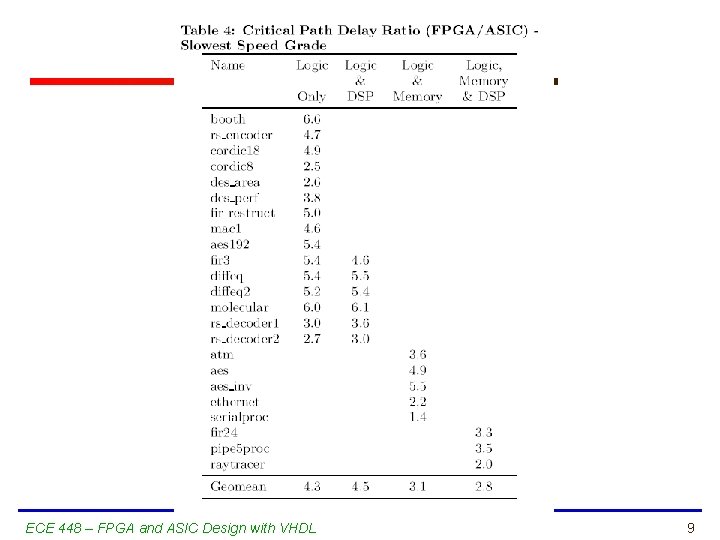

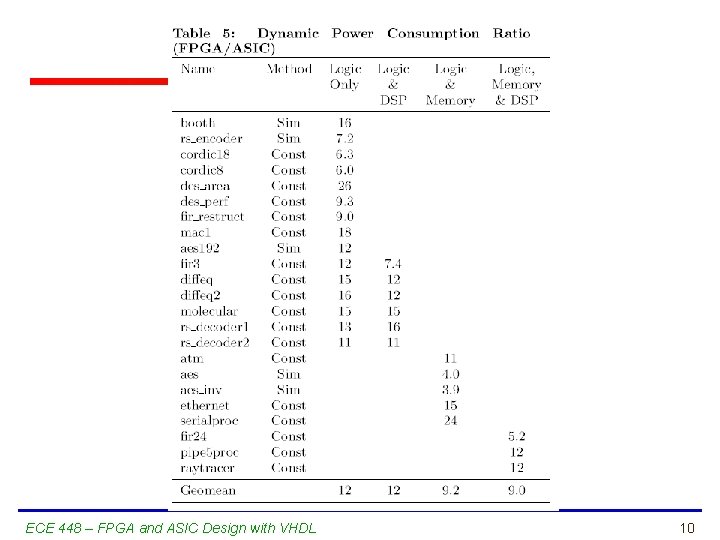

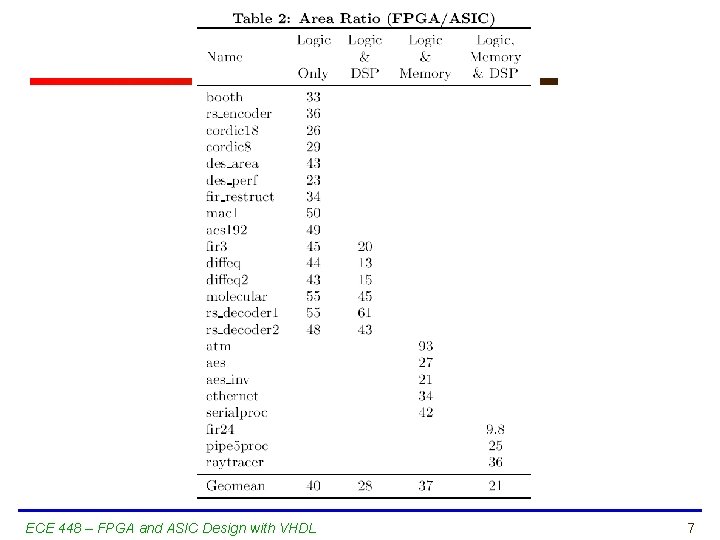

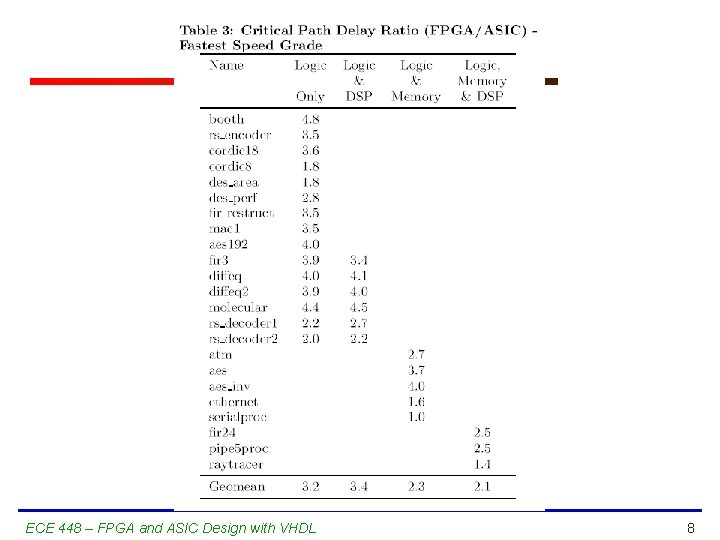

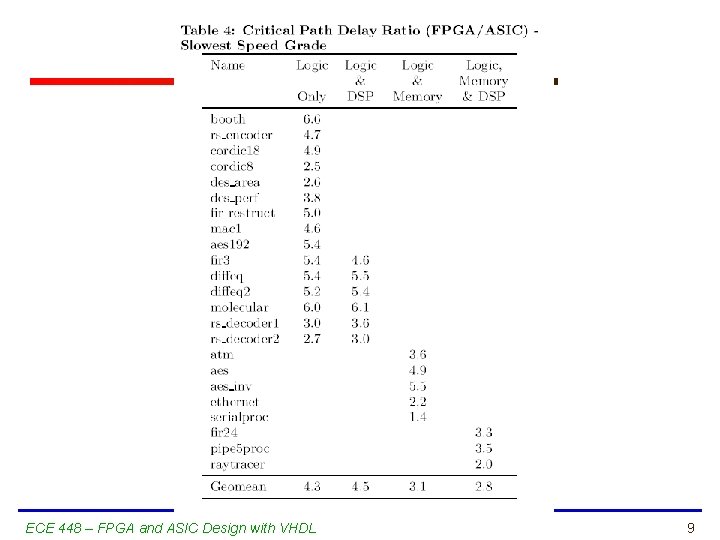

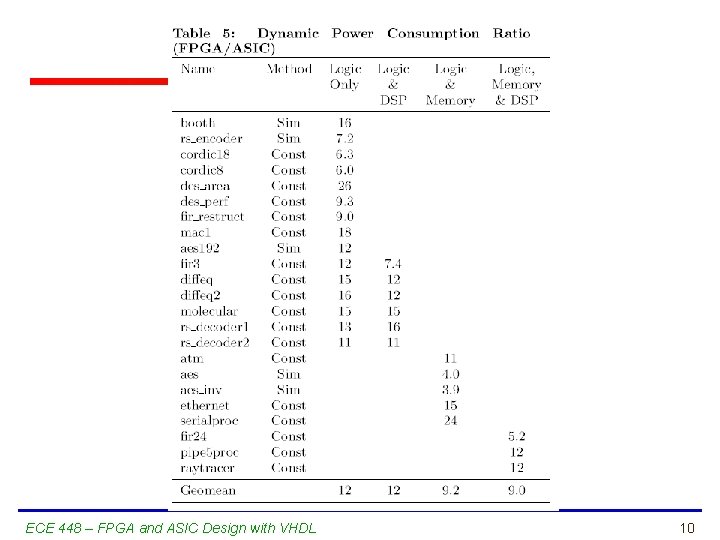

ASICs vs. FPGAs 23 representative circuits implemented using FPGAs and ASICs - computer arithmetic (booth, cordic 18, cordic 8, etc. ) - digital signal processing (rs_encoder, fir 3, fir 24, etc. ) - communications (ethernet, mac 1, atm, etc. ) - cryptography (des_area, des_perf, aes 192, etc. ) - scientific computations (molecular, raytracer, etc. ) ECE 448 – FPGA and ASIC Design with VHDL 6

ECE 448 – FPGA and ASIC Design with VHDL 7

ECE 448 – FPGA and ASIC Design with VHDL 8

ECE 448 – FPGA and ASIC Design with VHDL 9

ECE 448 – FPGA and ASIC Design with VHDL 10

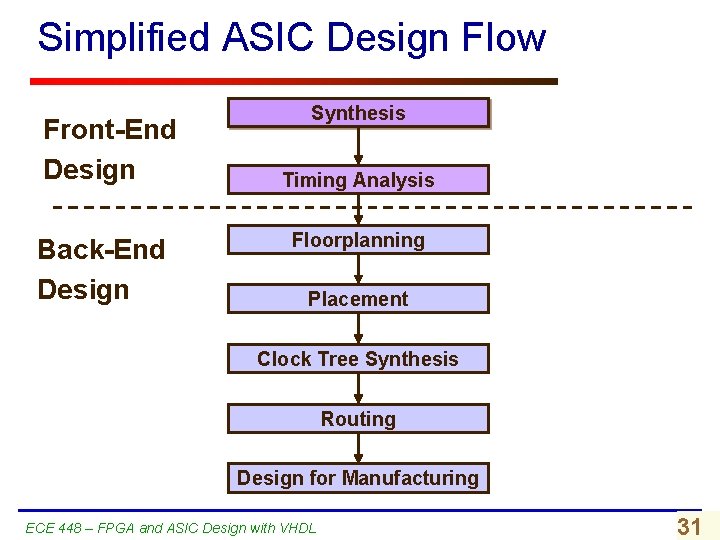

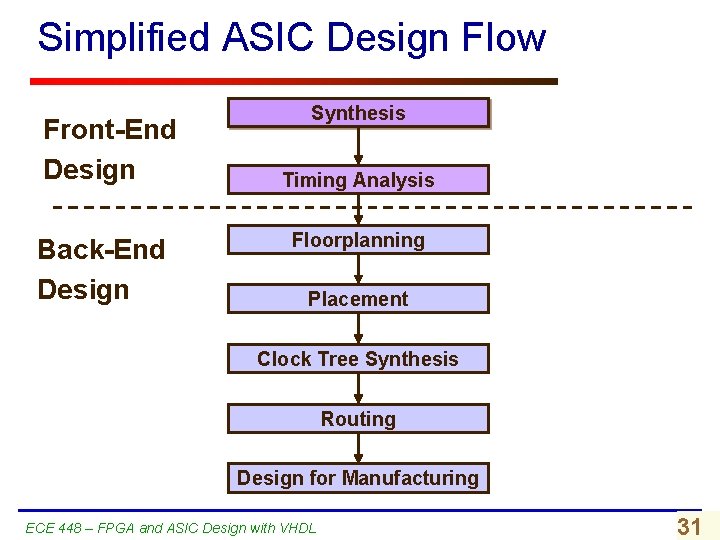

Simplified ASIC Design Flow Front-End Design Back-End Design Synthesis Timing Analysis Floorplanning Placement Clock Tree Synthesis Routing Design for Manufacturing ECE 448 – FPGA and ASIC Design with VHDL 11 31

Major ASIC Toolsets Cadence Magma ECE 448 – FPGA and ASIC Design with VHDL 12

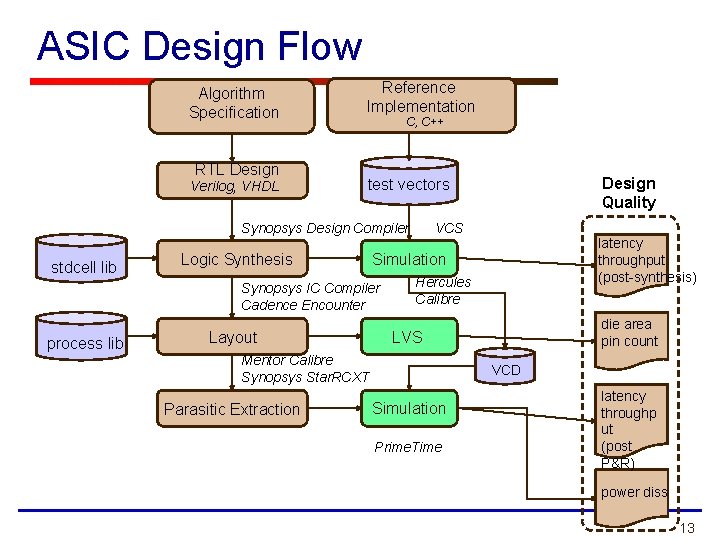

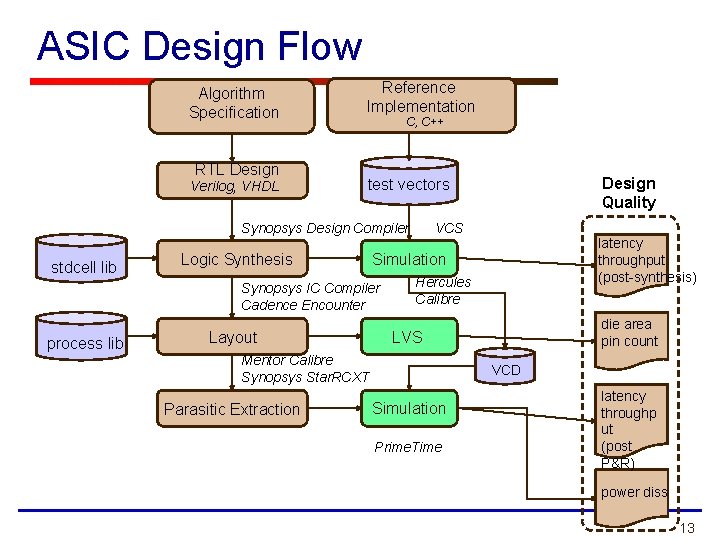

ASIC Design Flow Algorithm Specification RTL Design Verilog, VHDL Reference Implementation C, C++ Synopsys Design Compiler stdcell lib Logic Synthesis Layout VCS Hercules Calibre die area pin count LVS Mentor Calibre Synopsys Star. RCXT Parasitic Extraction latency throughput (post-synthesis) Simulation Synopsys IC Compiler Cadence Encounter process lib Design Quality test vectors VCD Simulation Prime. Time latency throughp ut (post P&R) power diss 13

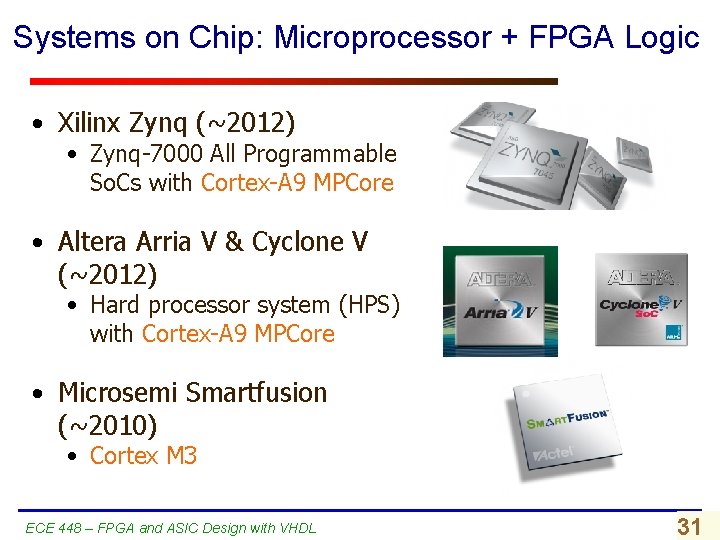

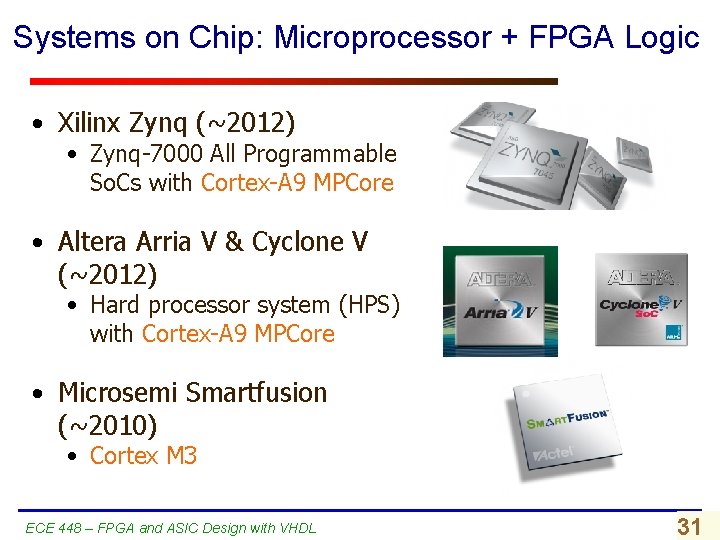

Systems on Chip: Microprocessor + FPGA Logic • Xilinx Zynq (~2012) • Zynq-7000 All Programmable So. Cs with Cortex-A 9 MPCore • Altera Arria V & Cyclone V (~2012) • Hard processor system (HPS) with Cortex-A 9 MPCore • Microsemi Smartfusion (~2010) • Cortex M 3 ECE 448 – FPGA and ASIC Design with VHDL 14 31

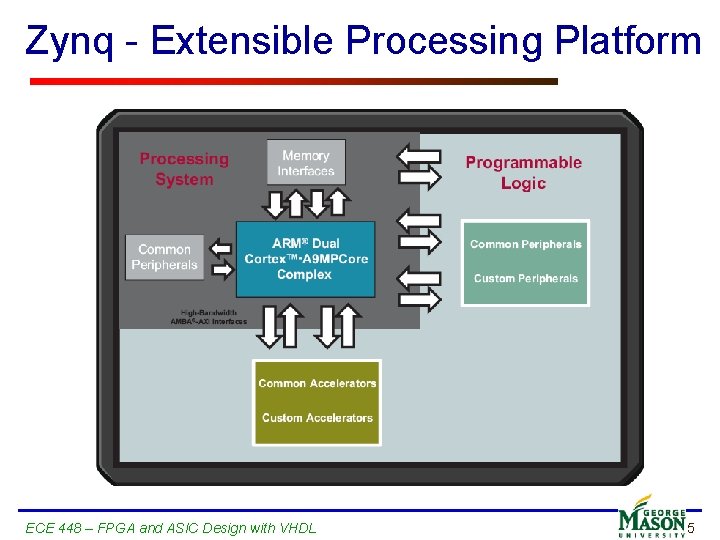

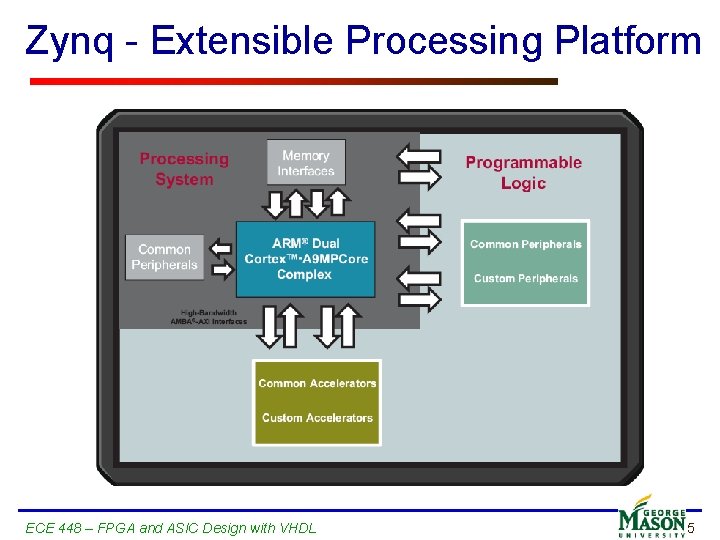

Zynq - Extensible Processing Platform ECE 448 – FPGA and ASIC Design with VHDL 15

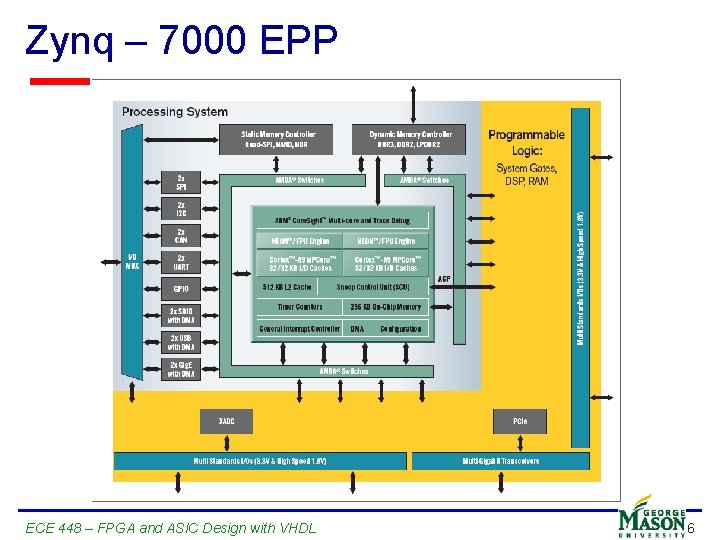

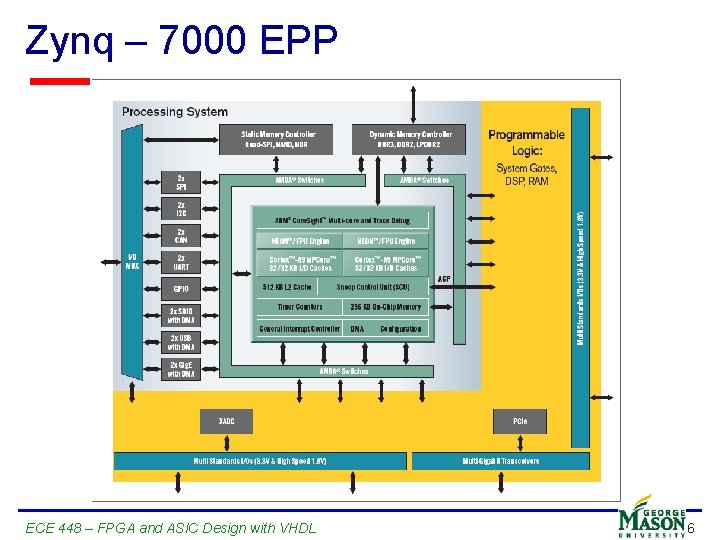

Zynq – 7000 EPP ECE 448 – FPGA and ASIC Design with VHDL 16

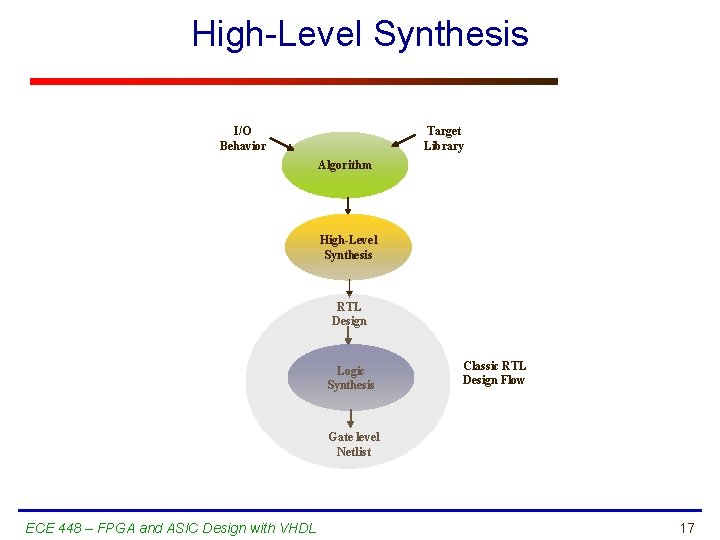

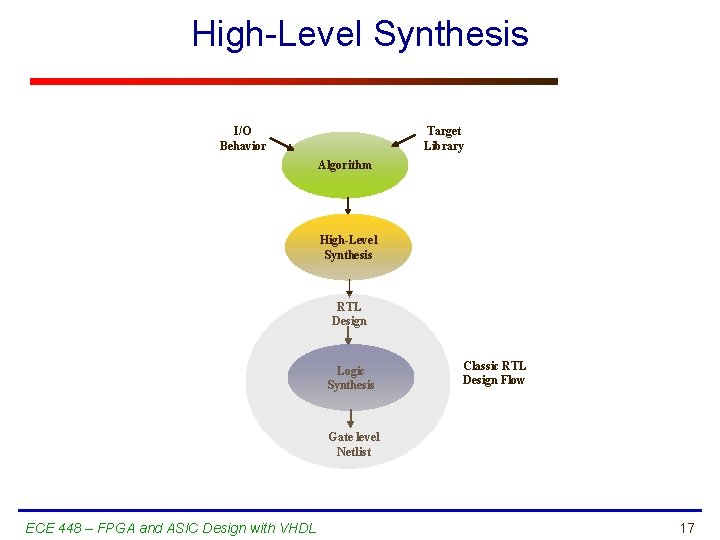

High-Level Synthesis I/O Behavior Target Library Algorithm High-Level Synthesis RTL Design Logic Synthesis Classic RTL Design Flow Gate level Netlist ECE 448 – FPGA and ASIC Design with VHDL 17

Need for High-Level Synthesis • • • Higher level of abstraction Modeling complex designs Reduce design efforts Fast turnaround time Technology independence Ease of HW/SW partitioning ECE 448 – FPGA and ASIC Design with VHDL 18

Advantages of High-Level Synthesis • • • Easy to model higher level of complexities Smaller in size source compared to RTL code Generates RTL much faster than manual method Multi-cycle functionality Loops Memory Access ECE 448 – FPGA and ASIC Design with VHDL 19

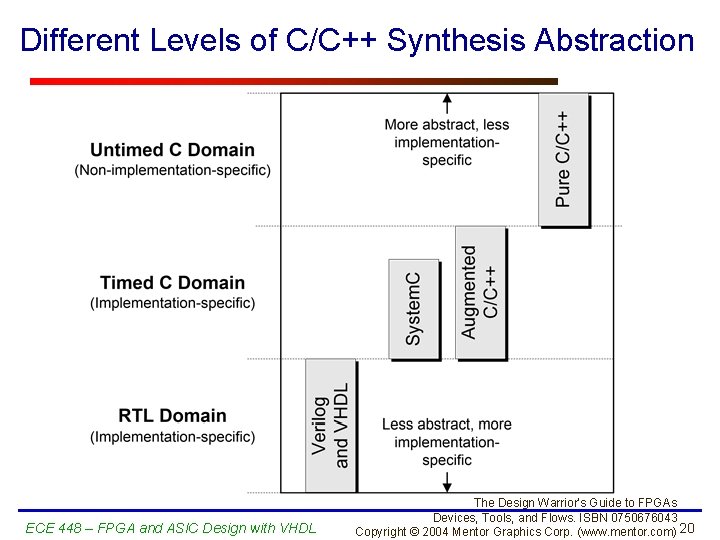

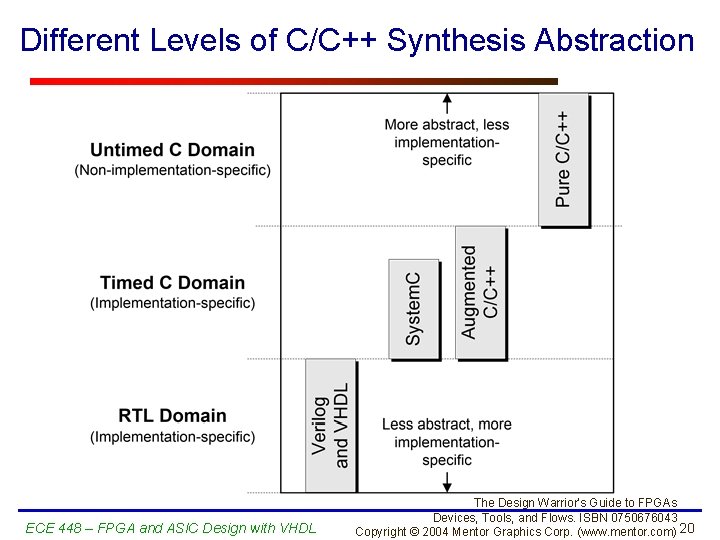

Different Levels of C/C++ Synthesis Abstraction ECE 448 – FPGA and ASIC Design with VHDL The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com) 20

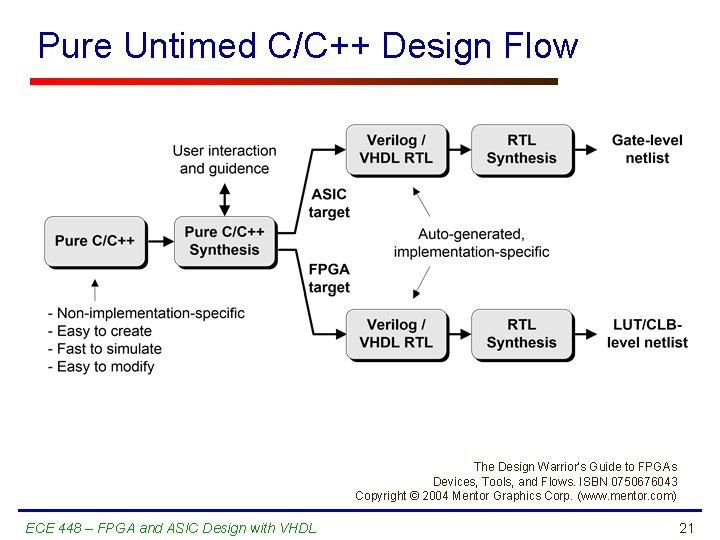

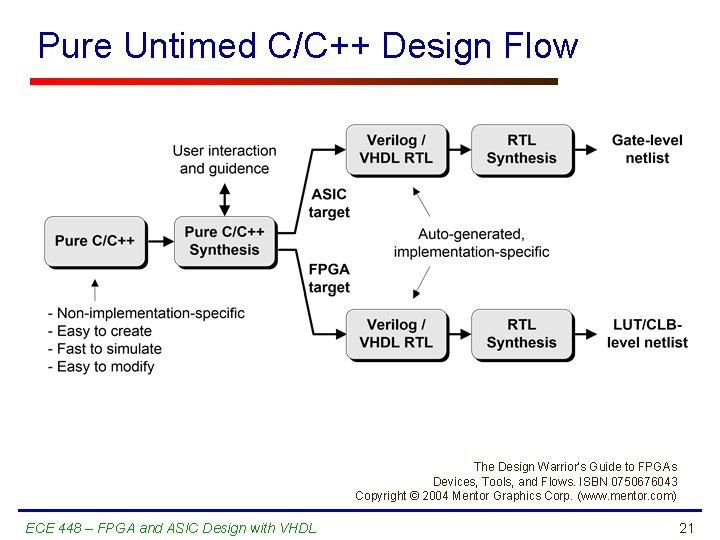

Pure Untimed C/C++ Design Flow The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com) ECE 448 – FPGA and ASIC Design with VHDL 21

Program Entry Program ECE 448 – FPGA and ASIC Design with VHDL 22

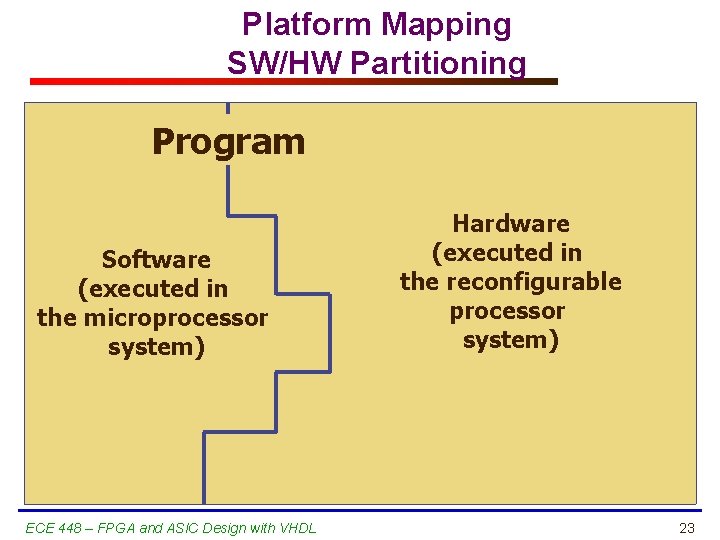

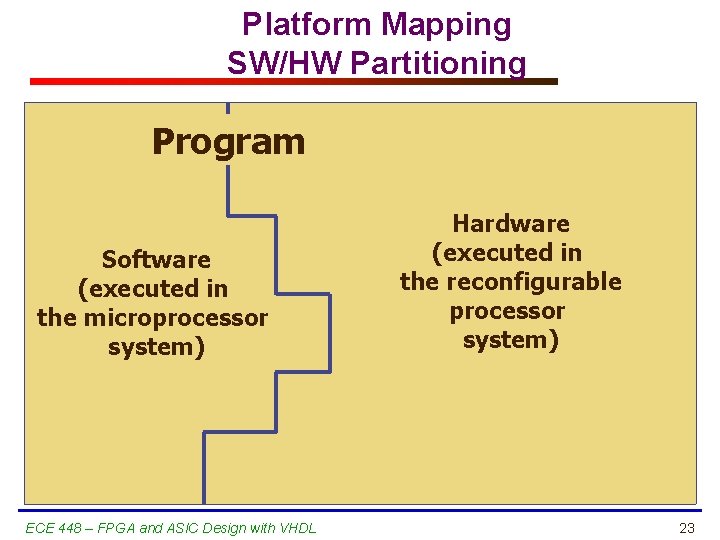

Platform Mapping SW/HW Partitioning Program Software (executed in the microprocessor system) ECE 448 – FPGA and ASIC Design with VHDL Hardware (executed in the reconfigurable processor system) 23

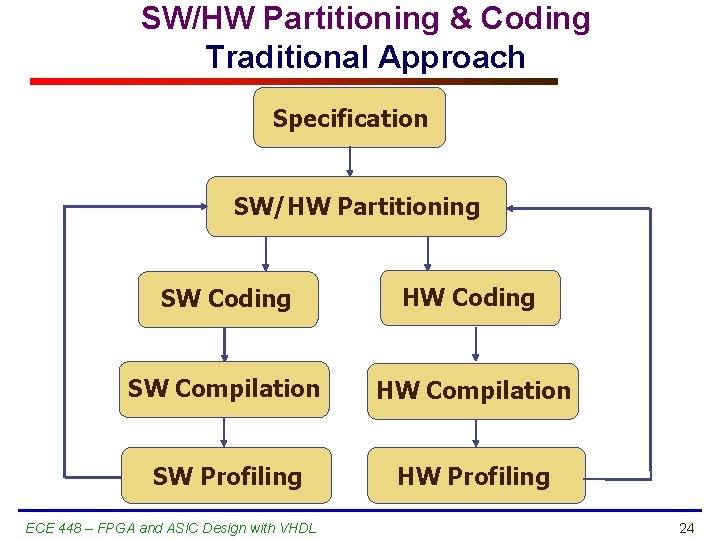

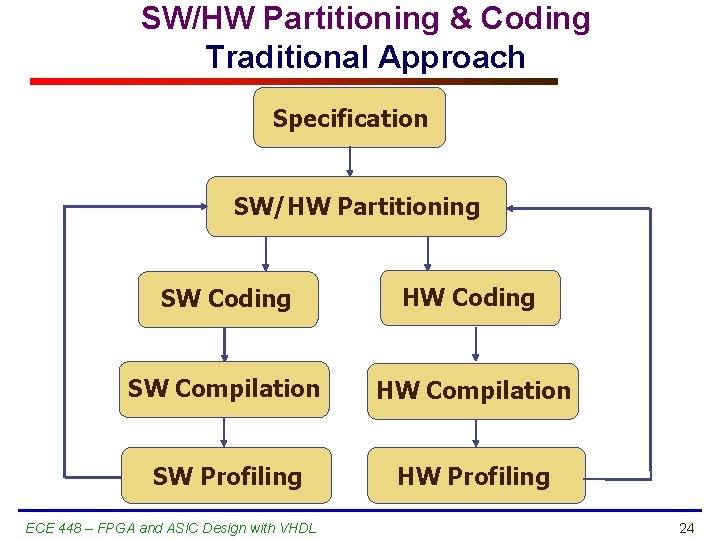

SW/HW Partitioning & Coding Traditional Approach Specification SW/HW Partitioning SW Coding HW Coding SW Compilation HW Compilation SW Profiling HW Profiling ECE 448 – FPGA and ASIC Design with VHDL 24

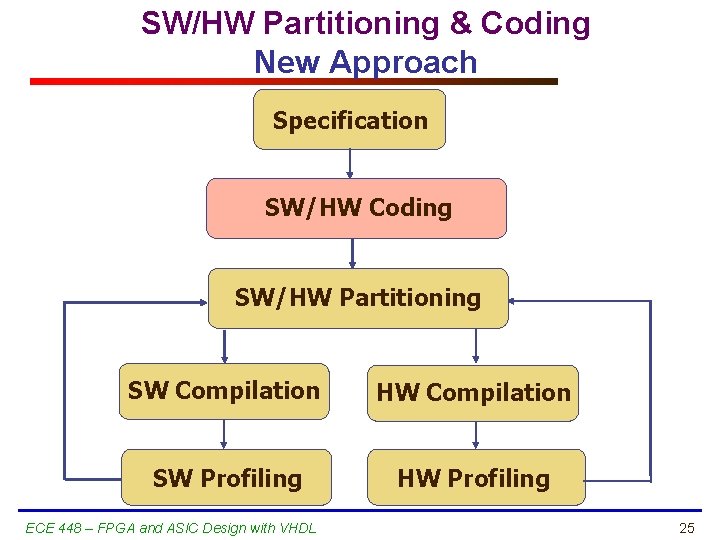

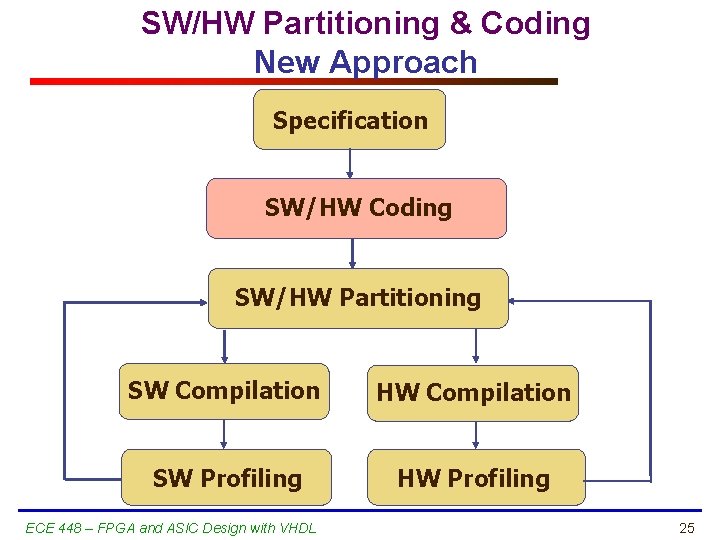

SW/HW Partitioning & Coding New Approach Specification SW/HW Coding SW/HW Partitioning SW Compilation HW Compilation SW Profiling HW Profiling ECE 448 – FPGA and ASIC Design with VHDL 25

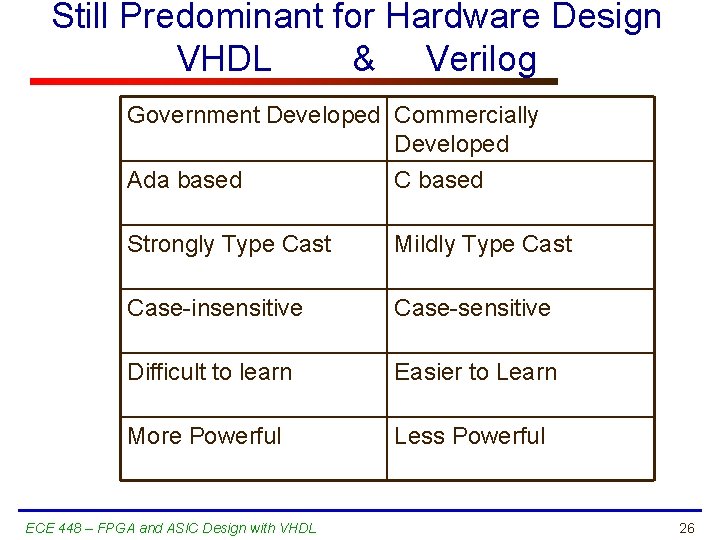

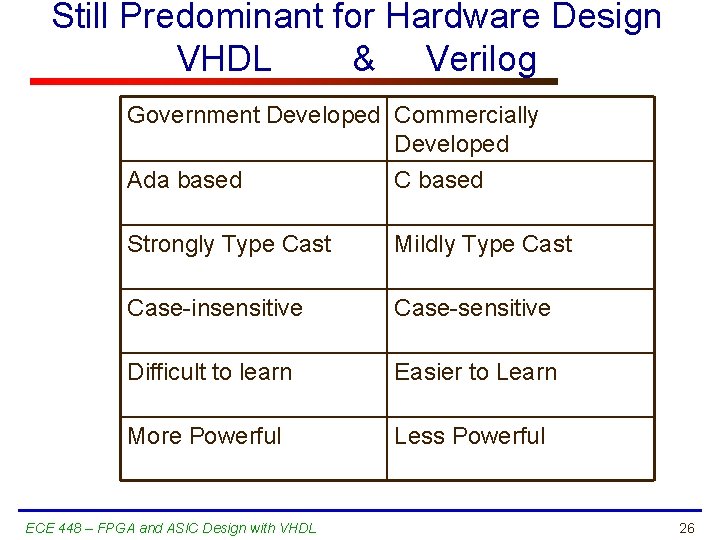

Still Predominant for Hardware Design VHDL & Verilog Government Developed Commercially Developed Ada based C based Strongly Type Cast Mildly Type Cast Case-insensitive Case-sensitive Difficult to learn Easier to Learn More Powerful Less Powerful ECE 448 – FPGA and ASIC Design with VHDL 26

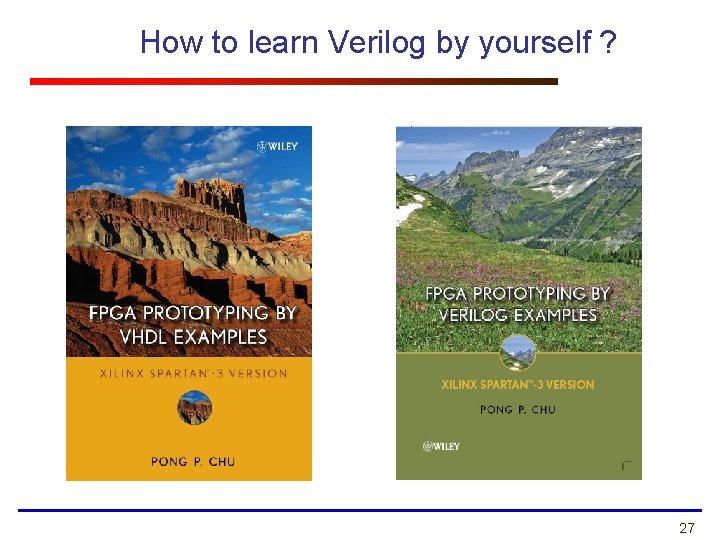

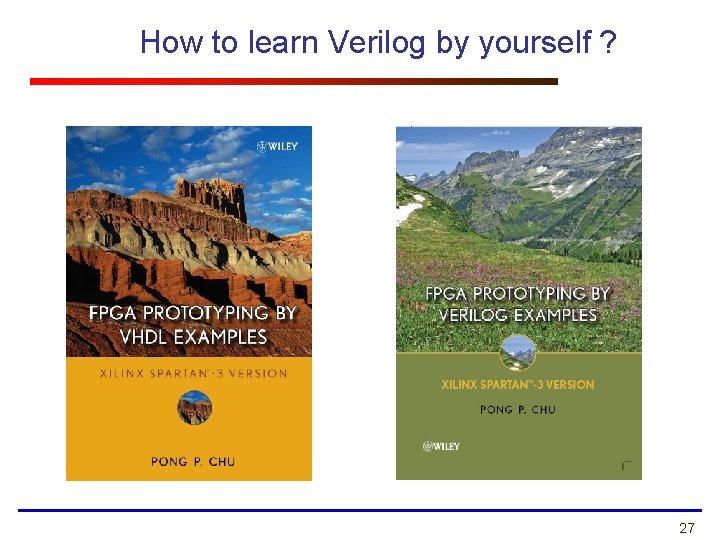

How to learn Verilog by yourself ? 27

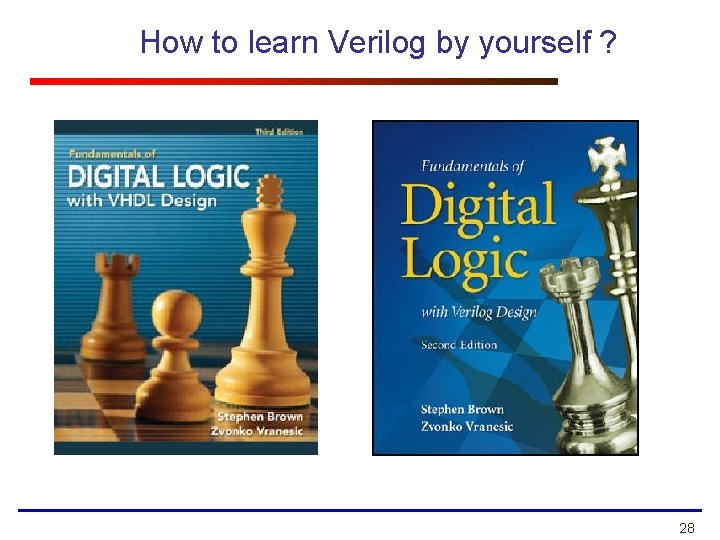

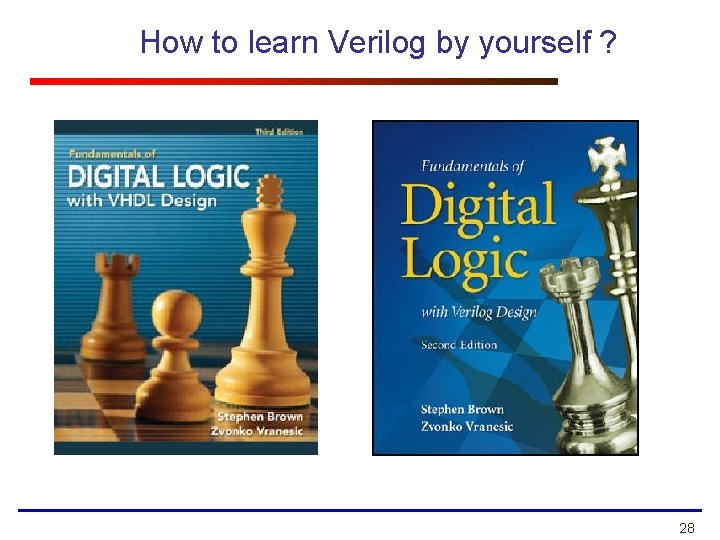

How to learn Verilog by yourself ? 28

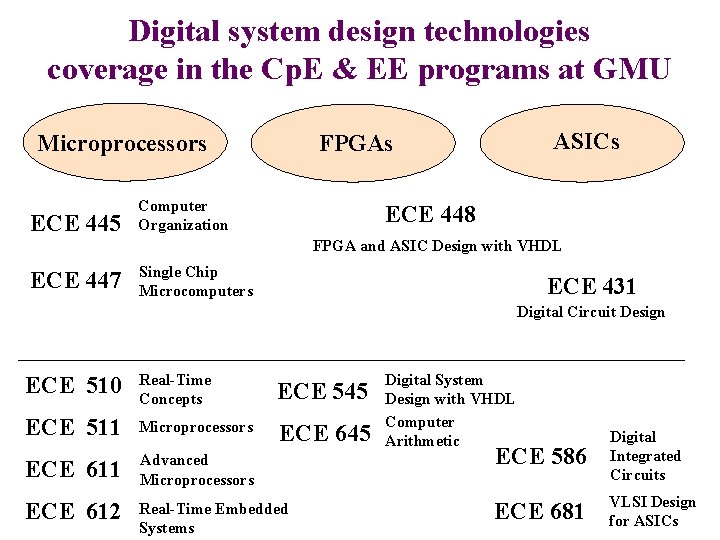

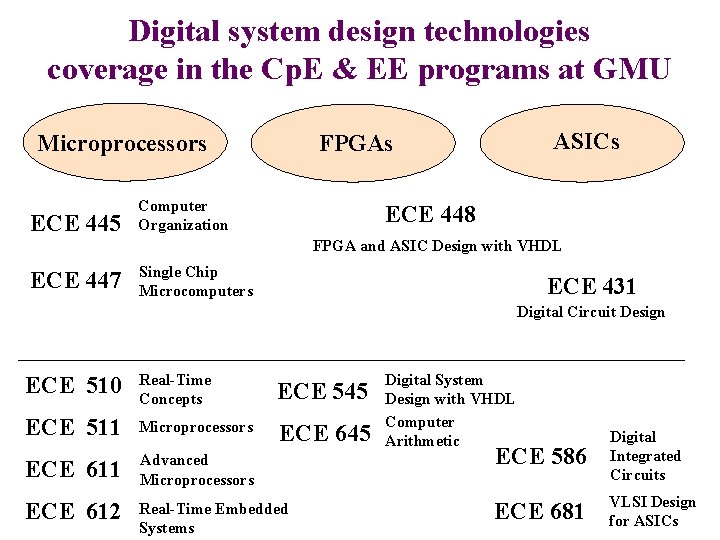

Digital system design technologies coverage in the Cp. E & EE programs at GMU Microprocessors ECE 445 ASICs FPGAs Computer Organization ECE 448 FPGA and ASIC Design with VHDL ECE 447 Single Chip Microcomputers ECE 431 Digital Circuit Design ECE 510 Real-Time Concepts ECE 545 ECE 511 Microprocessors ECE 645 ECE 611 Advanced Microprocessors ECE 612 Real-Time Embedded Systems Digital System Design with VHDL Computer Arithmetic ECE 586 Digital Integrated Circuits ECE 681 VLSI Design for ASICs

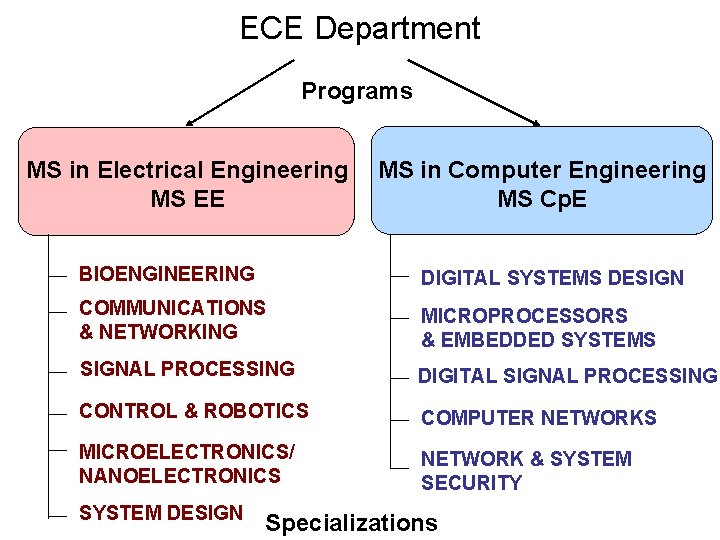

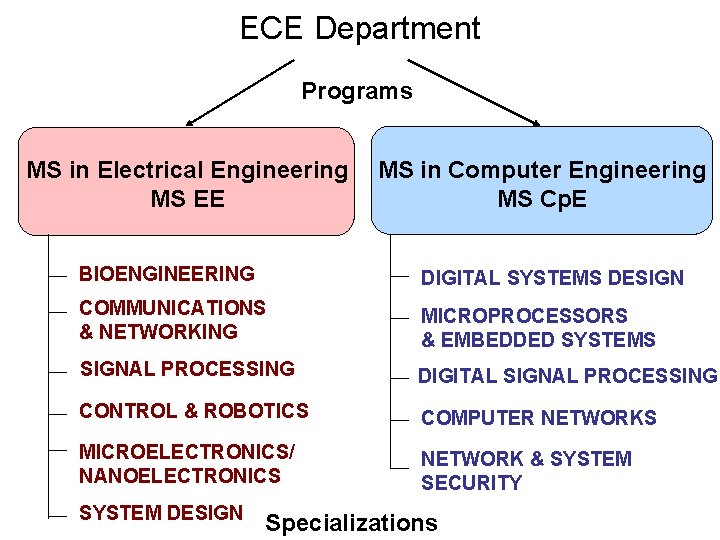

ECE Department Programs MS in Electrical Engineering MS EE MS in Computer Engineering MS Cp. E BIOENGINEERING DIGITAL SYSTEMS DESIGN COMMUNICATIONS & NETWORKING MICROPROCESSORS & EMBEDDED SYSTEMS SIGNAL PROCESSING DIGITAL SIGNAL PROCESSING CONTROL & ROBOTICS COMPUTER NETWORKS MICROELECTRONICS/ NANOELECTRONICS NETWORK & SYSTEM SECURITY SYSTEM DESIGN Specializations

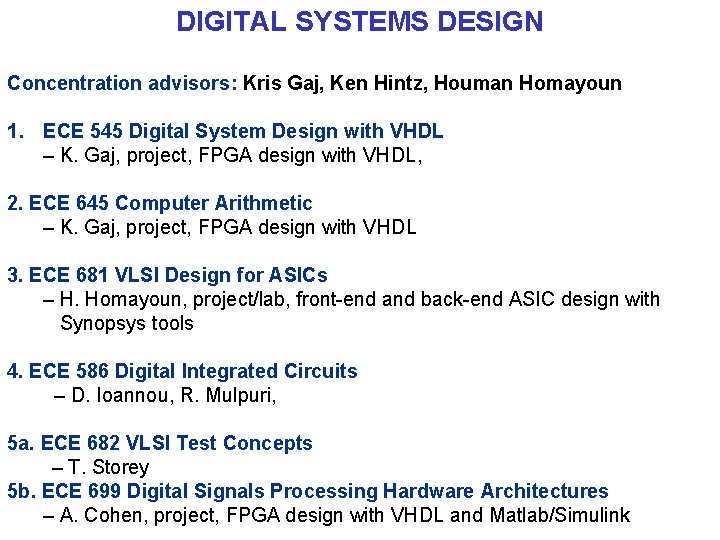

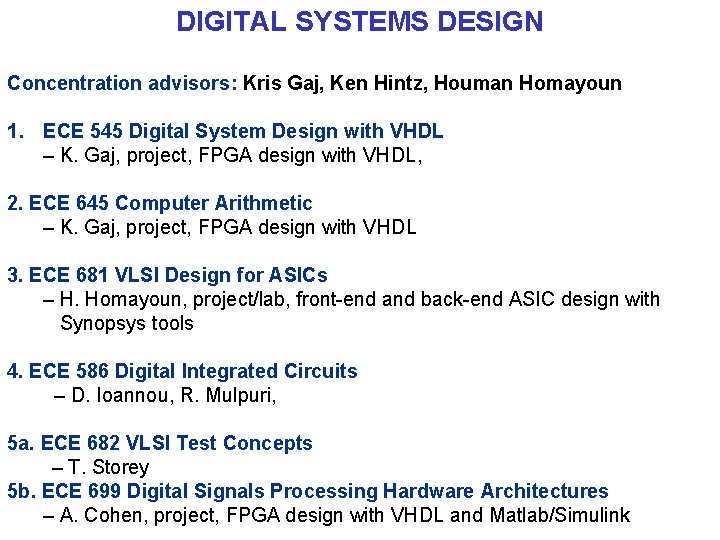

DIGITAL SYSTEMS DESIGN Concentration advisors: Kris Gaj, Ken Hintz, Houman Homayoun 1. ECE 545 Digital System Design with VHDL – K. Gaj, project, FPGA design with VHDL, 2. ECE 645 Computer Arithmetic – K. Gaj, project, FPGA design with VHDL 3. ECE 681 VLSI Design for ASICs – H. Homayoun, project/lab, front-end and back-end ASIC design with Synopsys tools 4. ECE 586 Digital Integrated Circuits – D. Ioannou, R. Mulpuri, 5 a. ECE 682 VLSI Test Concepts – T. Storey 5 b. ECE 699 Digital Signals Processing Hardware Architectures – A. Cohen, project, FPGA design with VHDL and Matlab/Simulink

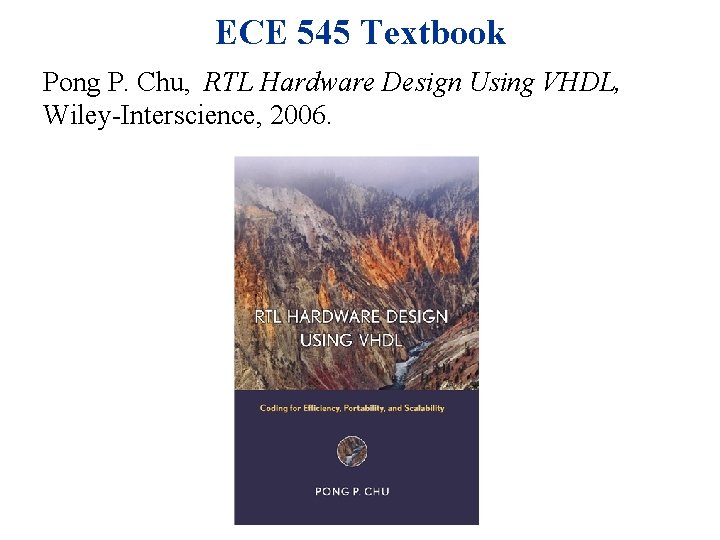

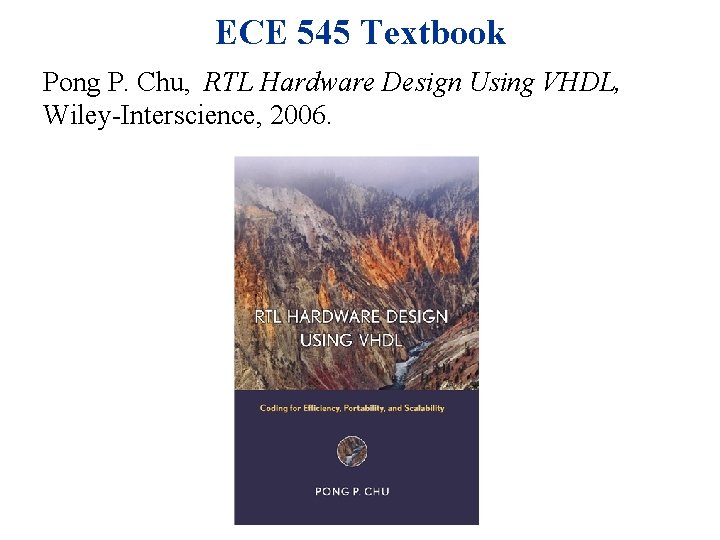

ECE 545 Textbook Pong P. Chu, RTL Hardware Design Using VHDL, Wiley-Interscience, 2006.

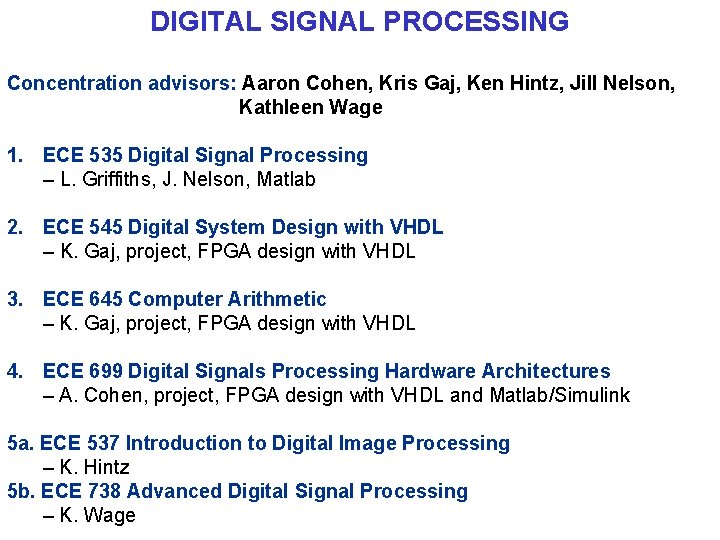

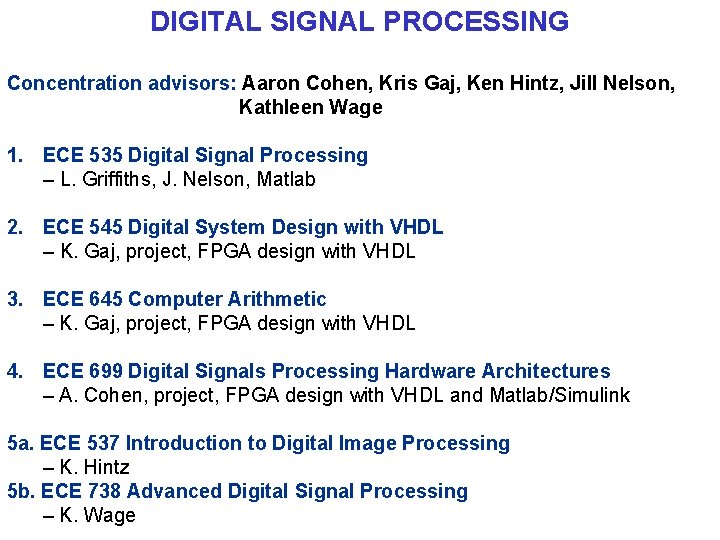

DIGITAL SIGNAL PROCESSING Concentration advisors: Aaron Cohen, Kris Gaj, Ken Hintz, Jill Nelson, Kathleen Wage 1. ECE 535 Digital Signal Processing – L. Griffiths, J. Nelson, Matlab 2. ECE 545 Digital System Design with VHDL – K. Gaj, project, FPGA design with VHDL 3. ECE 645 Computer Arithmetic – K. Gaj, project, FPGA design with VHDL 4. ECE 699 Digital Signals Processing Hardware Architectures – A. Cohen, project, FPGA design with VHDL and Matlab/Simulink 5 a. ECE 537 Introduction to Digital Image Processing – K. Hintz 5 b. ECE 738 Advanced Digital Signal Processing – K. Wage

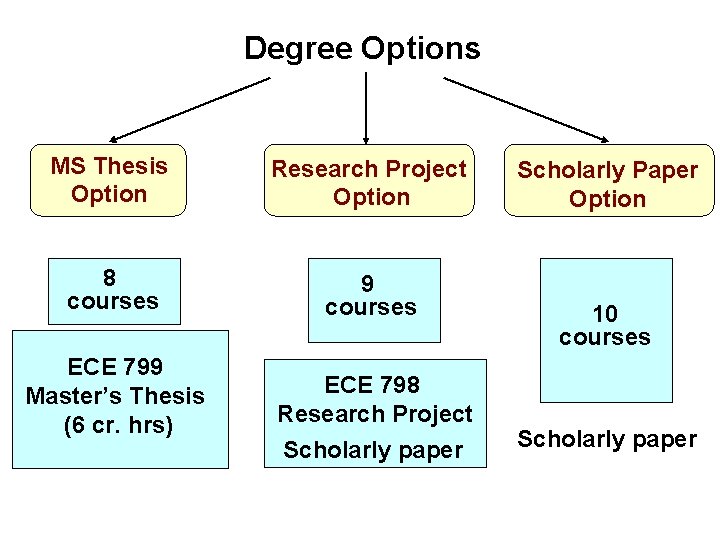

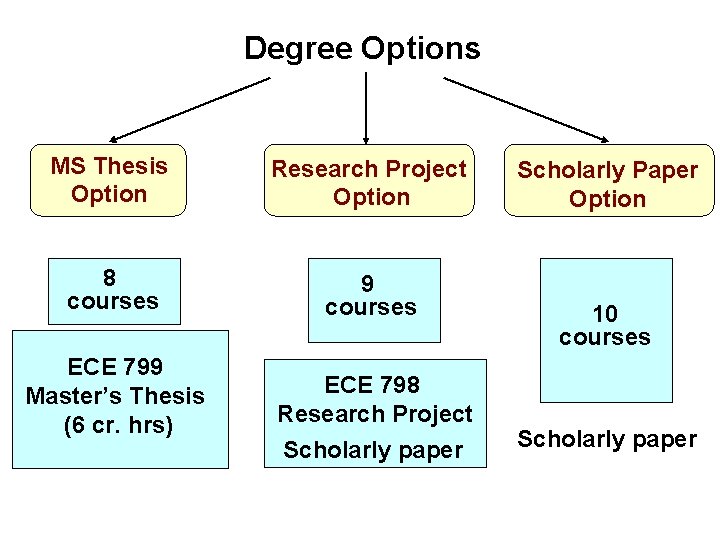

Degree Options MS Thesis Option Research Project Option 8 courses 9 courses ECE 799 Master’s Thesis (6 cr. hrs) ECE 798 Research Project Scholarly paper Scholarly Paper Option 10 courses Scholarly paper

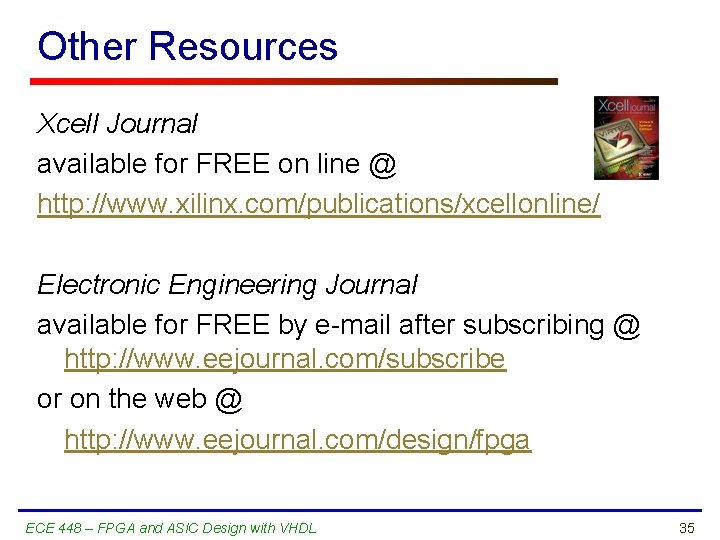

Other Resources Xcell Journal available for FREE on line @ http: //www. xilinx. com/publications/xcellonline/ Electronic Engineering Journal available for FREE by e-mail after subscribing @ http: //www. eejournal. com/subscribe or on the web @ http: //www. eejournal. com/design/fpga ECE 448 – FPGA and ASIC Design with VHDL 35