ECE 426 VLSI System Design Lecture 7 Synchronizers

- Slides: 33

ECE 426 - VLSI System Design Lecture 7 - Synchronizers and Metastability February 19, 2003 Prof. John Nestor ECE Department Lafayette College Easton, Pennsylvania 18042 nestorj@lafayette. edu 2/19/03 ECE 426 - Lecture 7 1

Announcements } No class Mon. 2/17 due to blizzard 2/19/03 ECE 426 - Lecture 7 2

Where we are. . . } Last Time } Verilog Coding Guidelines } Today } More about Synchronizers and Metastability 2/19/03 ECE 426 - Lecture 7 3

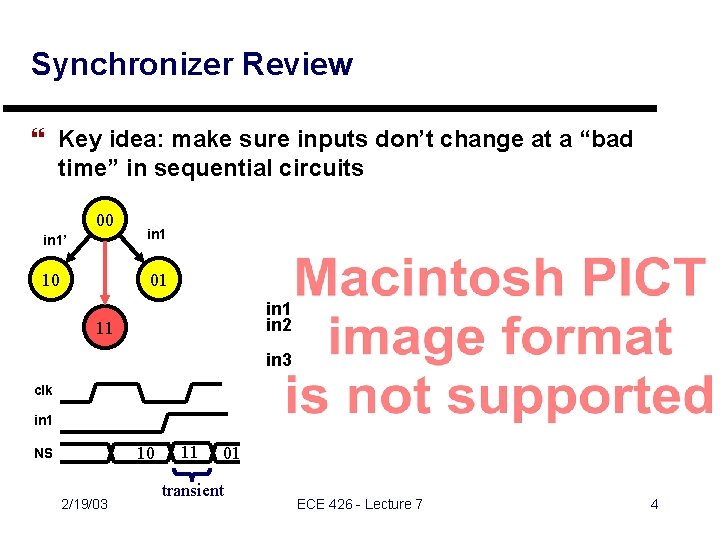

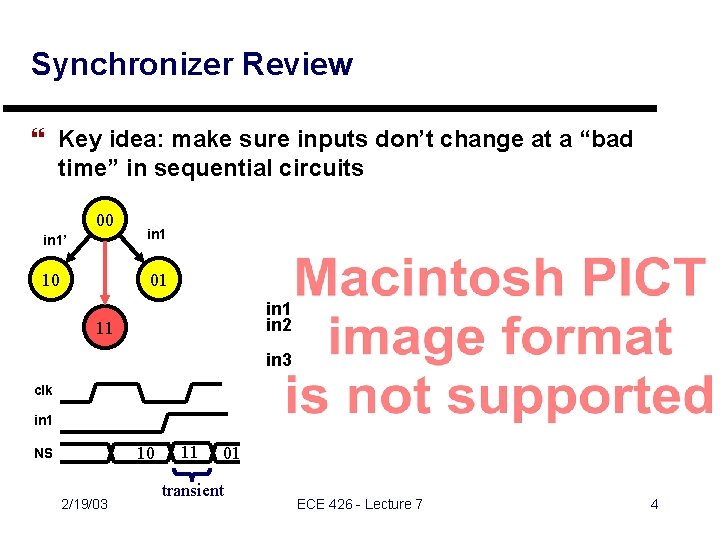

Synchronizer Review } Key idea: make sure inputs don’t change at a “bad time” in sequential circuits 00 in 1’ in 1 10 01 in 2 11 in 3 clk in 1 10 NS 2/19/03 11 01 transient ECE 426 - Lecture 7 4

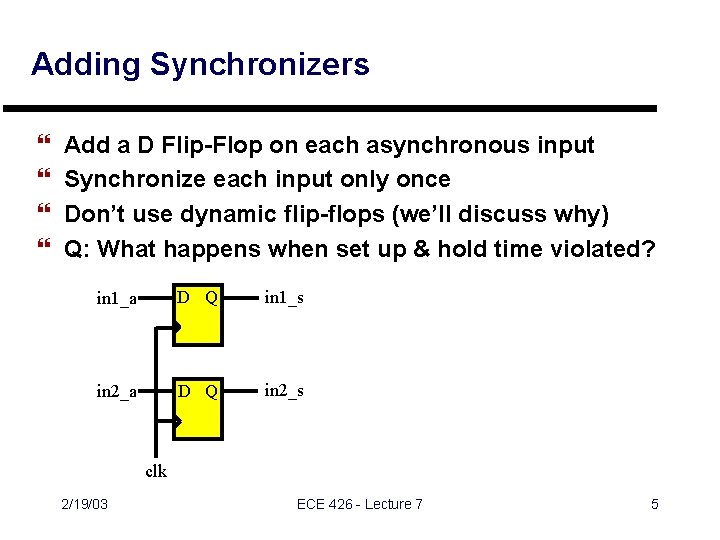

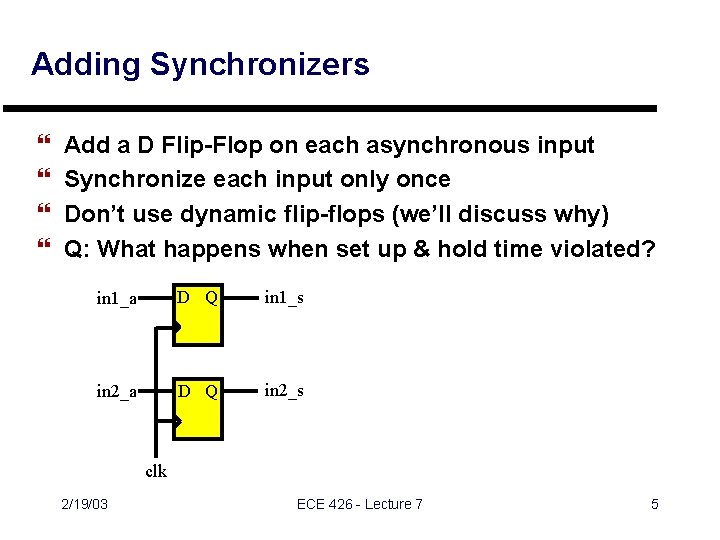

Adding Synchronizers } } Add a D Flip-Flop on each asynchronous input Synchronize each input only once Don’t use dynamic flip-flops (we’ll discuss why) Q: What happens when set up & hold time violated? in 1_a D Q in 1_s in 2_a D Q in 2_s clk 2/19/03 ECE 426 - Lecture 7 5

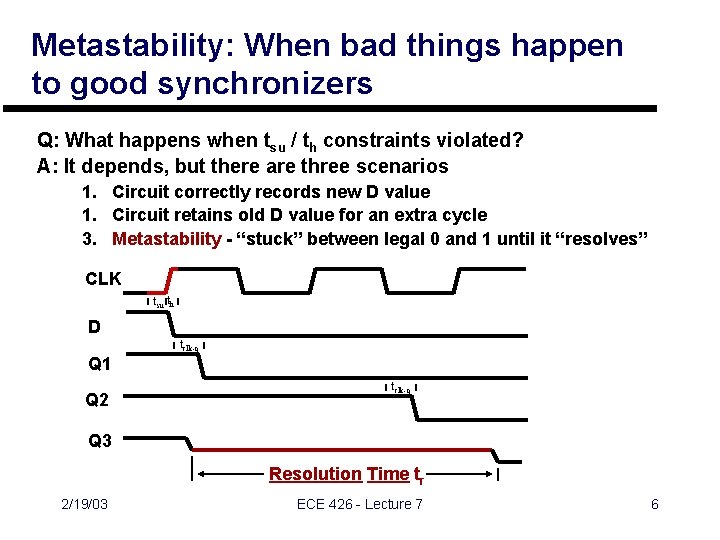

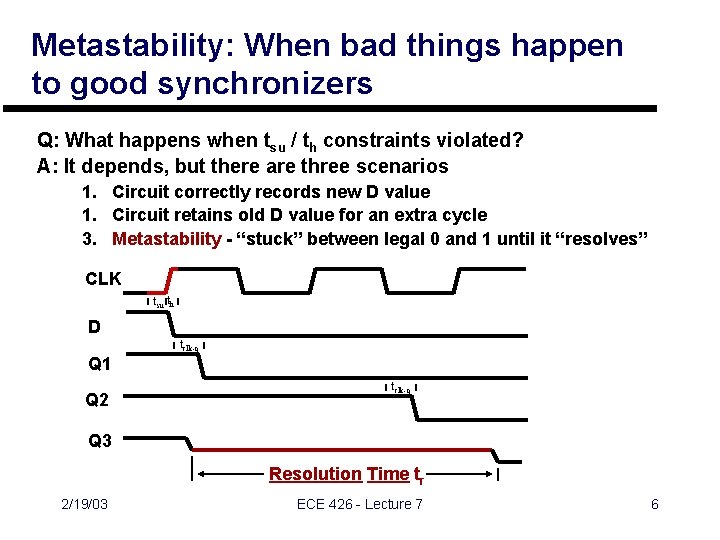

Metastability: When bad things happen to good synchronizers Q: What happens when tsu / th constraints violated? A: It depends, but there are three scenarios 1. Circuit correctly records new D value 1. Circuit retains old D value for an extra cycle 3. Metastability - “stuck” between legal 0 and 1 until it “resolves” CLK tsu th D tclk-q Q 1 Q 2 tclk-q Q 3 Resolution Time tr 2/19/03 ECE 426 - Lecture 7 6

Metastability - Review from last semester } Two stable states } Vo 1=L, Vo 2=H } Vo 1=H, Vo 2=L } One metastable state } Vo 1 = Vo 2 } Ugly characteristic: unbounded recovery time tr Graphic source: J. Rabaey, Digital Integrated Circuits, © Prentice-Hall, 1996 2/19/03 Metastable point ECE 426 - Lecture 7 7

Metastability - “Ball on the Hill” Analogy } Sides of hill = stable states } Top of hill = metastable state } Any small “push” (e. g. , noise) will move the ball off the hill and into a stable state 2/19/03 ECE 426 - Lecture 7 8

Metastability - Bad News / Good News } Bad news } Metastability is unavoidable } Recovery time is theoretically unbounded } Good news } Can empirically measure recovery times } Can use statistics from recovery times to make failure probability arbitrarily small 2/19/03 ECE 426 - Lecture 7 9

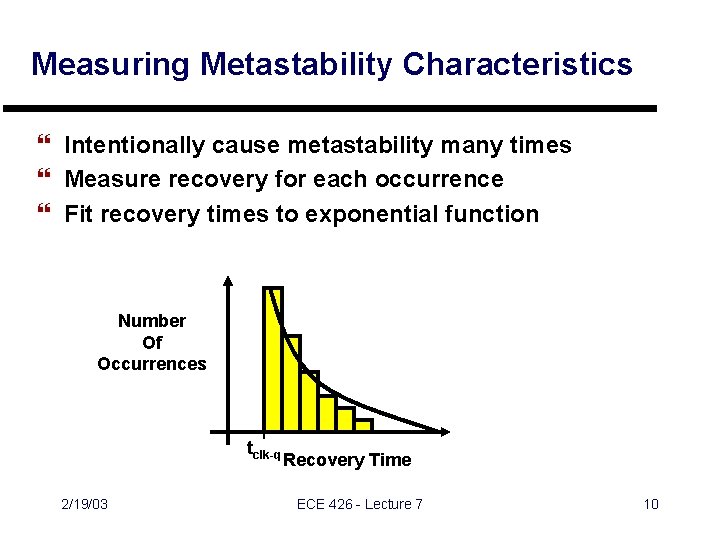

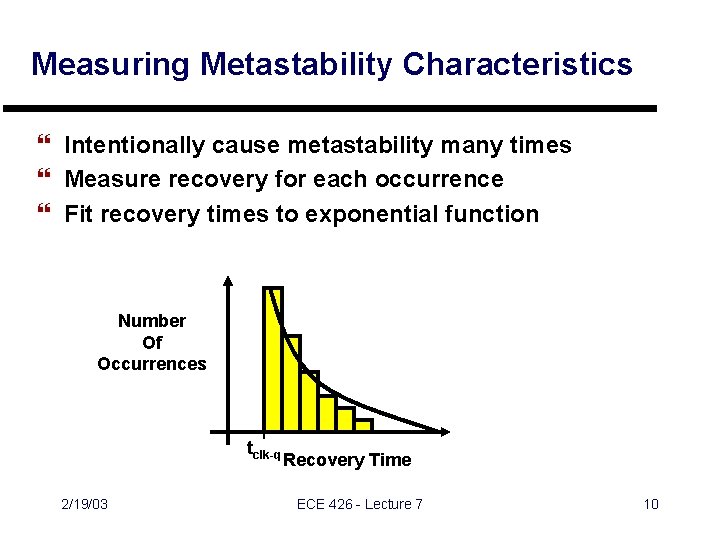

Measuring Metastability Characteristics } Intentionally cause metastability many times } Measure recovery for each occurrence } Fit recovery times to exponential function Number Of Occurrences tclk-q 2/19/03 Recovery Time ECE 426 - Lecture 7 10

Designing with Metastability } A synchronizer design at a given clock period provides a fixed amount of resolution time tr } Definition: a synchronization failure occurs when actual recovery time tr-actual > tr } For a given flip-flop, the mean time between failure (MTBF) is given by the formula fclk - System clock freq. a - asynchronous input rate of change. t - empirically derived constant To - empirically derived constant tr - time available for resolution 2/19/03 ECE 426 - Lecture 7 11

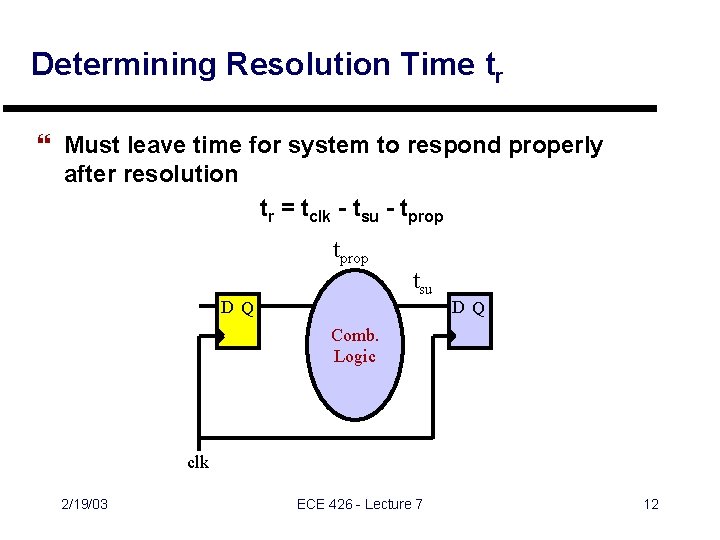

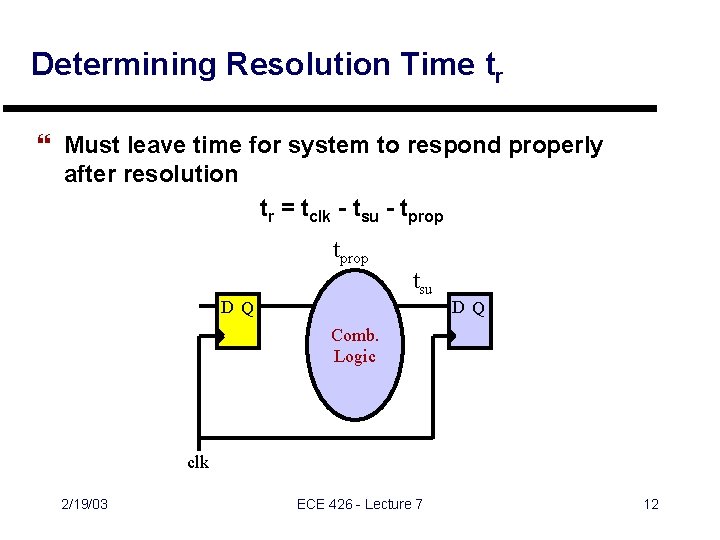

Determining Resolution Time tr } Must leave time for system to respond properly after resolution tr = tclk - tsu - tprop tsu DQ DQ Comb. Logic clk 2/19/03 ECE 426 - Lecture 7 12

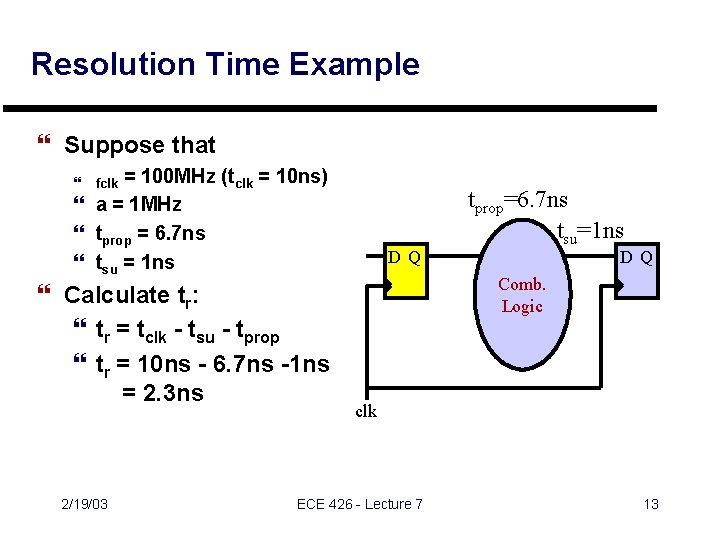

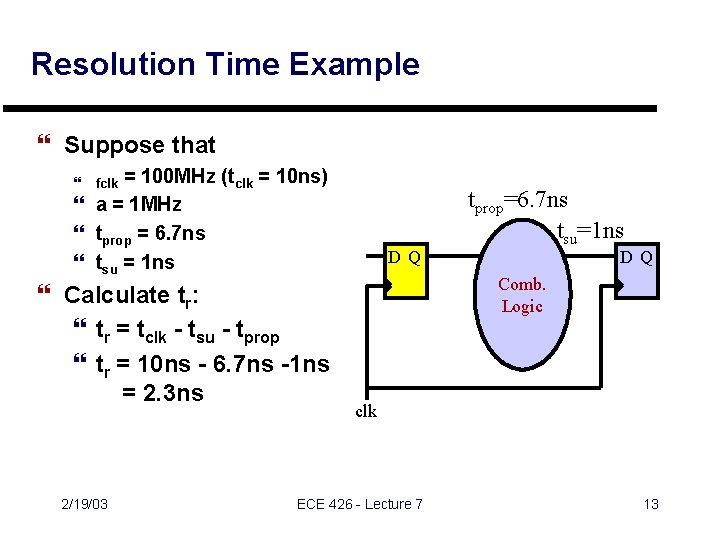

Resolution Time Example } Suppose that = 100 MHz (tclk = 10 ns) } a = 1 MHz } tprop = 6. 7 ns } tsu = 1 ns } fclk } Calculate tr: } tr = tclk - tsu - tprop } tr = 10 ns - 6. 7 ns -1 ns = 2. 3 ns 2/19/03 DQ tprop=6. 7 ns tsu=1 ns DQ Comb. Logic clk ECE 426 - Lecture 7 13

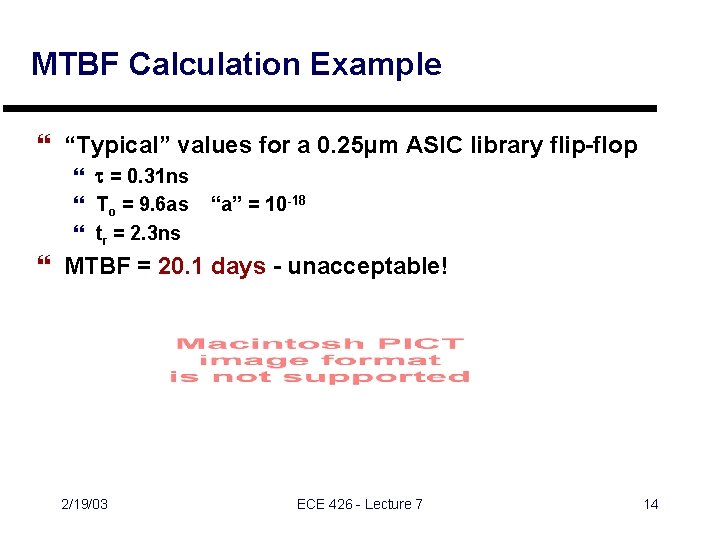

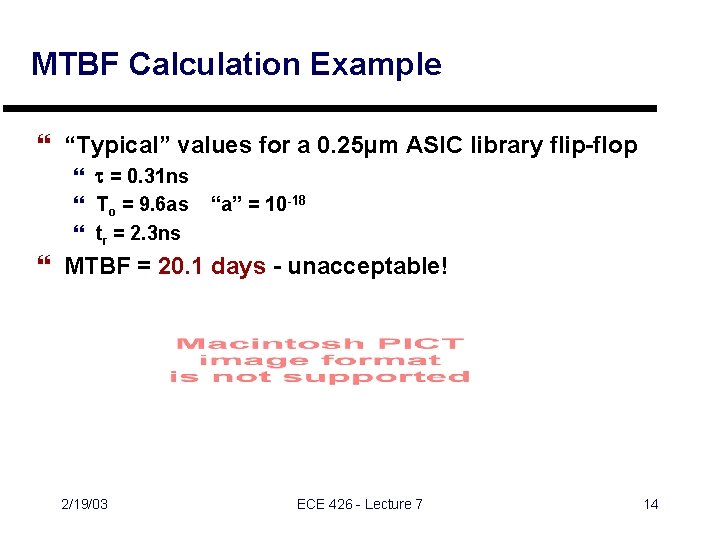

MTBF Calculation Example } “Typical” values for a 0. 25µm ASIC library flip-flop } t = 0. 31 ns } To = 9. 6 as } tr = 2. 3 ns “a” = 10 -18 } MTBF = 20. 1 days - unacceptable! 2/19/03 ECE 426 - Lecture 7 14

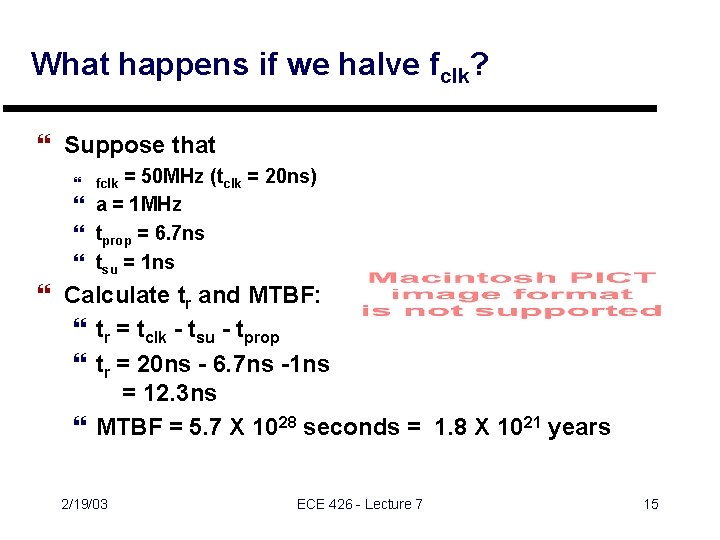

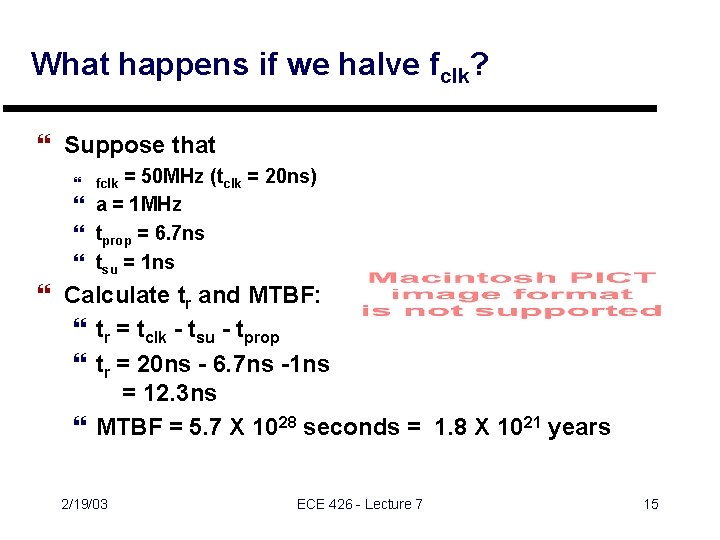

What happens if we halve fclk? } Suppose that = 50 MHz (tclk = 20 ns) } a = 1 MHz } tprop = 6. 7 ns } tsu = 1 ns } fclk } Calculate tr and MTBF: } tr = tclk - tsu - tprop } tr = 20 ns - 6. 7 ns -1 ns = 12. 3 ns } MTBF = 5. 7 X 1028 seconds = 1. 8 X 1021 years 2/19/03 ECE 426 - Lecture 7 15

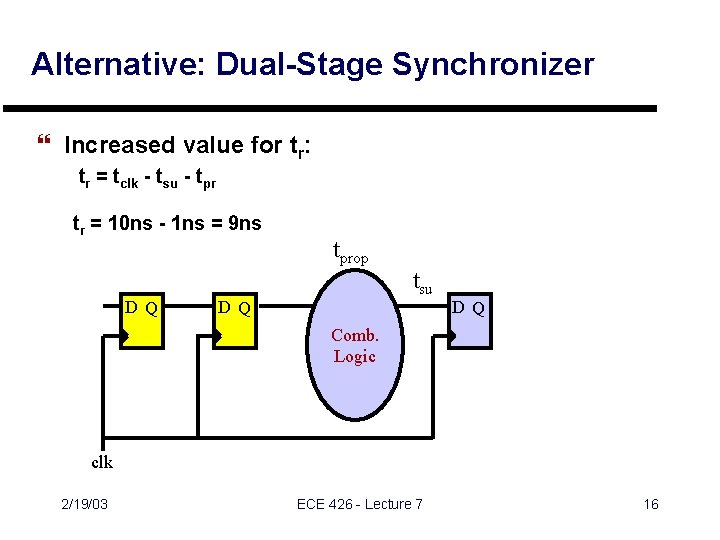

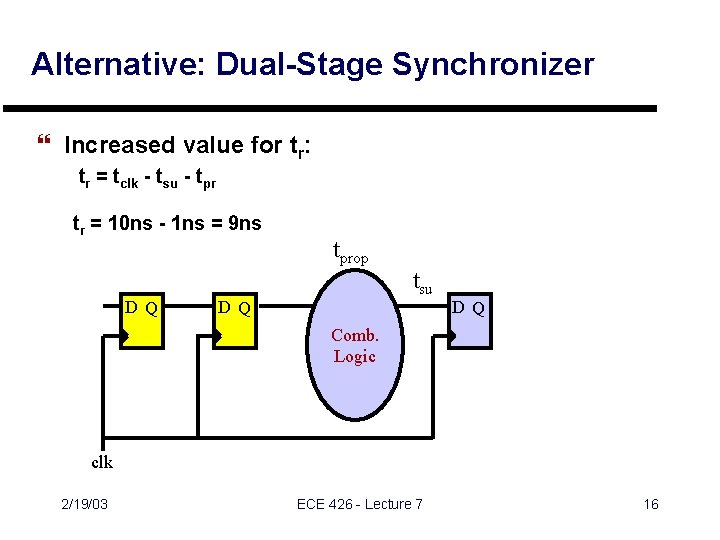

Alternative: Dual-Stage Synchronizer } Increased value for tr: tr = tclk - tsu - tpr tr = 10 ns - 1 ns = 9 ns DQ tprop tsu DQ DQ Comb. Logic clk 2/19/03 ECE 426 - Lecture 7 16

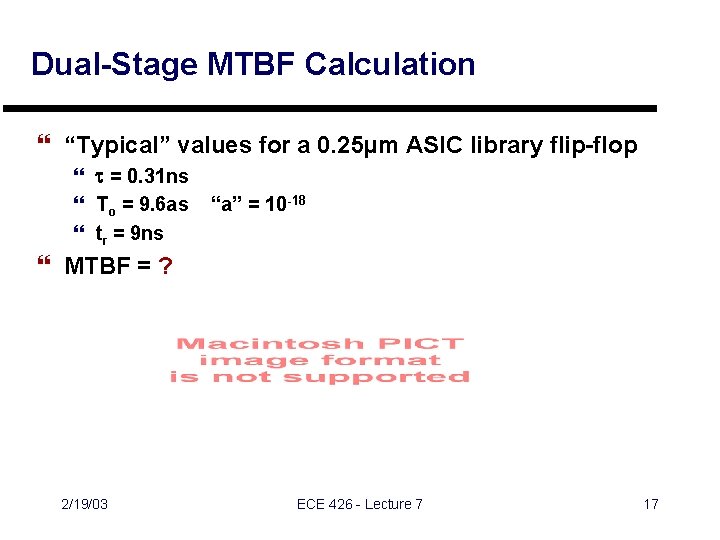

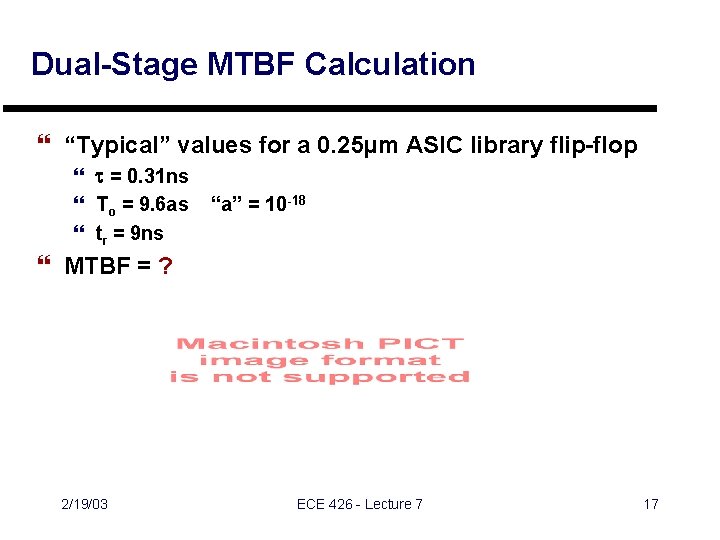

Dual-Stage MTBF Calculation } “Typical” values for a 0. 25µm ASIC library flip-flop } t = 0. 31 ns } To = 9. 6 as } tr = 9 ns “a” = 10 -18 } MTBF = ? 2/19/03 ECE 426 - Lecture 7 17

Other Synchronizer Alternatives } Metastability-hardened SYNC flip-flops provided by ASIC library } Multiple-Stage Synchronizers } Reduced-Clock Synchronizers 2/19/03 ECE 426 - Lecture 7 18

What to Do About Metastability } } } Start with simple synchronizer (single flip-flop) Calculate MTBF for your system Decide if it's acceptable If not, use faster flip-flop OR different design: } Two-stage flip-flop } Reduced-clock synchronizers 2/19/03 ECE 426 - Lecture 7 19

Back to Synchronous Logic Guidelines } See Lecture 6 Notes 2/19/03 ECE 426 - Lecture 7 20

Architecture Design (Ch. 8) } Goal: design high-level organization of chip } Organization is usually described using the register transfer abstraction } Describes system as connected network of • Registers • Combinational logic } Treats overall design as a large sequential circuit } Specifies system function on a cycle-by-cycle basis } Used as an input specification for logic synthesis (e. g. , Synopsys) tools 2/19/03 ECE 426 - Lecture 7 21

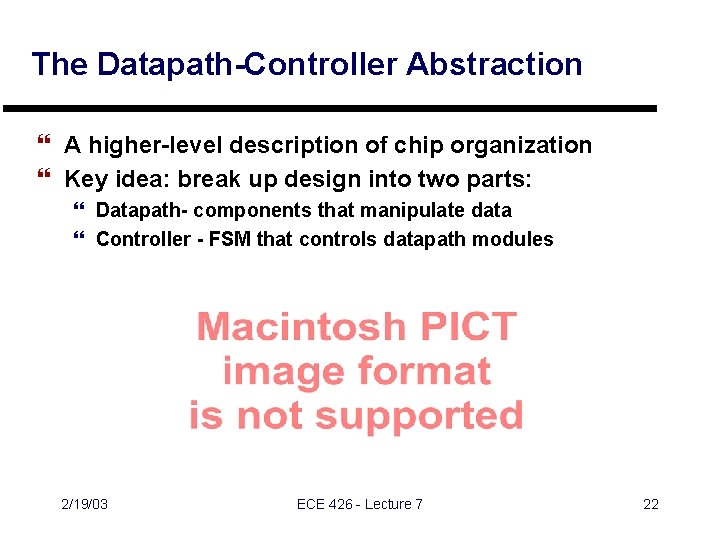

The Datapath-Controller Abstraction } A higher-level description of chip organization } Key idea: break up design into two parts: } Datapath- components that manipulate data } Controller - FSM that controls datapath modules 2/19/03 ECE 426 - Lecture 7 22

Steps in Architecture Design } Propose data unit components } } functions performed data inputs / outputs control inputs - perform operation when asserted status outputs - condition info for control unit } Design control-unit FSM } Respond to ext. inputs, status values from data unit } Generate control signals to drive data unit, external outputs } Control-Unit Representations • Traditional "bubble and arrow" state diagram • Algorithmic State Machine (ASM) diagrams 2/19/03 ECE 426 - Lecture 7 23

Coming Up } Next Lab: Verifying Sequential Circuits } ASM Diagrams } Controller / Datapath Design Examples 2/19/03 ECE 426 - Lecture 7 24

2/19/03 ECE 426 - Lecture 7 25

2/19/03 ECE 426 - Lecture 7 26

Verification Plan } Definition: A Specification of the Verification Effort } Prerequisite: Specification document for design } Defnining Success - Must Identify } Features which must be exercisedunder which conditions } Expected Response 2/19/03 ECE 426 - Lecture 7 27

Levels of Verification } } Board System / Subsystem ASIC / FPGA Unit / Subunit 2/19/03 ECE 426 - Lecture 7 28

Levels of Verification } } Connectivity Transaction / Cooperative Data Flow Functionality Ad Hoc } Designer verifies basic functionality 2/19/03 ECE 426 - Lecture 7 29

Levels of Verification - Notes } Stable interfaces required at each level of granularity 2/19/03 ECE 426 - Lecture 7 30

Rules for Style } Optimize the Right Thing } Good Comments Improve Maintainability } Encapsulation Hides Implementation Details 2/19/03 ECE 426 - Lecture 7 31

Lab 3 Overview } Self-checking testbench for generic counter } } } Identify important features Create conditions that test these features Check conditions Write message when error occurs “Insert” errors to demonstrate when self-check fails Test for varying values of N (2, 8, 10, 16) 2/19/03 ECE 426 - Lecture 7 32

System Design Issues } } ASM Diagrams Synchronization & Metastability Handshaking Working with Multiple Clocks 2/19/03 ECE 426 - Lecture 7 33