ECE 425 VLSI Circuit Design Lecture 15 ASIC

- Slides: 54

ECE 425 - VLSI Circuit Design Lecture 15 - ASIC Design with Verilog Spring 2007 Prof. John Nestor ECE Department Lafayette College Easton, Pennsylvania 18042 nestorj@lafayette. edu ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 1

Announcements } Reading } Book: 4. 1 -4. 8, 5. 1 -5. 2 } Verilog Handout: 5. 1 -5. 3, 5. 6 ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 2

Where we are } Last Time: } Logical Effort } Testing } Today: } ASIC Design with Verilog • Overview • Verilog Review - Combinational Design ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 3

ASIC Design with Logic Synthesis } Goal: automate ASIC Design Process } Translate HDL into Boolean Expressions } Optimize design for cost and timing constraints } Map into ASIC gate library } History } } Two-level logic optimization algorithms - early 1980 s Multi-level logic optimization - mid-1980 s Commercial logic synthesis (Synopsys) - late 1980 s Tighter integration with physical design - present ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 4

Logic Optimization } Two-Level Logic Optimization } Minimize logic in AND/OR form } Simple Optimization: Karnaugh Map } Computer-Based Optimization • Quine/Mc. Cluskey - Exact method (slow) • Espresso - Heuristic method (fast) } Multi-Level Logic Optimization } } Factor common subexpressions in a logic network Simplify individual nodes using two-level optimization Apply multiple transformations with command scripts Integrate with timing analysis, technology mapping ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 5

Outline - Introduction to Verilog } } } Goals of HDL-Based Design Verilog Background A First Example Module and Port Declarations Modeling with Continuous Assignments Some Language Details Modeling with Hierarchy Modeling with always blocks (combinational logic) Demonstration: Using Verilogger Discuss Project 1 Summary ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 6

HDL Overview } What is an HDL? A language for } simulation - “event driven” model of execution } synthesis - generates designs that match simulated behavior for a subset of the language } Common HDLs: } Verilog HDL } VHDL - VHSIC (Very High-Speed IC) HDL } System. C - C++ with class libraries to support System-Level Design and Hardware Design ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 7

Verilog Simulators } On Windows Machines: } Synapticad Verilogger } Mentor Model. Sim } On the Linux (? ): Synopsys vcs } vcs -RI ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 8

Verilog module construct } Key building block of language } declaration - specifies a module interface • Input & output ports connections to outside world • “black box” model - no details about internals } body - specifies contents of "black box" • behavior - what it does • structure - how it's built from other "black boxes" ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 9

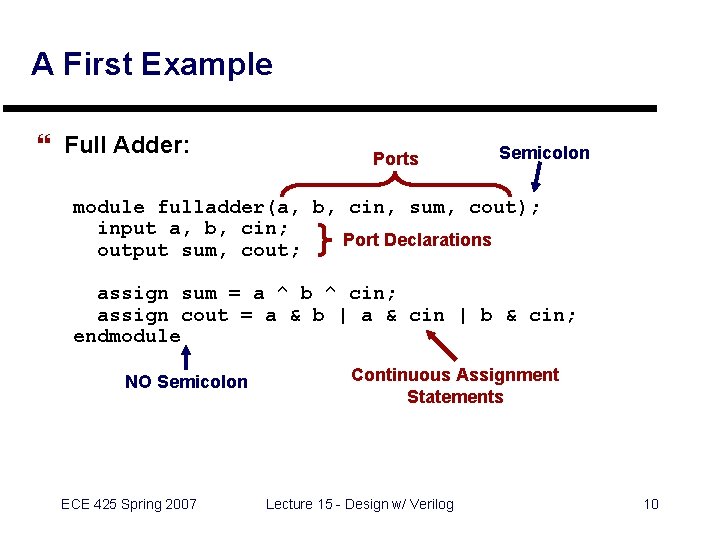

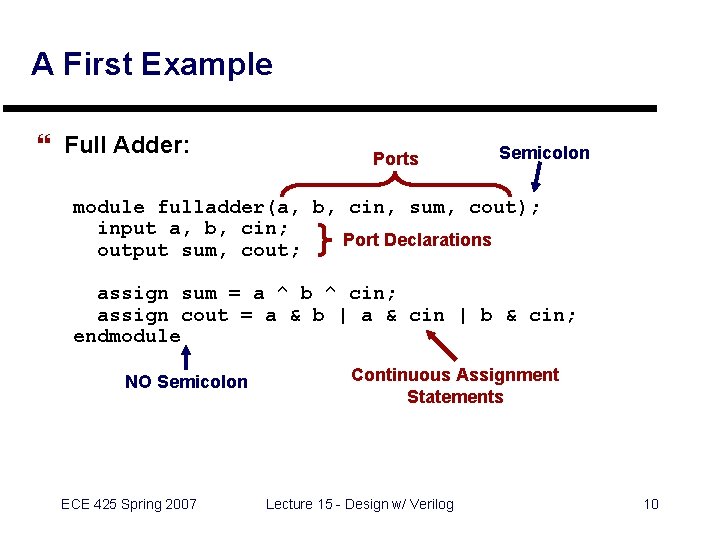

A First Example } Full Adder: Ports Semicolon module fulladder(a, b, cin, sum, cout); input a, b, cin; Port Declarations output sum, cout; assign sum = a ^ b ^ cin; assign cout = a & b | a & cin | b & cin; endmodule NO Semicolon ECE 425 Spring 2007 Continuous Assignment Statements Lecture 15 - Design w/ Verilog 10

Comments about the First Example } Verilog describes a circuit as a set of modules } Each module has input and output ports } Single bit } Multiple bit - array syntax } Each port can take on a digital value (0, 1, X, Z) during simulation } Three main ways to specify module internals } Continuous assignment statements - assign } Concurrent statements - always } Submodule instantiation (hierarchy) ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 11

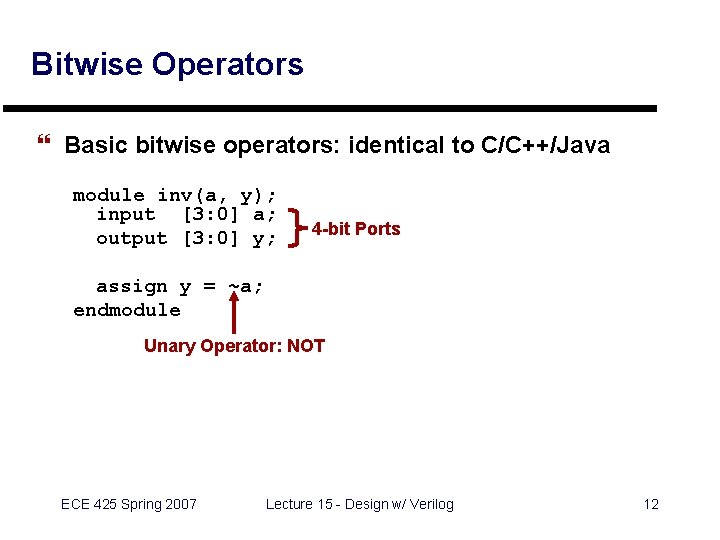

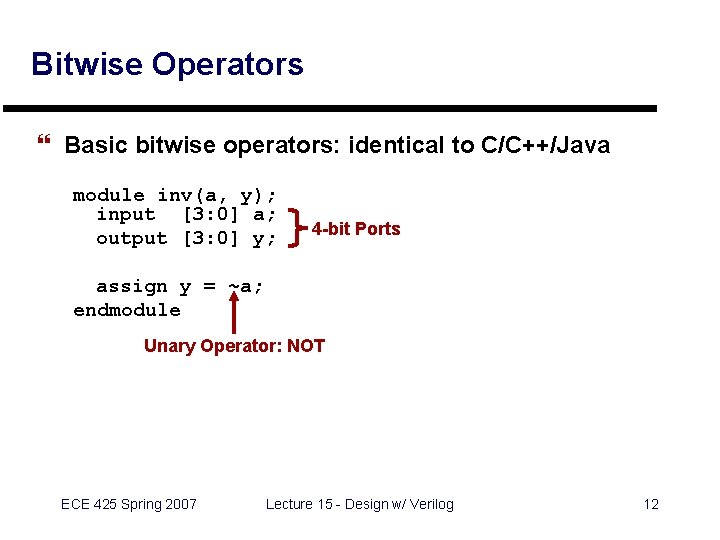

Bitwise Operators } Basic bitwise operators: identical to C/C++/Java module inv(a, y); input [3: 0] a; output [3: 0] y; 4 -bit Ports assign y = ~a; endmodule Unary Operator: NOT ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 12

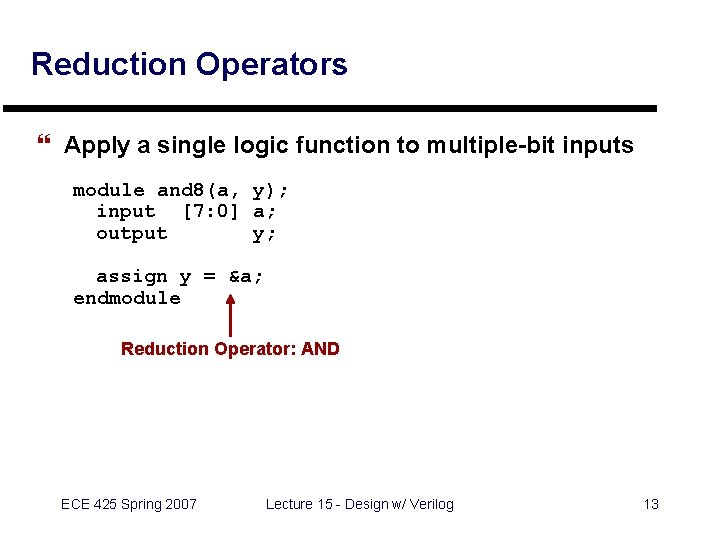

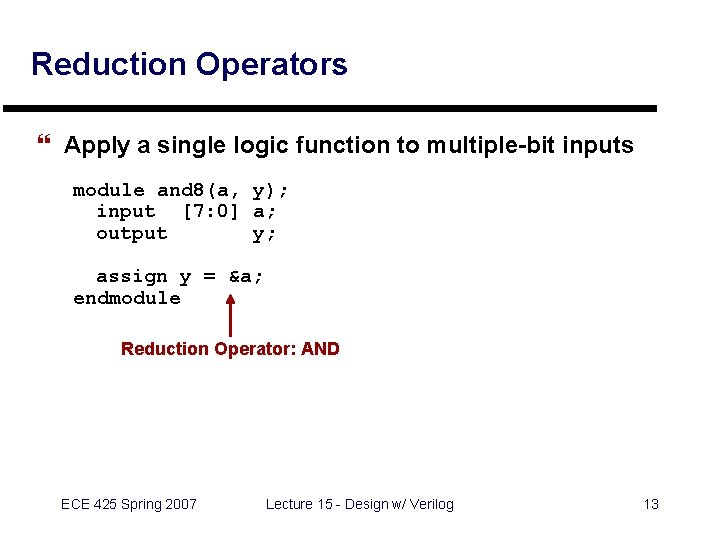

Reduction Operators } Apply a single logic function to multiple-bit inputs module and 8(a, y); input [7: 0] a; output y; assign y = &a; endmodule Reduction Operator: AND ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 13

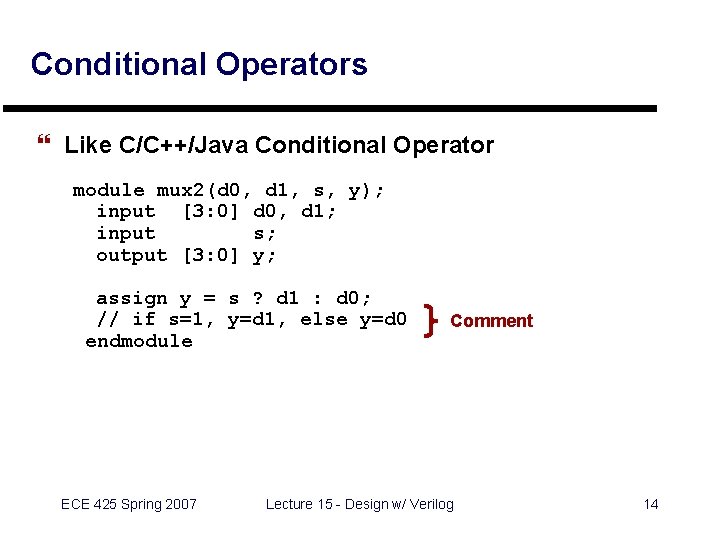

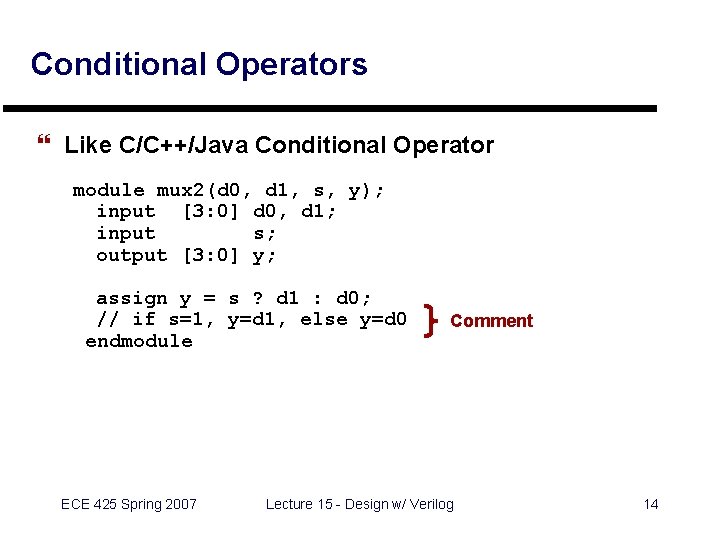

Conditional Operators } Like C/C++/Java Conditional Operator module mux 2(d 0, d 1, s, y); input [3: 0] d 0, d 1; input s; output [3: 0] y; assign y = s ? d 1 : d 0; // if s=1, y=d 1, else y=d 0 endmodule ECE 425 Spring 2007 Comment Lecture 15 - Design w/ Verilog 14

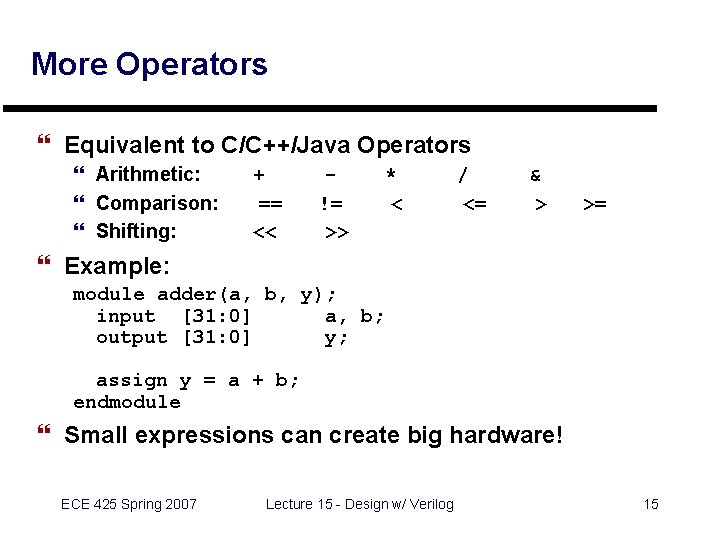

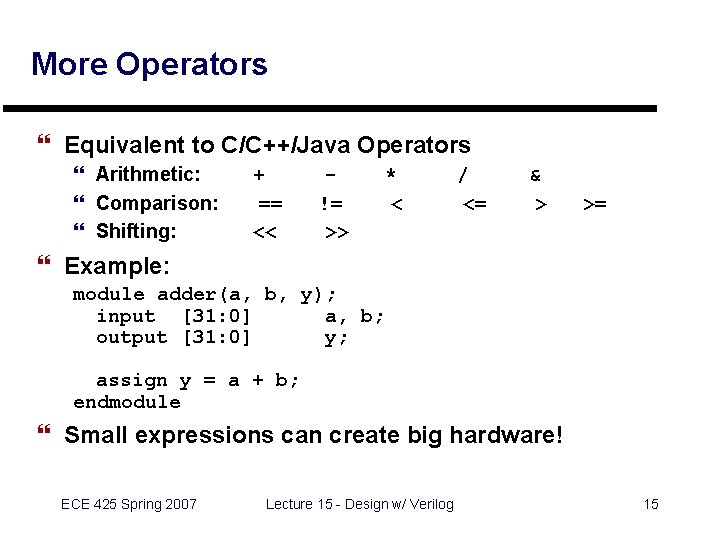

More Operators } Equivalent to C/C++/Java Operators } Arithmetic: } Comparison: } Shifting: + - * / & == != < <= > >= << >> } Example: module adder(a, b, y); input [31: 0] a, b; output [31: 0] y; assign y = a + b; endmodule } Small expressions can create big hardware! ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 15

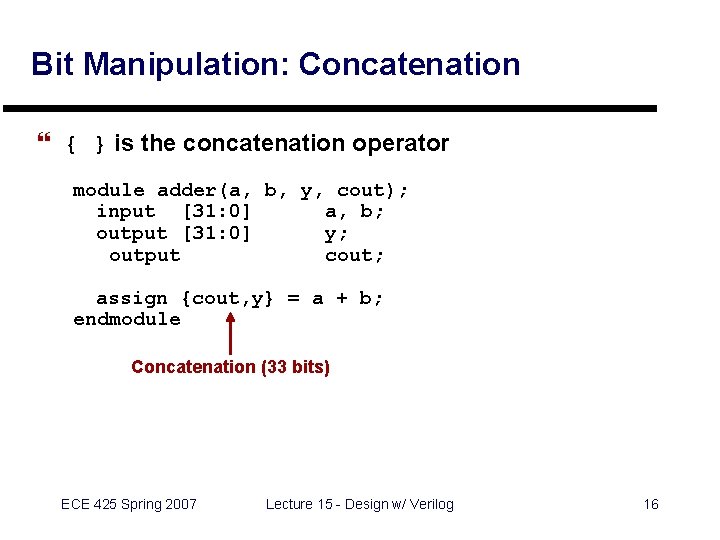

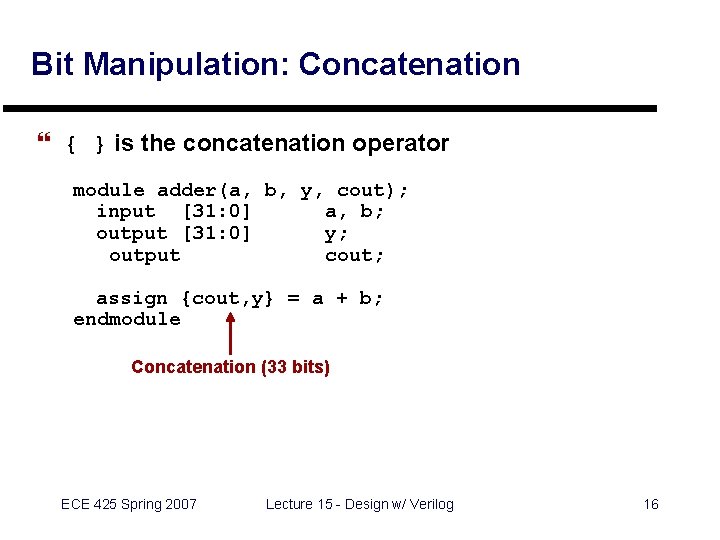

Bit Manipulation: Concatenation } { } is the concatenation operator module adder(a, b, y, cout); input [31: 0] a, b; output [31: 0] y; output cout; assign {cout, y} = a + b; endmodule Concatenation (33 bits) ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 16

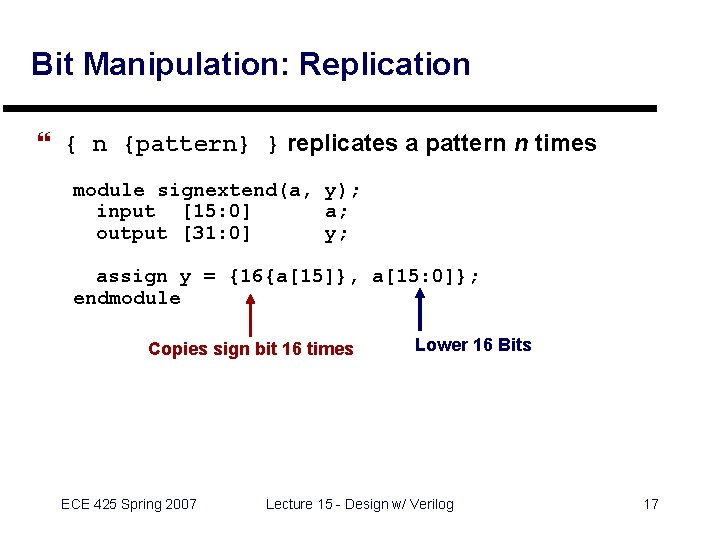

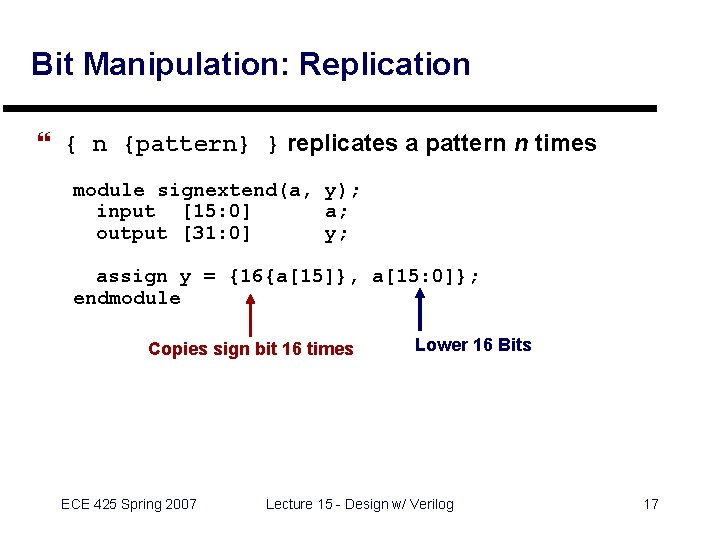

Bit Manipulation: Replication } { n {pattern} } replicates a pattern n times module signextend(a, y); input [15: 0] a; output [31: 0] y; assign y = {16{a[15]}, a[15: 0]}; endmodule Copies sign bit 16 times ECE 425 Spring 2007 Lower 16 Bits Lecture 15 - Design w/ Verilog 17

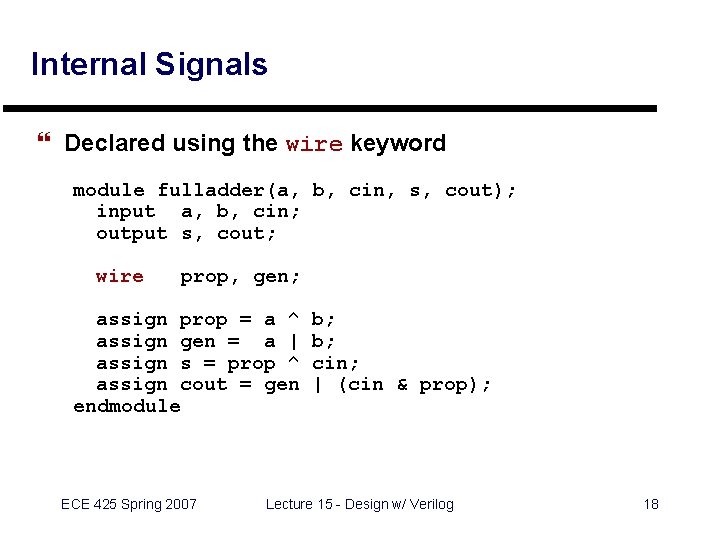

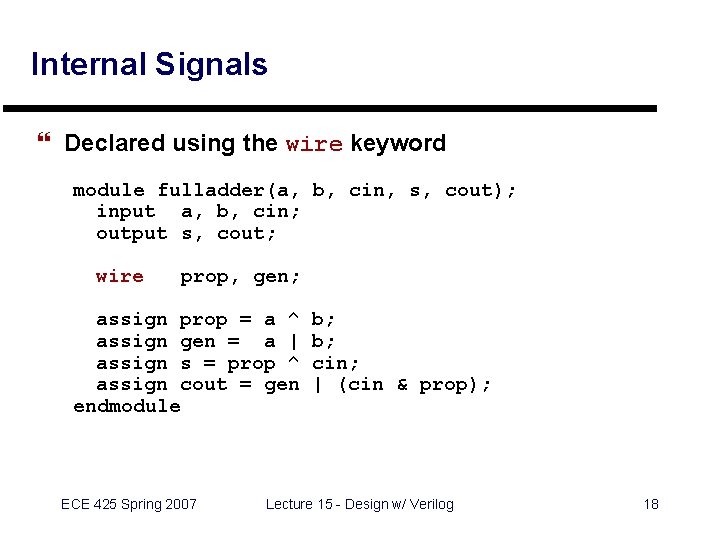

Internal Signals } Declared using the wire keyword module fulladder(a, b, cin, s, cout); input a, b, cin; output s, cout; wire prop, gen; assign prop = a ^ b; assign gen = a | b; assign s = prop ^ cin; assign cout = gen | (cin & prop); endmodule ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 18

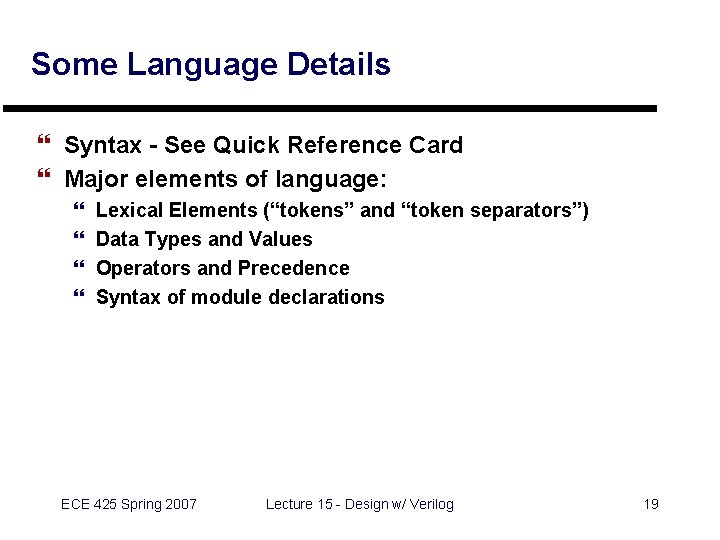

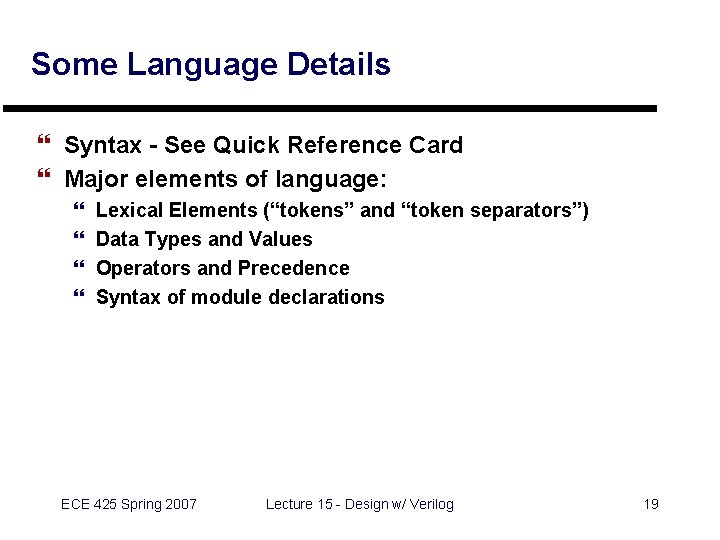

Some Language Details } Syntax - See Quick Reference Card } Major elements of language: } } Lexical Elements (“tokens” and “token separators”) Data Types and Values Operators and Precedence Syntax of module declarations ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 19

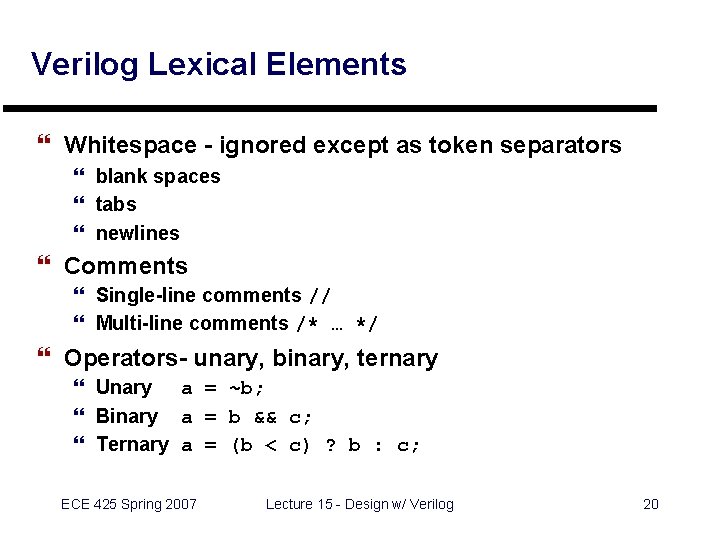

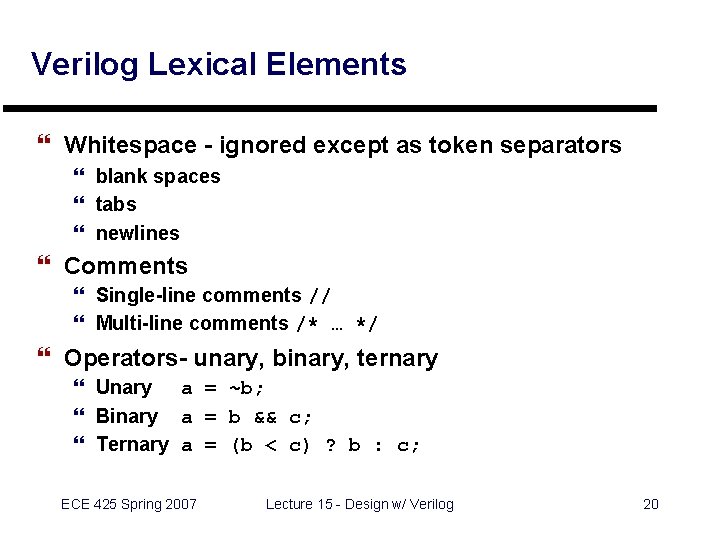

Verilog Lexical Elements } Whitespace - ignored except as token separators } blank spaces } tabs } newlines } Comments } Single-line comments // } Multi-line comments /* … */ } Operators- unary, binary, ternary } Unary a = ~b; } Binary a = b && c; } Ternary a = (b < c) ? b : c; ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 20

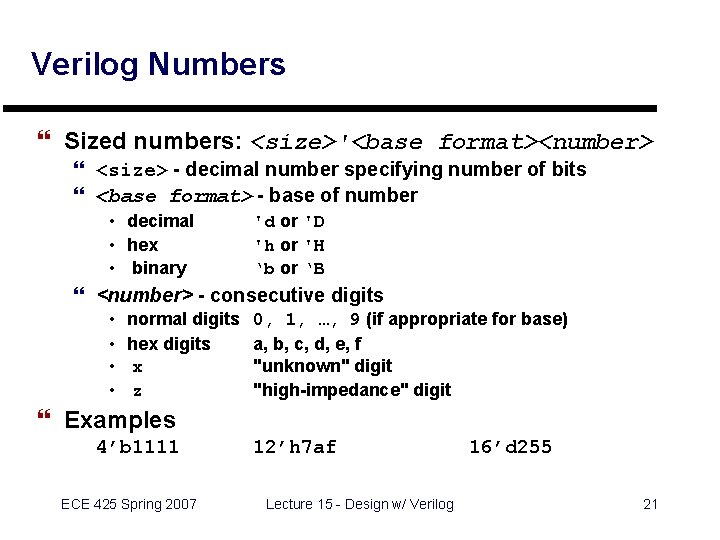

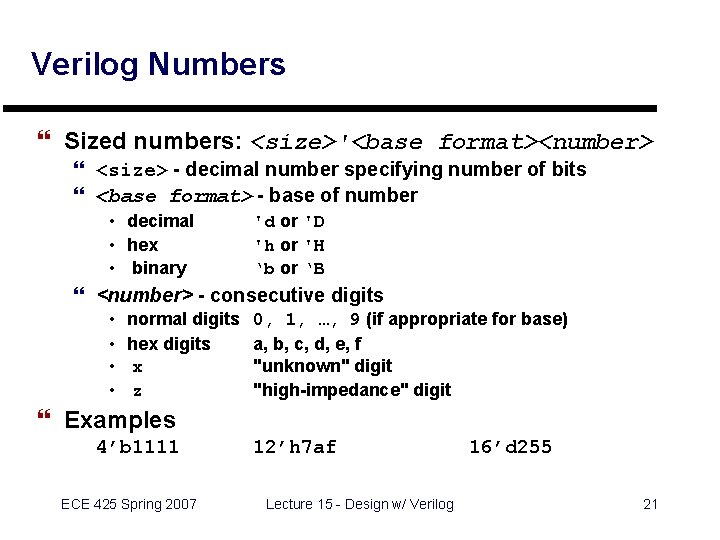

Verilog Numbers } Sized numbers: <size>'<base format><number> } <size> - decimal number specifying number of bits } <base format> - base of number • decimal • hex • binary 'd or 'D 'h or 'H ‘b or ‘B } <number> - consecutive digits • • normal digits hex digits x z 0, 1, …, 9 (if appropriate for base) a, b, c, d, e, f "unknown" digit "high-impedance" digit } Examples 4’b 1111 ECE 425 Spring 2007 12’h 7 af Lecture 15 - Design w/ Verilog 16’d 255 21

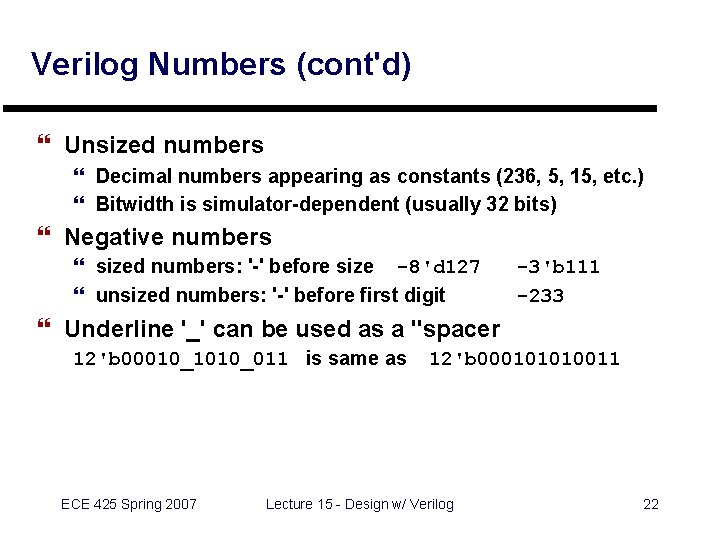

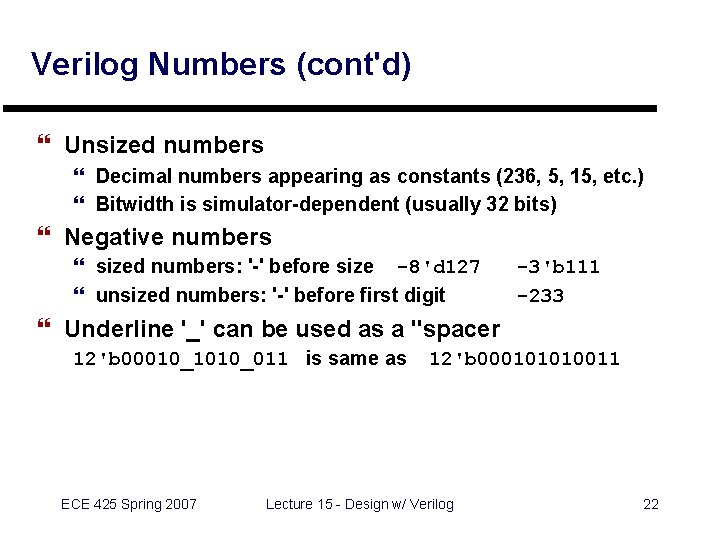

Verilog Numbers (cont'd) } Unsized numbers } Decimal numbers appearing as constants (236, 5, 15, etc. ) } Bitwidth is simulator-dependent (usually 32 bits) } Negative numbers } sized numbers: '-' before size -8'd 127 -3'b 111 } unsized numbers: '-' before first digit -233 } Underline '_' can be used as a "spacer 12'b 00010_1010_011 is same as ECE 425 Spring 2007 12'b 000101010011 Lecture 15 - Design w/ Verilog 22

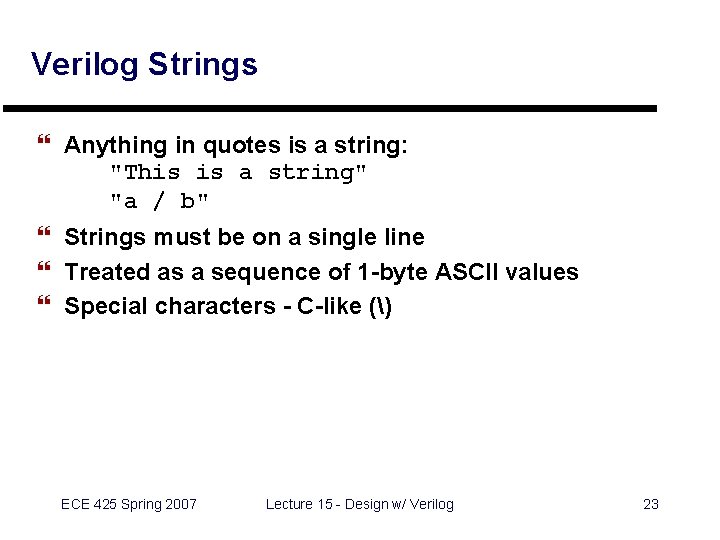

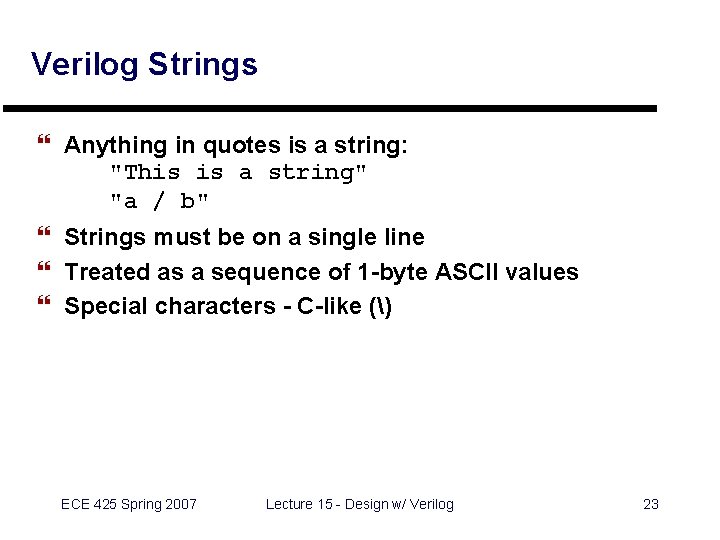

Verilog Strings } Anything in quotes is a string: "This is a string" "a / b" } Strings must be on a single line } Treated as a sequence of 1 -byte ASCII values } Special characters - C-like () ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 23

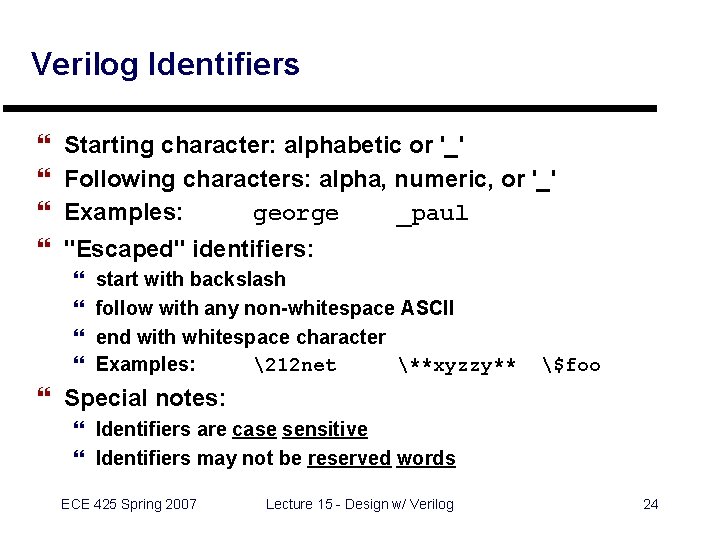

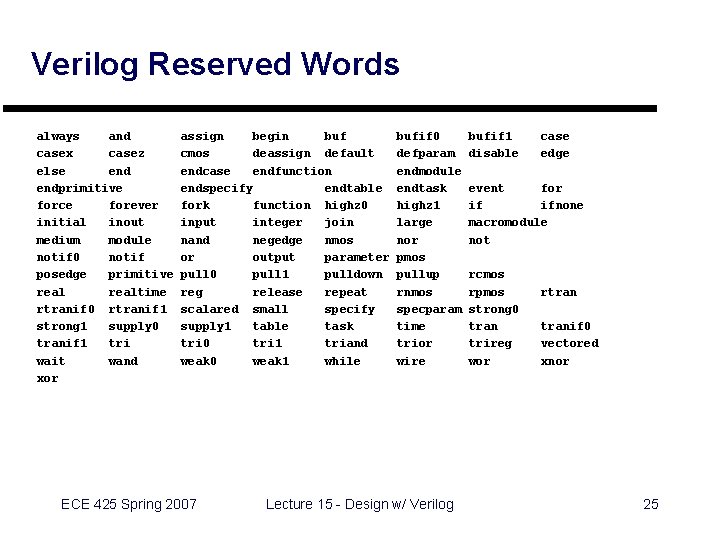

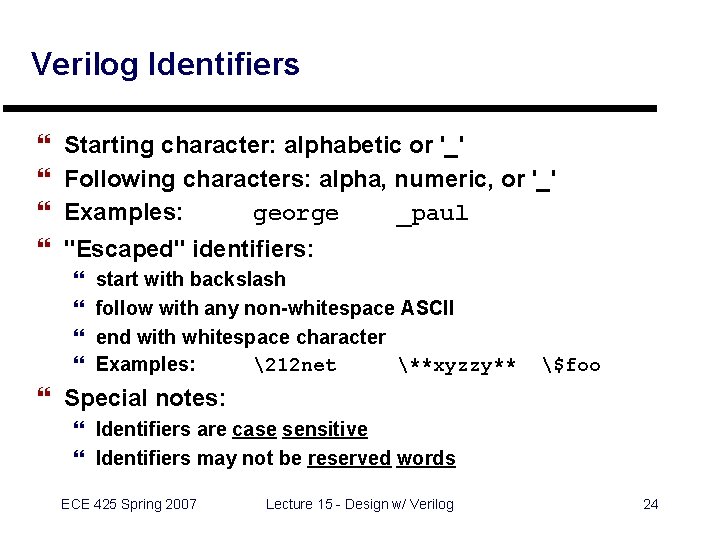

Verilog Identifiers } } Starting character: alphabetic or '_' Following characters: alpha, numeric, or '_' Examples: george _paul "Escaped" identifiers: } } start with backslash follow with any non-whitespace ASCII end with whitespace character Examples: 212 net **xyzzy** $foo } Special notes: } Identifiers are case sensitive } Identifiers may not be reserved words ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 24

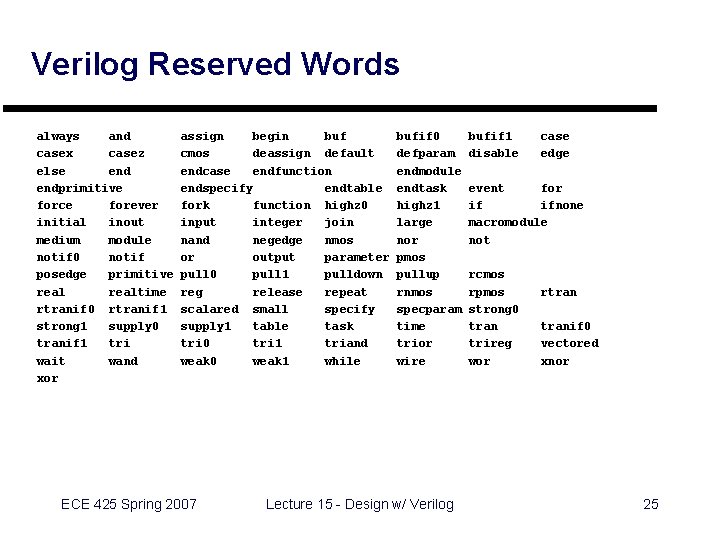

Verilog Reserved Words always and casex casez else endprimitive force forever initial inout medium module notif 0 notif posedge primitive realtime rtranif 0 rtranif 1 strong 1 supply 0 tranif 1 tri wait wand xor assign begin buf cmos deassign default endcase endfunction endspecify endtable fork function highz 0 input integer join nand negedge nmos or output parameter pull 0 pull 1 pulldown reg release repeat scalared small specify supply 1 table task tri 0 tri 1 triand weak 0 weak 1 while ECE 425 Spring 2007 bufif 0 defparam endmodule endtask highz 1 large nor pmos pullup rnmos specparam time trior wire Lecture 15 - Design w/ Verilog bufif 1 disable case edge event for if ifnone macromodule not rcmos rpmos strong 0 tran trireg wor rtranif 0 vectored xnor 25

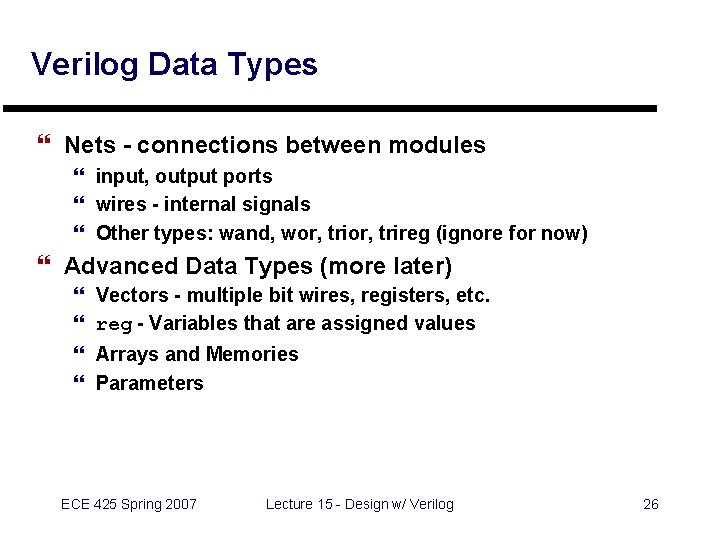

Verilog Data Types } Nets - connections between modules } input, output ports } wires - internal signals } Other types: wand, wor, trireg (ignore for now) } Advanced Data Types (more later) } } Vectors - multiple bit wires, registers, etc. reg - Variables that are assigned values Arrays and Memories Parameters ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 26

Operators and Precedence } Override with parentheses () when needed ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 27

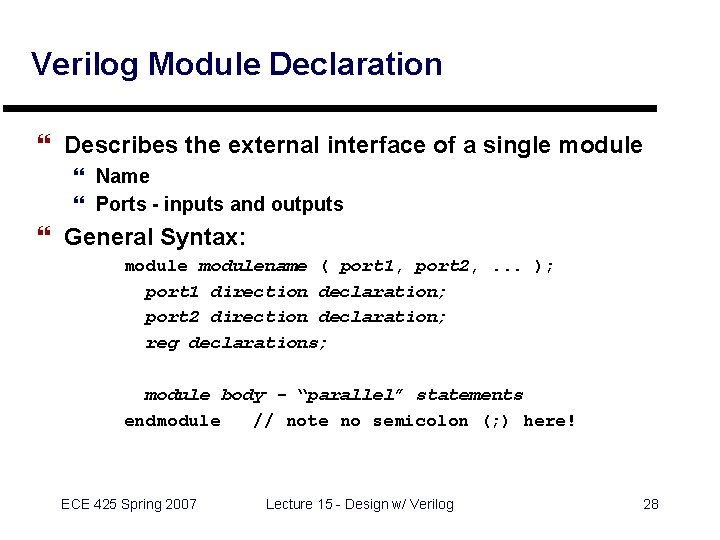

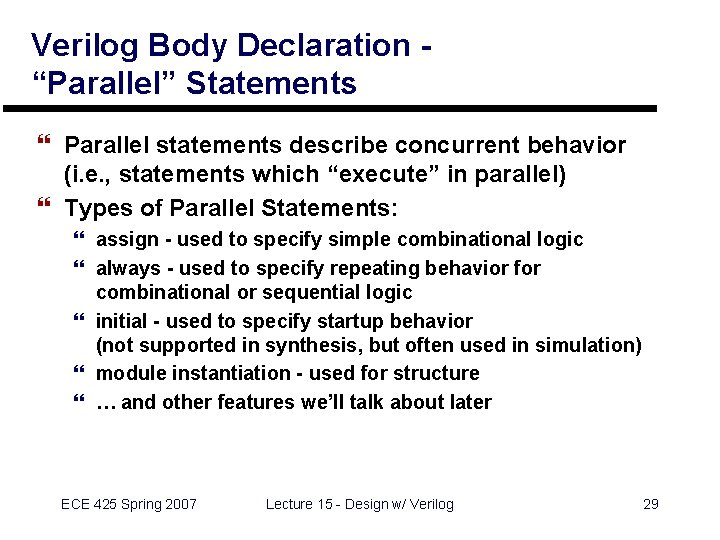

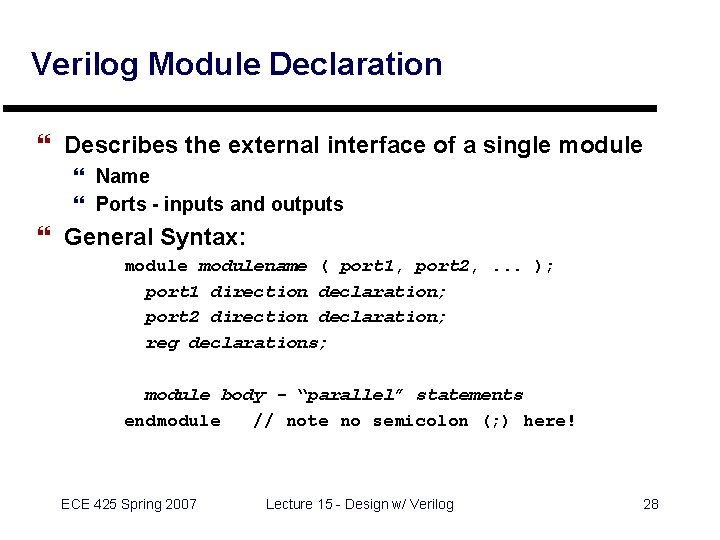

Verilog Module Declaration } Describes the external interface of a single module } Name } Ports - inputs and outputs } General Syntax: modulename ( port 1, port 2, . . . ); port 1 direction declaration; port 2 direction declaration; reg declarations; module body - “parallel” statements endmodule // note no semicolon (; ) here! ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 28

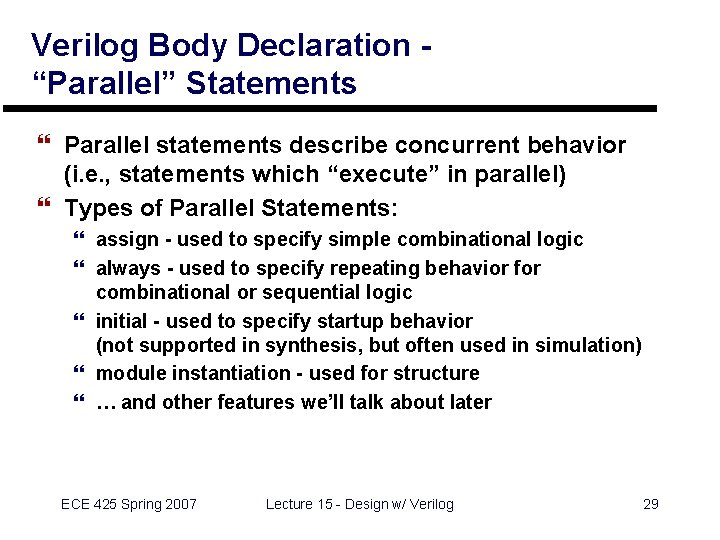

Verilog Body Declaration “Parallel” Statements } Parallel statements describe concurrent behavior (i. e. , statements which “execute” in parallel) } Types of Parallel Statements: } assign - used to specify simple combinational logic } always - used to specify repeating behavior for combinational or sequential logic } initial - used to specify startup behavior (not supported in synthesis, but often used in simulation) } module instantiation - used for structure } … and other features we’ll talk about later ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 29

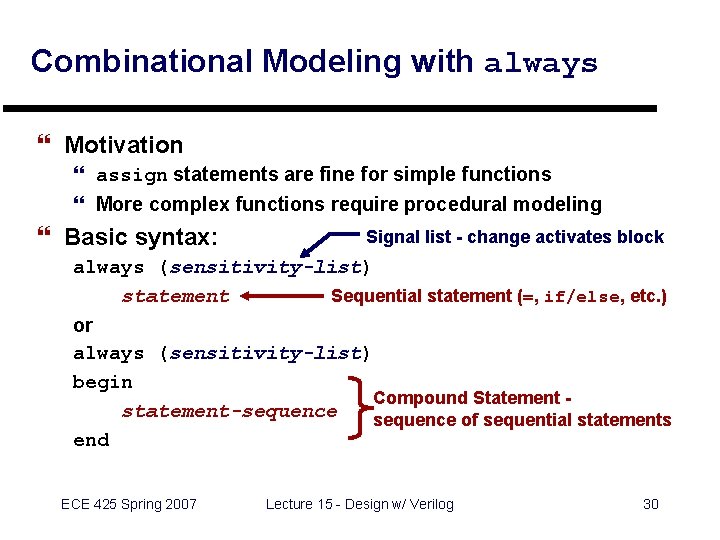

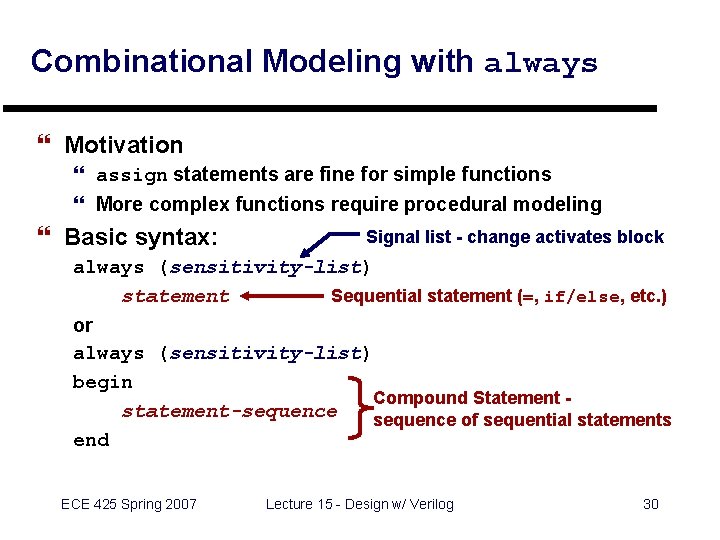

Combinational Modeling with always } Motivation } assign statements are fine for simple functions } More complex functions require procedural modeling } Basic syntax: Signal list - change activates block always (sensitivity-list) Sequential statement (=, if/else, etc. ) statement or always (sensitivity-list) begin Compound Statement statement-sequence of sequential statements end ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 30

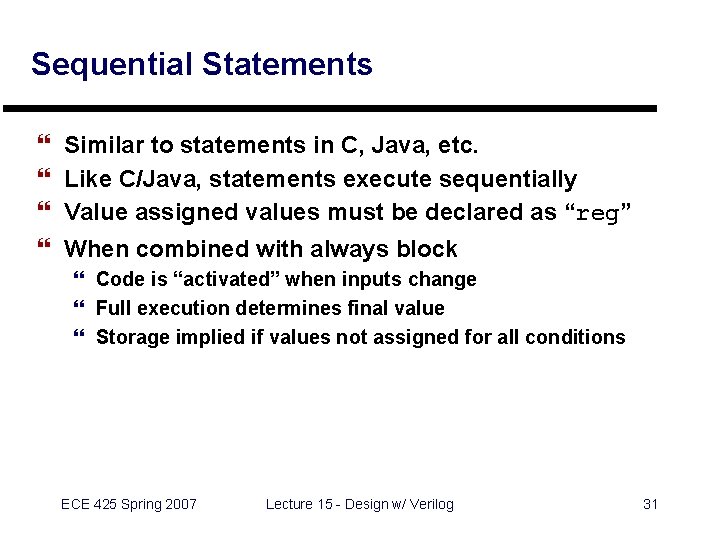

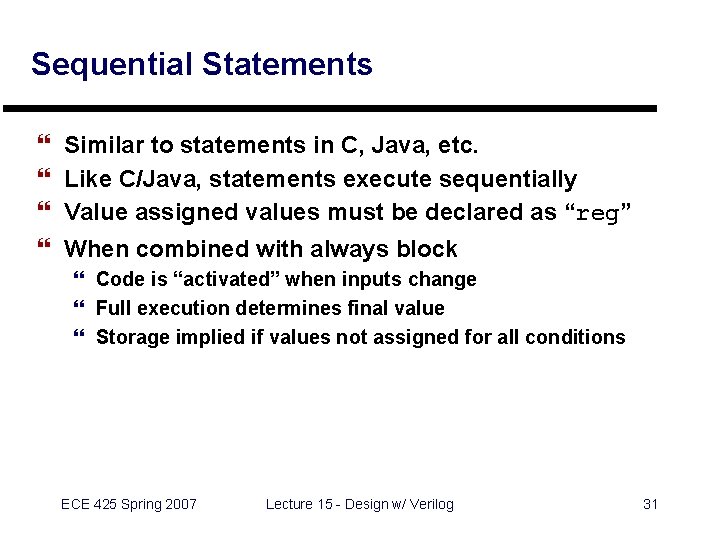

Sequential Statements } } Similar to statements in C, Java, etc. Like C/Java, statements execute sequentially Value assigned values must be declared as “reg” When combined with always block } Code is “activated” when inputs change } Full execution determines final value } Storage implied if values not assigned for all conditions ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 31

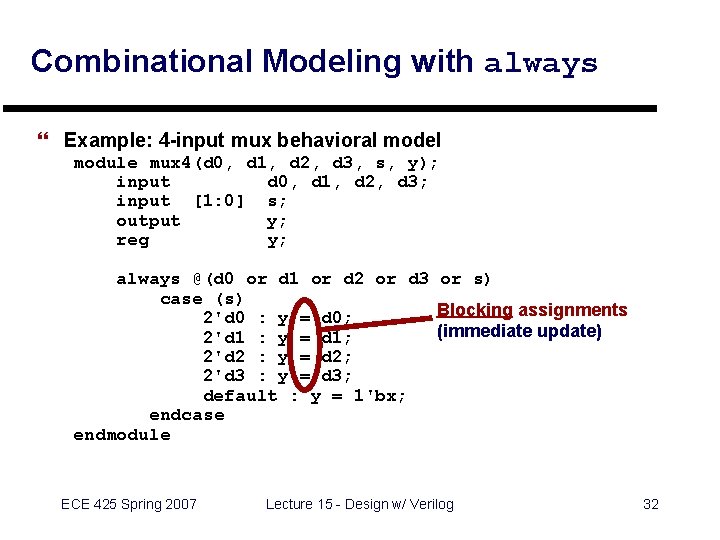

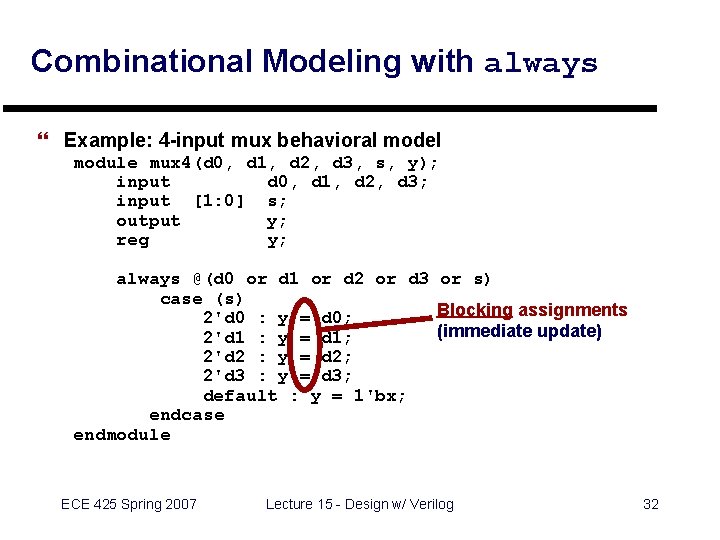

Combinational Modeling with always } Example: 4 -input mux behavioral model module mux 4(d 0, d 1, d 2, d 3, s, y); input d 0, d 1, d 2, d 3; input [1: 0] s; output y; reg y; always @(d 0 or d 1 or d 2 or d 3 or s) case (s) Blocking assignments 2'd 0 : y = d 0; (immediate update) 2'd 1 : y = d 1; 2'd 2 : y = d 2; 2'd 3 : y = d 3; default : y = 1'bx; endcase endmodule ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 32

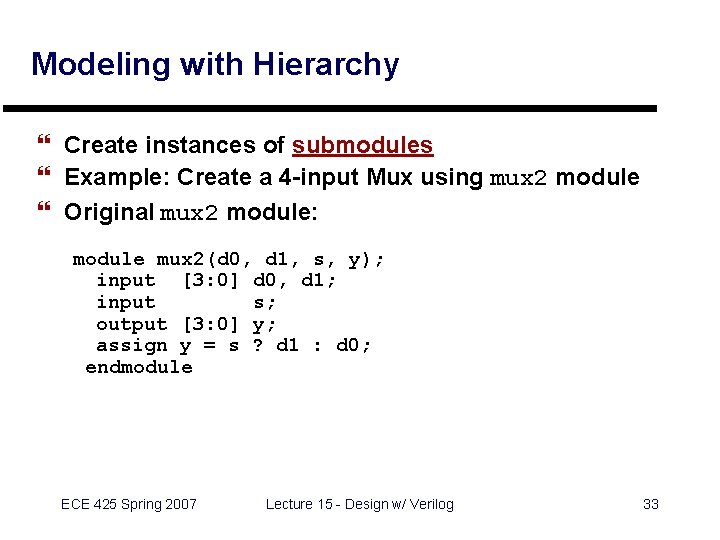

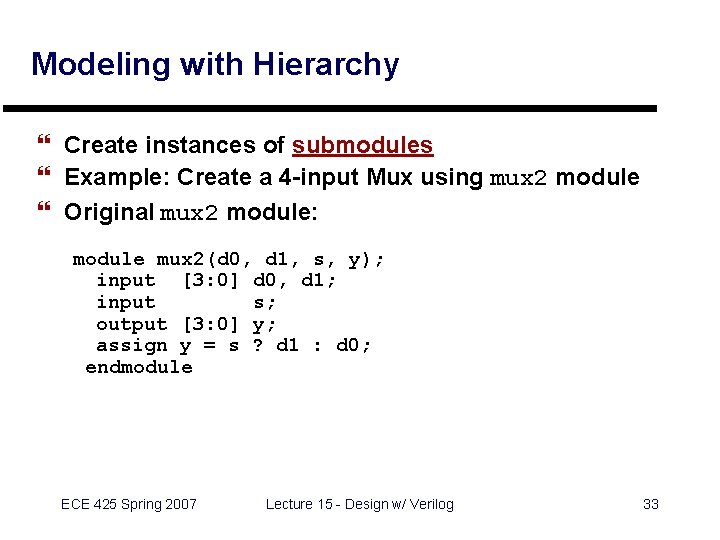

Modeling with Hierarchy } Create instances of submodules } Example: Create a 4 -input Mux using mux 2 module } Original mux 2 module: module mux 2(d 0, d 1, s, y); input [3: 0] d 0, d 1; input s; output [3: 0] y; assign y = s ? d 1 : d 0; endmodule ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 33

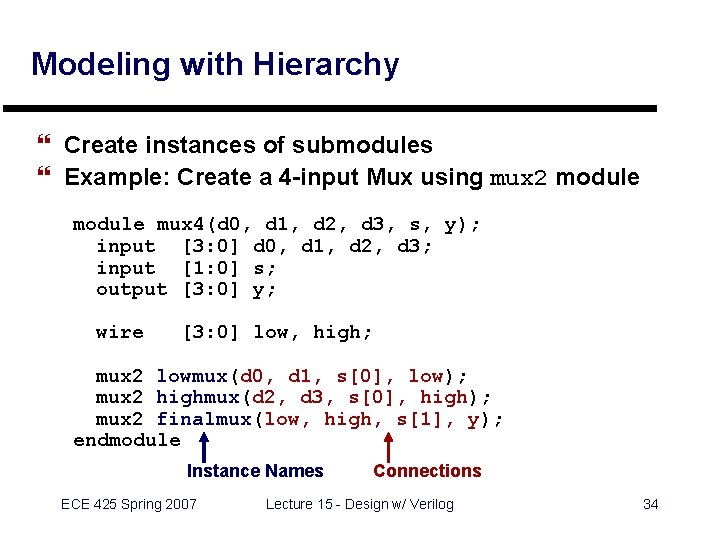

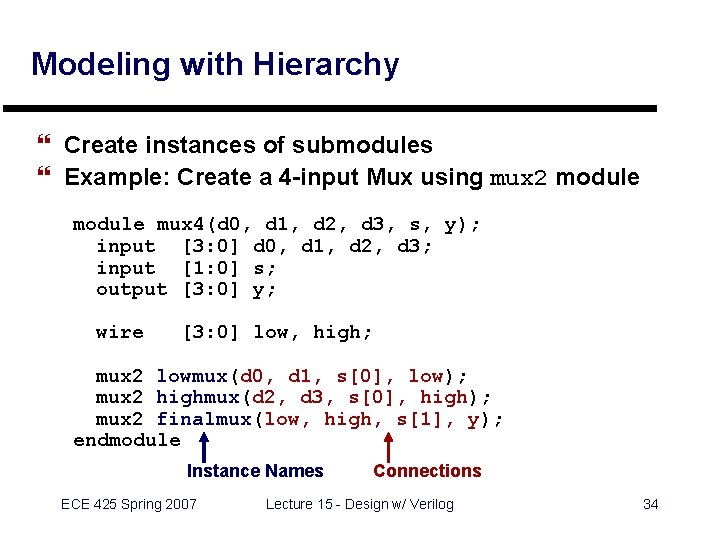

Modeling with Hierarchy } Create instances of submodules } Example: Create a 4 -input Mux using mux 2 module mux 4(d 0, d 1, d 2, d 3, s, y); input [3: 0] d 0, d 1, d 2, d 3; input [1: 0] s; output [3: 0] y; wire [3: 0] low, high; mux 2 lowmux(d 0, d 1, s[0], low); mux 2 highmux(d 2, d 3, s[0], high); mux 2 finalmux(low, high, s[1], y); endmodule Instance Names ECE 425 Spring 2007 Connections Lecture 15 - Design w/ Verilog 34

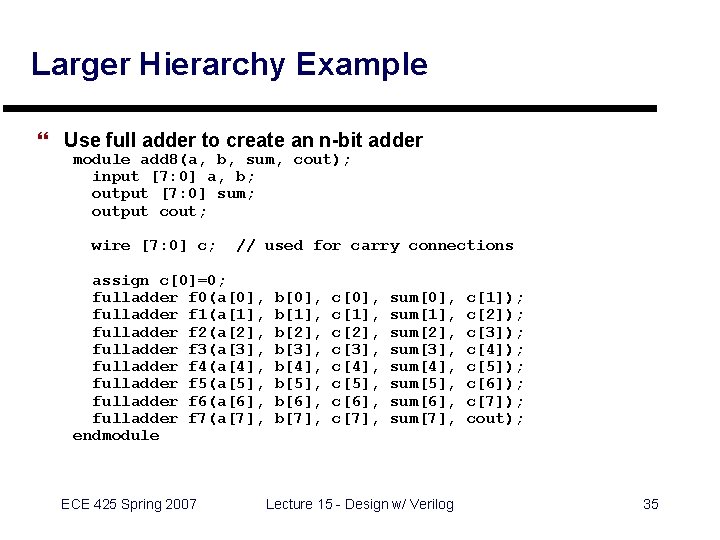

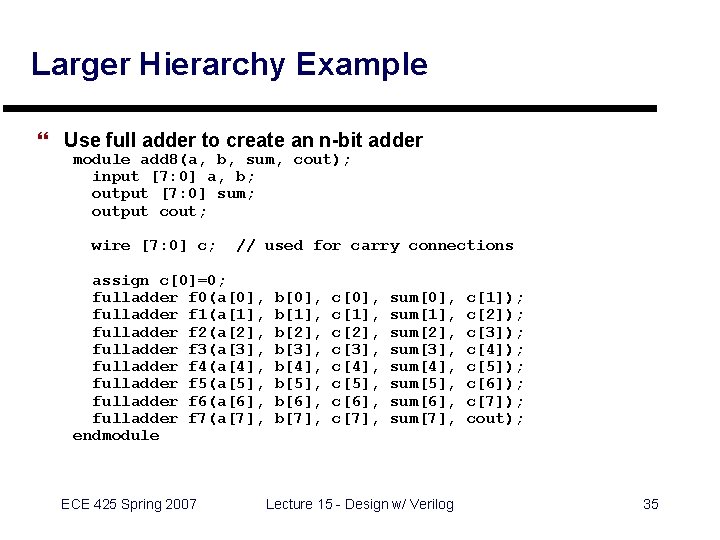

Larger Hierarchy Example } Use full adder to create an n-bit adder module add 8(a, b, sum, cout); input [7: 0] a, b; output [7: 0] sum; output cout; wire [7: 0] c; // used for carry connections assign c[0]=0; fulladder f 0(a[0], b[0], c[0], sum[0], c[1]); fulladder f 1(a[1], b[1], c[1], sum[1], c[2]); fulladder f 2(a[2], b[2], c[2], sum[2], c[3]); fulladder f 3(a[3], b[3], c[3], sum[3], c[4]); fulladder f 4(a[4], b[4], c[4], sum[4], c[5]); fulladder f 5(a[5], b[5], c[5], sum[5], c[6]); fulladder f 6(a[6], b[6], c[6], sum[6], c[7]); fulladder f 7(a[7], b[7], c[7], sum[7], cout); endmodule ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 35

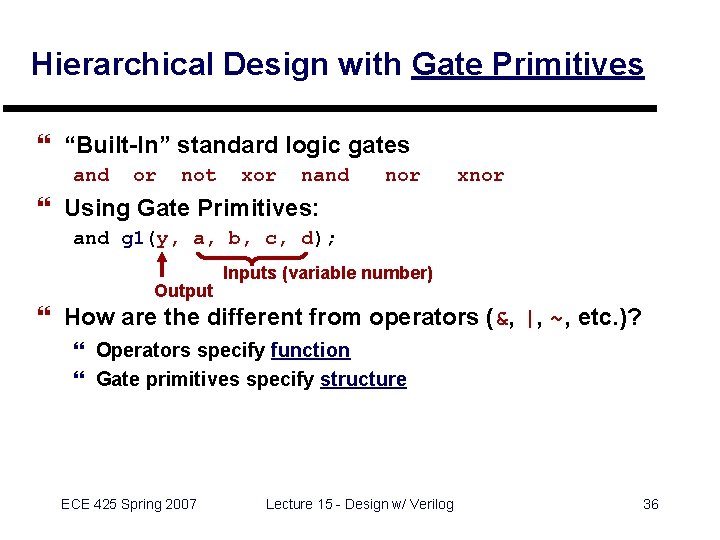

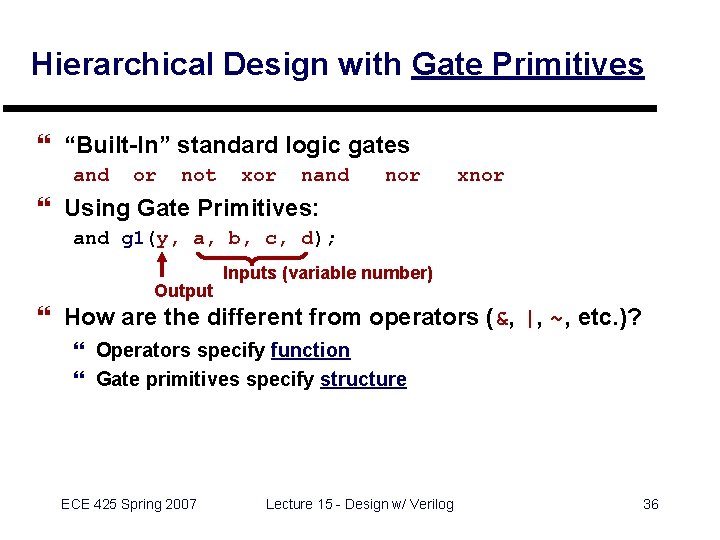

Hierarchical Design with Gate Primitives } “Built-In” standard logic gates and or not xor nand nor xnor } Using Gate Primitives: and g 1(y, a, b, c, d); Output Inputs (variable number) } How are the different from operators (&, |, ~, etc. )? } Operators specify function } Gate primitives specify structure ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 36

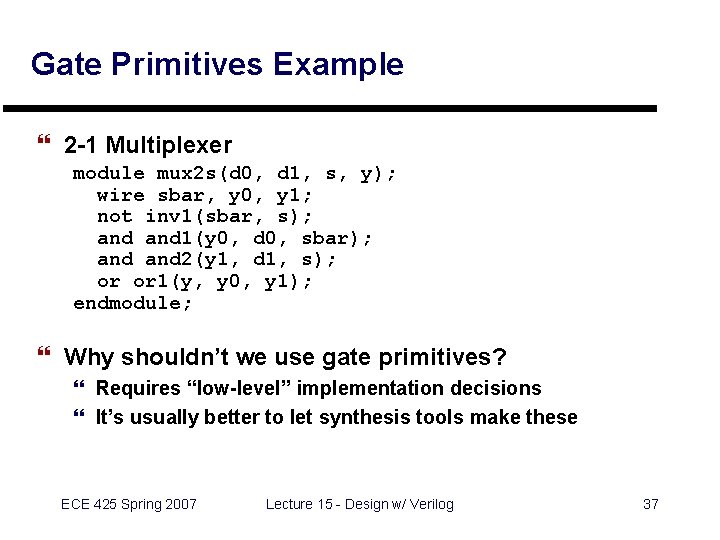

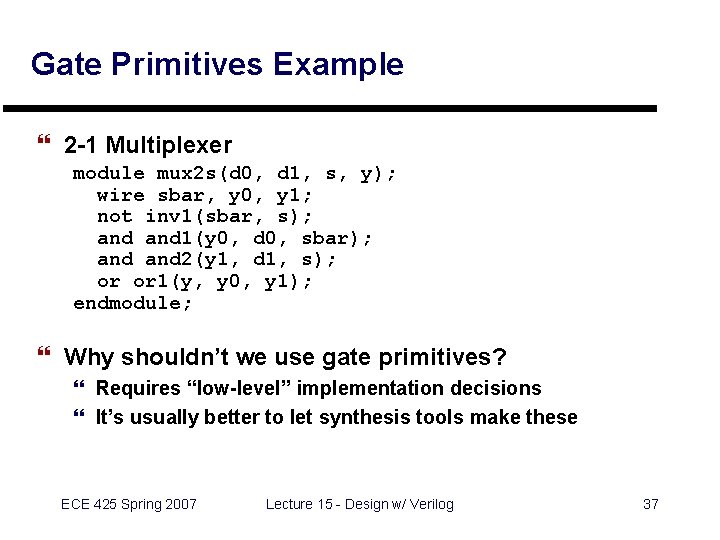

Gate Primitives Example } 2 -1 Multiplexer module mux 2 s(d 0, d 1, s, y); wire sbar, y 0, y 1; not inv 1(sbar, s); and 1(y 0, d 0, sbar); and 2(y 1, d 1, s); or or 1(y, y 0, y 1); endmodule; } Why shouldn’t we use gate primitives? } Requires “low-level” implementation decisions } It’s usually better to let synthesis tools make these ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 37

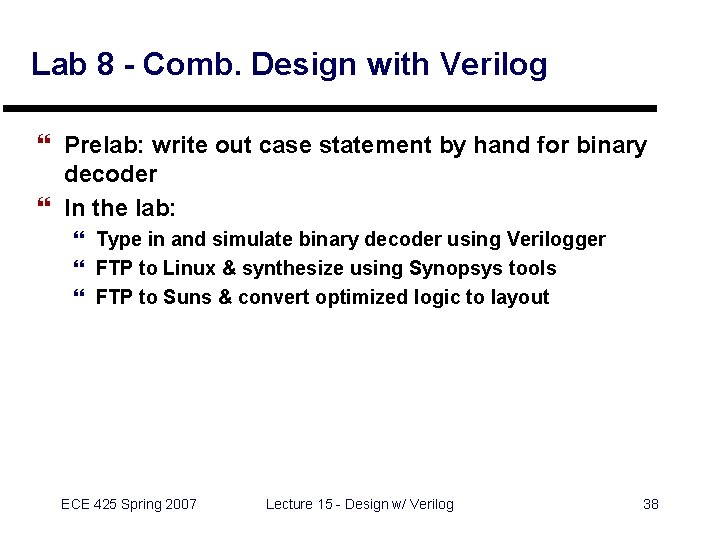

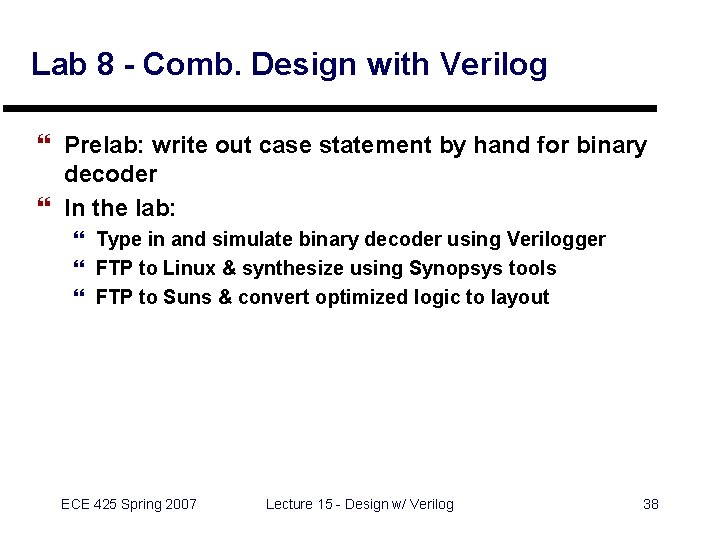

Lab 8 - Comb. Design with Verilog } Prelab: write out case statement by hand for binary decoder } In the lab: } Type in and simulate binary decoder using Verilogger } FTP to Linux & synthesize using Synopsys tools } FTP to Suns & convert optimized logic to layout ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 38

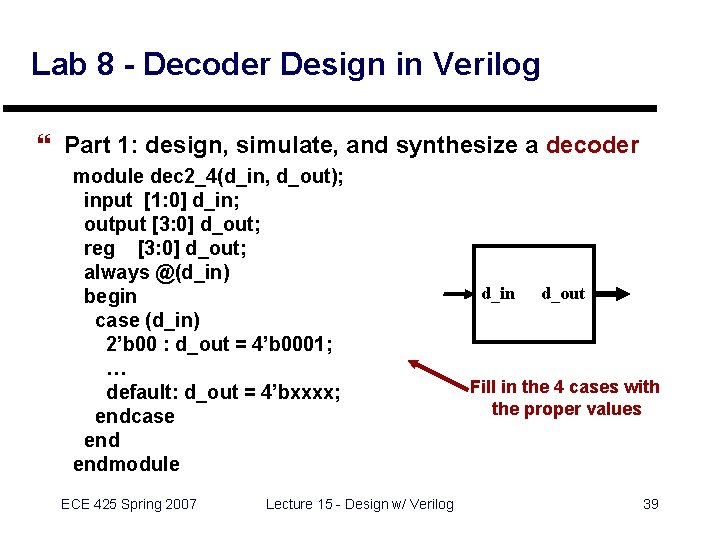

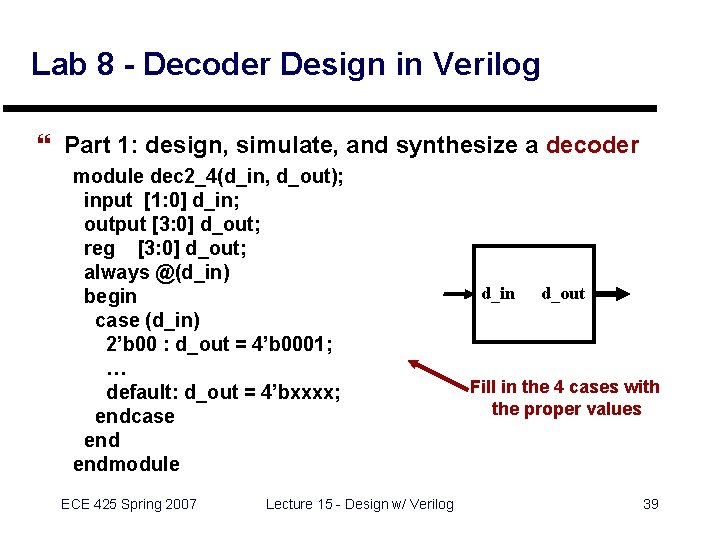

Lab 8 - Decoder Design in Verilog } Part 1: design, simulate, and synthesize a decoder module dec 2_4(d_in, d_out); input [1: 0] d_in; output [3: 0] d_out; reg [3: 0] d_out; always @(d_in) begin case (d_in) 2’b 00 : d_out = 4’b 0001; … default: d_out = 4’bxxxx; endcase endmodule ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog d_in d_out Fill in the 4 cases with the proper values 39

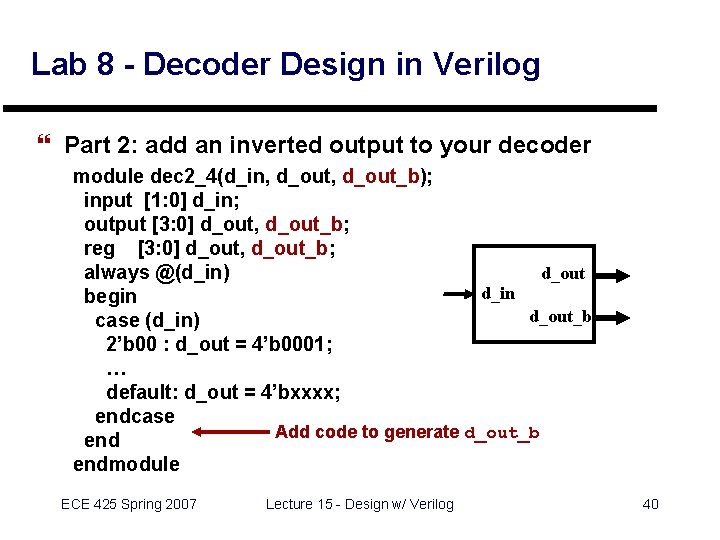

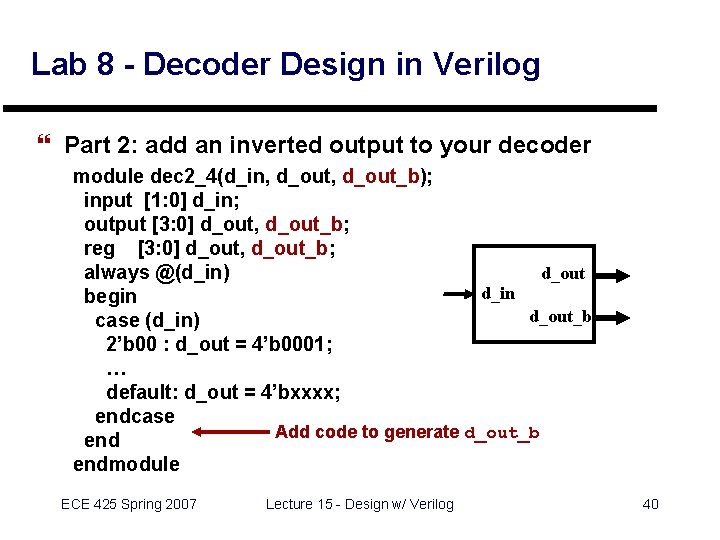

Lab 8 - Decoder Design in Verilog } Part 2: add an inverted output to your decoder module dec 2_4(d_in, d_out_b); input [1: 0] d_in; output [3: 0] d_out, d_out_b; reg [3: 0] d_out, d_out_b; always @(d_in) d_out d_in begin d_out_b case (d_in) 2’b 00 : d_out = 4’b 0001; … default: d_out = 4’bxxxx; endcase Add code to generate d_out_b endmodule ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 40

Lab 8 - Additional Tasks } Modify decoder to intentionally create a “latch inference” and synthesize } Create, simulate, and synthesize designs for: } Row decoder for D/A converter (include d 2 input) } 4 -bit incrementer } 4 -bit adder ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 41

Lab 8 - CAD Tools } } Verilogger - simulator Synopsys - synthesis db 2 mag - placement/routing magic - use to view resulting layout ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 42

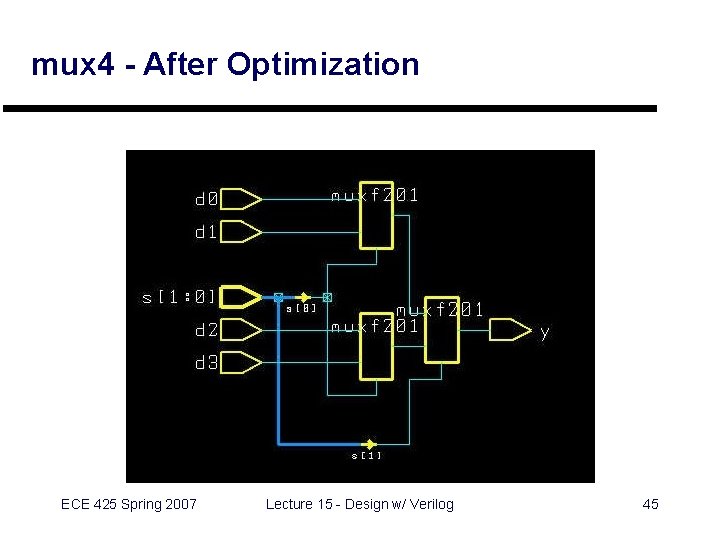

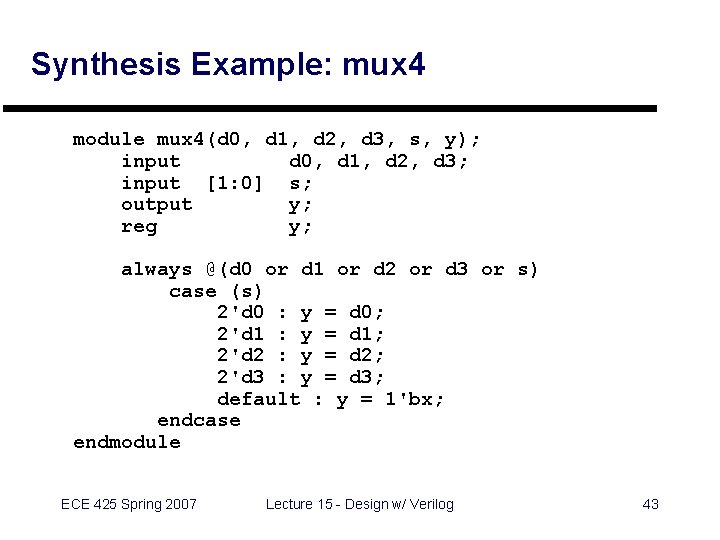

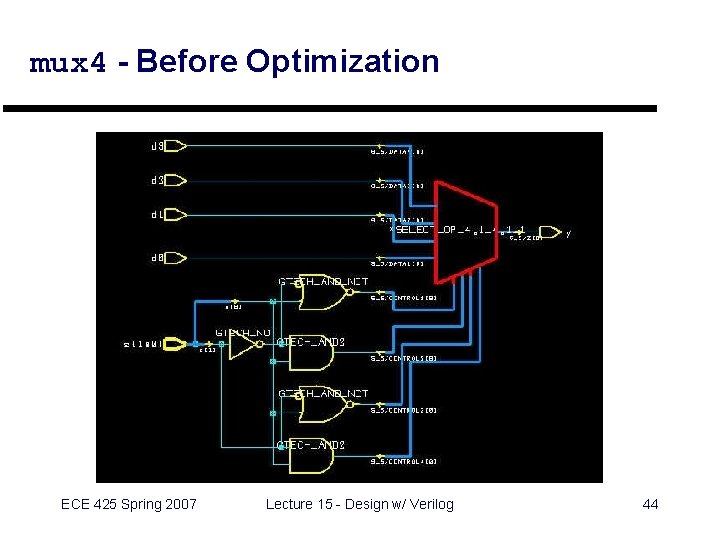

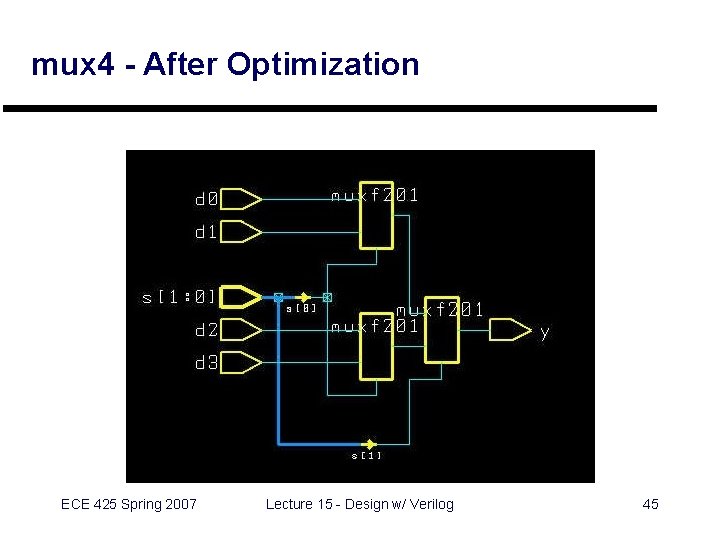

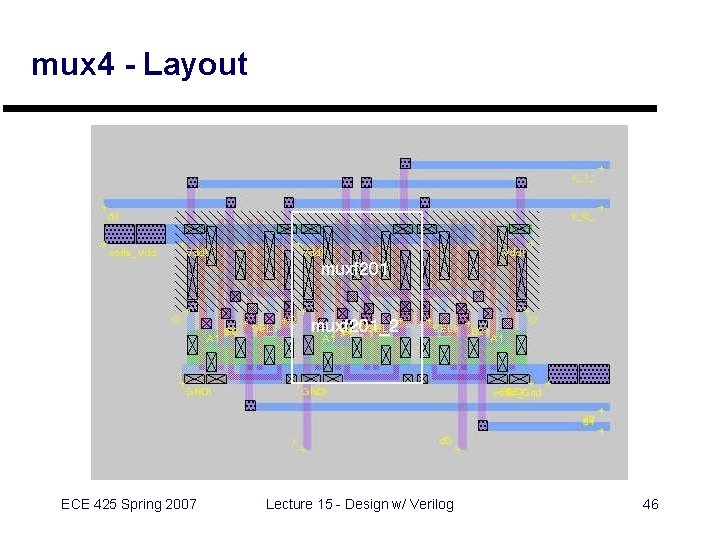

Synthesis Example: mux 4 module mux 4(d 0, d 1, d 2, d 3, s, y); input d 0, d 1, d 2, d 3; input [1: 0] s; output y; reg y; always @(d 0 or d 1 or d 2 or d 3 or s) case (s) 2'd 0 : y = d 0; 2'd 1 : y = d 1; 2'd 2 : y = d 2; 2'd 3 : y = d 3; default : y = 1'bx; endcase endmodule ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 43

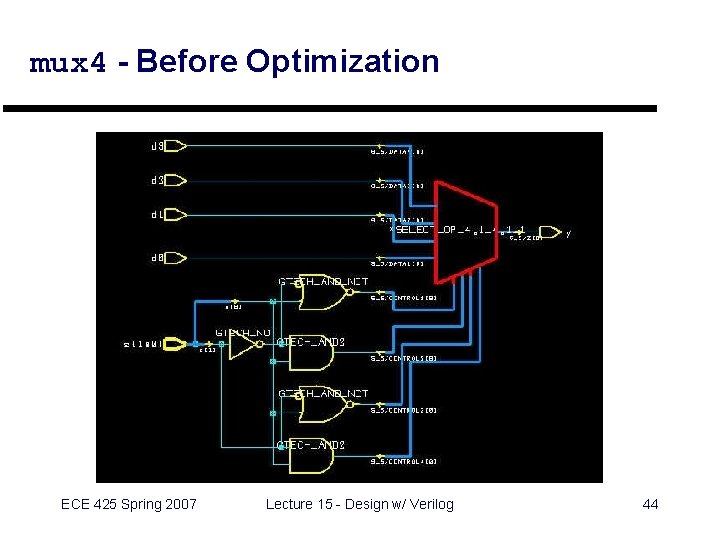

mux 4 - Before Optimization ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 44

mux 4 - After Optimization ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 45

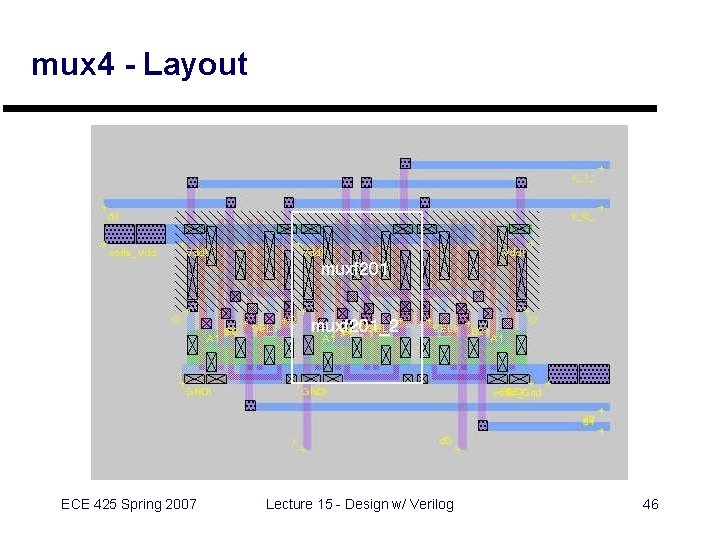

mux 4 - Layout ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 46

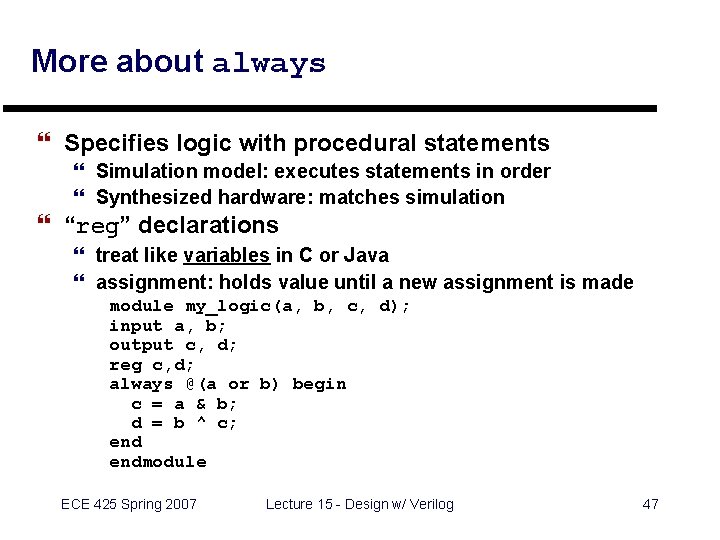

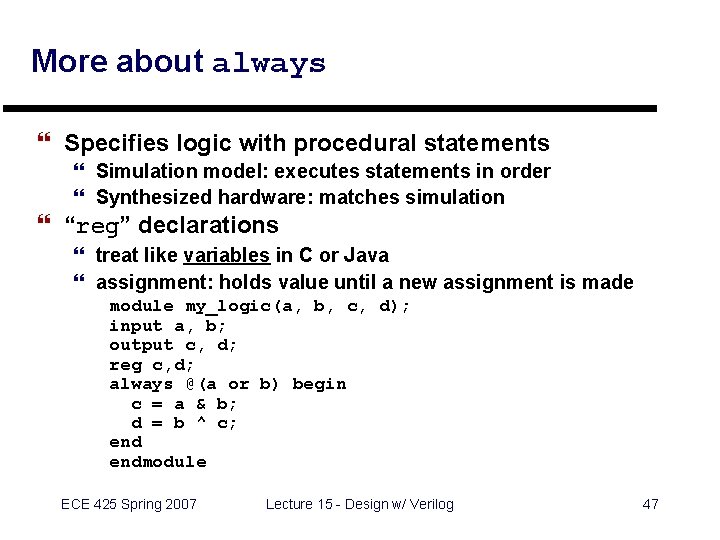

More about always } Specifies logic with procedural statements } Simulation model: executes statements in order } Synthesized hardware: matches simulation } “reg” declarations } treat like variables in C or Java } assignment: holds value until a new assignment is made module my_logic(a, b, c, d); input a, b; output c, d; reg c, d; always @(a or b) begin c = a & b; d = b ^ c; endmodule ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 47

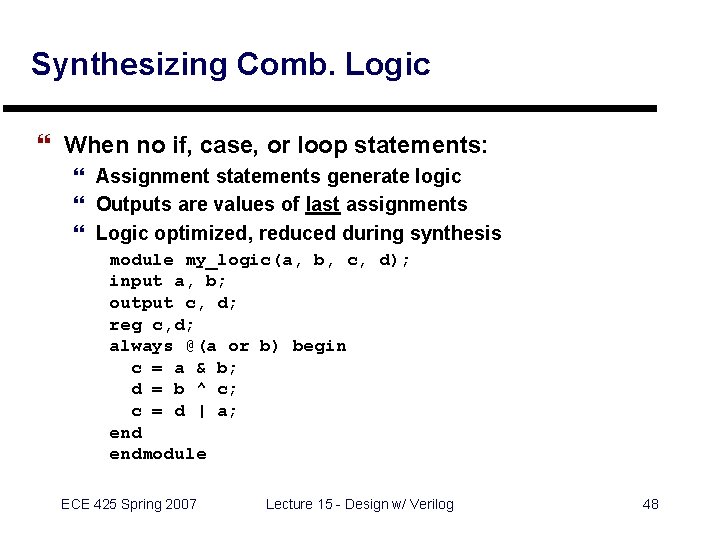

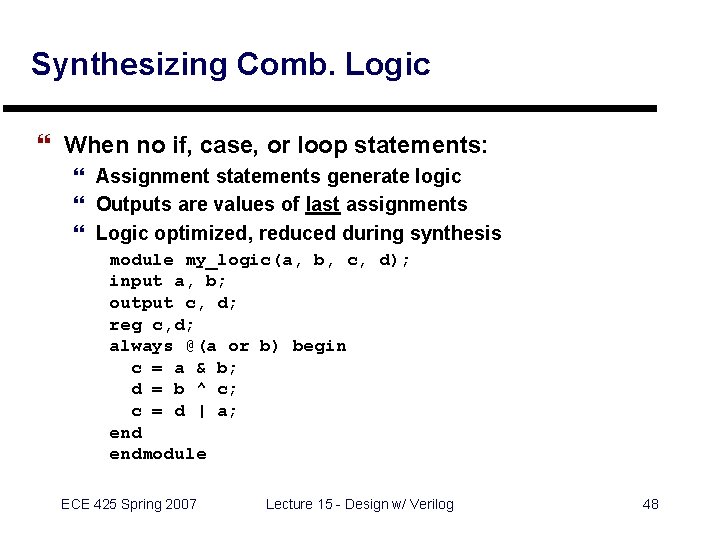

Synthesizing Comb. Logic } When no if, case, or loop statements: } Assignment statements generate logic } Outputs are values of last assignments } Logic optimized, reduced during synthesis module my_logic(a, b, c, d); input a, b; output c, d; reg c, d; always @(a or b) begin c = a & b; d = b ^ c; c = d | a; endmodule ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 48

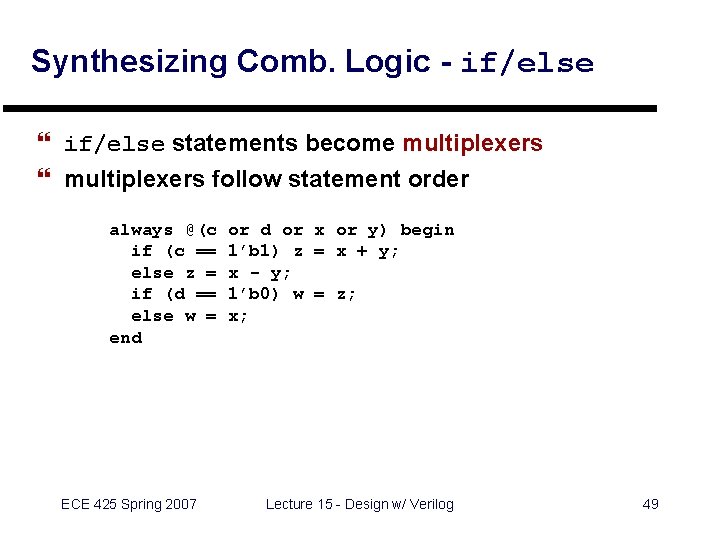

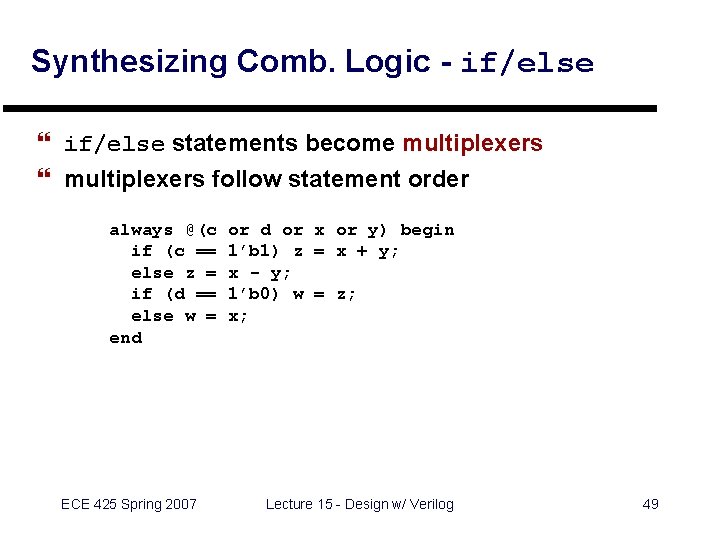

Synthesizing Comb. Logic - if/else } if/else statements become multiplexers } multiplexers follow statement order always @(c or d or x or y) begin if (c == 1’b 1) z = x + y; else z = x - y; if (d == 1’b 0) w = z; else w = x; end ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 49

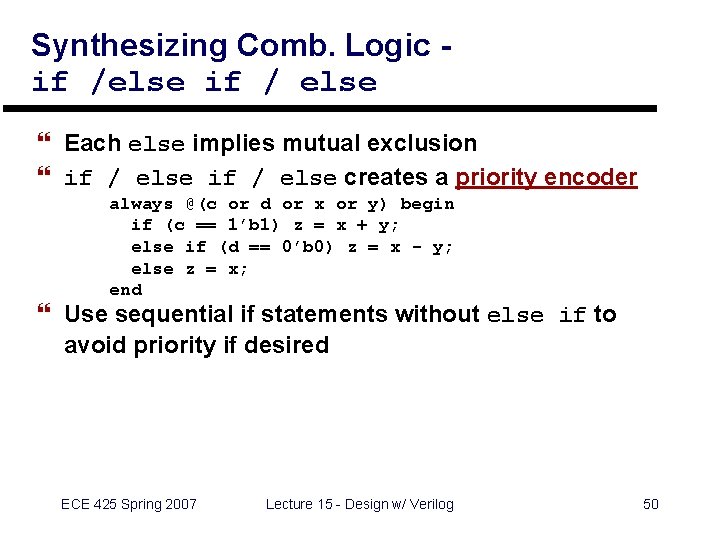

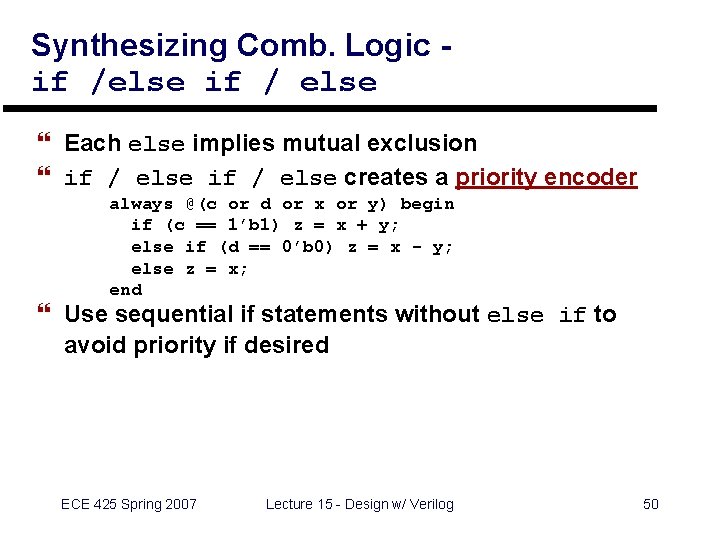

Synthesizing Comb. Logic if /else if / else } Each else implies mutual exclusion } if / else creates a priority encoder always @(c or d or x or y) begin if (c == 1’b 1) z = x + y; else if (d == 0’b 0) z = x - y; else z = x; end } Use sequential if statements without else if to avoid priority if desired ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 50

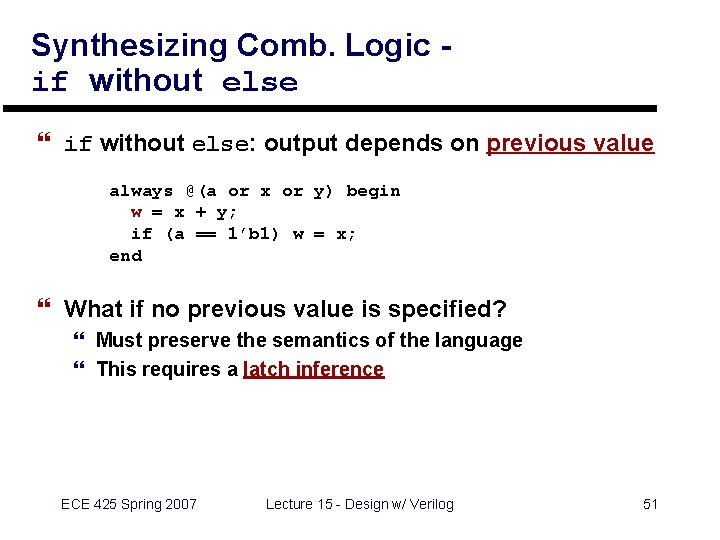

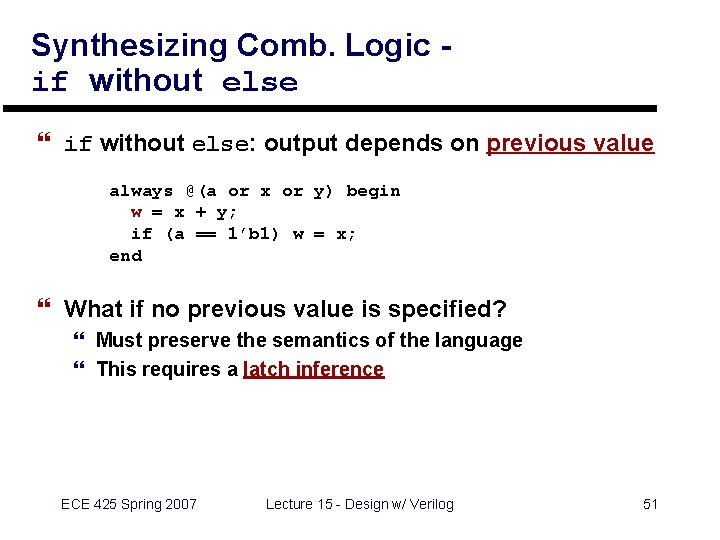

Synthesizing Comb. Logic if without else } if without else: output depends on previous value always @(a or x or y) begin w = x + y; if (a == 1’b 1) w = x; end } What if no previous value is specified? } Must preserve the semantics of the language } This requires a latch inference ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 51

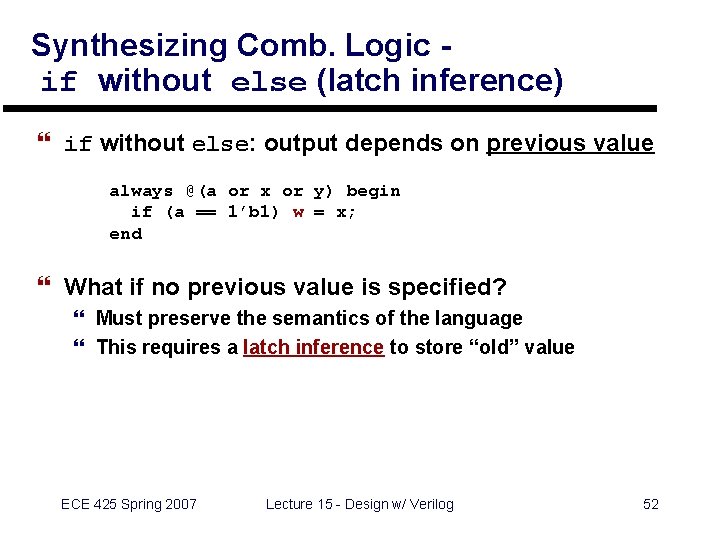

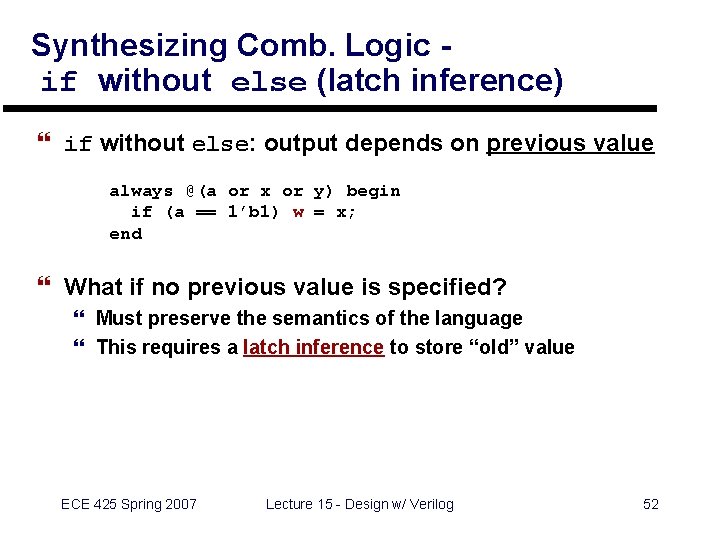

Synthesizing Comb. Logic if without else (latch inference) } if without else: output depends on previous value always @(a or x or y) begin if (a == 1’b 1) w = x; end } What if no previous value is specified? } Must preserve the semantics of the language } This requires a latch inference to store “old” value ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 52

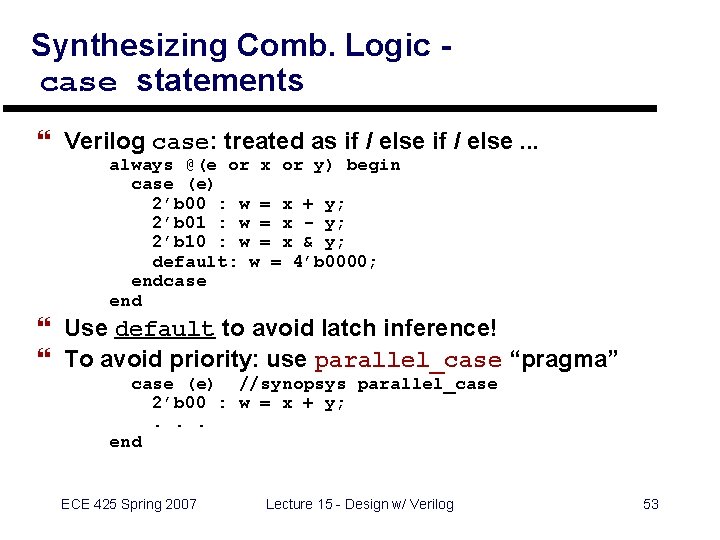

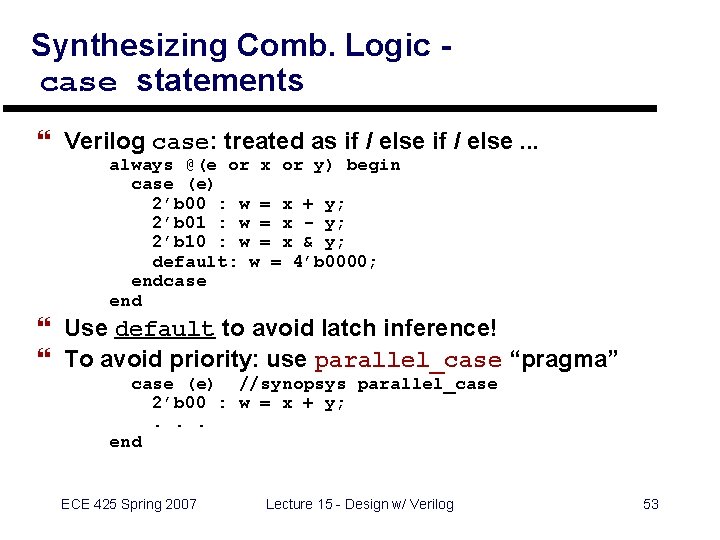

Synthesizing Comb. Logic case statements } Verilog case: treated as if / else. . . always @(e or x or y) begin case (e) 2’b 00 : w = x + y; 2’b 01 : w = x - y; 2’b 10 : w = x & y; default: w = 4’b 0000; endcase end } Use default to avoid latch inference! } To avoid priority: use parallel_case “pragma” case (e) //synopsys parallel_case 2’b 00 : w = x + y; . . . end ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 53

Coming Up } Sequential Logic } Latches } Flip-Flops } Finite State Machines ECE 425 Spring 2007 Lecture 15 - Design w/ Verilog 54