ECE 354 Lecture 1 The Big Picture What

ECE 354 Lecture 1 The Big Picture § What are embedded systems? § Challenges in embedded computing system design. § Design methodologies. § § § ECE 354 © Koren/Moritz 2008, Sophisticated functionality. Real-time operation. Low manufacturing cost. Low power. Designed to tight deadlines by small teams. some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 1

Definition § Embedded system: any device that includes a programmable computer but is not itself a general-purpose computer. § Take advantage of application characteristics to optimize the design: • don’t need all the general-purpose bells and whistles. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 2

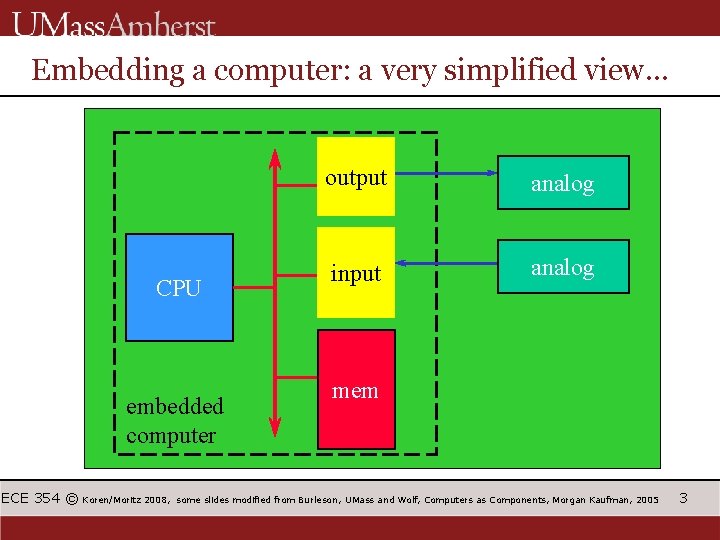

Embedding a computer: a very simplified view… CPU embedded computer ECE 354 © Koren/Moritz 2008, output analog input analog mem some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 3

Examples § § § Personal digital assistant (PDA). Printer. Cell phone. Automobile: engine, brakes, dash, etc. Television. Household appliances. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 4

More examples § Cell phones, Ipod and MP 3 players, Webcams, Navigation Systems § Routers, Blade servers, Wireless PC cards § Automobiles, Car Alarms, Keyless Entry Systems § Building Security, card swiping systems § Embedded Medical Devices - Pacemakers ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 5

Characteristics of embedded systems § § § Sophisticated functionality. Real-time operation. Low manufacturing cost. Low power. Reliable and secure Designed to tight deadlines by small teams. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 6

Functional complexity § Often have to run sophisticated algorithms or multiple algorithms. • Cell phone, laser printer. § Often provide sophisticated user interfaces. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 7

Real-time operation § Must finish operations by deadlines. • Hard real time: missing deadline causes failure. • Soft real time: missing deadline results in degraded performance. § Many systems are multi-rate: must handle operations at widely varying rates. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 8

Non-functional requirements § Many embedded systems are mass-market items that must have low manufacturing costs. • Limited memory, microprocessor power, etc. § Power consumption is critical in battery-powered devices. • Excessive power consumption increases system cost even in wall-powered devices. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 9

Design teams § Often designed by a small team of designers. § Often must meet tight deadlines. • 6 month market window is common. • E. g. , can’t miss back-to-school window for calculator. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 10

Microprocessor alternatives for embedded systems § Ordinary microprocessor: CPU plus on-chip cache units. § Microcontroller: includes I/O devices, on-board memory. § Digital signal processor (DSP): microprocessor optimized for digital signal processing. § Hard core vs. soft core. § Typical embedded word sizes: 8 -bit, 16 -bit, 32 bit. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 11

Embedded microprocessors § ARM, MIPS, Power PC, Freescale, 8051, X 86 § Various purposes • • • Networks – MIPS Mobile phone – ARM dominated Industrial – Freescale Coldfire Security – 8051 based, Infineon High performance – X 86, Intel Epic, other VLIW and superscalars ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 12

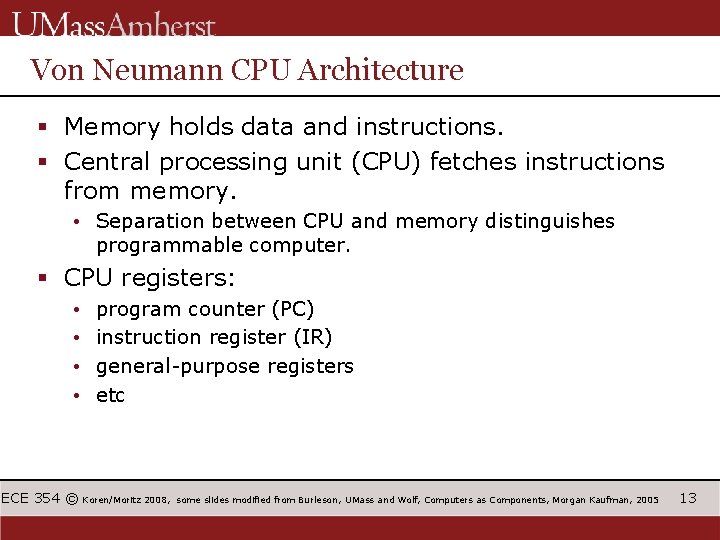

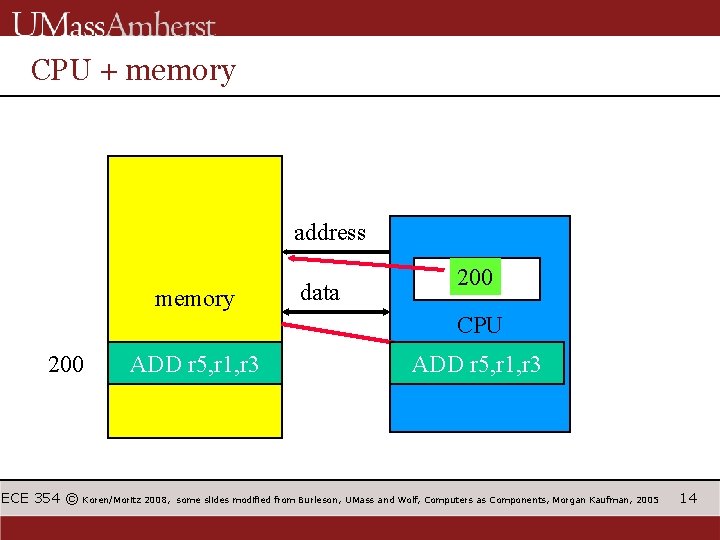

Von Neumann CPU Architecture § Memory holds data and instructions. § Central processing unit (CPU) fetches instructions from memory. • Separation between CPU and memory distinguishes programmable computer. § CPU registers: • • program counter (PC) instruction register (IR) general-purpose registers etc ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 13

CPU + memory address memory data 200 PC CPU 200 ADD r 5, r 1, r 3 ECE 354 © Koren/Moritz 2008, ADD IR r 5, r 1, r 3 some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 14

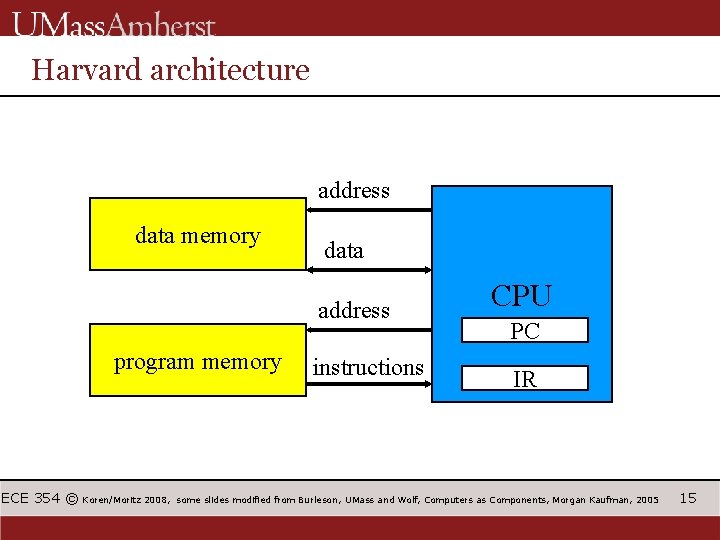

Harvard architecture address data memory data address program memory ECE 354 © Koren/Moritz 2008, instructions CPU PC IR some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 15

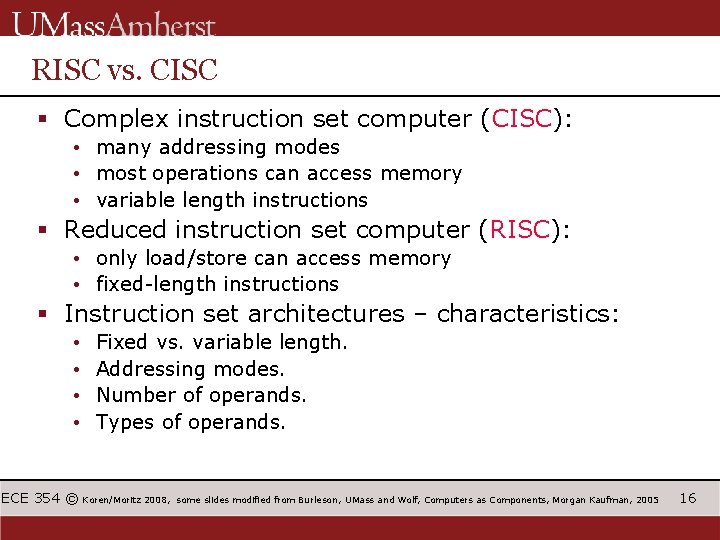

RISC vs. CISC § Complex instruction set computer (CISC): • many addressing modes • most operations can access memory • variable length instructions § Reduced instruction set computer (RISC): • only load/store can access memory • fixed-length instructions § Instruction set architectures – characteristics: • • Fixed vs. variable length. Addressing modes. Number of operands. Types of operands. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 16

Multiple implementations of an ISA § Instruction set architectures may have several implementations: • • varying clock speeds; different bus widths; different cache sizes; etc. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 17

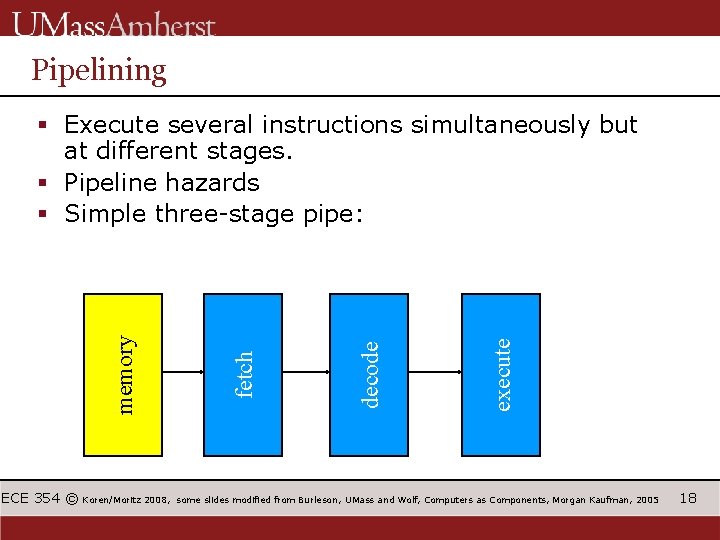

Pipelining ECE 354 © Koren/Moritz 2008, execute decode fetch memory § Execute several instructions simultaneously but at different stages. § Pipeline hazards § Simple three-stage pipe: some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 18

Soft Core Processors § Are soft, i. e. specified through field programming just like programmable logic • Shipped as hardware description files, which can be mapped onto FPGA. e. g: Nios 2. • Are bundled with software development tools (compiler, simulator, etc. ) § Offer flexibility as microprocessor parameters can be tuned to the application with tight on-chip interconnection with additional circuitry. § Designs can be marketed quickly. You can test and validate many designs quickly without making any specific board; no soldering and no wiring! ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 19

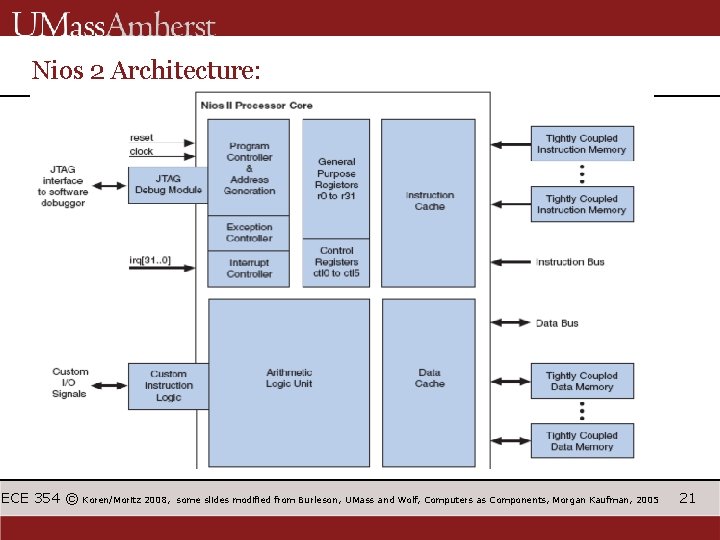

What is Nios 2? § A 32 -bit soft core processor from Altera § Comes in three flavors: Fast, Standard, Light § The three cores trade FPGA area and power consumption for speed of execution. § Is a RISC, Harvard Architecture: Simple instructions, separate data and instruction memories. § Has 32 levels of interrupts. § Uses the Avalon Bus interface § Programs compiled using GNU C/C++ toolchain. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 20

Nios 2 Architecture: ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 21

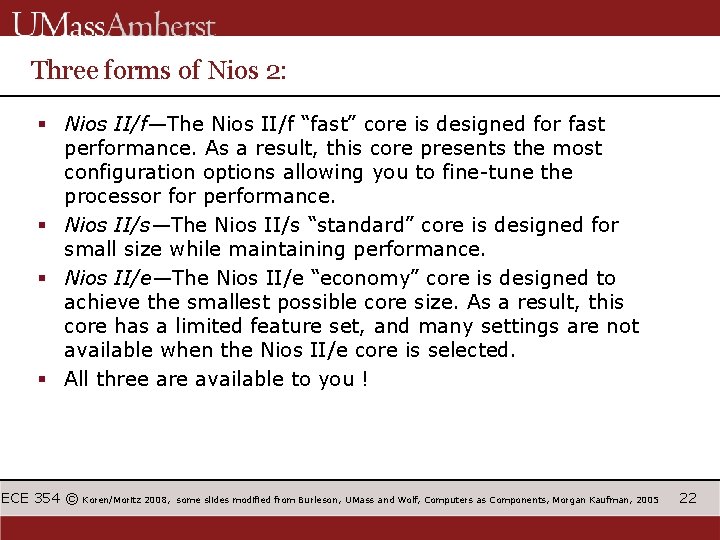

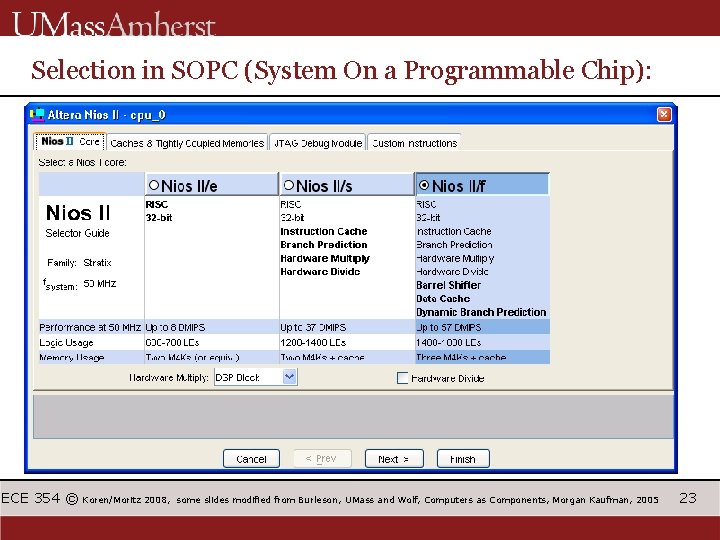

Three forms of Nios 2: § Nios II/f—The Nios II/f “fast” core is designed for fast performance. As a result, this core presents the most configuration options allowing you to fine-tune the processor for performance. § Nios II/s—The Nios II/s “standard” core is designed for small size while maintaining performance. § Nios II/e—The Nios II/e “economy” core is designed to achieve the smallest possible core size. As a result, this core has a limited feature set, and many settings are not available when the Nios II/e core is selected. § All three are available to you ! ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 22

Selection in SOPC (System On a Programmable Chip): ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 23

Why use microprocessors? § Alternatives: random logic on a fieldprogrammable gate arrays (FPGAs), custom logic, etc. § Microprocessors are often very efficient: can use same logic to perform many different functions. § Microprocessors simplify the design of families of products. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 24

The performance paradox § Microprocessors use much more logic to implement a function than does custom logic. § But microprocessors are often at least as fast: • heavily pipelined; • sophisticated design - large design teams; • aggressive VLSI technology. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 25

Power § Custom logic is a clear winner for low power devices. § Modern microprocessors offer features to help control power consumption. § Software design techniques can help reduce power consumption. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 26

Challenges in embedded system design § How much hardware do we need? • How big is the CPU? Memory? § How do we meet our deadlines? • Faster hardware or cleverer software? § How do we minimize power? • Turn off unnecessary logic? Reduce memory accesses? ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 27

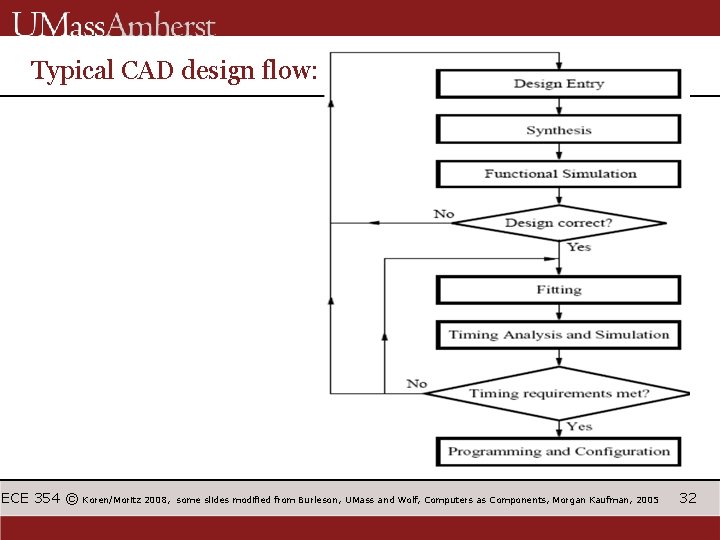

Design methodologies § A procedure for designing a system. § Understanding your methodology helps you ensure you didn’t skip anything. § Compilers, software engineering tools, computeraided design (CAD) tools, etc. , can be used to: • help automate methodology steps; • keep track of the methodology itself. § Altera CAD tools: Quartus 2 , SOPC, Nios 2 IDE (Integrated Development Environment). ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 28

Design goals § Performance. • Overall speed, deadlines. § § Functionality and user interface. Manufacturing cost. Power consumption. Other requirements (physical size, etc. ) ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 29

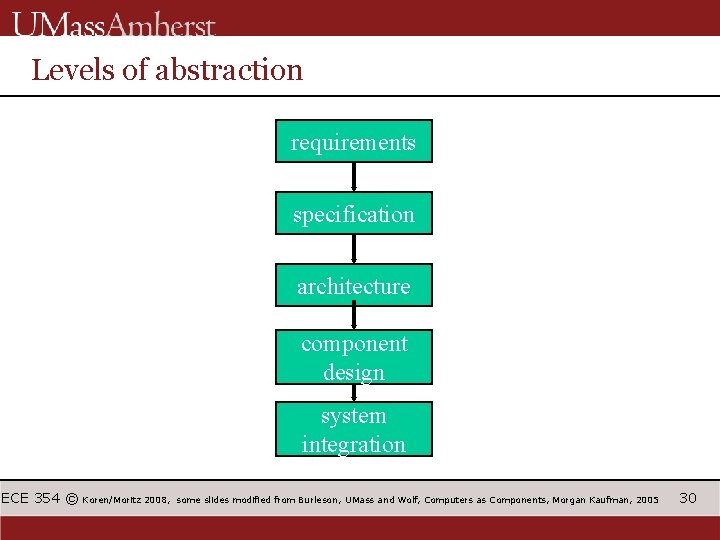

Levels of abstraction requirements specification architecture component design system integration ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 30

Top-down vs. bottom-up § Top-down design: • start from most abstract description; • work to most detailed. § Bottom-up design: • work from small components to big system. § Real design uses both techniques. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 31

Typical CAD design flow: ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 32

Designing hardware and software components § Must spend time architecting the system before you start coding. § Some components are ready-made, some can be modified from existing designs, others must be designed from scratch. § Example: SOPC for Hardware design and Nios 2 IDE for Software Design. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 33

SOPC § System On a Programmable Chip – a hardware development tool. § Used for integrating various hardware components together like: • • § Microprocessors, such as the Nios II processor Timers Serial communication interfaces: UART, SPI General purpose I/O Digital signal processing (DSP) functions Communications peripherals Interfaces to off-chip devices • Memory controllers • Buses and bridges • Application-specific standard products (ASSP) • Application-specific integrated circuits (ASIC) • Processors Generates files in Verilog or VHDL which can be added to the Quartus 2 project. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 34

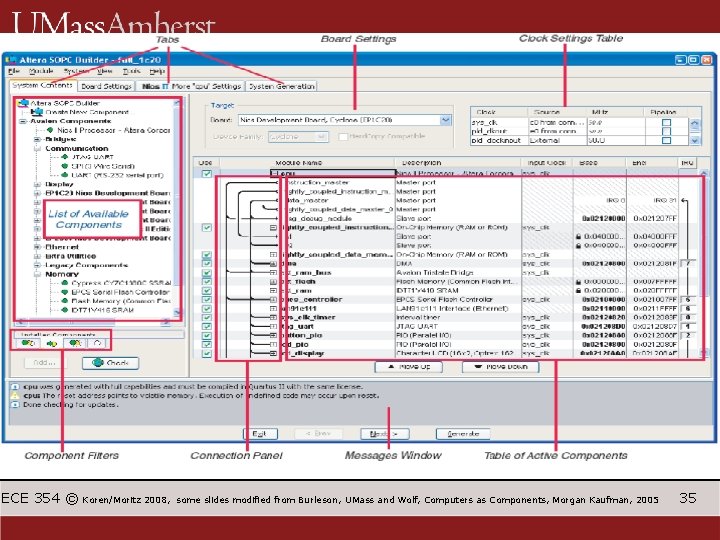

ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 35

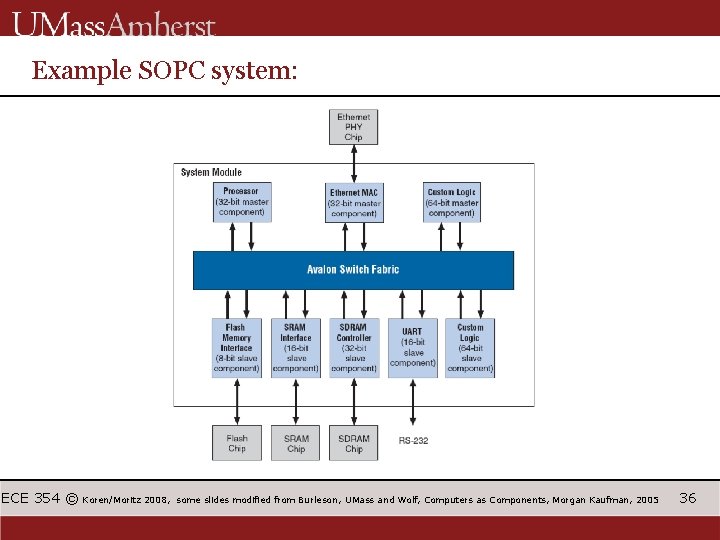

Example SOPC system: ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 36

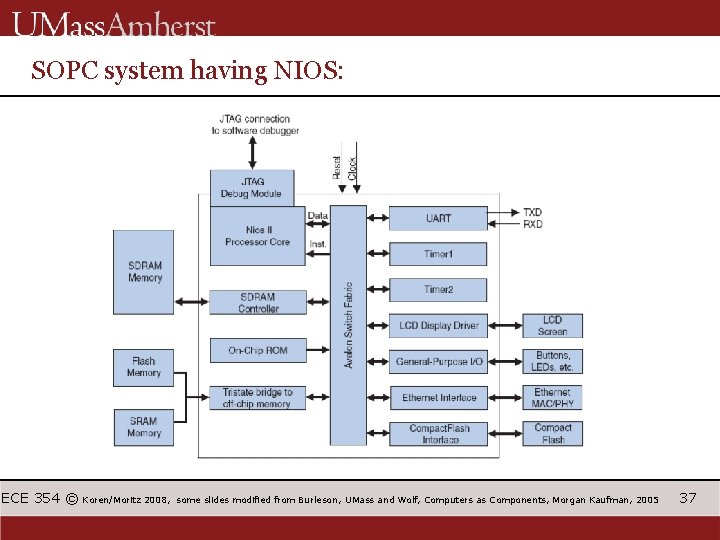

SOPC system having NIOS: ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 37

JTAG § JTAG - Joint Test Action Group: IEEE 1149. 1 standard entitled: Standard Test Access Port and Boundary-Scan Architecture for test access ports used for testing printed circuit boards (and chips) using boundary scan. § Currently used also for programming embedded devices. • Most FPGAs and PLDs are programmed via a JTAG port. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 38

Summary § Embedded computers are all around us. • Many systems have complex embedded hardware and software. § Embedded systems pose many design challenges: design time, deadlines, power, etc. § Design methodologies help us manage the design process. § CAD tools like SOPC can reduce design time. ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 39

What’s Next in Lecture 2? § We will peek inside CPU, addressing, assembly languages etc. § You will learn about I/Os and Caches. § You will learn about some cool features of SOPC and Nios 2 IDE ! ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 40

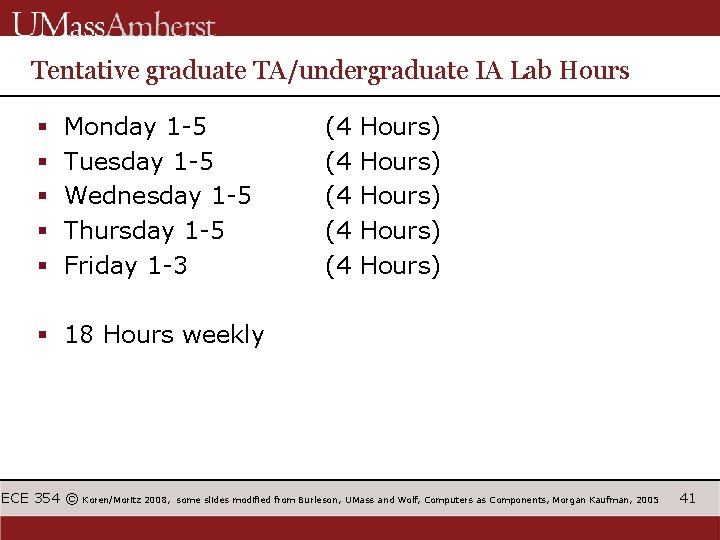

Tentative graduate TA/undergraduate IA Lab Hours § § § Monday 1 -5 Tuesday 1 -5 Wednesday 1 -5 Thursday 1 -5 Friday 1 -3 (4 (4 (4 Hours) Hours) § 18 Hours weekly ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 41

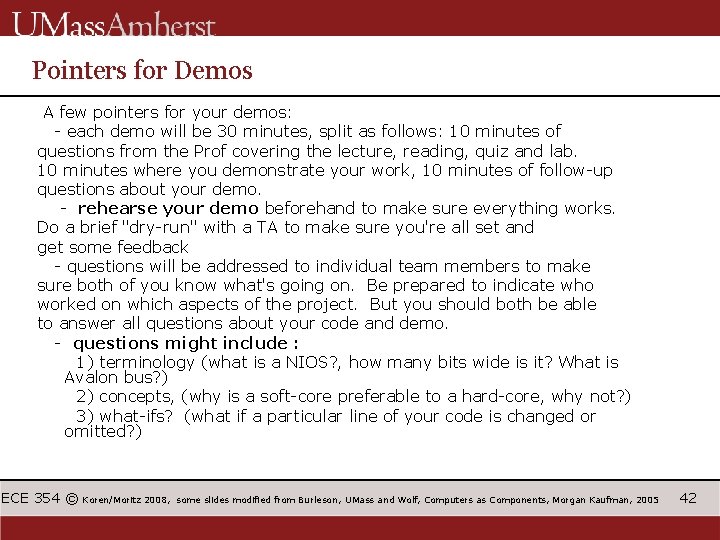

Pointers for Demos A few pointers for your demos: - each demo will be 30 minutes, split as follows: 10 minutes of questions from the Prof covering the lecture, reading, quiz and lab. 10 minutes where you demonstrate your work, 10 minutes of follow-up questions about your demo. - rehearse your demo beforehand to make sure everything works. Do a brief "dry-run" with a TA to make sure you're all set and get some feedback - questions will be addressed to individual team members to make sure both of you know what's going on. Be prepared to indicate who worked on which aspects of the project. But you should both be able to answer all questions about your code and demo. - questions might include : 1) terminology (what is a NIOS? , how many bits wide is it? What is Avalon bus? ) 2) concepts, (why is a soft-core preferable to a hard-core, why not? ) 3) what-ifs? (what if a particular line of your code is changed or omitted? ) ECE 354 © Koren/Moritz 2008, some slides modified from Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 42

- Slides: 42