ECE 353 Introduction to Microprocessor Systems Week 3

- Slides: 38

ECE 353 Introduction to Microprocessor Systems Week 3 Michael J. Schulte

Topics 80 C 188 EB Organization (continued) n n n Segmentation Reset Processing Programmer’s Model 80 C 188 EB Machine Language 80 C 188 EB Assembly Language and Assemblers 80 C 188 EB Debuggers

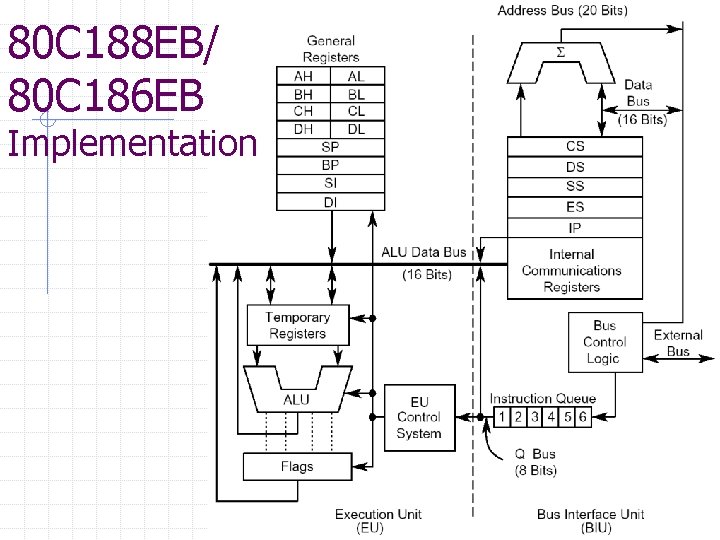

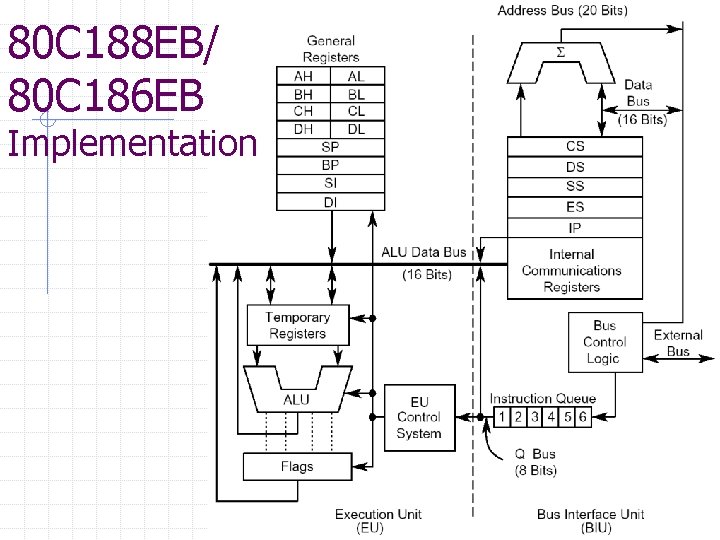

80 C 188 EB/ 80 C 186 EB Implementation

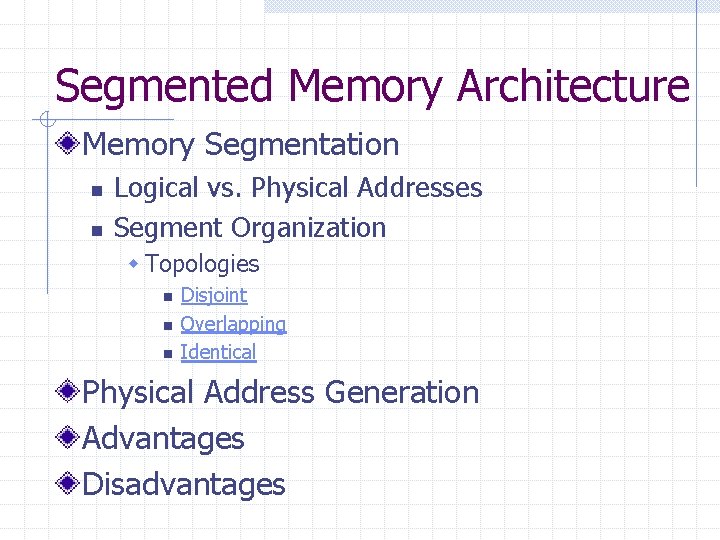

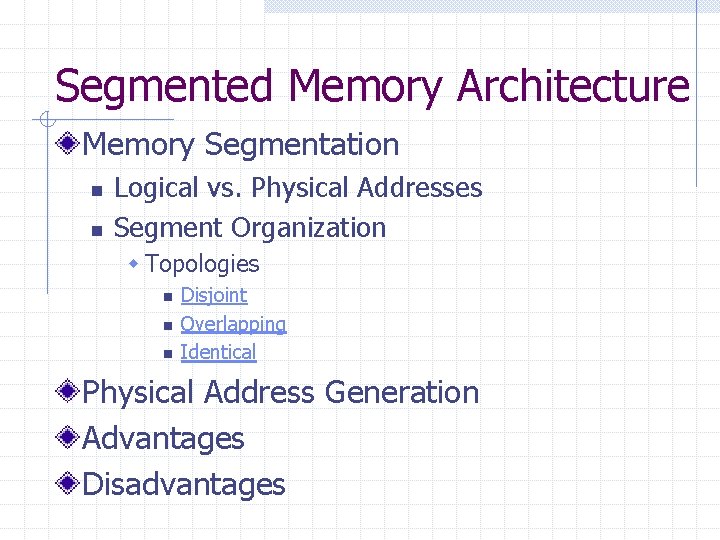

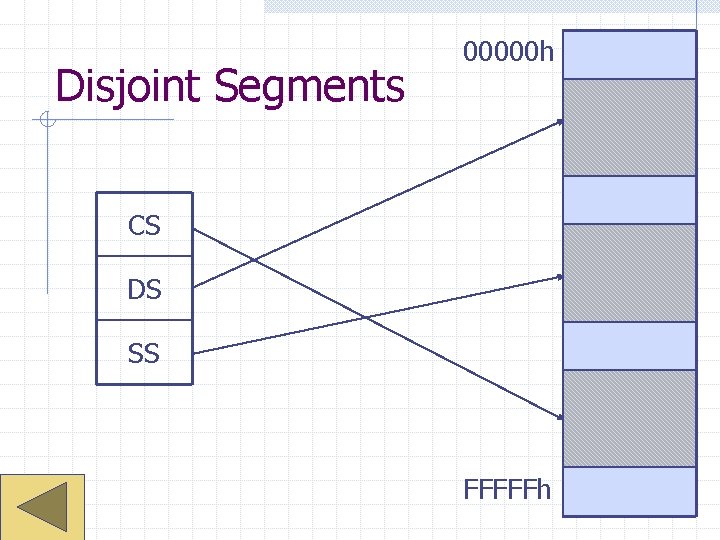

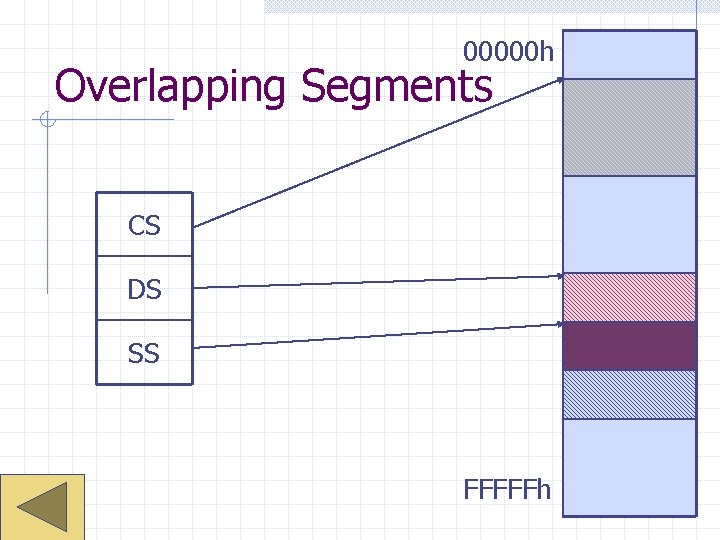

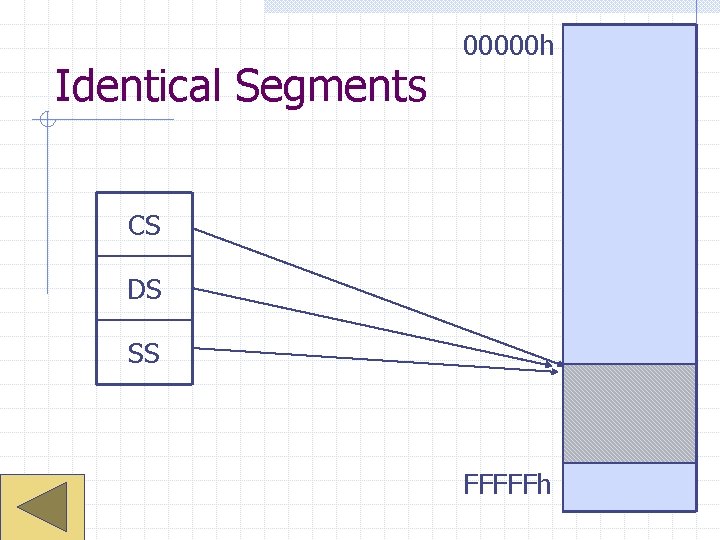

Segmented Memory Architecture Memory Segmentation n n Logical vs. Physical Addresses Segment Organization w Topologies n n n Disjoint Overlapping Identical Physical Address Generation Advantages Disadvantages

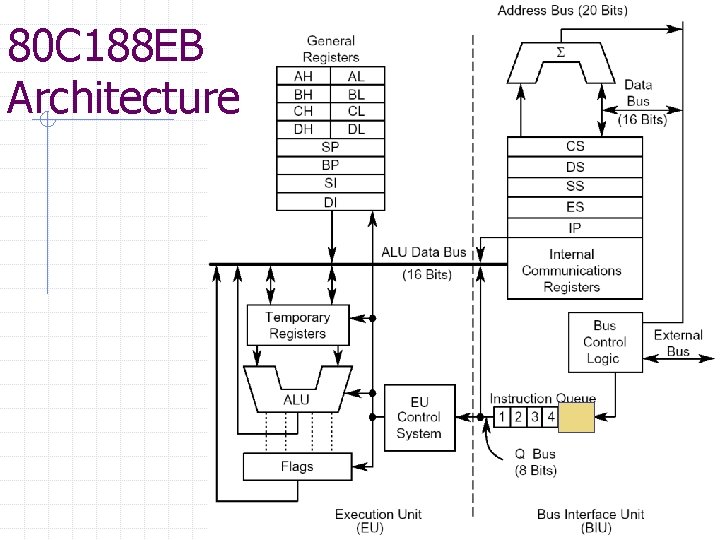

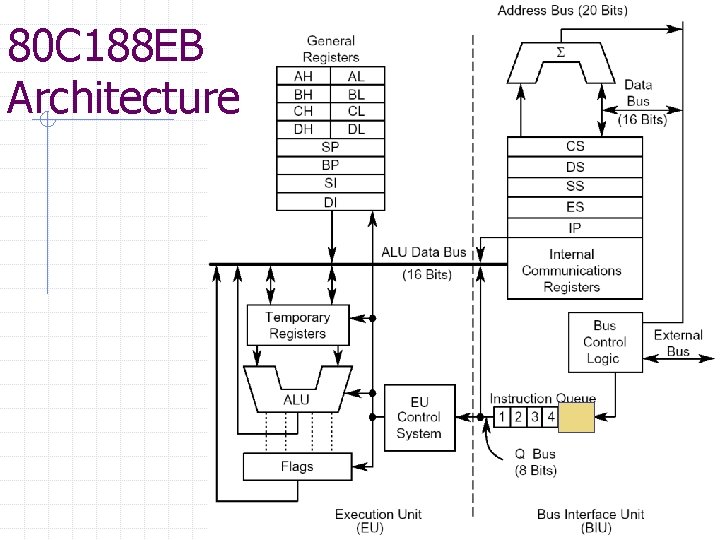

80 C 188 EB Architecture

80 C 188 EB Programmer’s Model

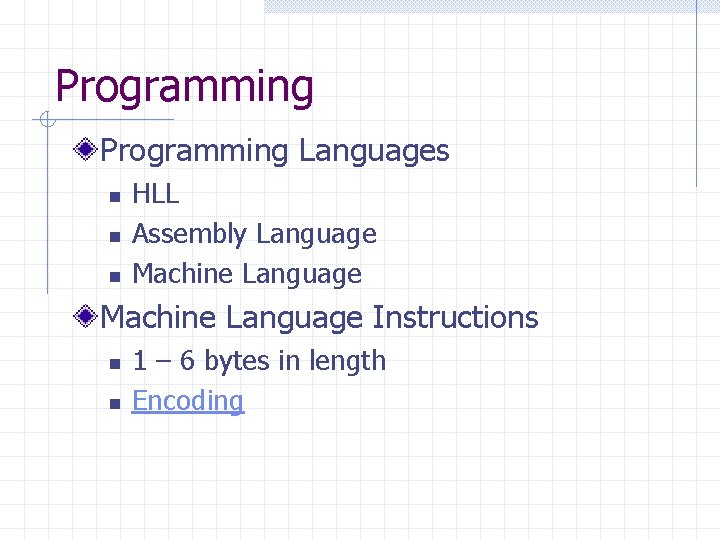

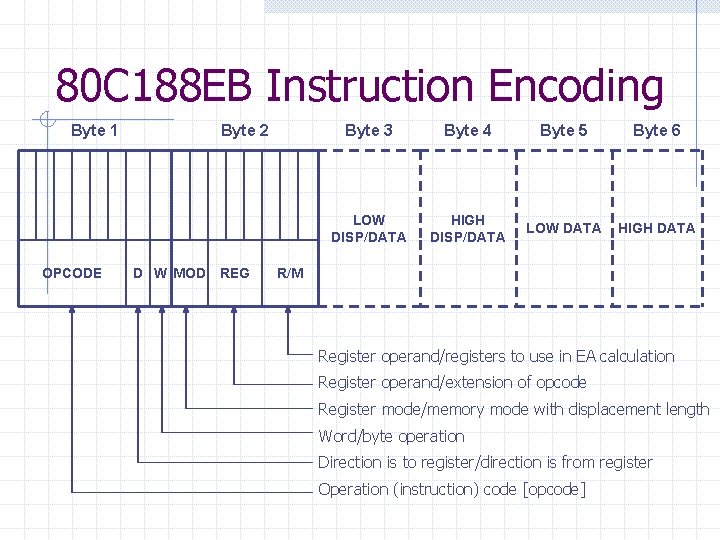

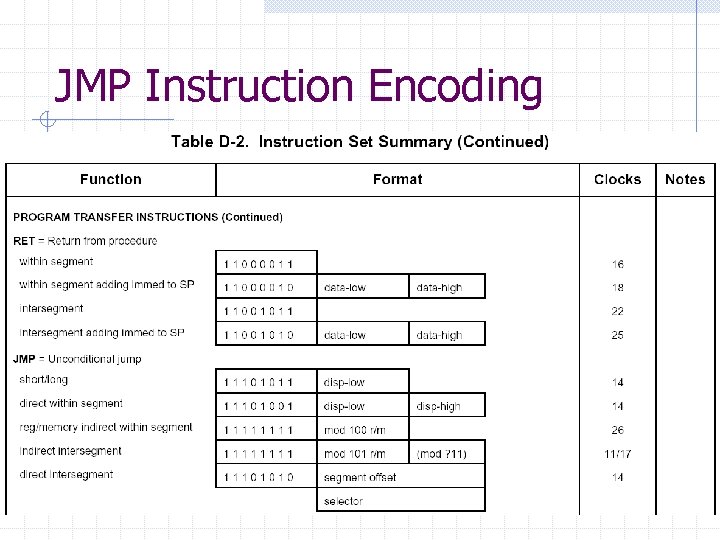

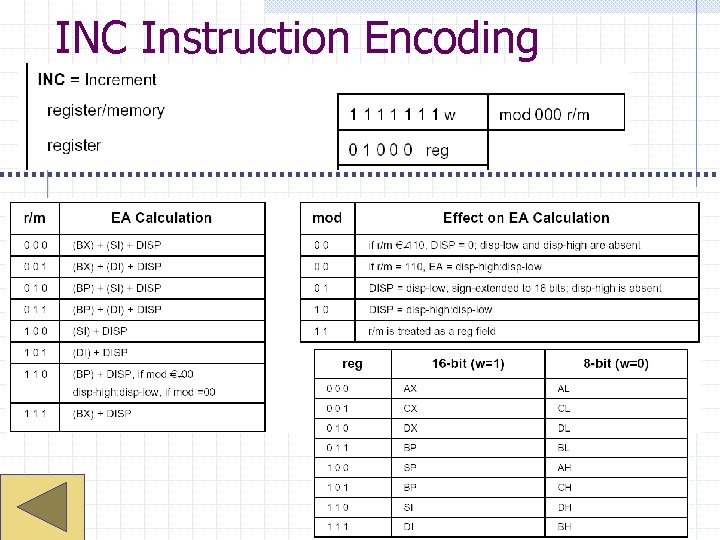

Programming Languages n n n HLL Assembly Language Machine Language Instructions n n 1 – 6 bytes in length Encoding

Assembler Primer Assembler Types n n Native Assembler Cross Assembler General Instruction Syntax Assembler Functions n n What does an assembler do? Syntax checking Offset calculation Encoding to machine code

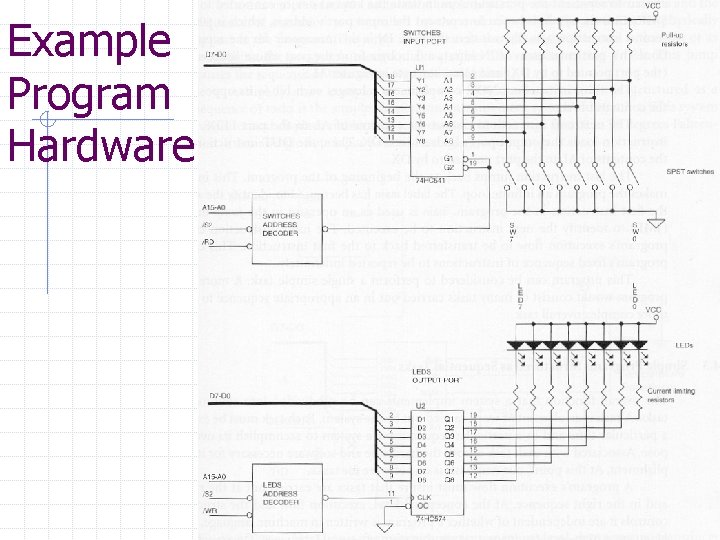

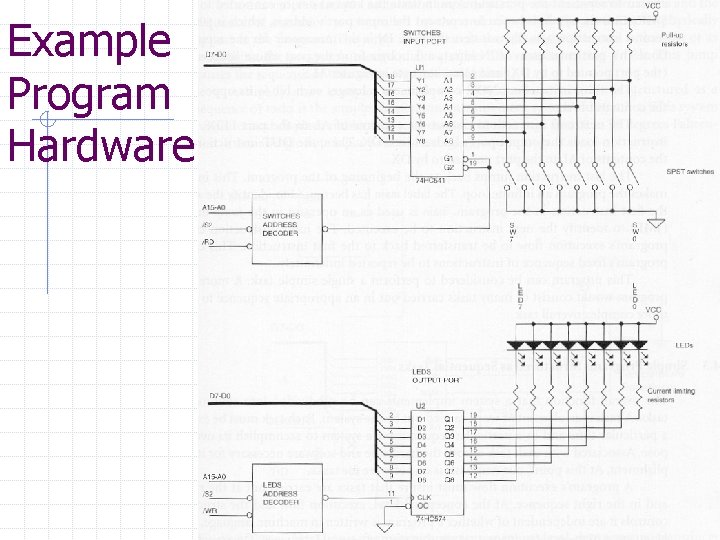

Example Program Hardware

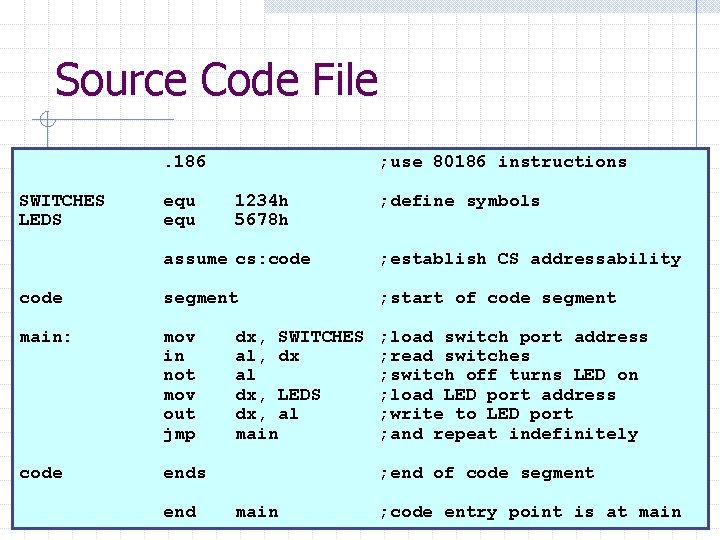

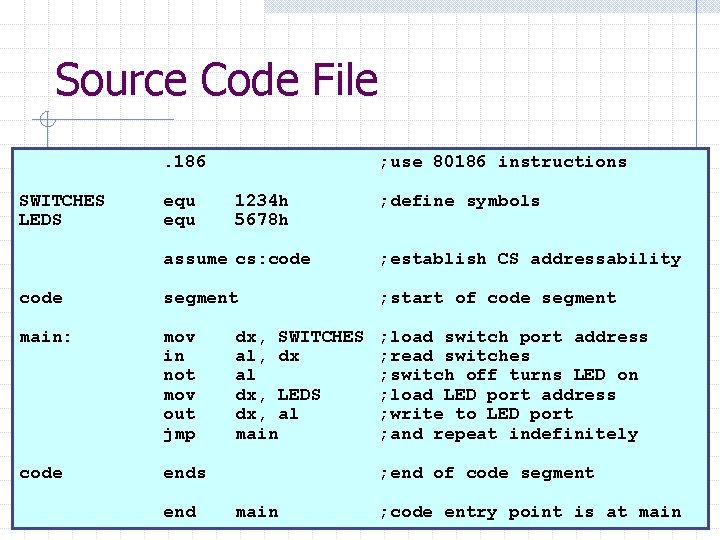

Source Code File. 186 SWITCHES LEDS equ ; use 80186 instructions 1234 h 5678 h ; define symbols assume cs: code ; establish CS addressability code segment ; start of code segment main: mov in not mov out jmp ; load switch port address ; read switches ; switch off turns LED on ; load LED port address ; write to LED port ; and repeat indefinitely code ends end dx, SWITCHES al, dx al dx, LEDS dx, al main ; end of code segment main ; code entry point is at main

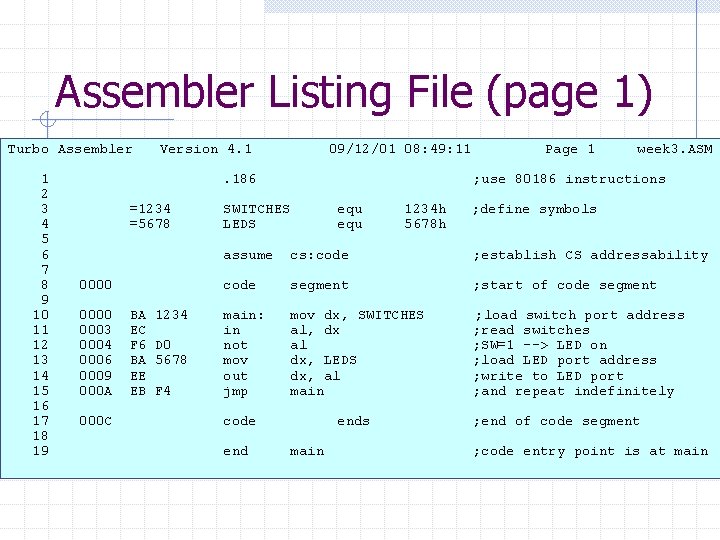

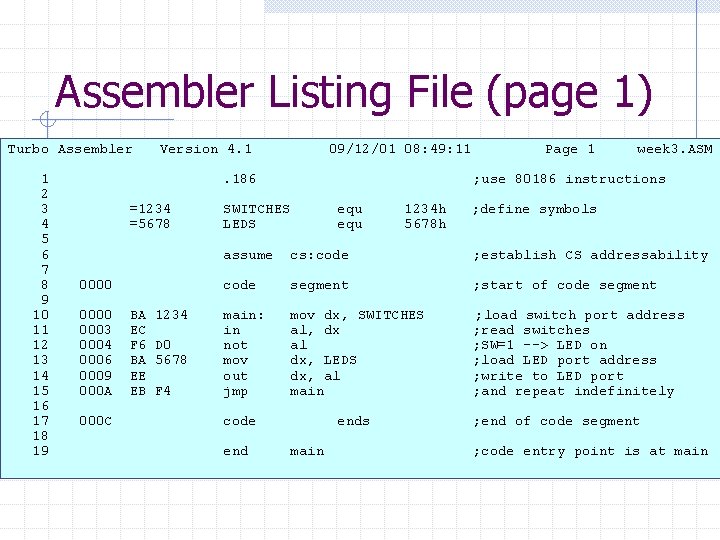

Assembler Listing File (page 1) Turbo Assembler 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 Version 4. 1 09/12/01 08: 49: 11 . 186 =1234 =5678 0000 0003 0004 0006 0009 000 A 000 C BA EC F 6 BA EE EB 1234 D 0 5678 F 4 Page 1 week 3. ASM ; use 80186 instructions SWITCHES LEDS equ 1234 h 5678 h ; define symbols assume cs: code ; establish CS addressability code segment ; start of code segment main: in not mov out jmp mov dx, SWITCHES al, dx al dx, LEDS dx, al main ; load switch port address ; read switches ; SW=1 --> LED on ; load LED port address ; write to LED port ; and repeat indefinitely code ends end main ; end of code segment ; code entry point is at main

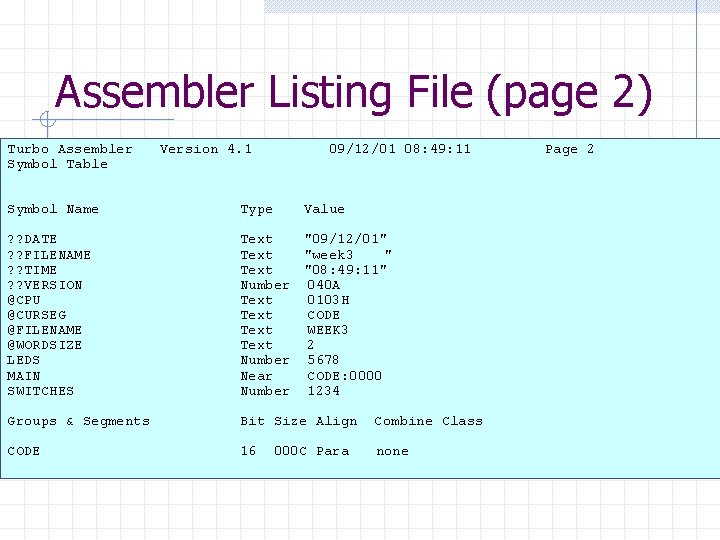

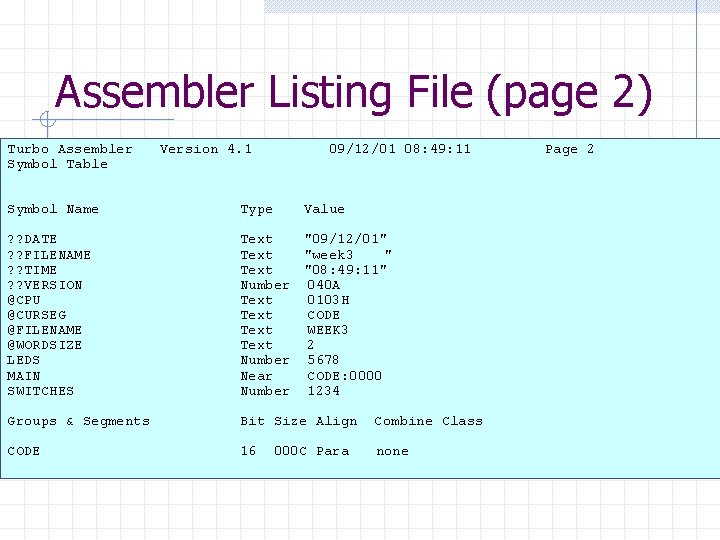

Assembler Listing File (page 2) Turbo Assembler Symbol Table Version 4. 1 09/12/01 08: 49: 11 Symbol Name Type Value ? ? DATE ? ? FILENAME ? ? TIME ? ? VERSION @CPU @CURSEG @FILENAME @WORDSIZE LEDS MAIN SWITCHES Text "09/12/01" Text "week 3 " Text "08: 49: 11" Number 040 A Text 0103 H Text CODE Text WEEK 3 Text 2 Number 5678 Near CODE: 0000 Number 1234 Groups & Segments Bit Size Align Combine Class CODE 16 none 000 C Para Page 2

Code Generation Process

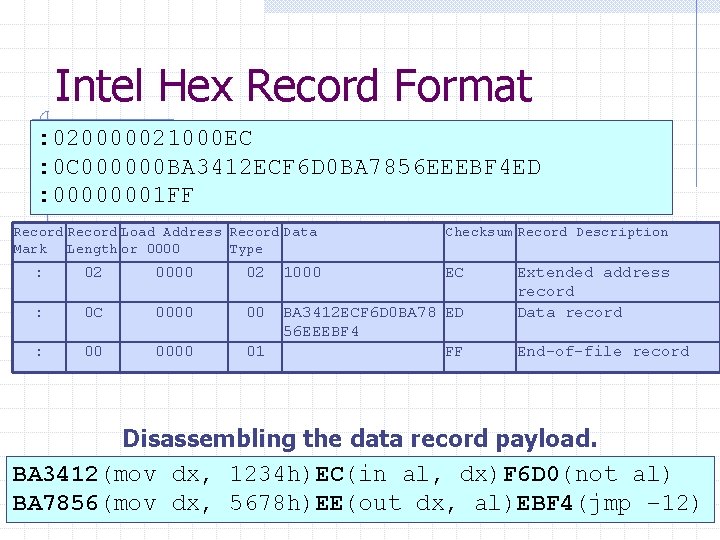

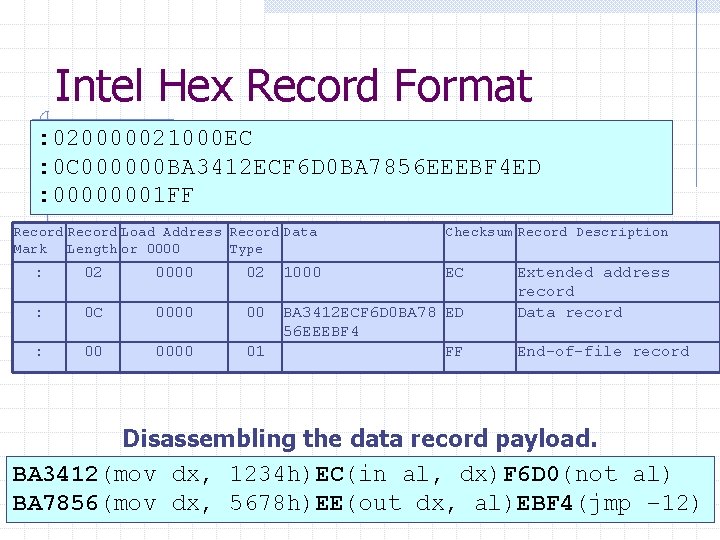

Intel Hex Record Format : 020000021000 EC : 0 C 000000 BA 3412 ECF 6 D 0 BA 7856 EEEBF 4 ED : 00000001 FF Record Load Address Record Data Mark Length or 0000 Type Checksum Record Description : 02 0000 02 1000 EC : 0 C 0000 00 : 00 0000 01 BA 3412 ECF 6 D 0 BA 78 ED 56 EEEBF 4 FF Extended address record Data record End-of-file record Disassembling the data record payload. BA 3412(mov dx, 1234 h)EC(in al, dx)F 6 D 0(not al) BA 7856(mov dx, 5678 h)EE(out dx, al)EBF 4(jmp – 12)

Borland Development Tools

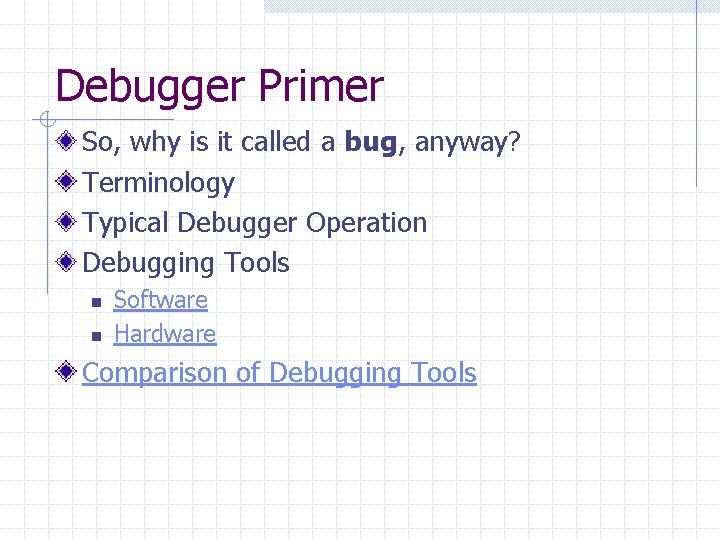

Debugger Primer So, why is it called a bug, anyway? Terminology Typical Debugger Operation Debugging Tools n n Software Hardware Comparison of Debugging Tools

Code Development Tips Use structured programming methods - no spaghetti code. Use descriptive symbols and names. Write comments as you go (or before!). When fixing assembler errors, fix only the top one or two and re-assemble – a lot of the later errors may be due to the first few. When debugging, verify what the registers are loaded with as compared to what you think they should be loaded with.

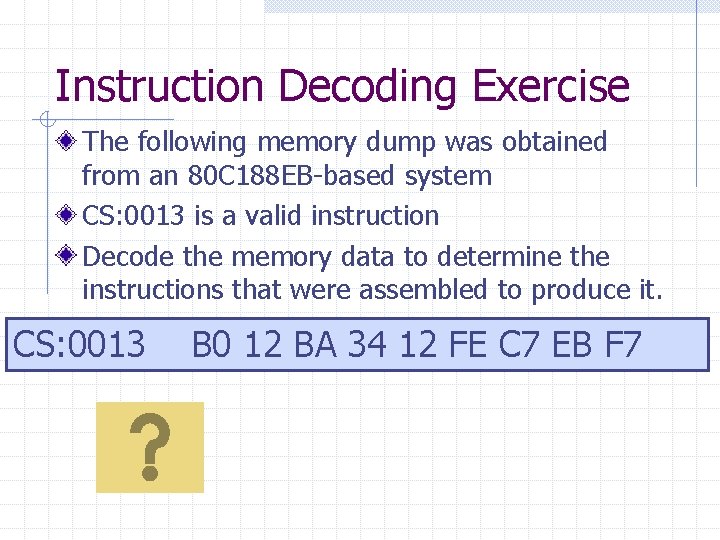

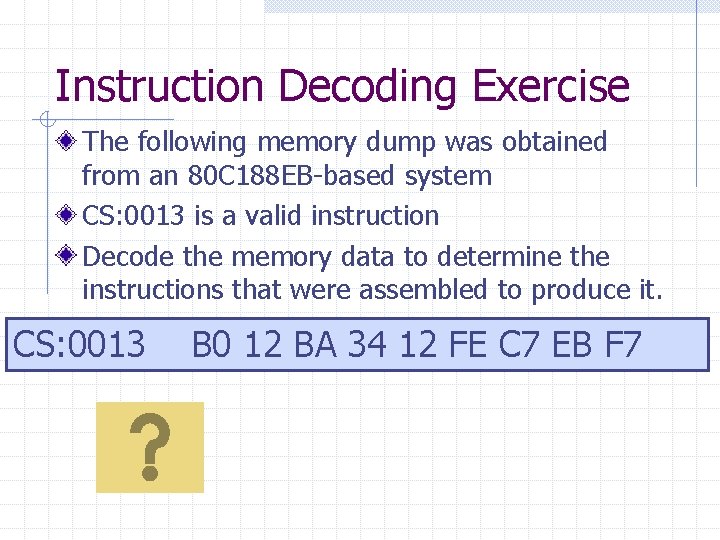

Instruction Decoding Exercise The following memory dump was obtained from an 80 C 188 EB-based system CS: 0013 is a valid instruction Decode the memory data to determine the instructions that were assembled to produce it. CS: 0013 B 0 12 BA 34 12 FE C 7 EB F 7

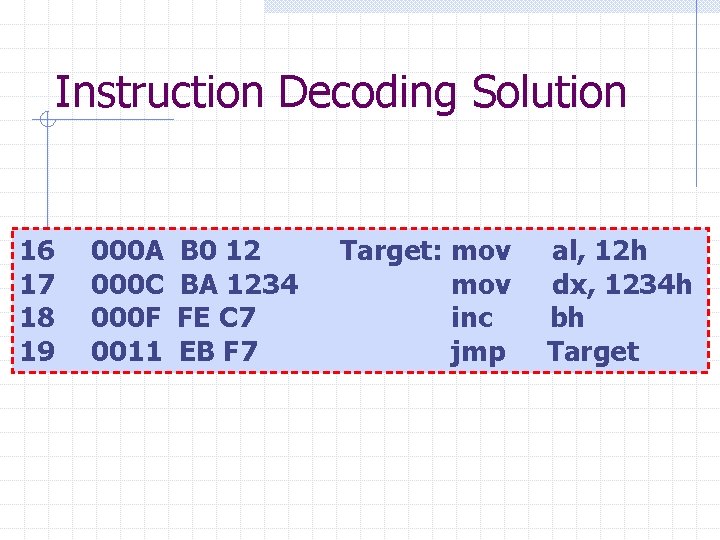

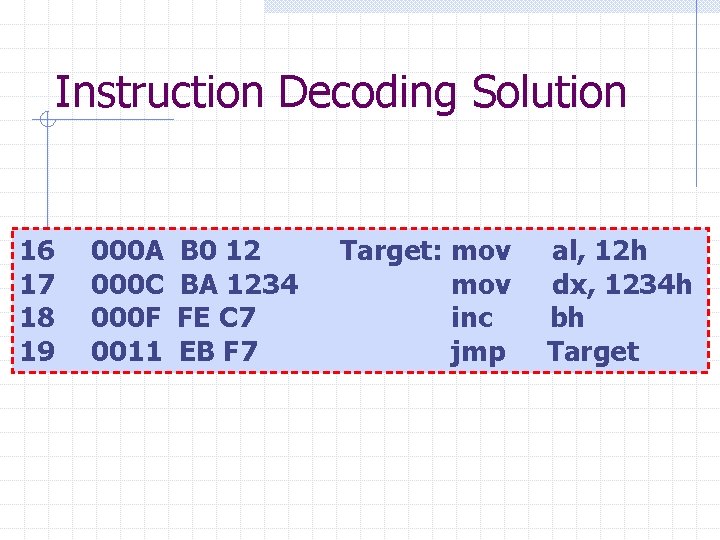

Instruction Decoding Solution 16 17 18 19 000 A 000 C 000 F 0011 B 0 12 BA 1234 FE C 7 EB F 7 Target: mov inc jmp al, 12 h dx, 1234 h bh Target

Wrapping Up Homework #2 due Friday 2/18 Reading for next week n Chapter 6

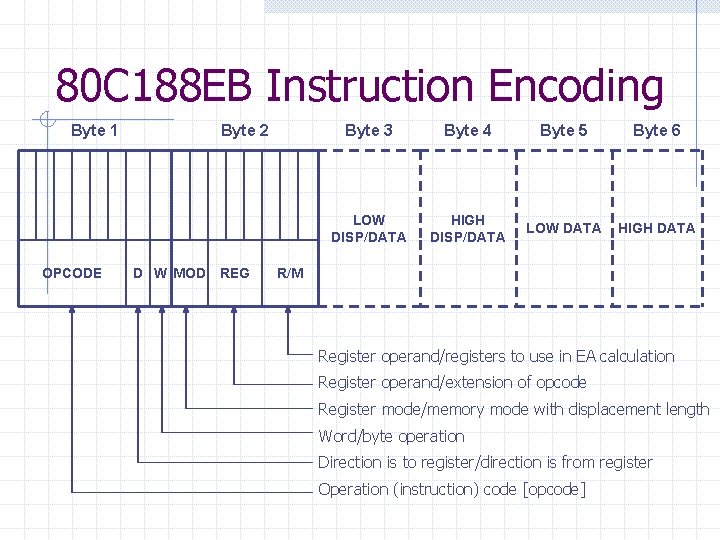

80 C 188 EB Instruction Encoding Byte 1 OPCODE Byte 2 D W MOD REG Byte 3 Byte 4 Byte 5 Byte 6 LOW DISP/DATA HIGH DISP/DATA LOW DATA HIGH DATA R/M Register operand/registers to use in EA calculation Register operand/extension of opcode Register mode/memory mode with displacement length Word/byte operation Direction is to register/direction is from register Operation (instruction) code [opcode]

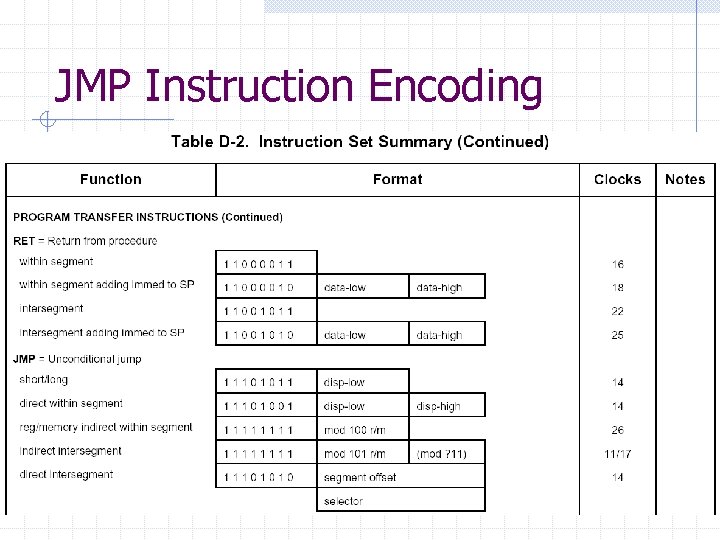

JMP Instruction Encoding

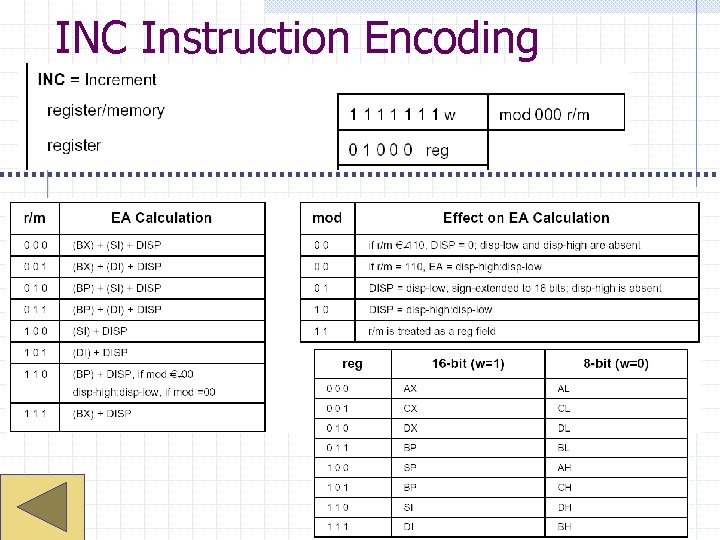

INC Instruction Encoding

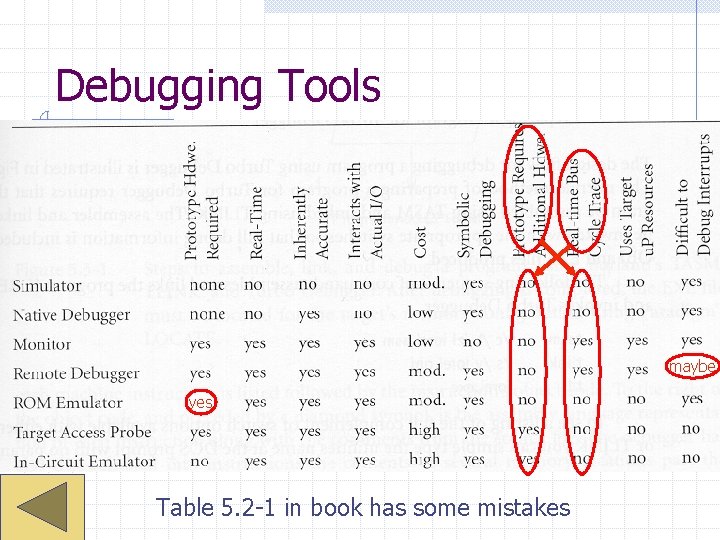

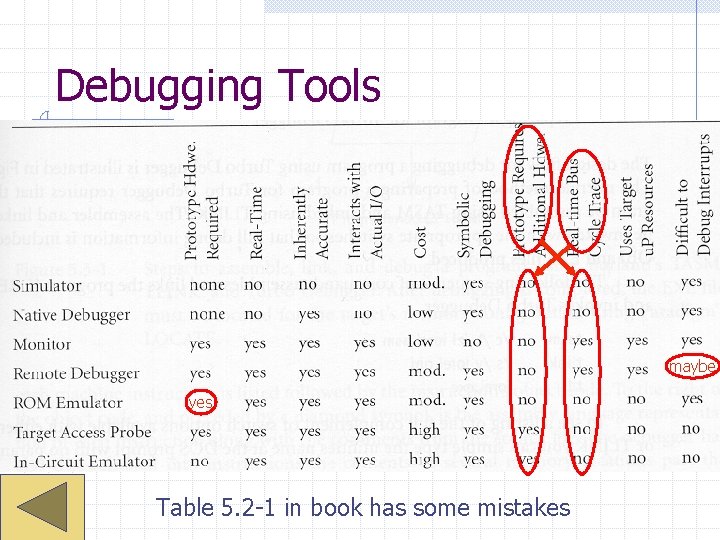

Debugging Tools maybe yes Table 5. 2 -1 in book has some mistakes

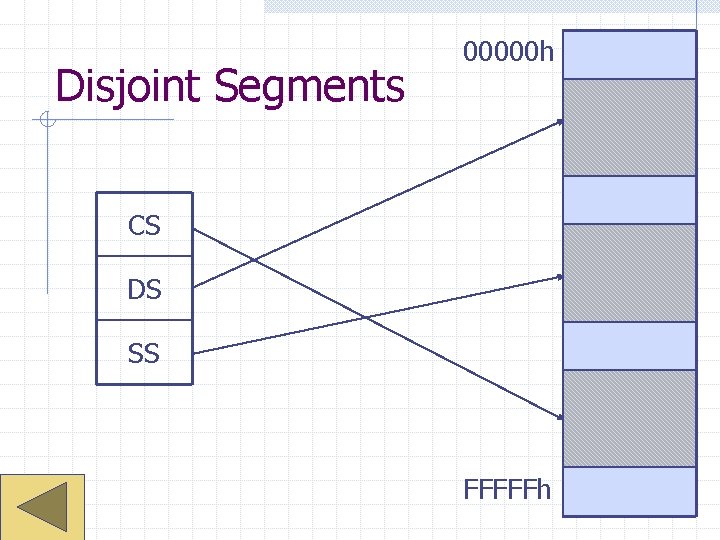

Disjoint Segments 00000 h CS DS SS FFFFFh

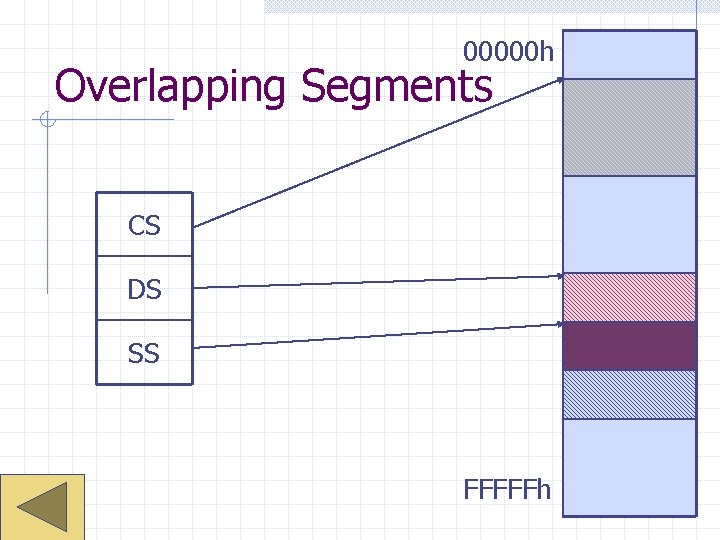

00000 h Overlapping Segments CS DS SS FFFFFh

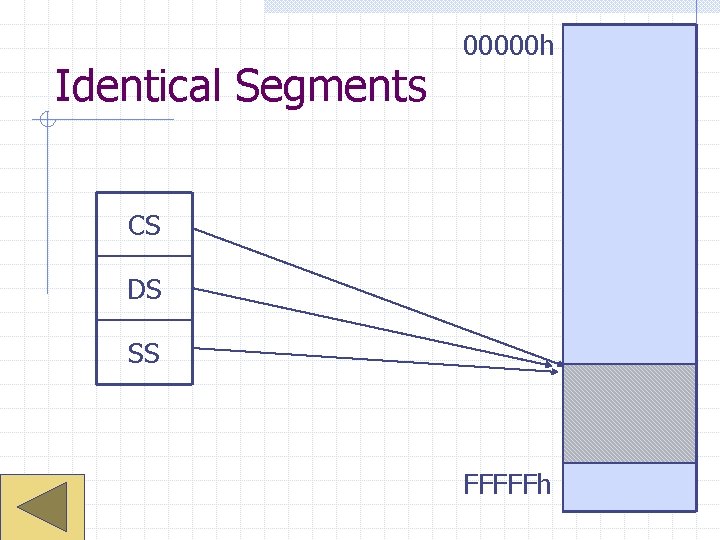

Identical Segments 00000 h CS DS SS FFFFFh

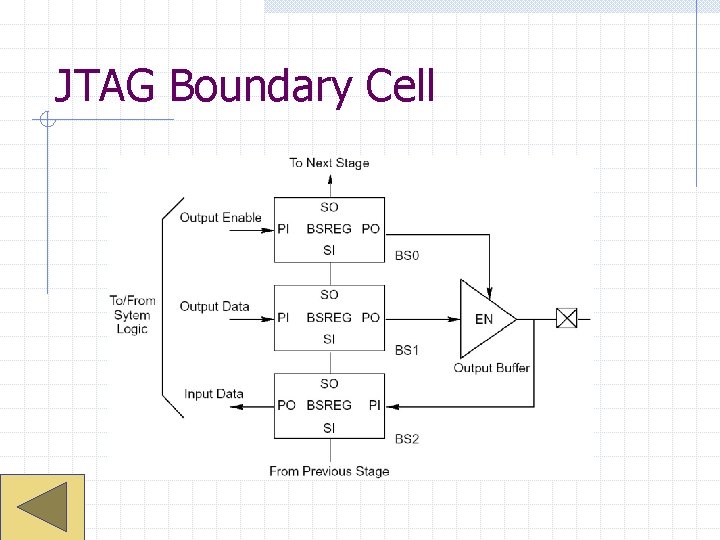

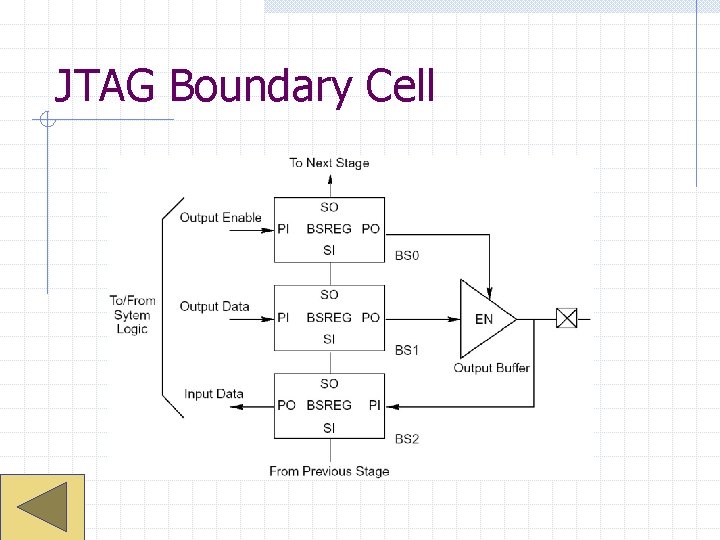

JTAG Boundary Cell

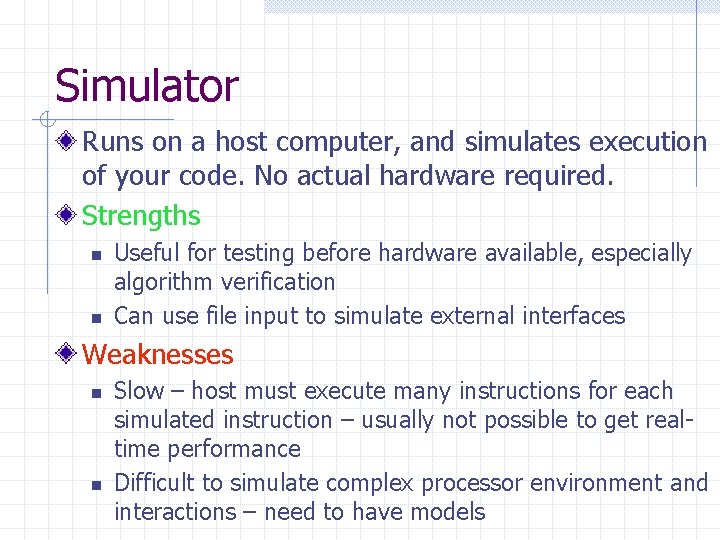

Simulator Runs on a host computer, and simulates execution of your code. No actual hardware required. Strengths n n Useful for testing before hardware available, especially algorithm verification Can use file input to simulate external interfaces Weaknesses n n Slow – host must execute many instructions for each simulated instruction – usually not possible to get realtime performance Difficult to simulate complex processor environment and interactions – need to have models

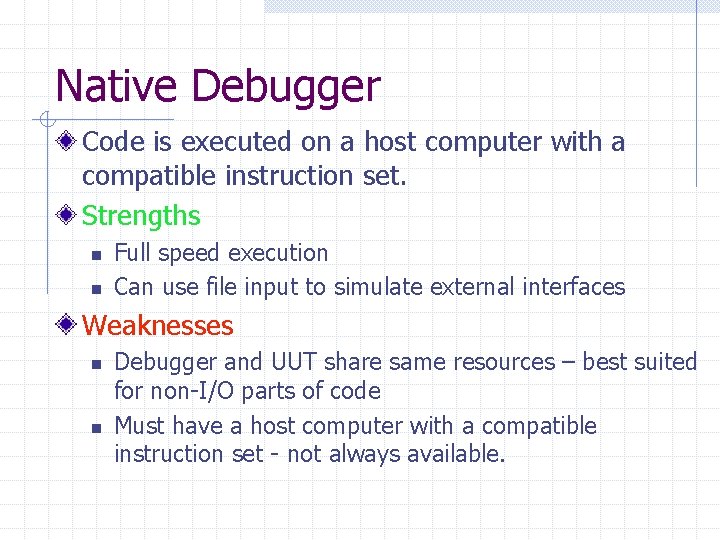

Native Debugger Code is executed on a host computer with a compatible instruction set. Strengths n n Full speed execution Can use file input to simulate external interfaces Weaknesses n n Debugger and UUT share same resources – best suited for non-I/O parts of code Must have a host computer with a compatible instruction set - not always available.

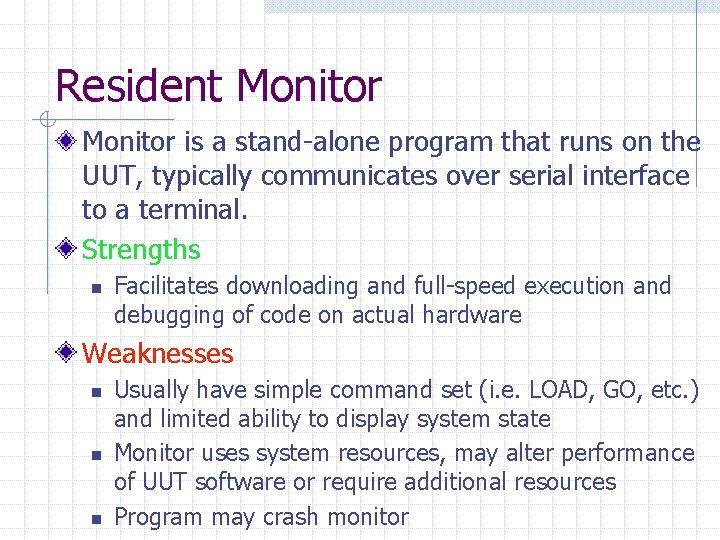

Resident Monitor is a stand-alone program that runs on the UUT, typically communicates over serial interface to a terminal. Strengths n Facilitates downloading and full-speed execution and debugging of code on actual hardware Weaknesses n n n Usually have simple command set (i. e. LOAD, GO, etc. ) and limited ability to display system state Monitor uses system resources, may alter performance of UUT software or require additional resources Program may crash monitor

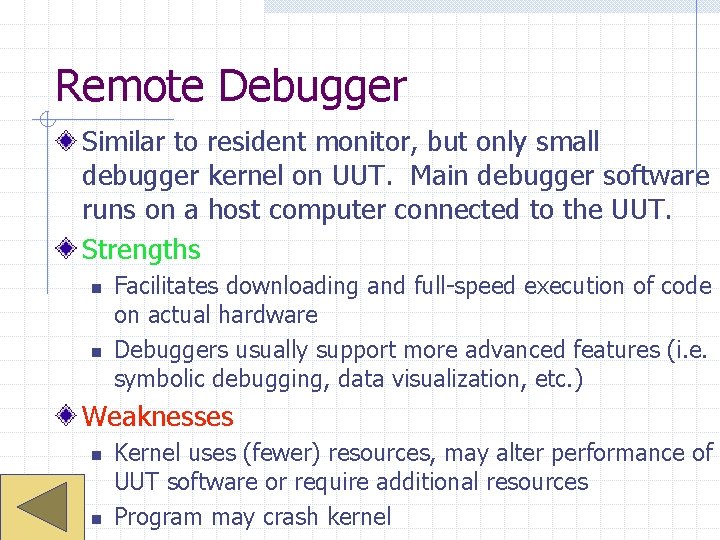

Remote Debugger Similar to resident monitor, but only small debugger kernel on UUT. Main debugger software runs on a host computer connected to the UUT. Strengths n n Facilitates downloading and full-speed execution of code on actual hardware Debuggers usually support more advanced features (i. e. symbolic debugging, data visualization, etc. ) Weaknesses n n Kernel uses (fewer) resources, may alter performance of UUT software or require additional resources Program may crash kernel

ROM Emulator Hardware plugs into ROM socket on UUT. Usually has serial connection to host computer. Strengths n n No disruption of system operation Quick and easy to load new code to UUT Weaknesses n Really just a quicker way to reprogram ROMs in place

Target Access Probe Replaces the CPU on UUT. Connected to host computer for control. Strengths n n Full visibility of processor bus activity Usually can record and playback execution traces Weaknesses n n Doesn’t give arbitrary control of bus activity Expensive

In-Circuit Emulator Replaces UUT CPU with hardware that gives full control of CPU pins (i. e. can run arbitrary bus cycles). Often contain overlay memory to allow testing of software before system hardware is available. May clamp over existing CPU that is soldered in place. Strengths n n n Complete visibility and control of CPU activity Hardware assisted debugging – can set breakpoints on specific bus operations (i. e. read X from Y) Record and playback execution traces Weaknesses n Even more expensive

JTAG Emulators Special serial interface to a device originally created just for testing (IEEE Std 1149. 1) n n Boundary Scan Emulation Scan Strengths n n n No extra hardware except for small connector, usually left on production boards Complete control over CPU state and operation Can use for production and field testing/debugging Weaknesses n n Relatively slow – must load/retrieve CPU serially Actually stops CPU when loading/retrieving