ECE 353 Introduction to Microprocessor Systems Week 2

- Slides: 25

ECE 353 Introduction to Microprocessor Systems Week 2 Michael J. Schulte

Topics Simple P Organization Simple P Architecture n n Fetch-Decode-Execute model Instruction encoding Notation – bit and byte numbering 80 C 188 EB Organization 80 C 188 EB Subsystems

Simple P Organization A less simple architecture

A Simple P Architecture Register Transfer Expressions Simple P Operation n Fetch-Decode-Execute Instruction Set n n Typical Operations Operand Ordering Instruction Encoding and Decoding Example Register View (or programmers’ model) of a simple P

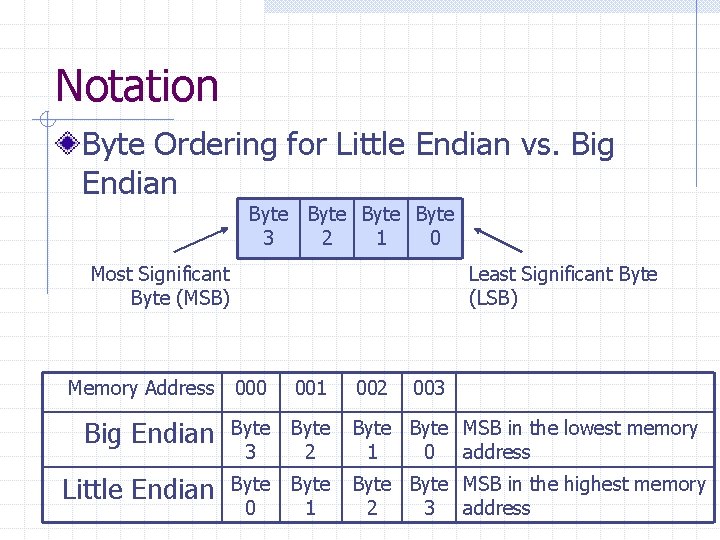

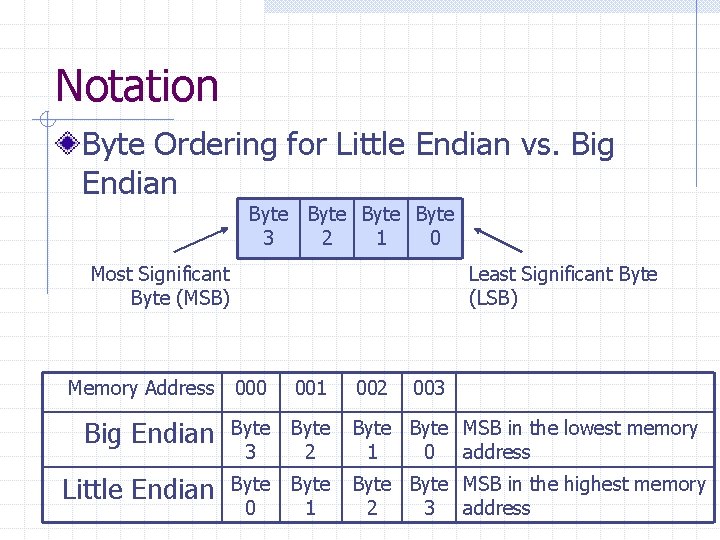

Notation Byte Ordering for Little Endian vs. Big Endian Byte 3 2 1 0 Most Significant Byte (MSB) Least Significant Byte (LSB) Memory Address 000 001 002 003 Big Endian Byte 3 Byte 2 Byte MSB in the lowest memory 1 0 address Little Endian Byte 0 Byte 1 Byte MSB in the highest memory 2 3 address

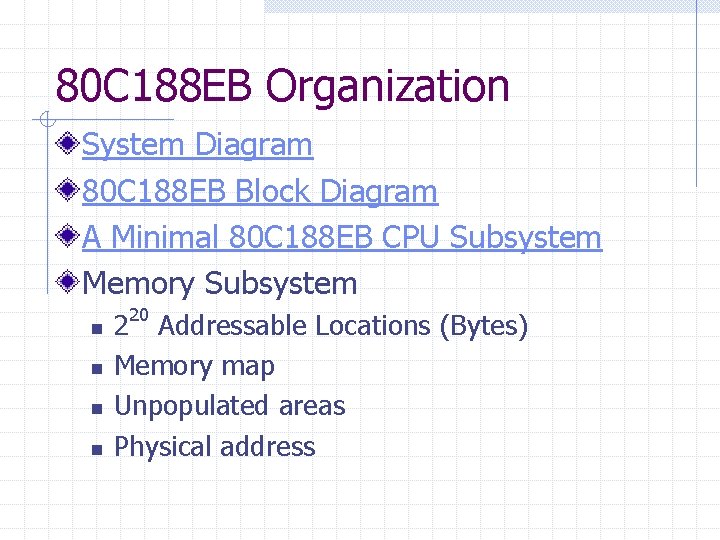

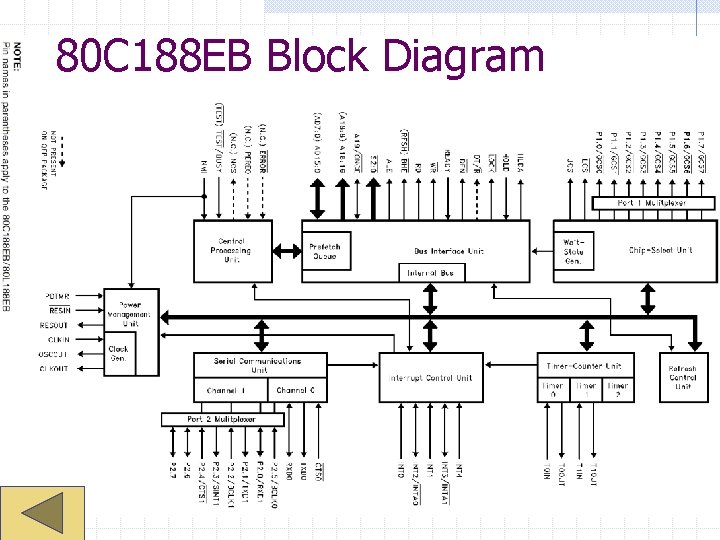

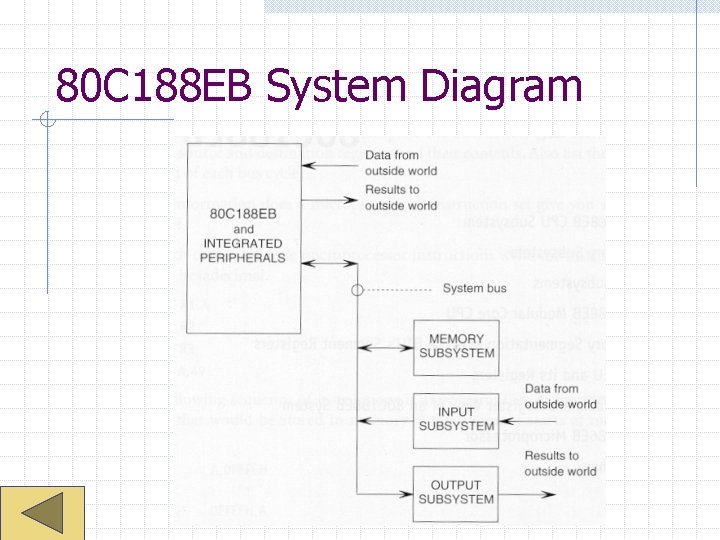

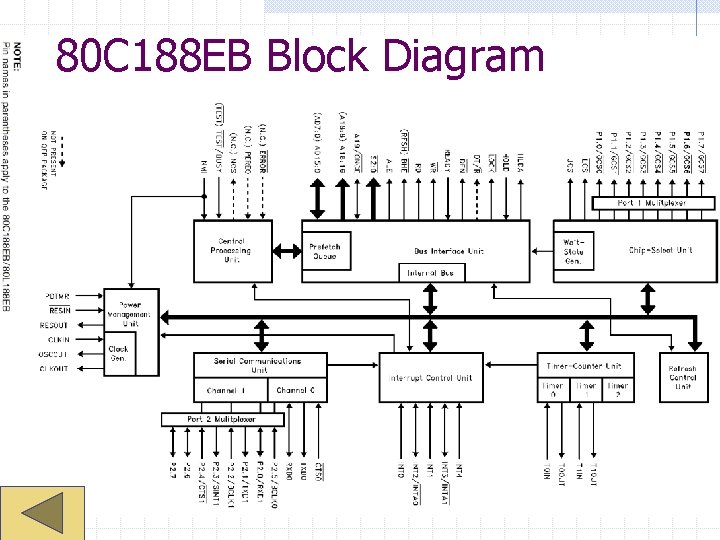

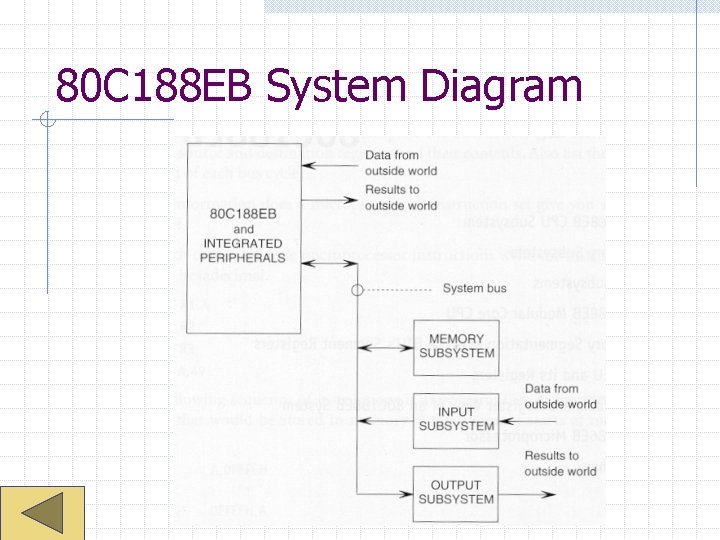

80 C 188 EB Organization System Diagram 80 C 188 EB Block Diagram A Minimal 80 C 188 EB CPU Subsystem Memory Subsystem n n 220 Addressable Locations (Bytes) Memory map Unpopulated areas Physical address

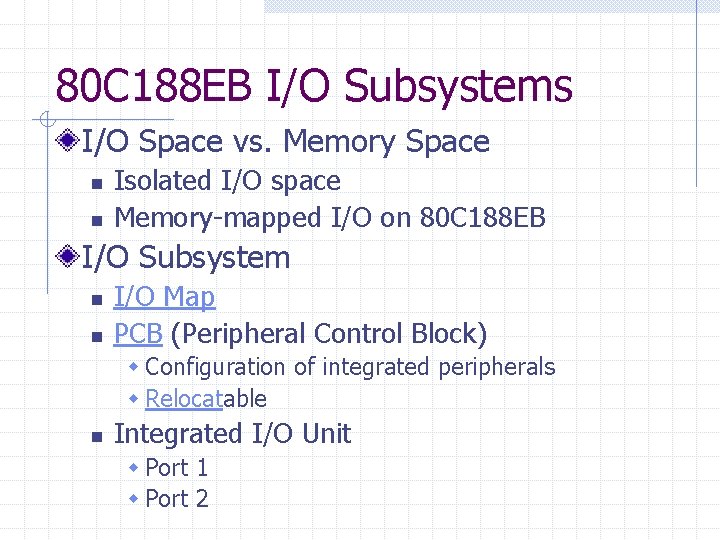

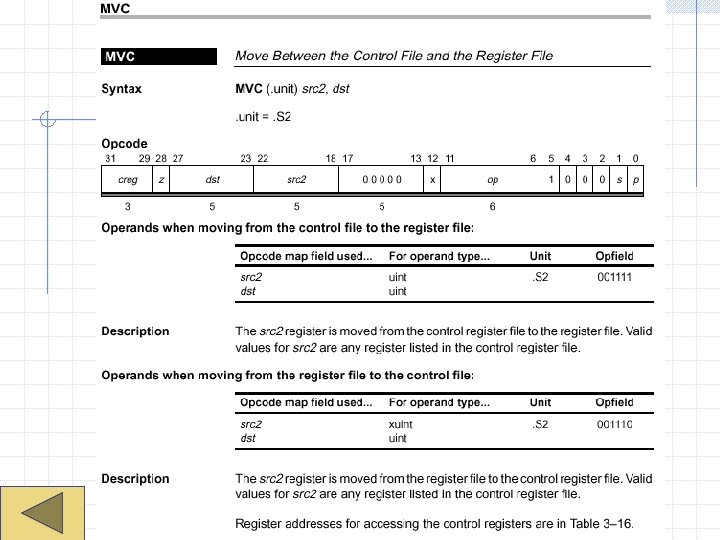

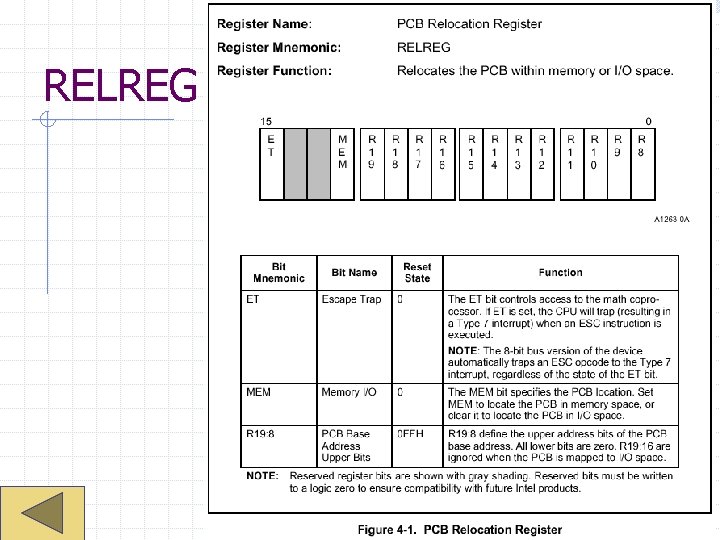

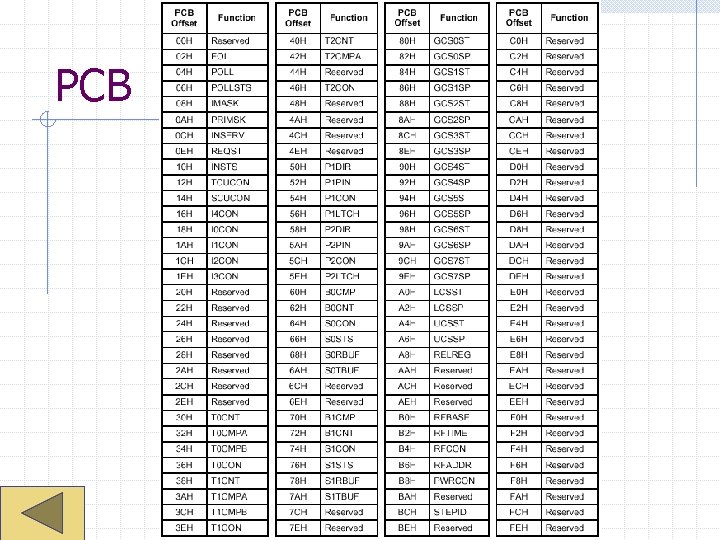

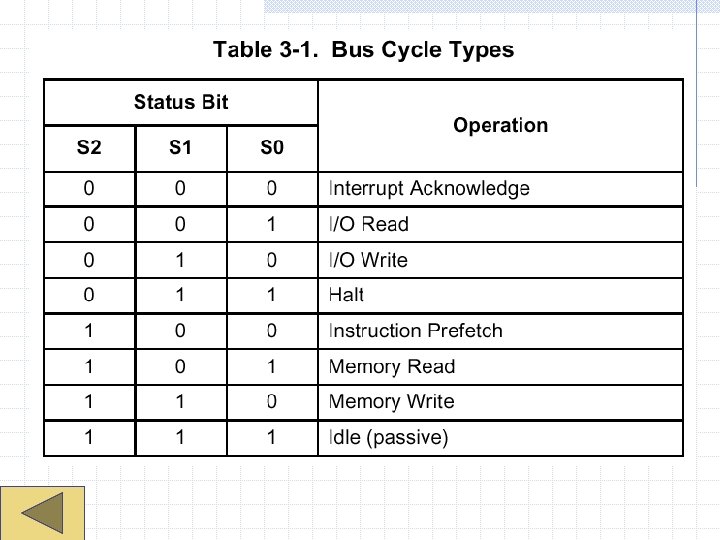

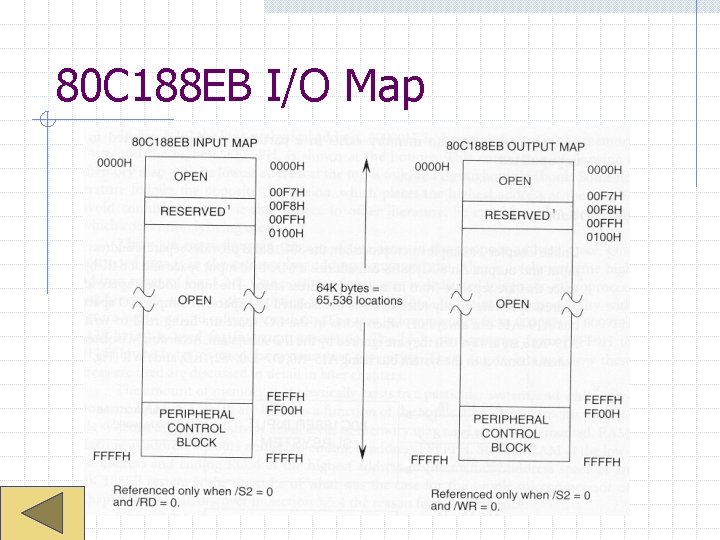

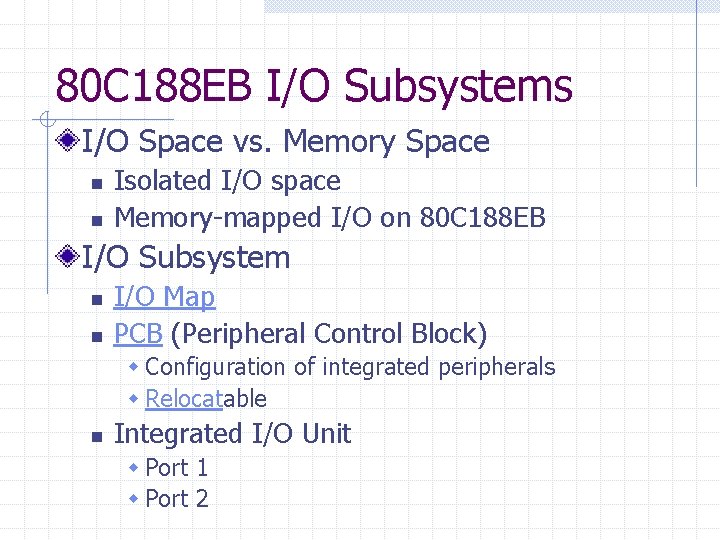

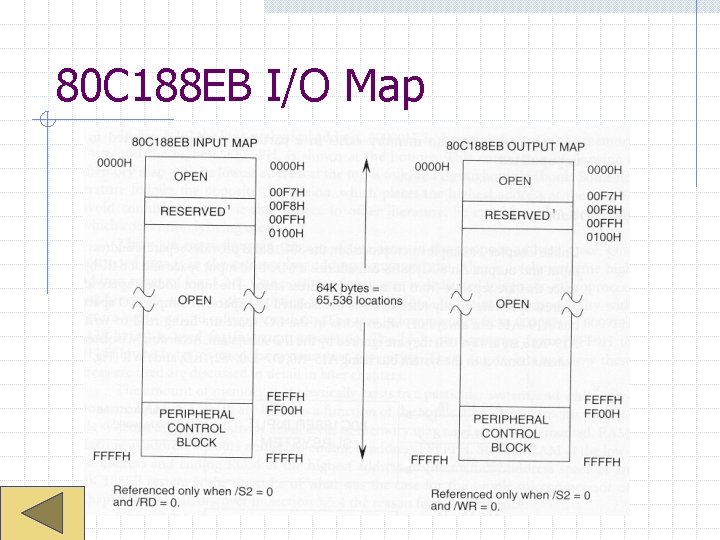

80 C 188 EB I/O Subsystems I/O Space vs. Memory Space n n Isolated I/O space Memory-mapped I/O on 80 C 188 EB I/O Subsystem n n I/O Map PCB (Peripheral Control Block) w Configuration of integrated peripherals w Relocatable n Integrated I/O Unit w Port 1 w Port 2

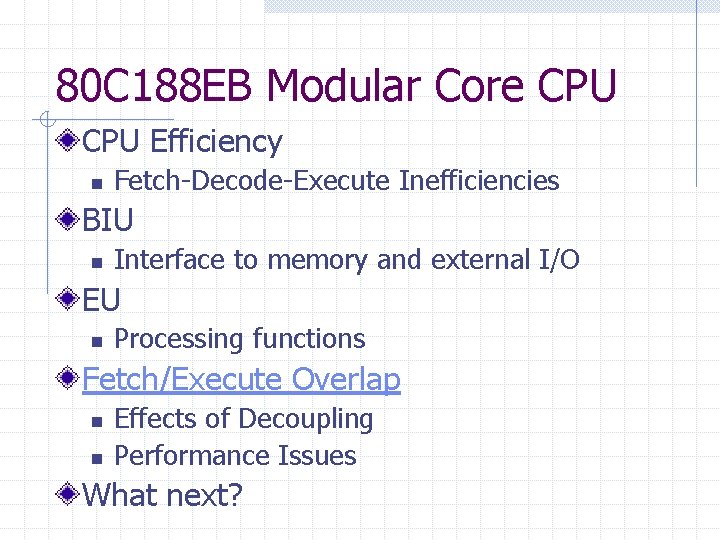

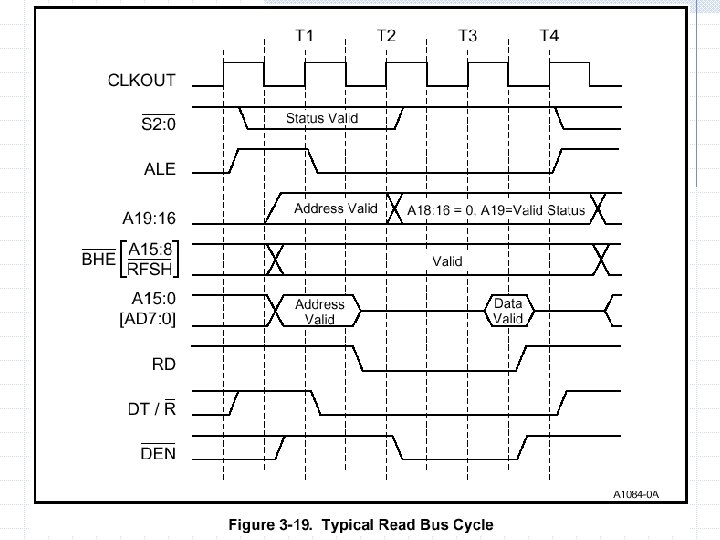

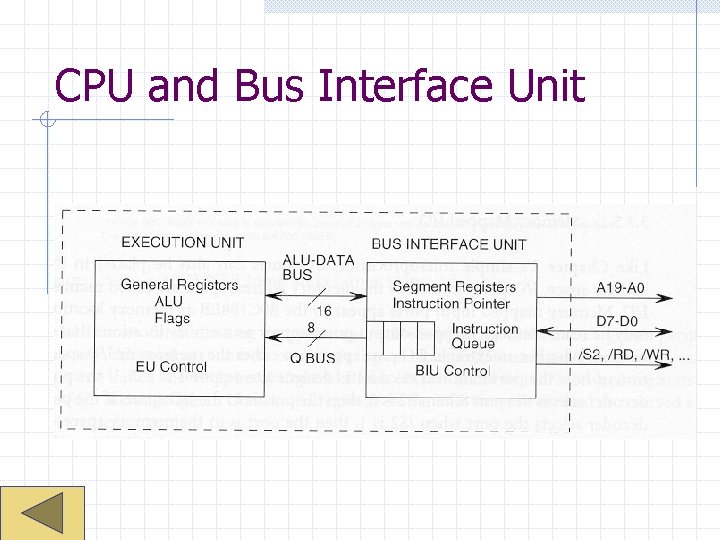

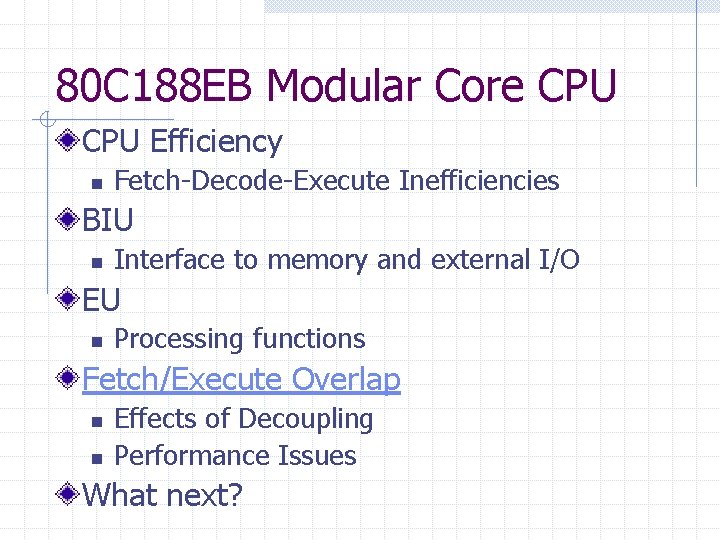

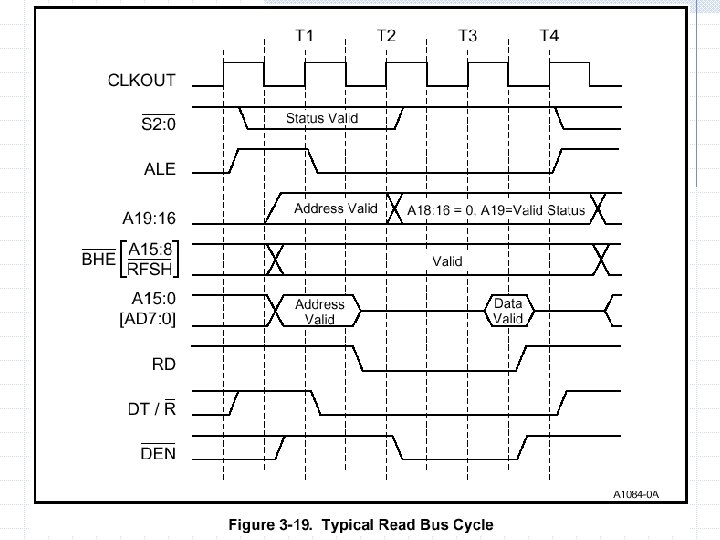

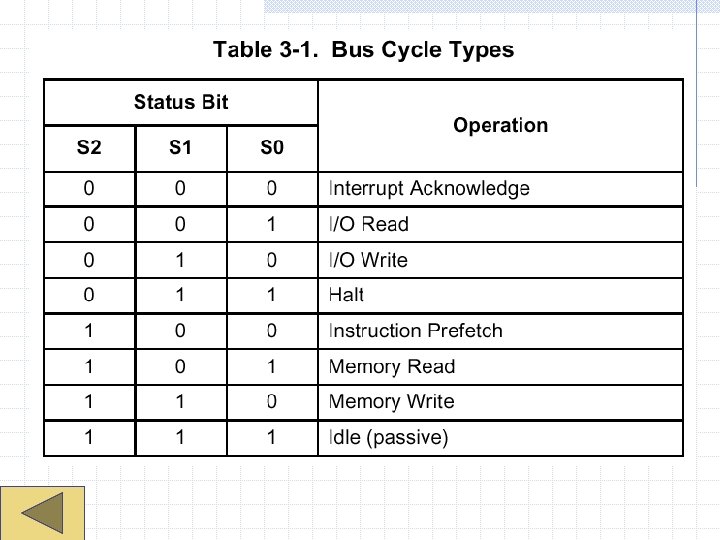

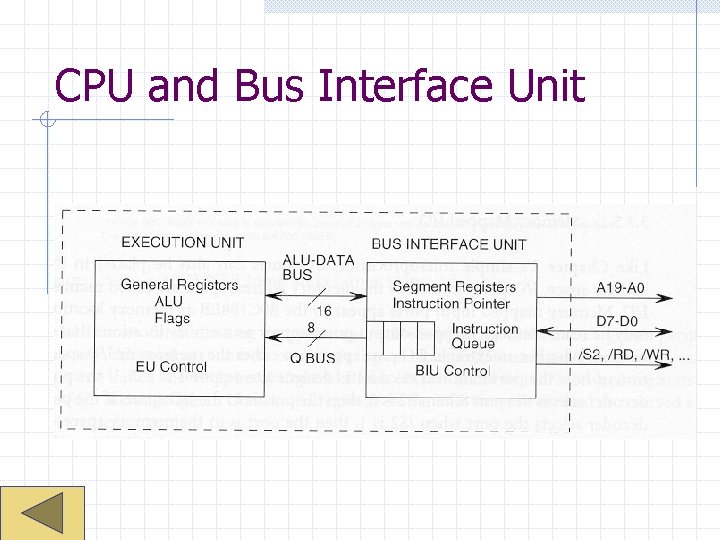

80 C 188 EB Modular Core CPU Efficiency n Fetch-Decode-Execute Inefficiencies BIU n Interface to memory and external I/O EU n Processing functions Fetch/Execute Overlap n n Effects of Decoupling Performance Issues What next?

Wrapping Up Homework #1 due Friday 2/4 Week 3 reading is chapters 3. 5 -3. 9, 4, 5 from textbook

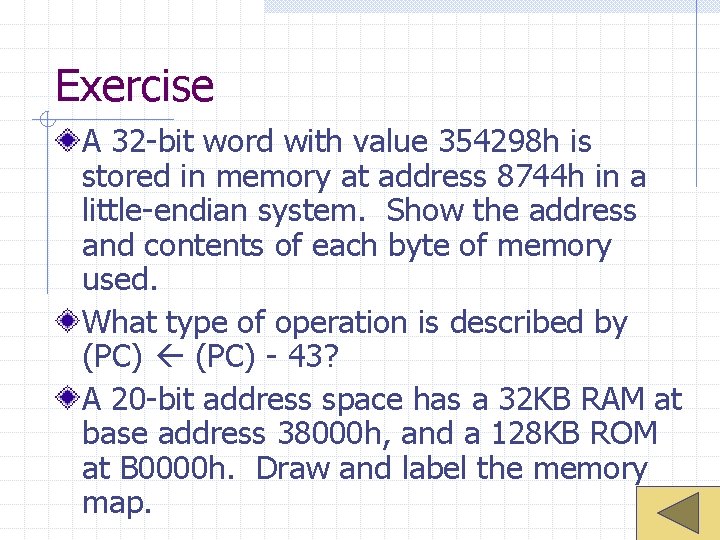

Exercise A 32 -bit word with value 354298 h is stored in memory at address 8744 h in a little-endian system. Show the address and contents of each byte of memory used. What type of operation is described by (PC) - 43? A 20 -bit address space has a 32 KB RAM at base address 38000 h, and a 128 KB ROM at B 0000 h. Draw and label the memory map.

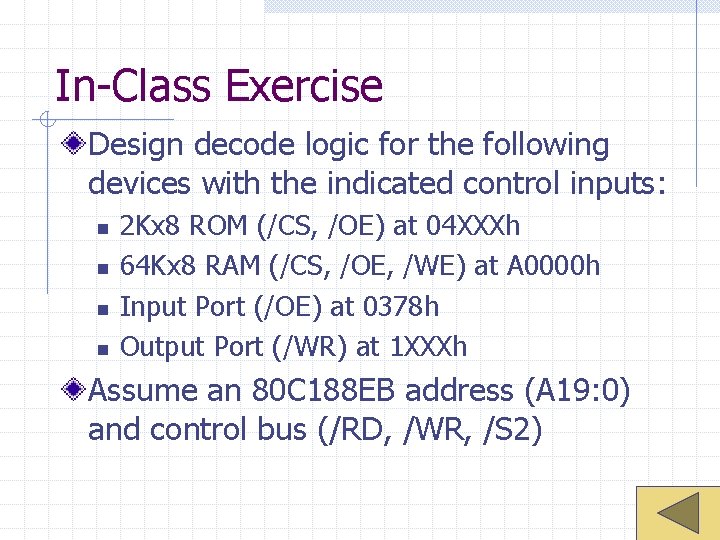

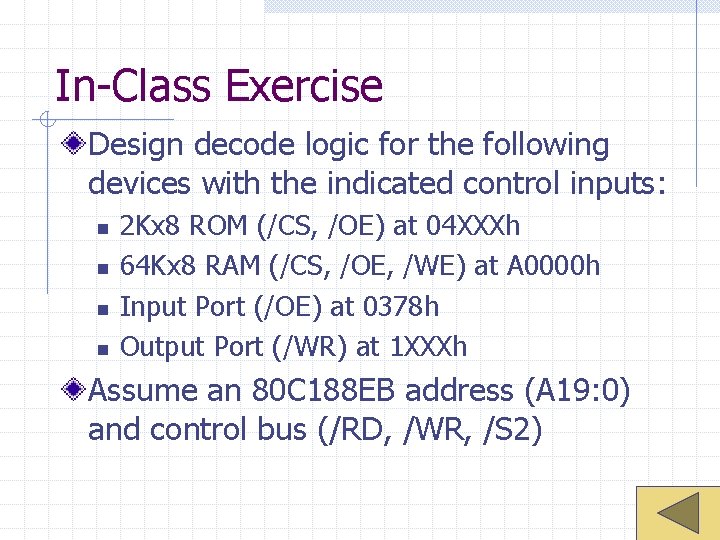

In-Class Exercise Design decode logic for the following devices with the indicated control inputs: n n 2 Kx 8 ROM (/CS, /OE) at 04 XXXh 64 Kx 8 RAM (/CS, /OE, /WE) at A 0000 h Input Port (/OE) at 0378 h Output Port (/WR) at 1 XXXh Assume an 80 C 188 EB address (A 19: 0) and control bus (/RD, /WR, /S 2)

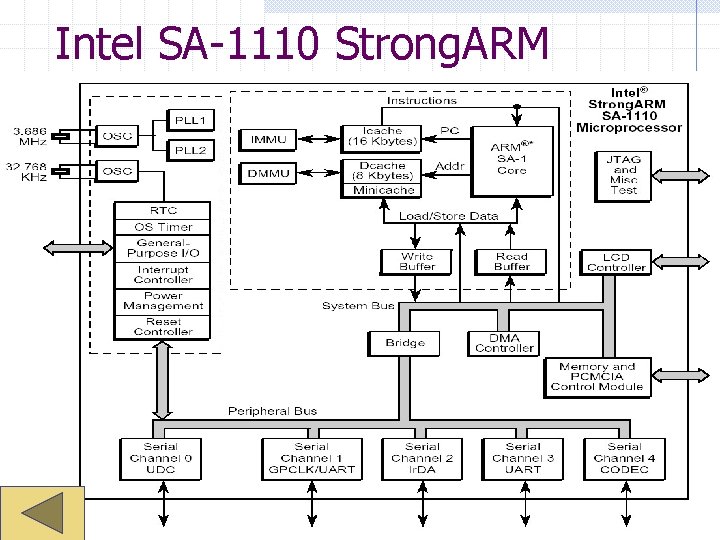

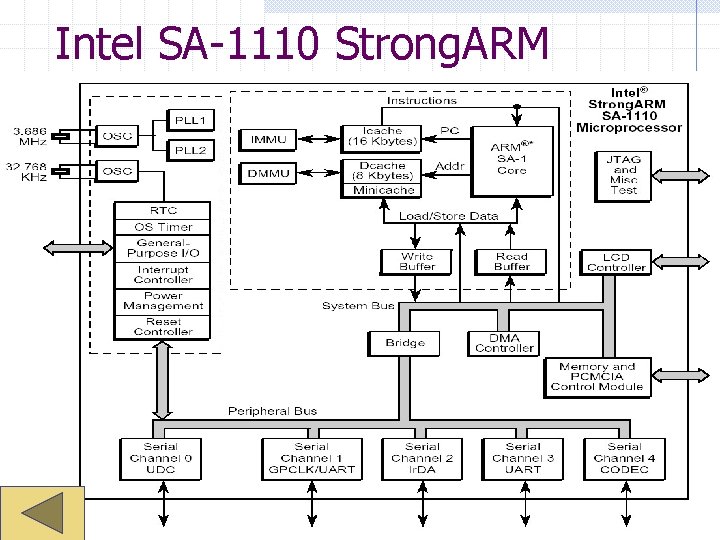

Intel SA-1110 Strong. ARM

80 C 188 EB Block Diagram

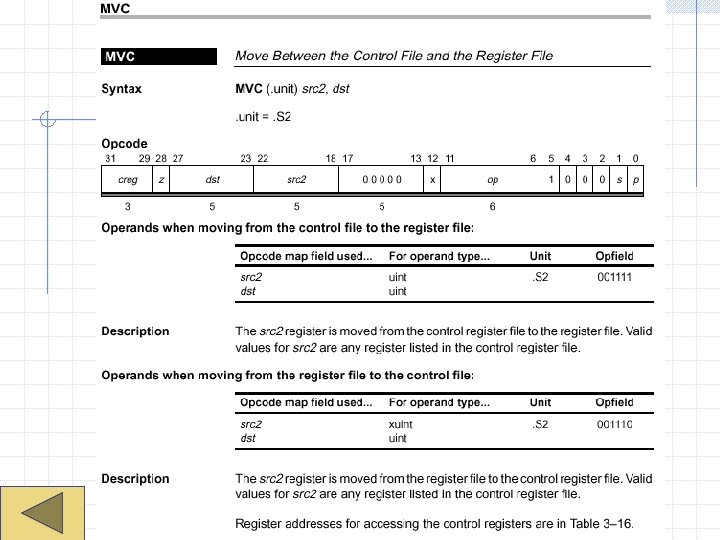

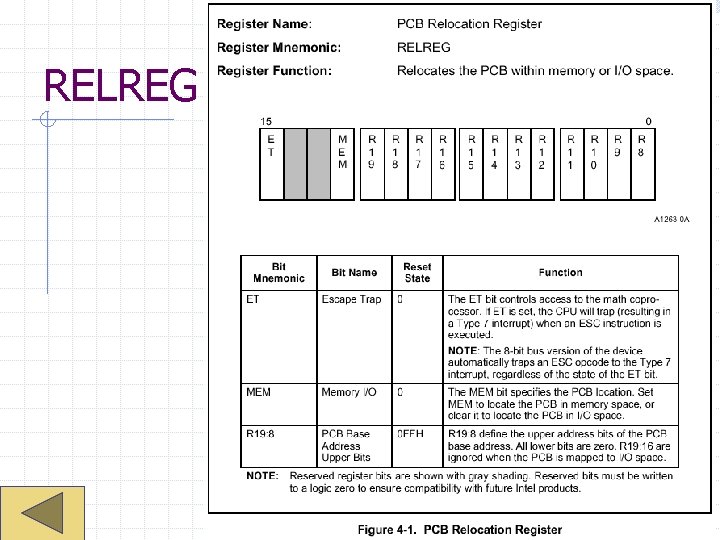

RELREG

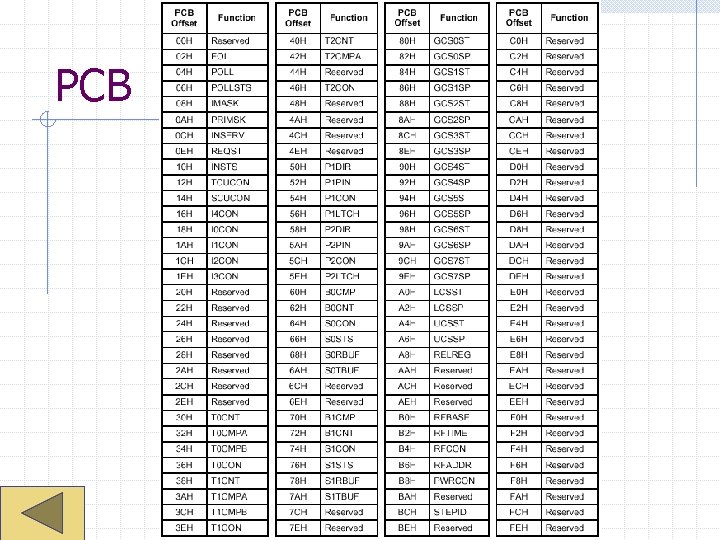

PCB

Register View of a Simple P aka “Von Neumann” or “Princeton” architecture

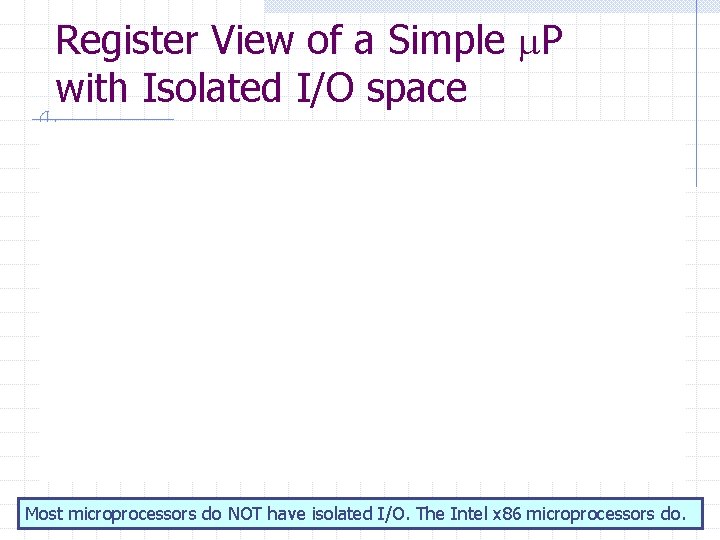

Register View of a Simple P with Isolated I/O space Most microprocessors do NOT have isolated I/O. The Intel x 86 microprocessors do.

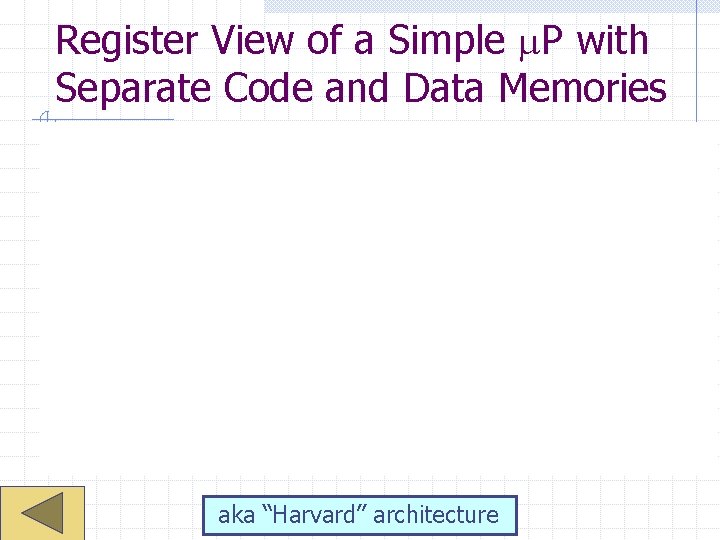

Register View of a Simple P with Separate Code and Data Memories aka “Harvard” architecture

80 C 188 EB System Diagram

Minimal 80 C 188 EB CPU Subsystem

80 C 188 EB I/O Map

CPU and Bus Interface Unit