ECE 353 Introduction to Microprocessor Systems Week 11

- Slides: 43

ECE 353 Introduction to Microprocessor Systems Week 11 Michael J. Schulte

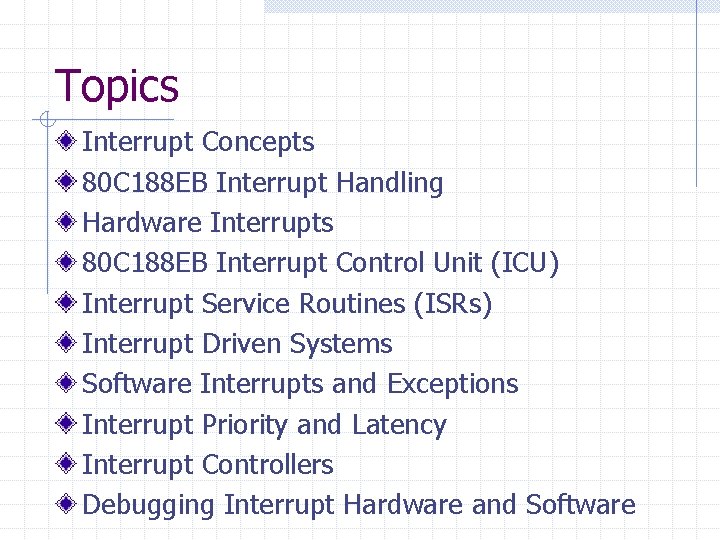

Topics Interrupt Concepts 80 C 188 EB Interrupt Handling Hardware Interrupts 80 C 188 EB Interrupt Control Unit (ICU) Interrupt Service Routines (ISRs) Interrupt Driven Systems Software Interrupts and Exceptions Interrupt Priority and Latency Interrupt Controllers Debugging Interrupt Hardware and Software

Why Use Interrupts? Maximize processor utilization and efficiency Allow use of sleep/idle states when nothing to do to save power Minimize latency in responding to complex input/output structures Facilitate event driven applications

Interrupt Primer Terminology n n n Event – an occurrence that the processor must respond to Asynchronous events – events that occur at unpredictable times while program is running Pending interrupt – an IRQ signal has been received, but it has not been serviced yet. Interrupt Service Routine (ISr) – the code executed in response to an IRQ signal. Interrupt-driven I/O – I/O devices that use interrupts to signal when they require service Critical code section – a section of code that cannot be interrupted

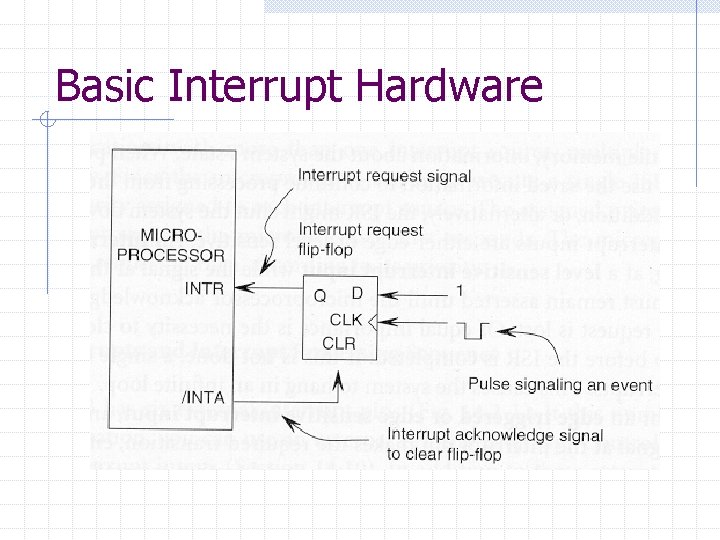

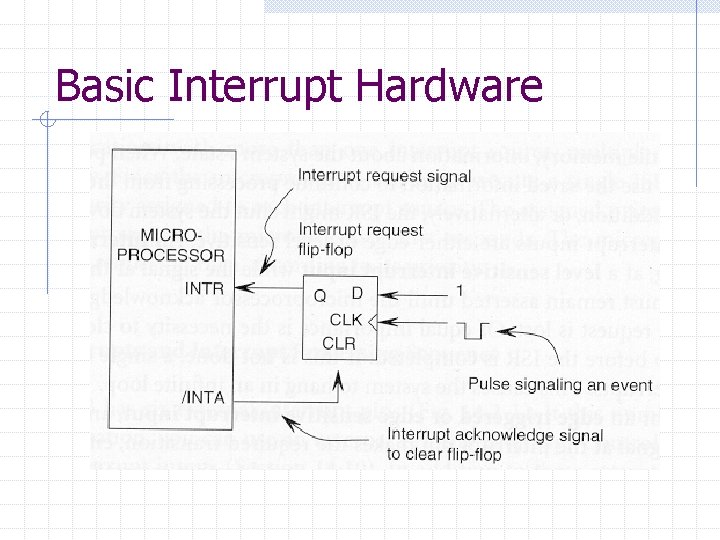

Basic Interrupt Hardware

Types of Interrupts n n Maskable interrupt – an interrupt that can be disabled when desired Nonmaskable interrupt (NMI) – an interrupt that cannot be disabled. Level-sensitive interrupts – an interrupt request is said to exist whenever the IRQ signal is at the designated level Edge-sensitive interrupts – an interrupt is only recognized on the signal’s transition

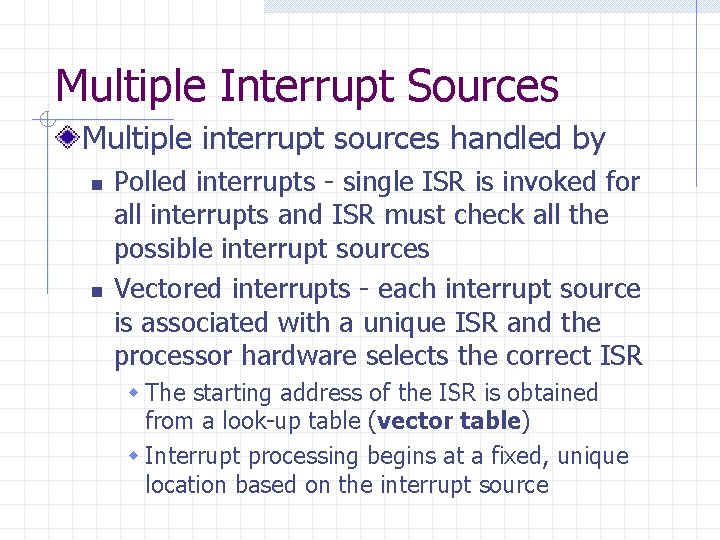

Multiple Interrupt Sources Multiple interrupt sources handled by n n Polled interrupts - single ISR is invoked for all interrupts and ISR must check all the possible interrupt sources Vectored interrupts - each interrupt source is associated with a unique ISR and the processor hardware selects the correct ISR w The starting address of the ISR is obtained from a look-up table (vector table) w Interrupt processing begins at a fixed, unique location based on the interrupt source

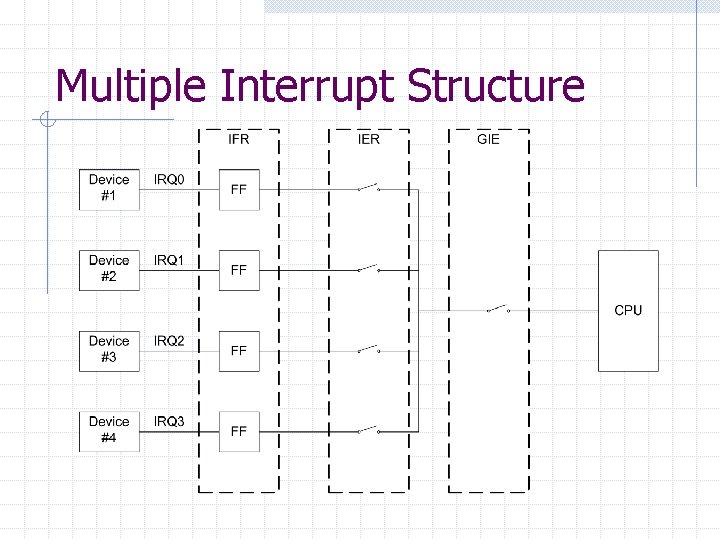

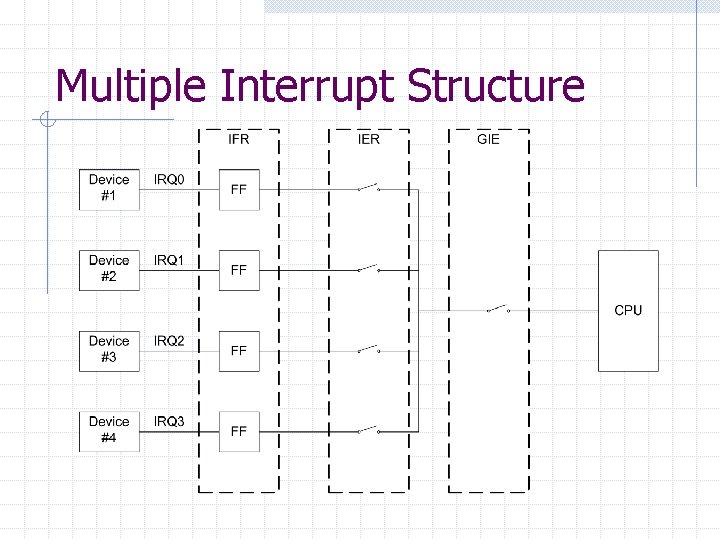

Multiple Interrupt Structure

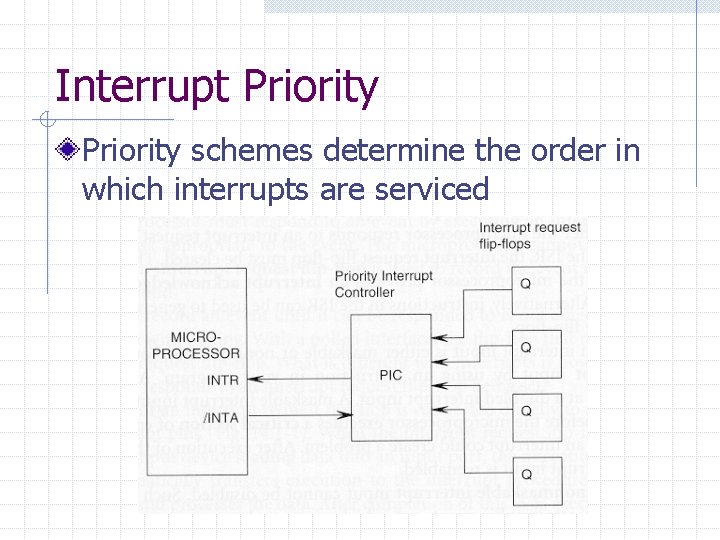

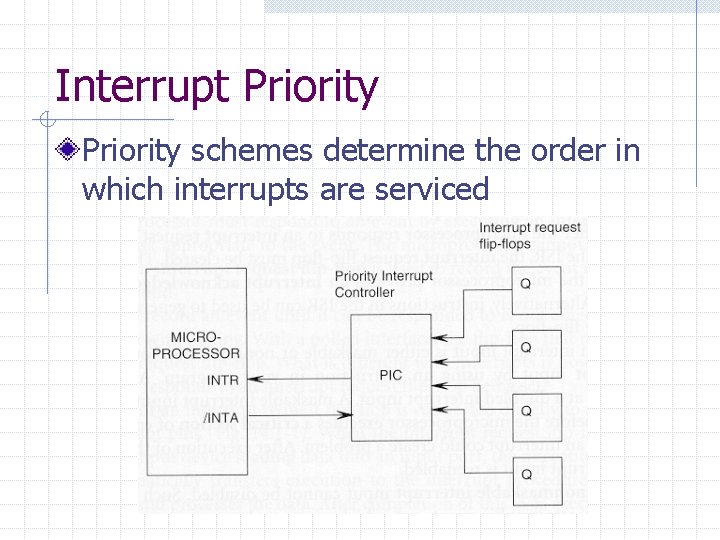

Interrupt Priority schemes determine the order in which interrupts are serviced

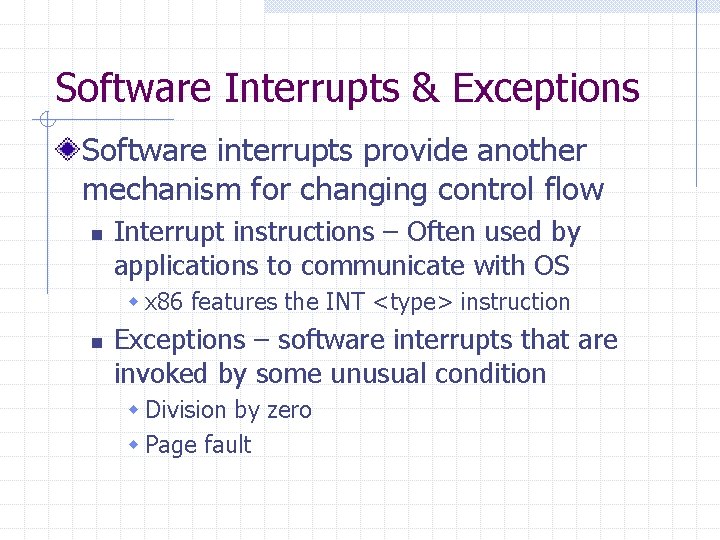

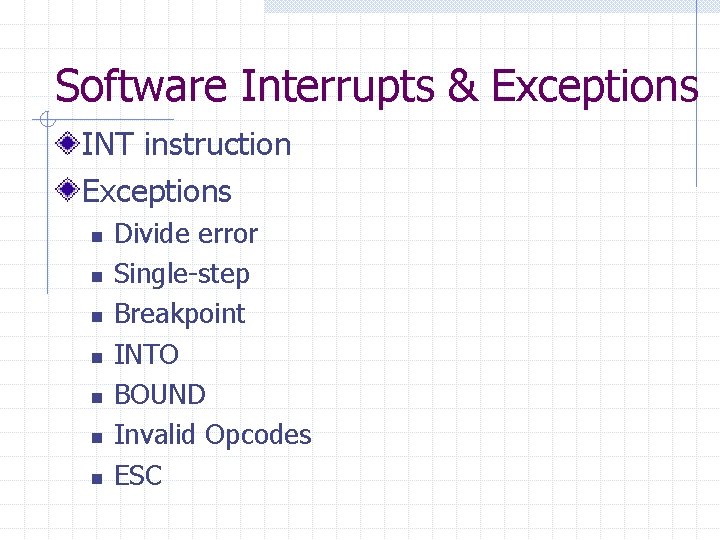

Software Interrupts & Exceptions Software interrupts provide another mechanism for changing control flow n Interrupt instructions – Often used by applications to communicate with OS w x 86 features the INT <type> instruction n Exceptions – software interrupts that are invoked by some unusual condition w Division by zero w Page fault

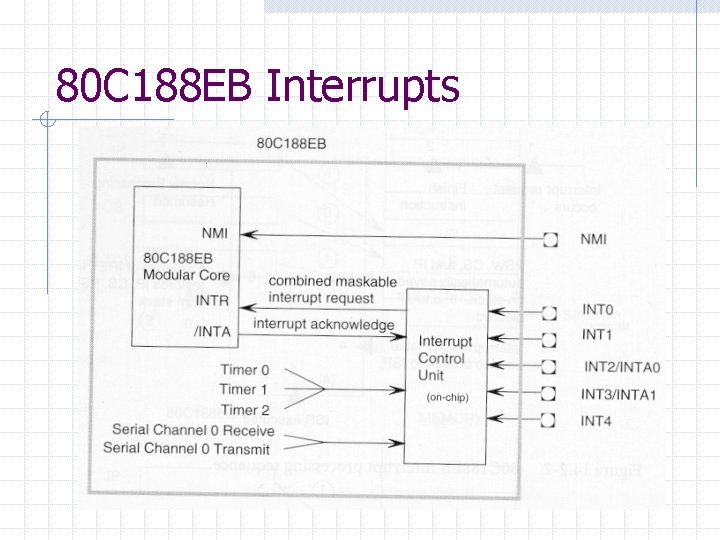

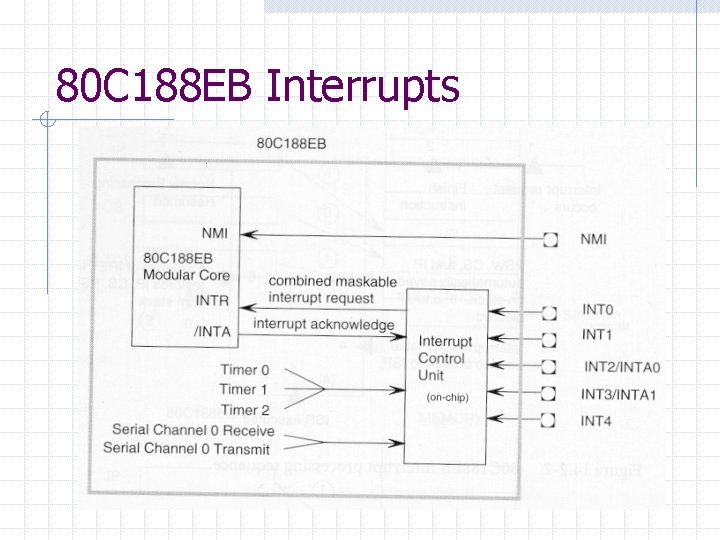

80 C 188 EB Interrupts

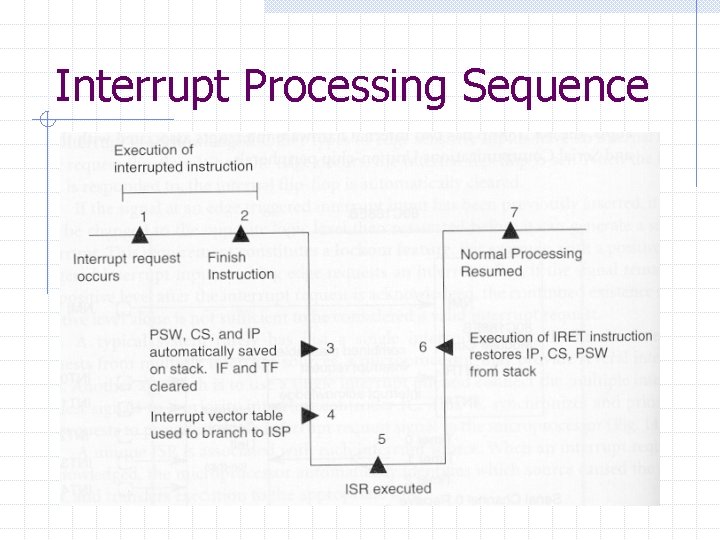

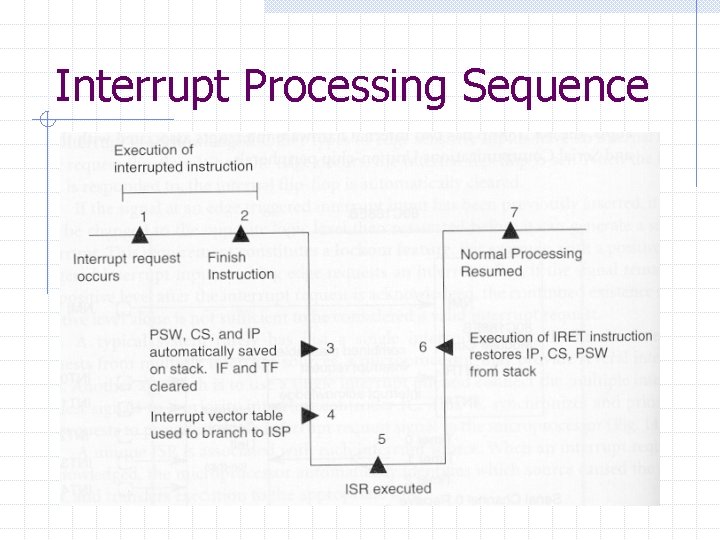

Interrupt Processing Sequence

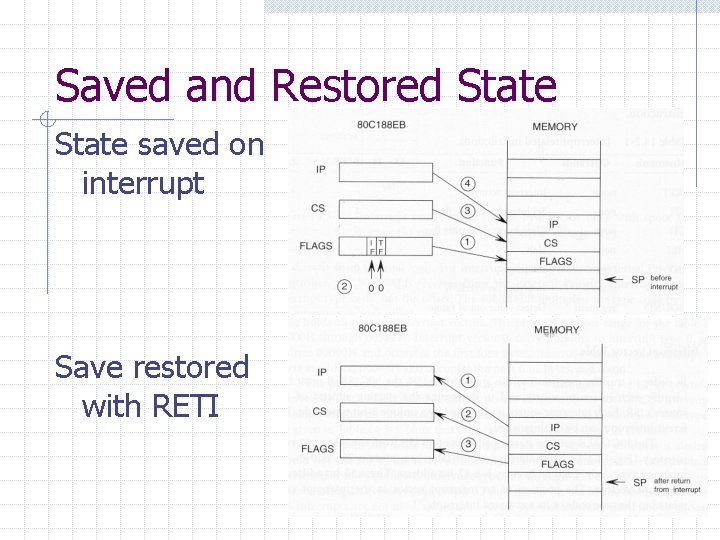

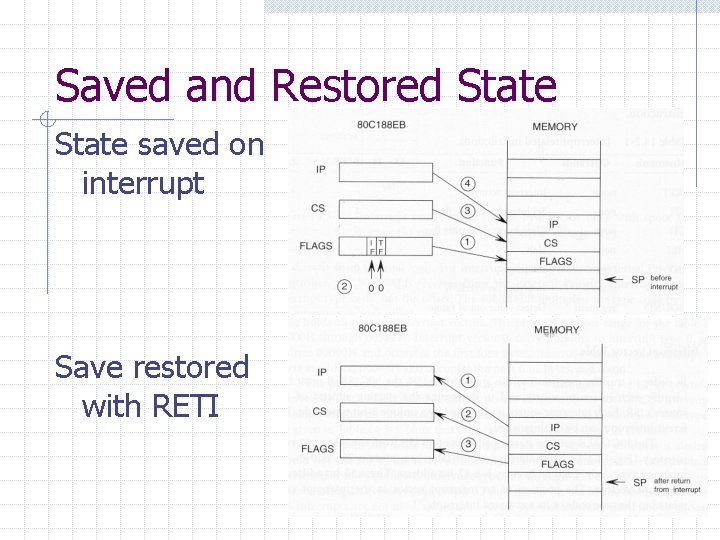

Saved and Restored State saved on interrupt Save restored with RETI

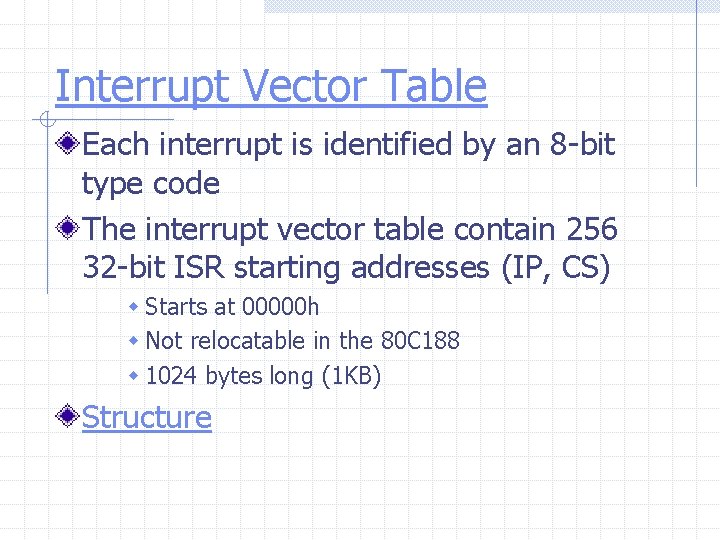

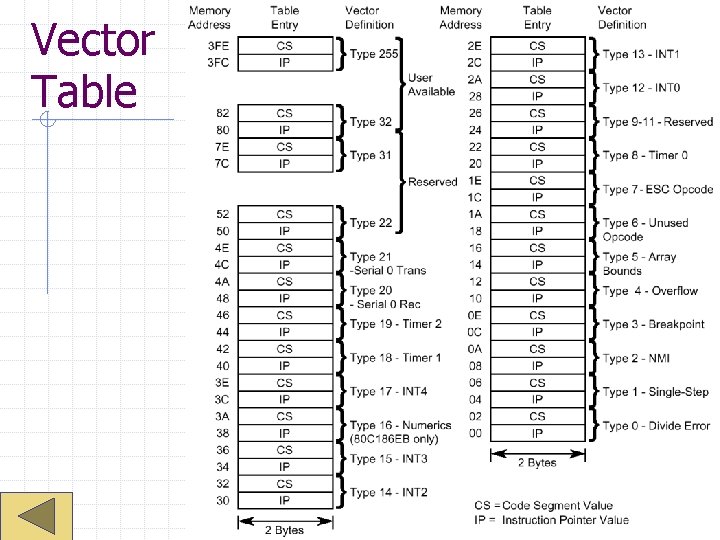

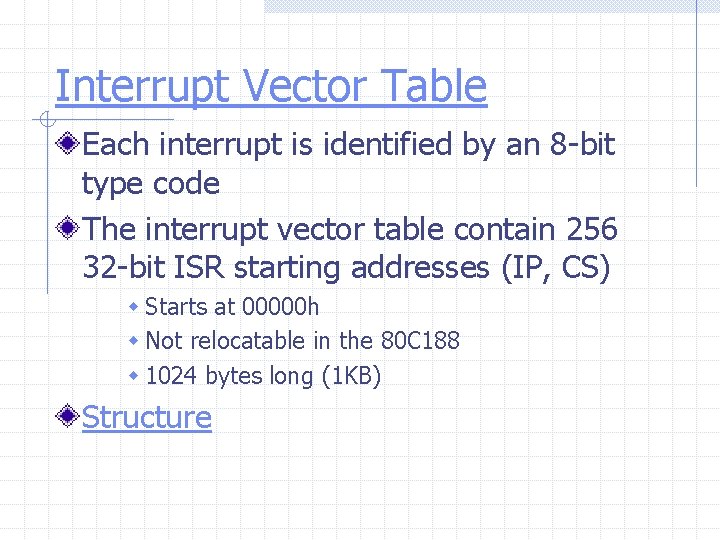

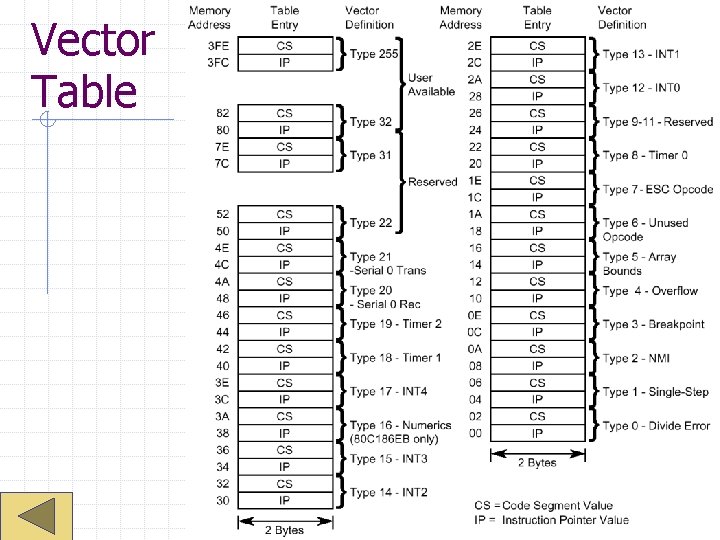

Interrupt Vector Table Each interrupt is identified by an 8 -bit type code The interrupt vector table contain 256 32 -bit ISR starting addresses (IP, CS) w Starts at 00000 h w Not relocatable in the 80 C 188 w 1024 bytes long (1 KB) Structure

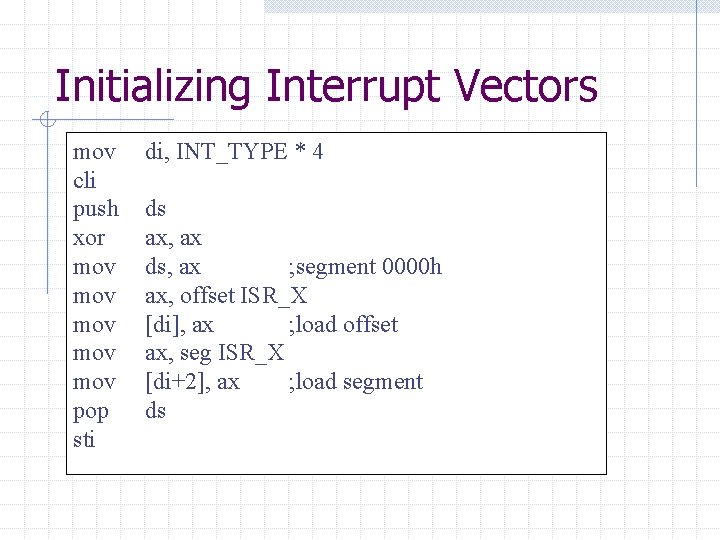

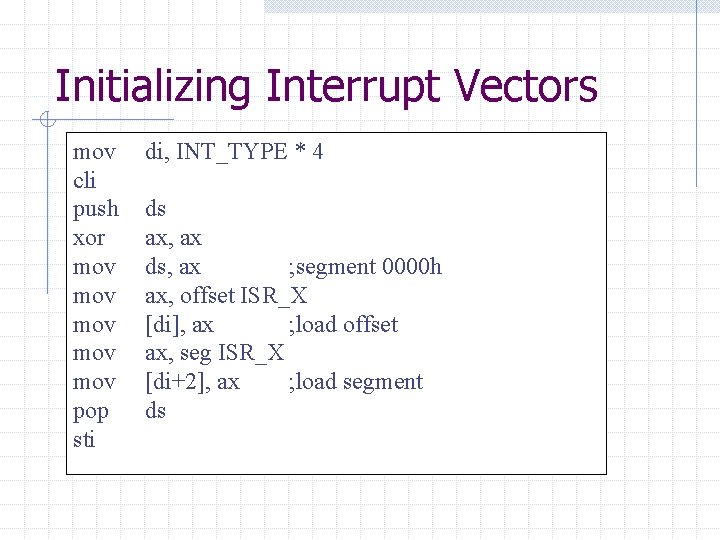

Initializing Interrupt Vectors mov cli push xor mov mov mov pop sti di, INT_TYPE * 4 ds ax, ax ds, ax ; segment 0000 h ax, offset ISR_X [di], ax ; load offset ax, seg ISR_X [di+2], ax ; load segment ds

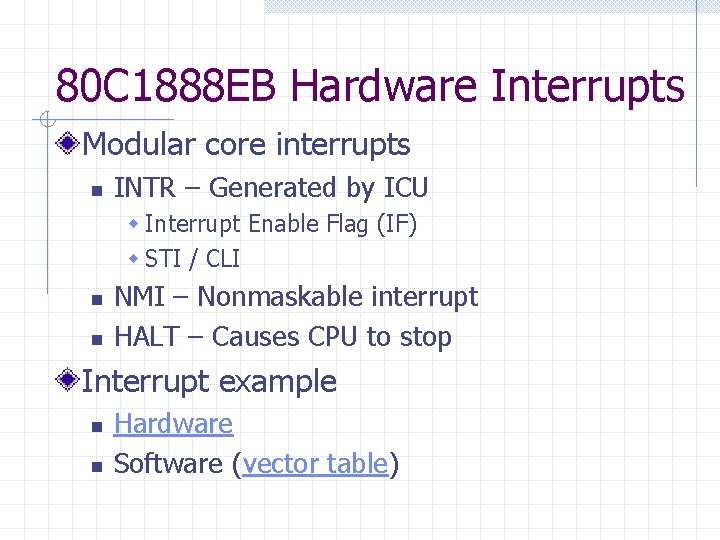

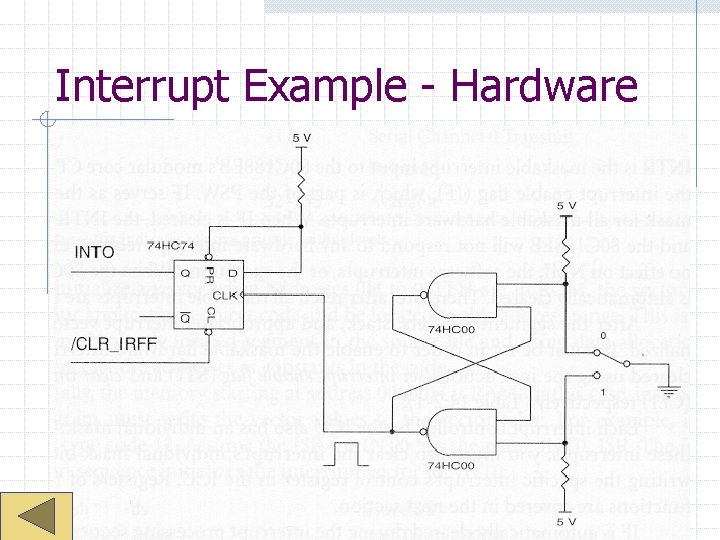

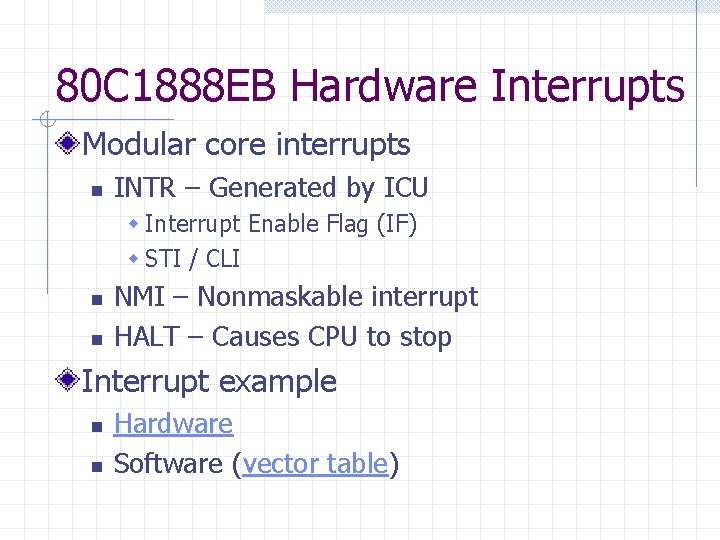

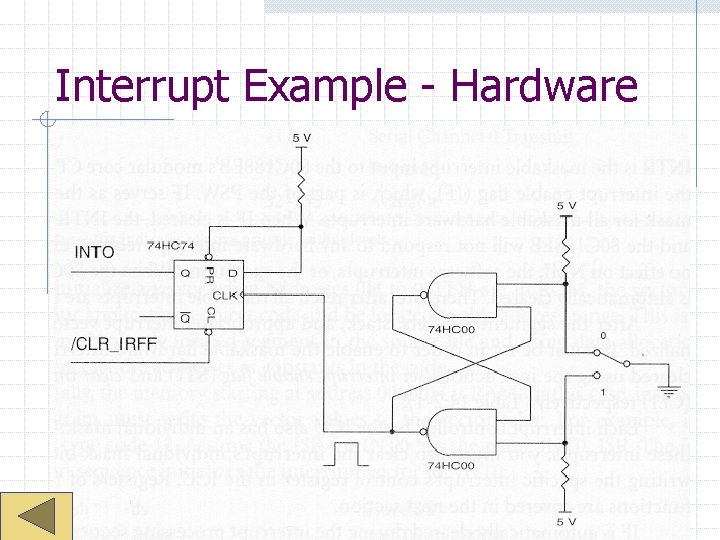

80 C 1888 EB Hardware Interrupts Modular core interrupts n INTR – Generated by ICU w Interrupt Enable Flag (IF) w STI / CLI n n NMI – Nonmaskable interrupt HALT – Causes CPU to stop Interrupt example n n Hardware Software (vector table)

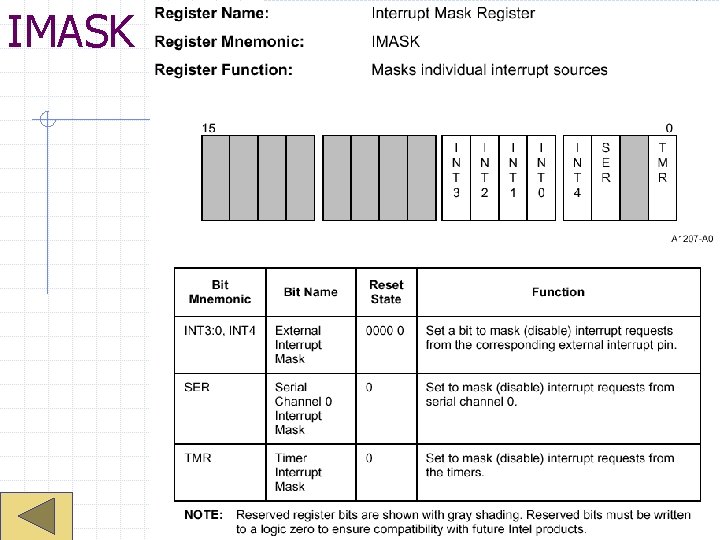

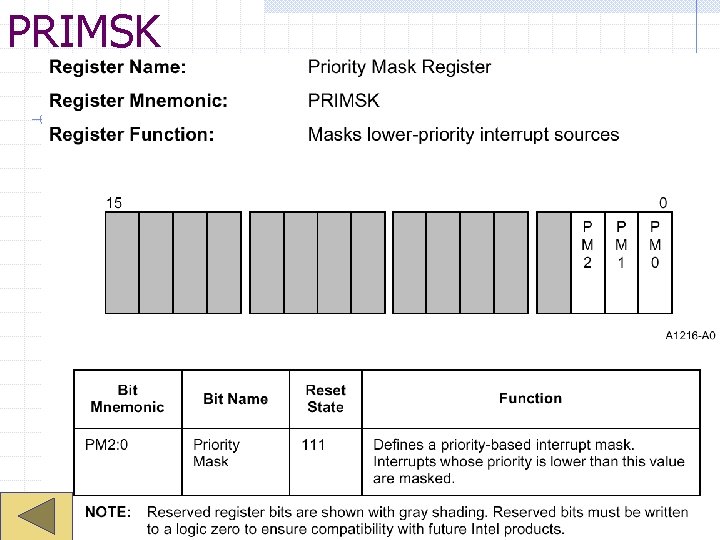

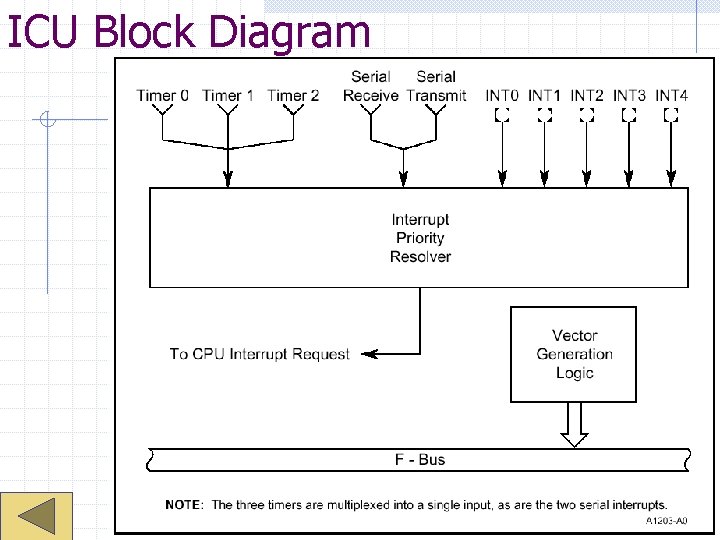

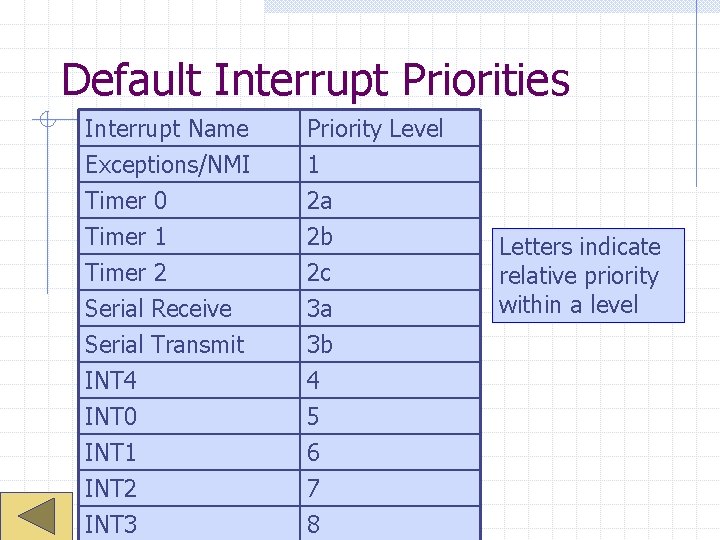

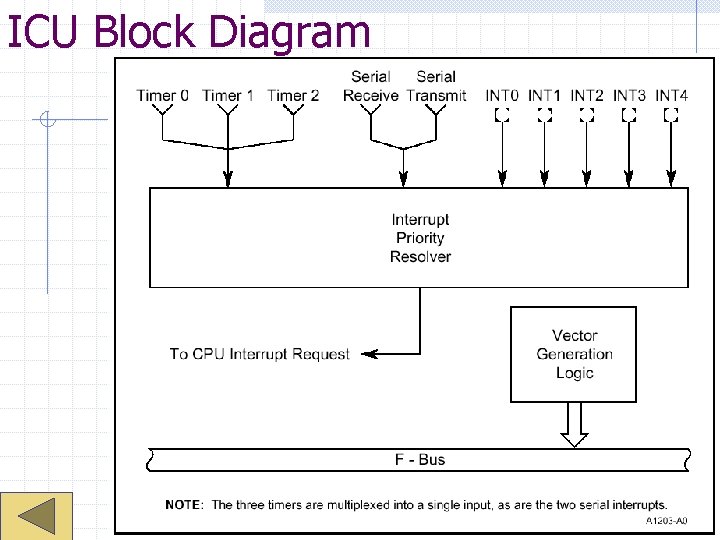

80 C 188 EB ICU Performs synchronization and prioritization of interrupts to CPU (block diagram) Functions n n Masking (IMASK, PRIMSK) Priorities (TCU/SCU, INT 0 -1, INT 2 -4) w Default n n n Synchronization/prioritization (REQST, INSERV) External interrupts (INT 0 -1, INT 2 -4) Internal interrupts (TCU/SCU, INTSTS) Polling interrupt sources (POLLSTS, POLL)

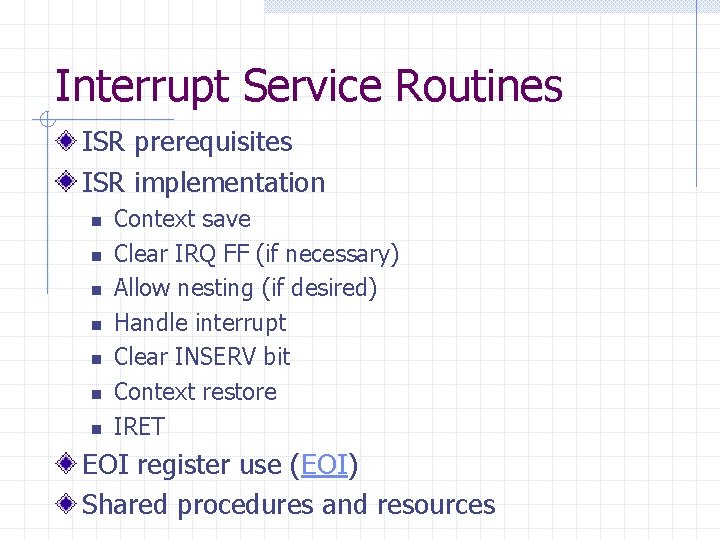

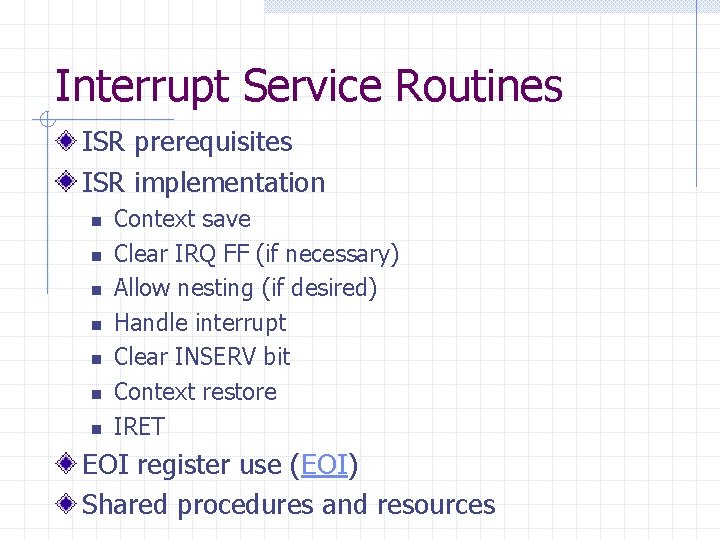

Interrupt Service Routines ISR prerequisites ISR implementation n n n Context save Clear IRQ FF (if necessary) Allow nesting (if desired) Handle interrupt Clear INSERV bit Context restore IRET EOI register use (EOI) Shared procedures and resources

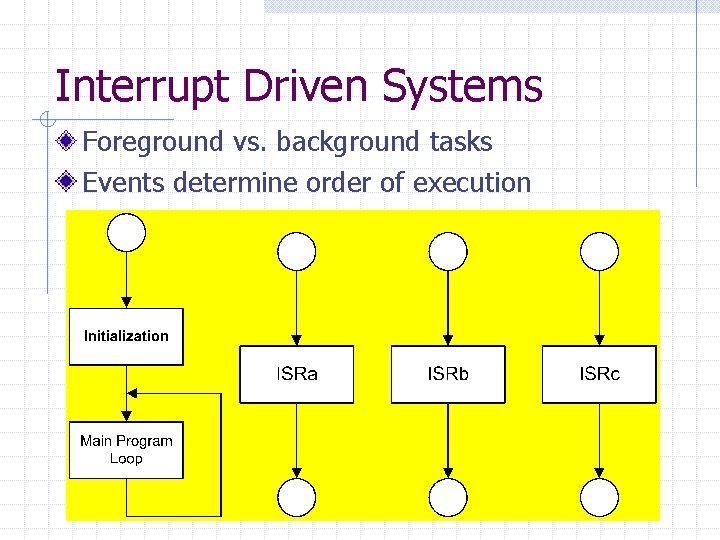

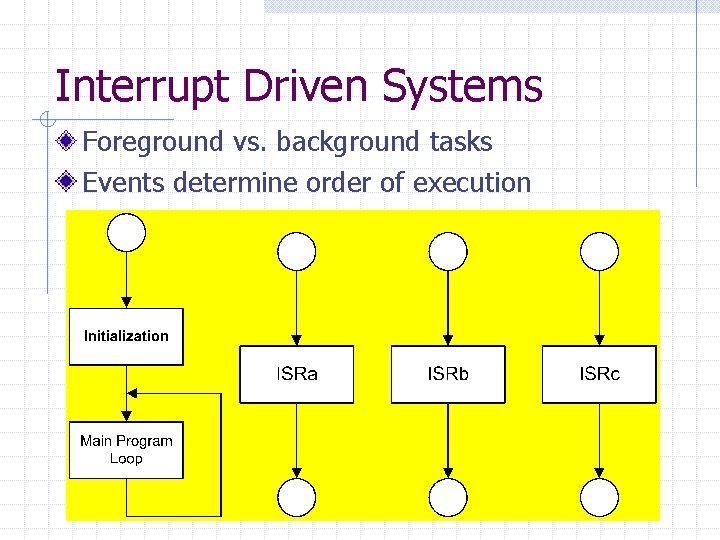

Interrupt Driven Systems Foreground vs. background tasks Events determine order of execution

Software Interrupts & Exceptions INT instruction Exceptions n n n n Divide error Single-step Breakpoint INTO BOUND Invalid Opcodes ESC

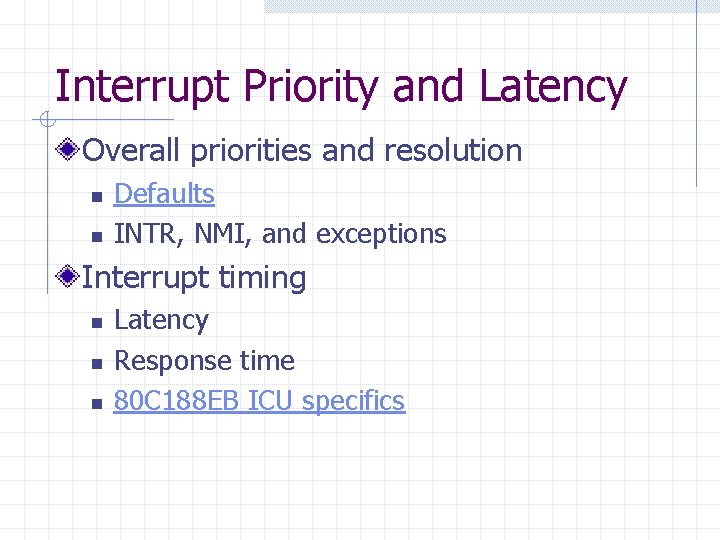

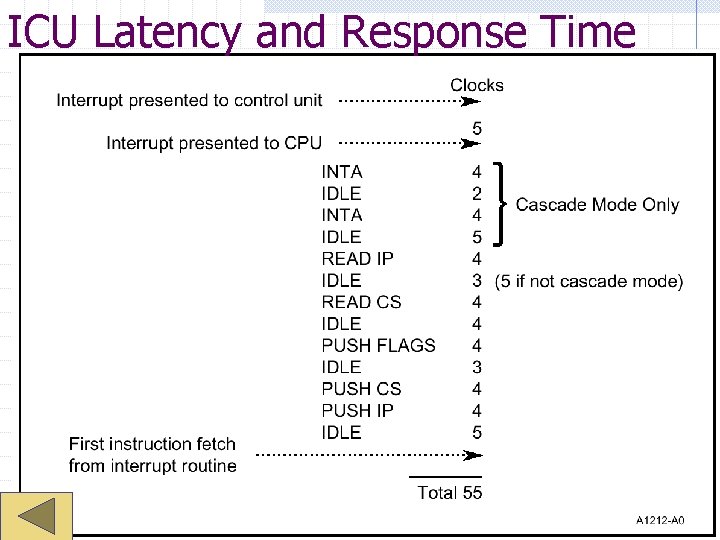

Interrupt Priority and Latency Overall priorities and resolution n n Defaults INTR, NMI, and exceptions Interrupt timing n n n Latency Response time 80 C 188 EB ICU specifics

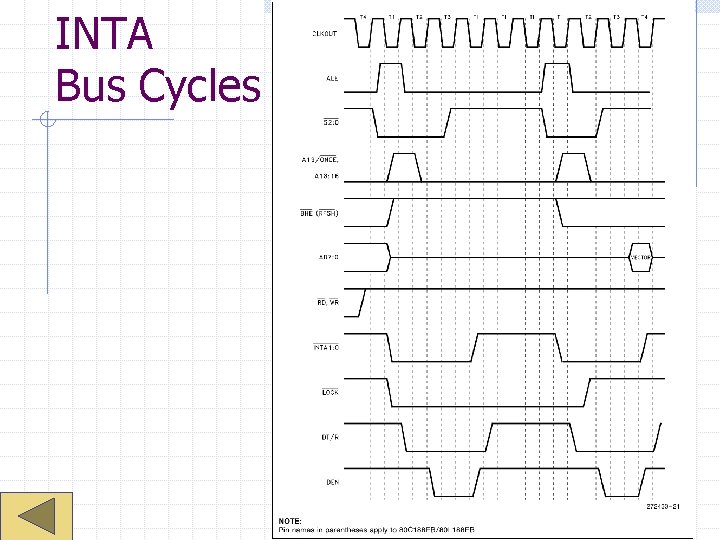

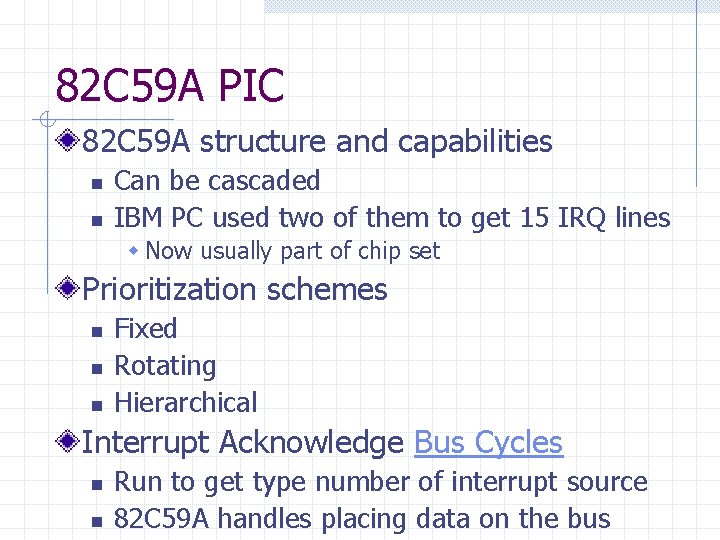

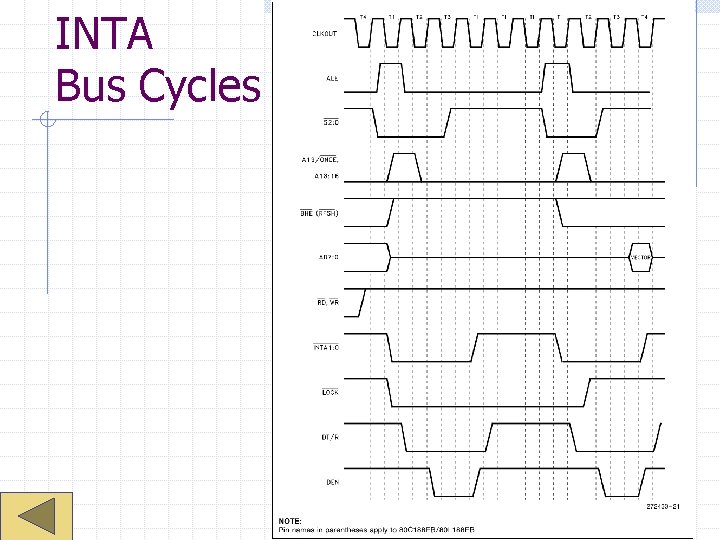

82 C 59 A PIC 82 C 59 A structure and capabilities n n Can be cascaded IBM PC used two of them to get 15 IRQ lines w Now usually part of chip set Prioritization schemes n n n Fixed Rotating Hierarchical Interrupt Acknowledge Bus Cycles n n Run to get type number of interrupt source 82 C 59 A handles placing data on the bus

Interrupt Issues Using periodic interrupts to perform iterative tasks What to do when good interrupts go bad… n n Software debugging Hardware debugging Real-time issues Inter-process communication (IPC) issues

In-Class Assessment Quiz What sort of safeguards might you need to design into NMI hardware? For the 80 C 188 EB, describe what happens between an IRQ being asserted and the actual execution of the ISR. What are the differences between vectored interrupts and polled interrupts?

In-Class Assessment Quiz What is a ‘level-sensitive’ interrupt? What problems can arise when using a semaphore to control access to a resource used by the main program and an ISR? What 80 C 188 instructions help handle this? Draw a flowchart for a periodic (1 KHz) ISR that will be used to generate precise delays. Only a single word variable is to be used to communicate with the ISR.

Vector Table

Interrupt Example - Hardware

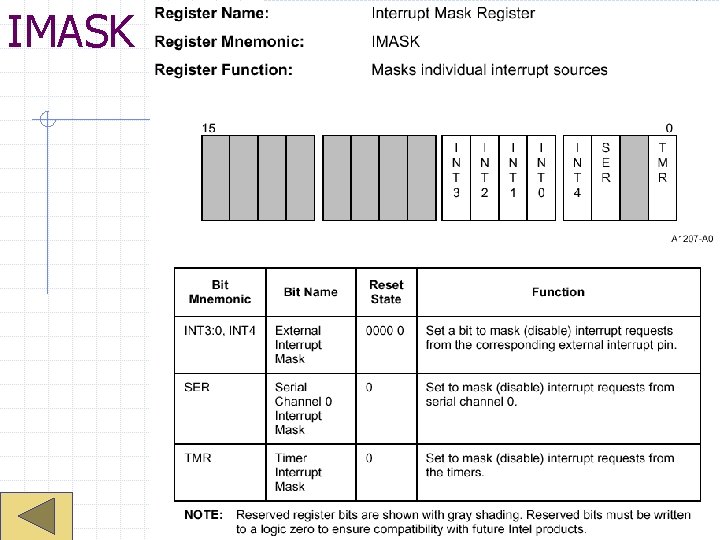

IMASK

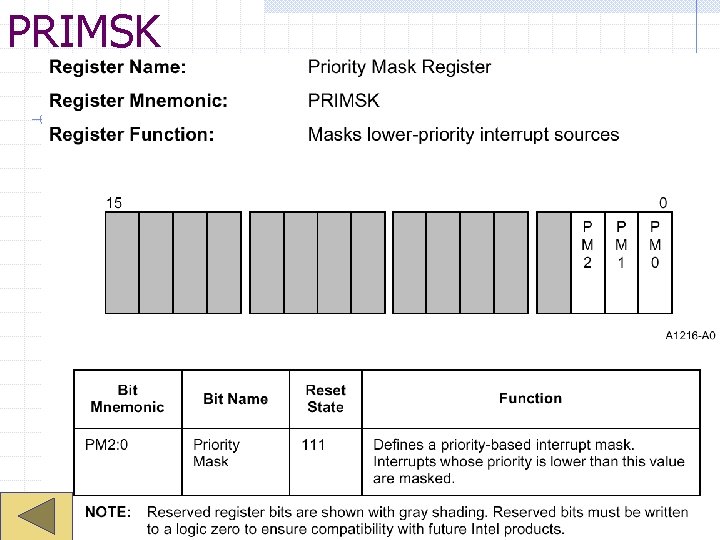

PRIMSK

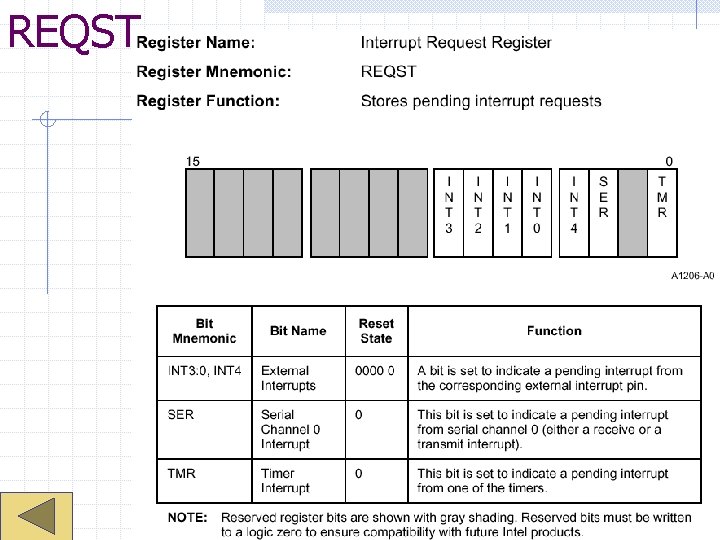

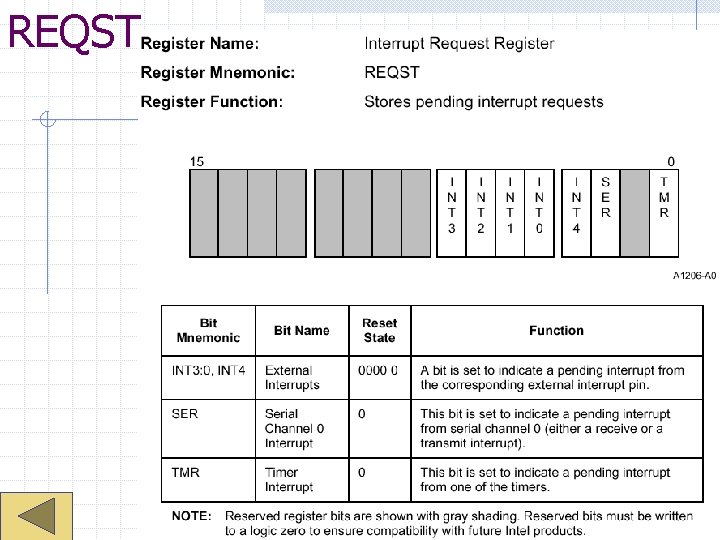

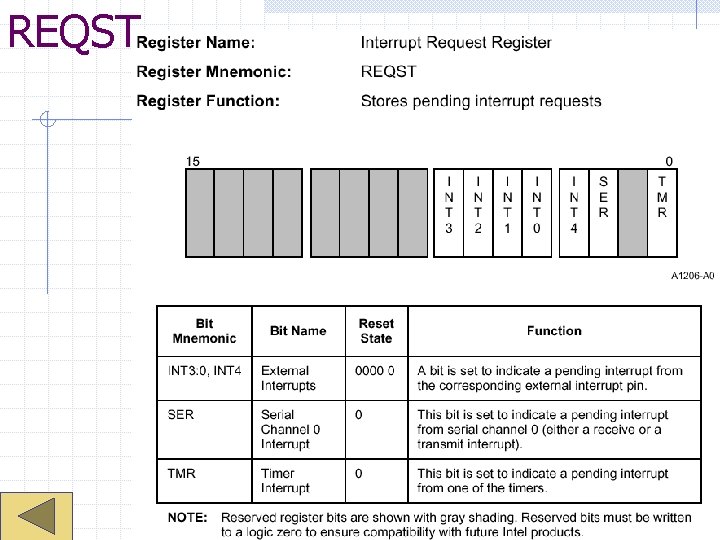

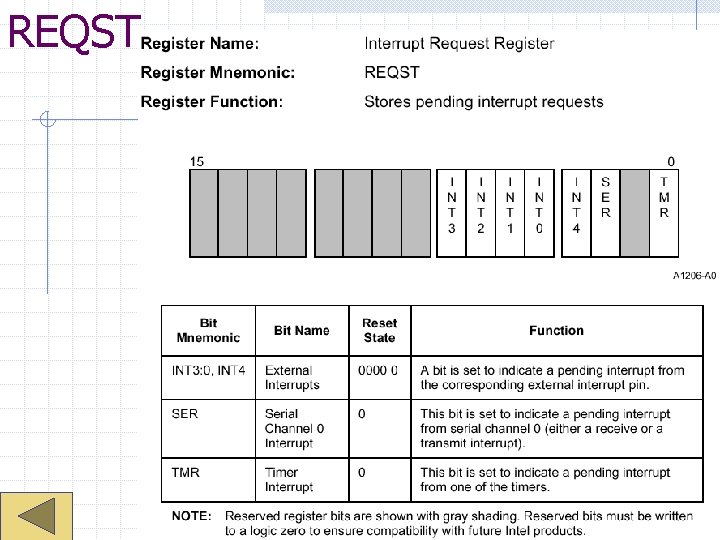

REQST

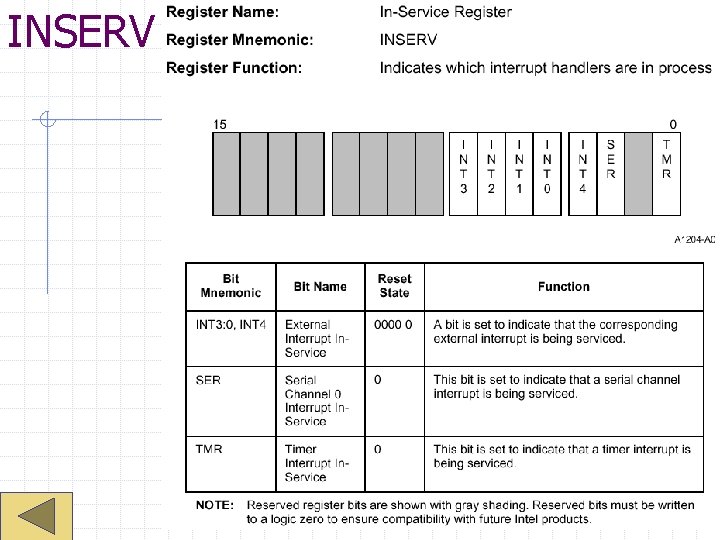

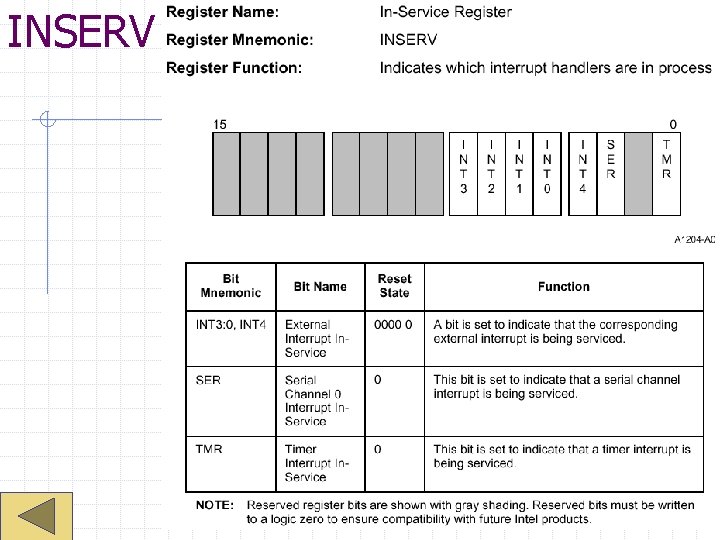

INSERV

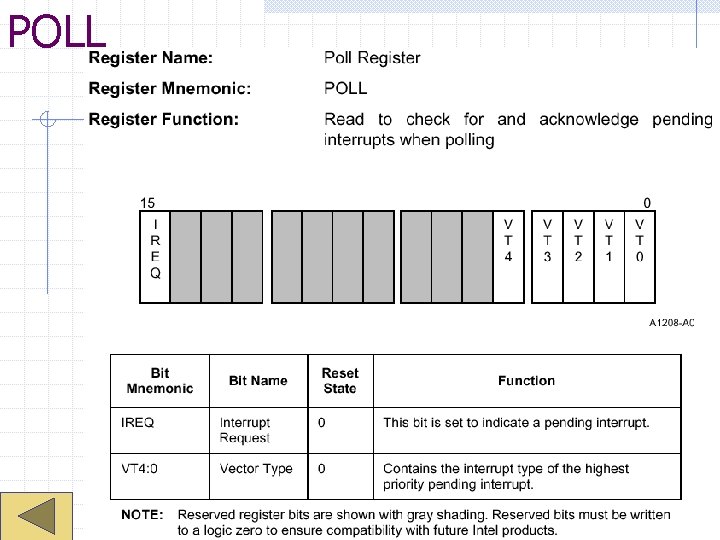

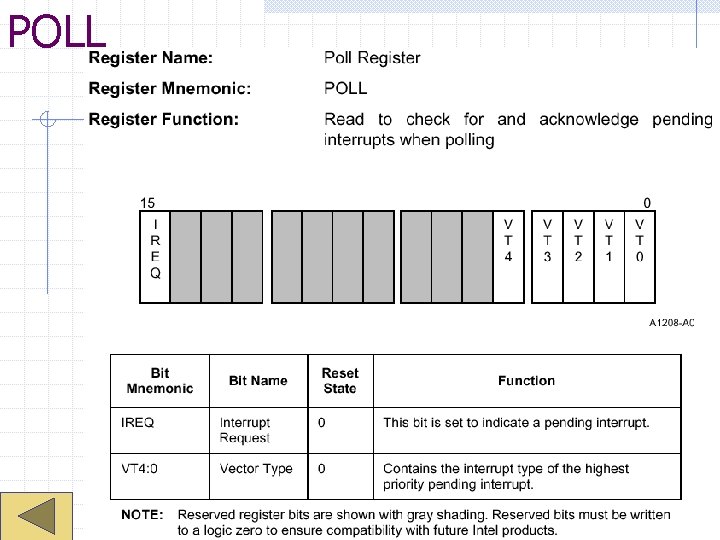

POLL

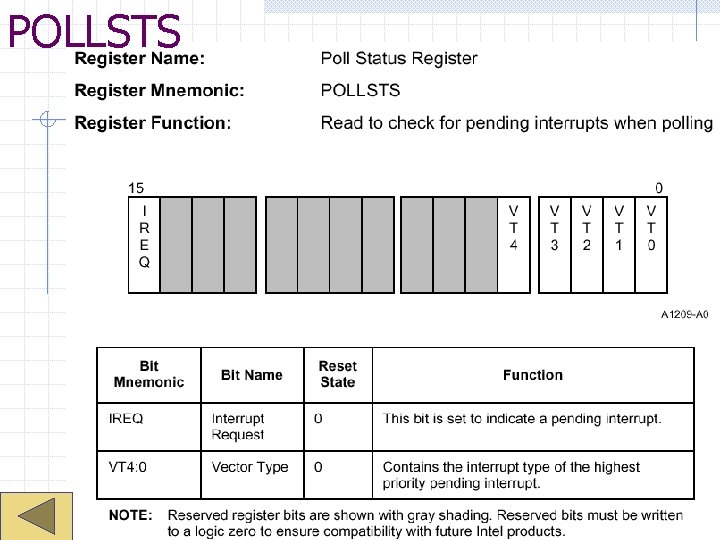

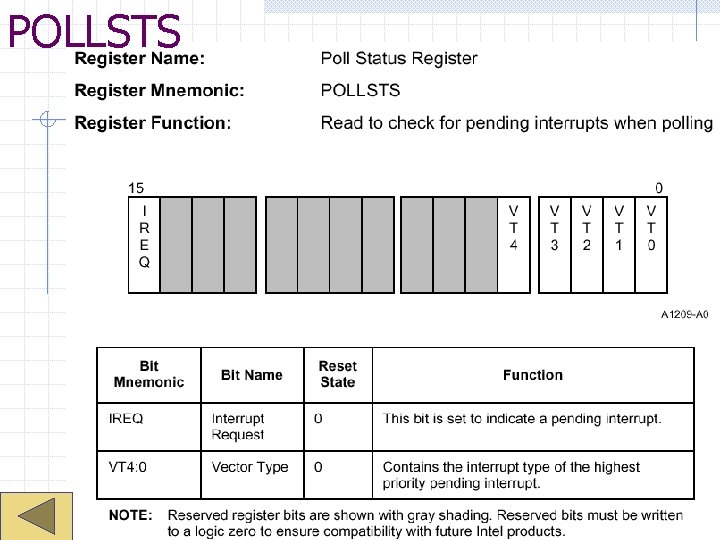

POLLSTS

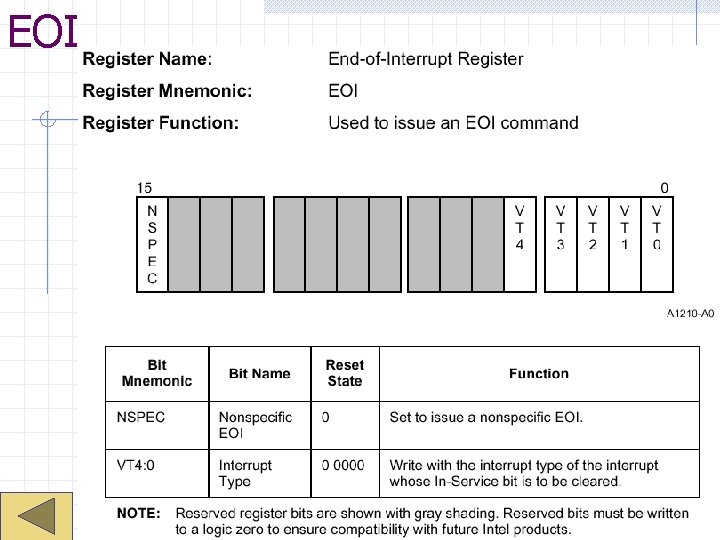

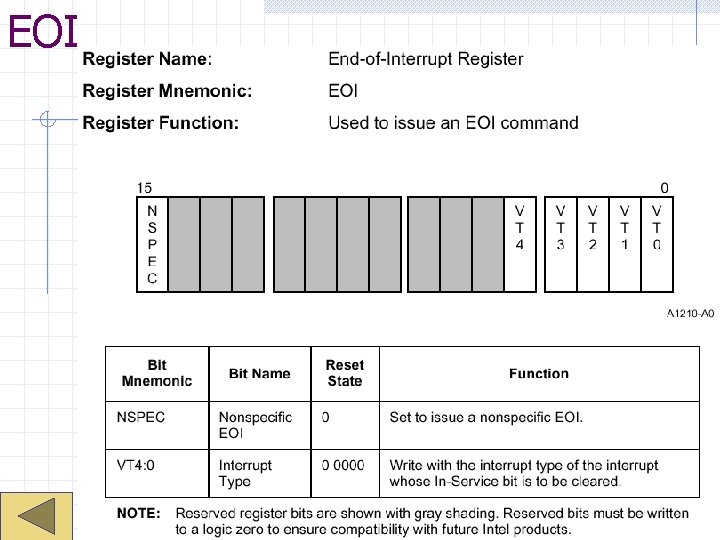

EOI

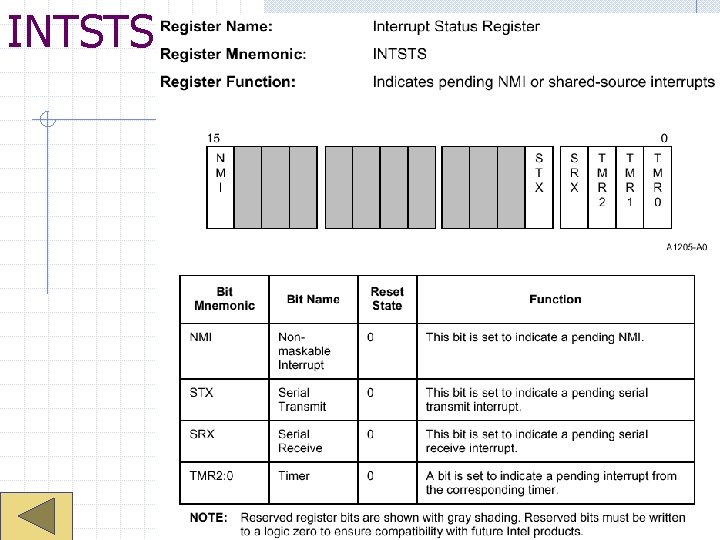

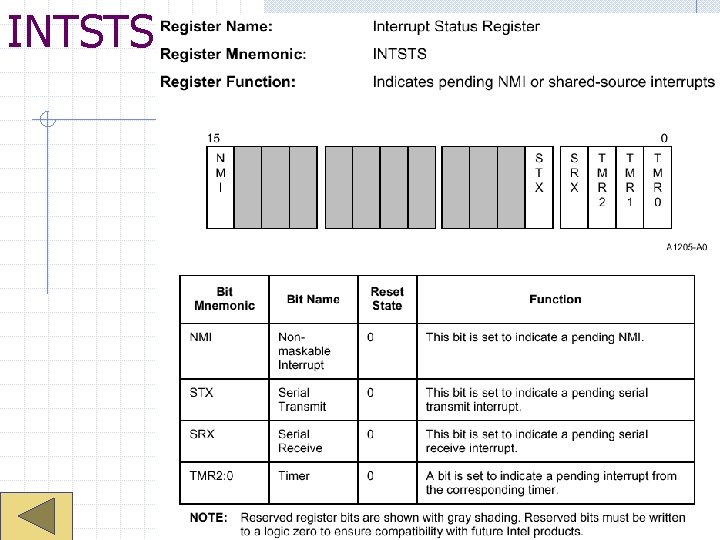

INTSTS

REQST

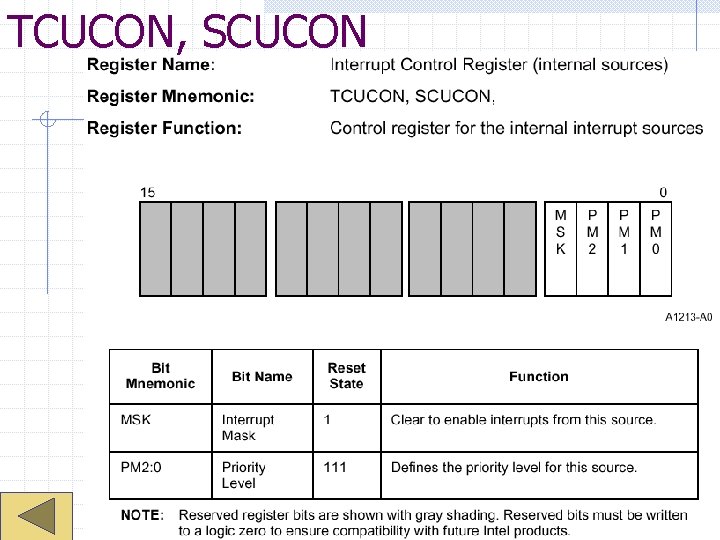

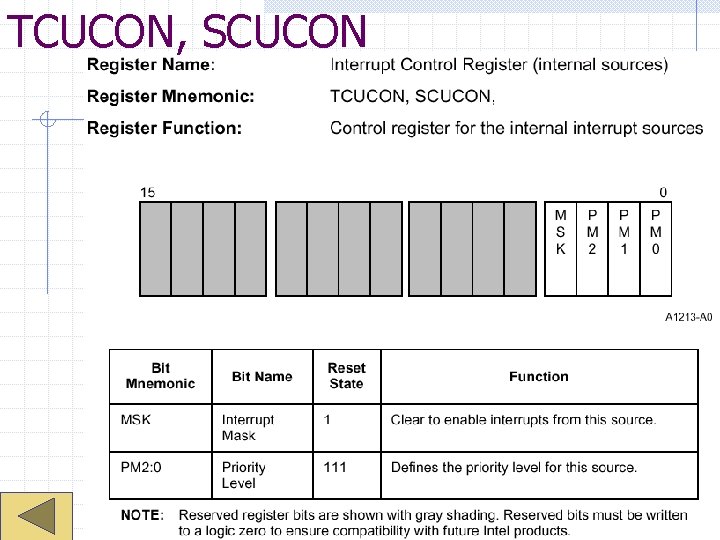

TCUCON, SCUCON

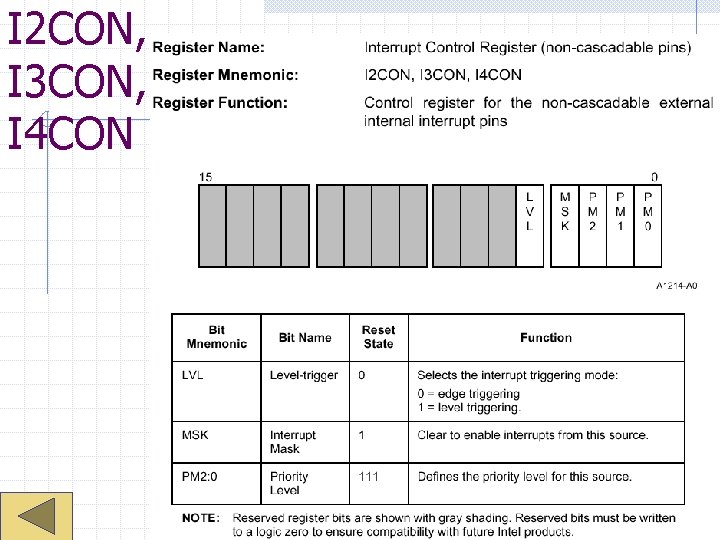

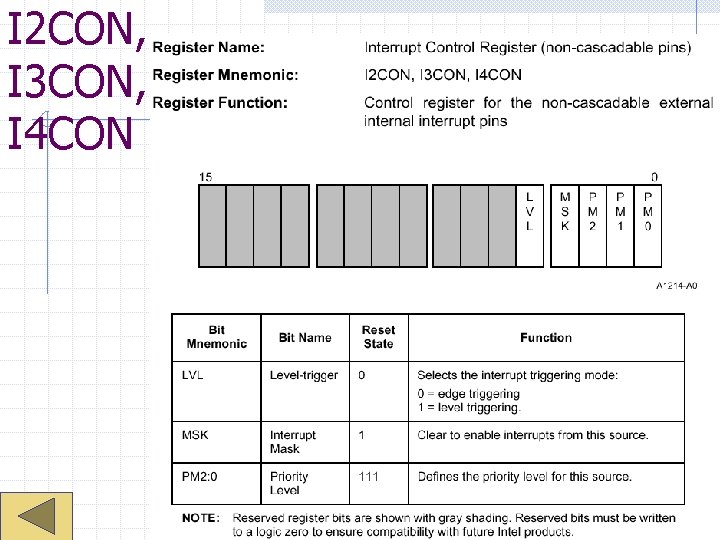

I 2 CON, I 3 CON, I 4 CON

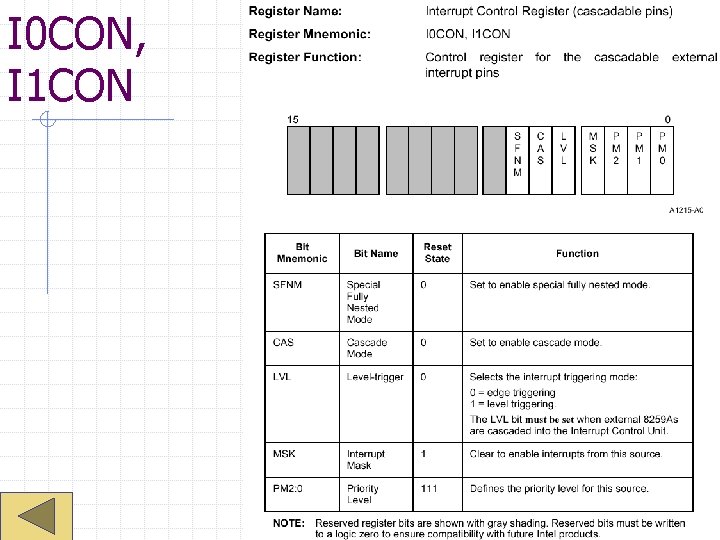

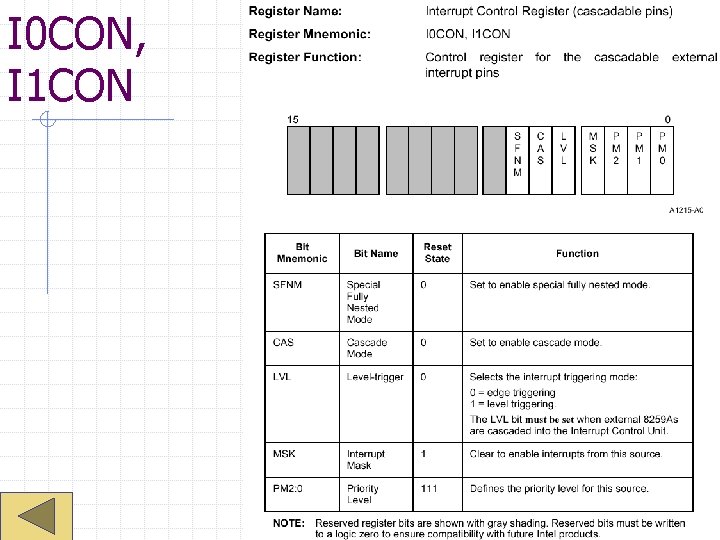

I 0 CON, I 1 CON

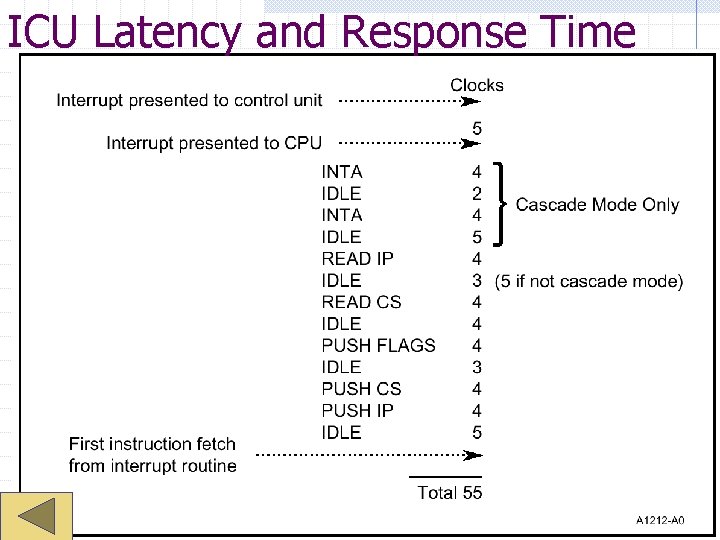

ICU Latency and Response Time

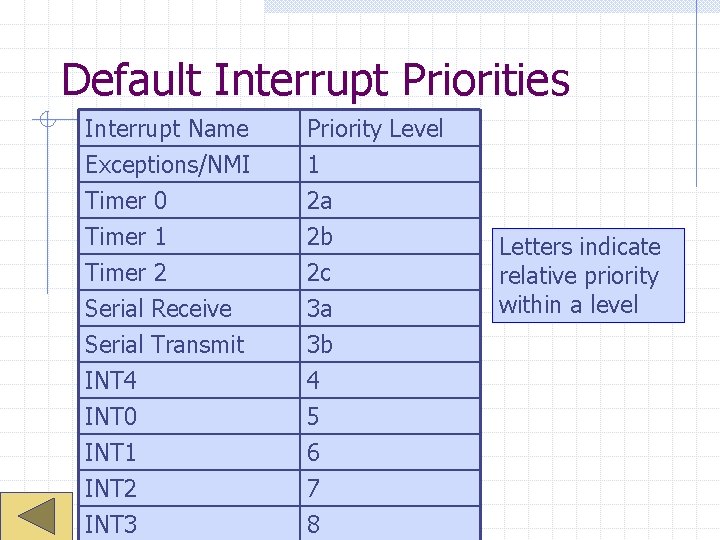

Default Interrupt Priorities Interrupt Name Exceptions/NMI Timer 0 Timer 1 Priority Level 1 2 a 2 b Timer 2 Serial Receive Serial Transmit INT 4 INT 0 INT 1 INT 2 2 c 3 a 3 b 4 5 6 7 INT 3 8 Letters indicate relative priority within a level

ICU Block Diagram

INTA Bus Cycles