ECAL Upgrade per HLLHC Contributo Italiano Stefano Argir

ECAL Upgrade per HL-LHC Contributo Italiano Stefano Argirò per ECAL Italia 1

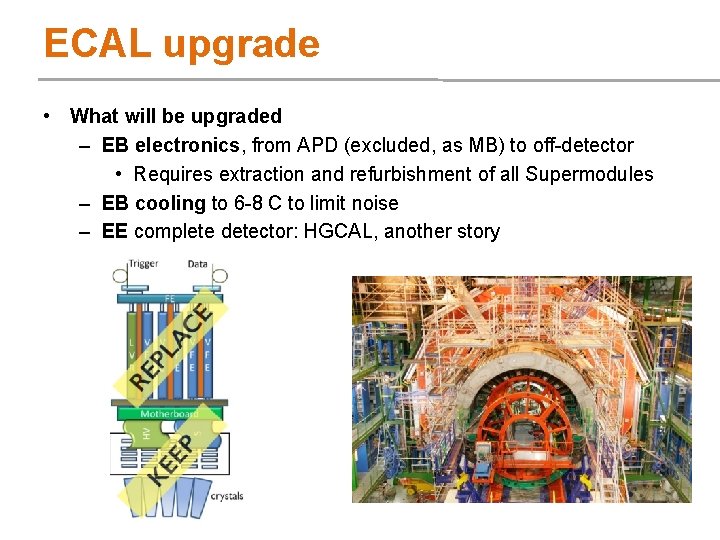

ECAL upgrade • What will be upgraded – EB electronics, from APD (excluded, as MB) to off-detector • Requires extraction and refurbishment of all Supermodules – EB cooling to 6 -8 C to limit noise – EE complete detector: HGCAL, another story

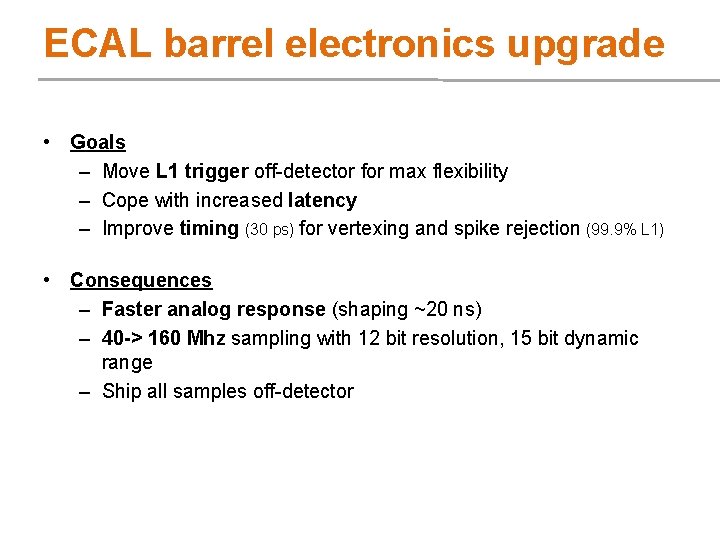

ECAL barrel electronics upgrade • Goals – Move L 1 trigger off-detector for max flexibility – Cope with increased latency – Improve timing (30 ps) for vertexing and spike rejection (99. 9% L 1) • Consequences – Faster analog response (shaping ~20 ns) – 40 -> 160 Mhz sampling with 12 bit resolution, 15 bit dynamic range – Ship all samples off-detector

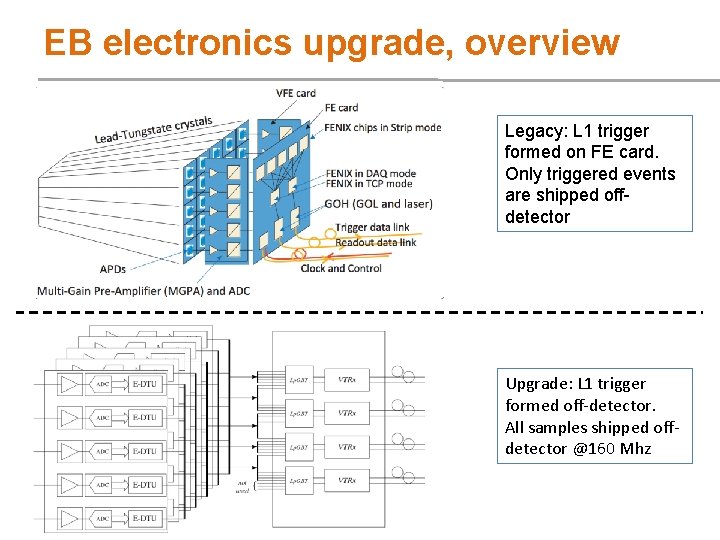

EB electronics upgrade, overview Legacy: L 1 trigger formed on FE card. Only triggered events are shipped offdetector Upgrade: L 1 trigger formed off-detector. All samples shipped offdetector @160 Mhz

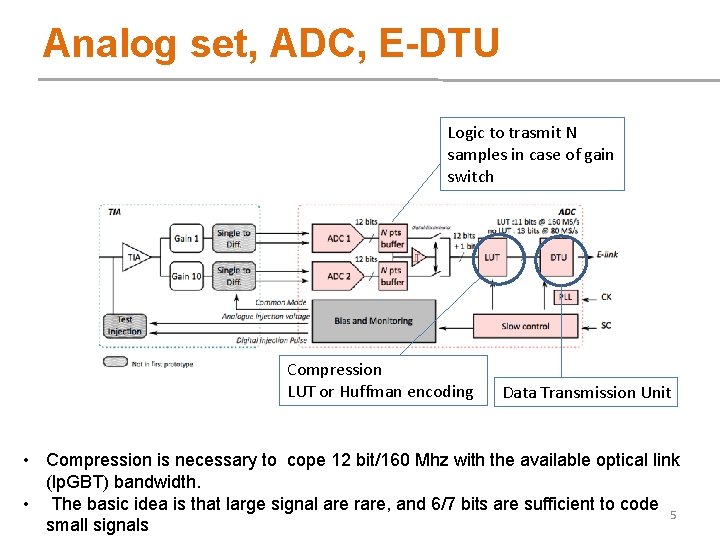

Analog set, ADC, E-DTU Logic to trasmit N samples in case of gain switch Compression LUT or Huffman encoding Data Transmission Unit • Compression is necessary to cope 12 bit/160 Mhz with the available optical link (lp. GBT) bandwidth. • The basic idea is that large signal are rare, and 6/7 bits are sufficient to code 5 small signals

Analog set, ADC The new readout concept has been extensively validated at H 4 testbeam this summer, using discrete components. Testbeams are italian-driven at large A protype TIA Asic 130 nm has been submitted in fall 2016 6

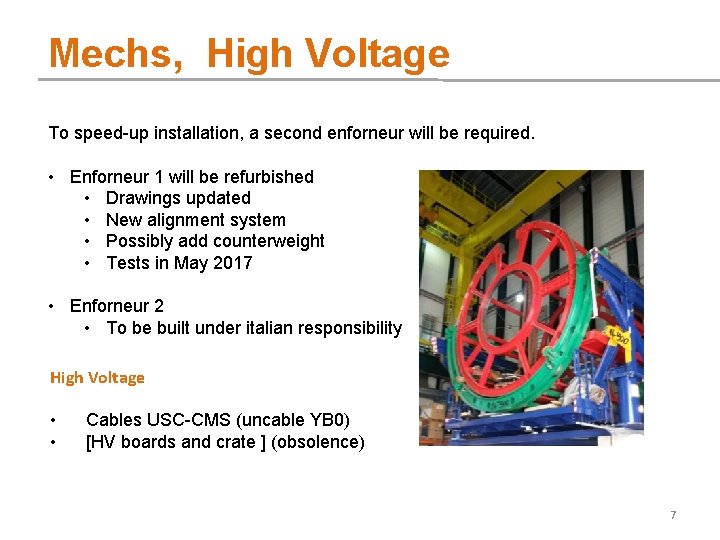

Mechs, High Voltage To speed-up installation, a second enforneur will be required. • Enforneur 1 will be refurbished • Drawings updated • New alignment system • Possibly add counterweight • Tests in May 2017 • Enforneur 2 • To be built under italian responsibility High Voltage • • Cables USC-CMS (uncable YB 0) [HV boards and crate ] (obsolence) 7

Italian Involvement, summary • Roma: nuovo Enforneur, HV • Torino: E-DTU design, integration with ADC, testbed. Prototype Asic in Q 4 2017. • Mi, To, Ts, Rm : performance studies, simulation, testbeam validation

Extras

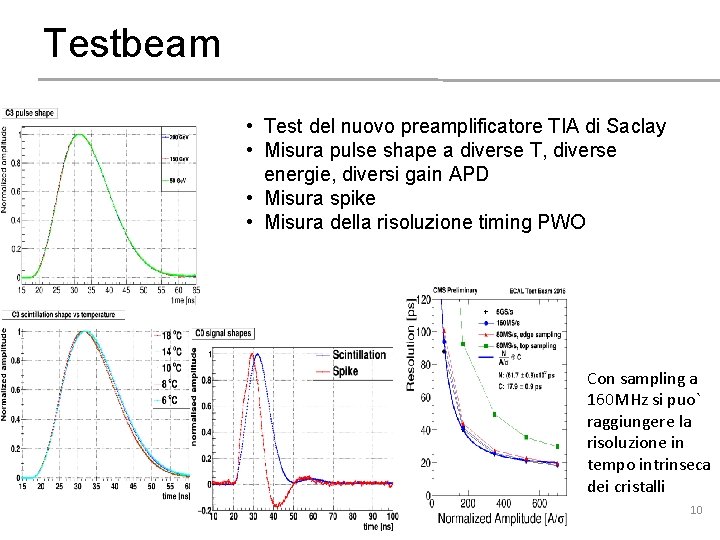

Testbeam • Test del nuovo preamplificatore TIA di Saclay • Misura pulse shape a diverse T, diverse energie, diversi gain APD • Misura spike • Misura della risoluzione timing PWO Con sampling a 160 MHz si puo` raggiungere la risoluzione in tempo intrinseca dei cristalli 10

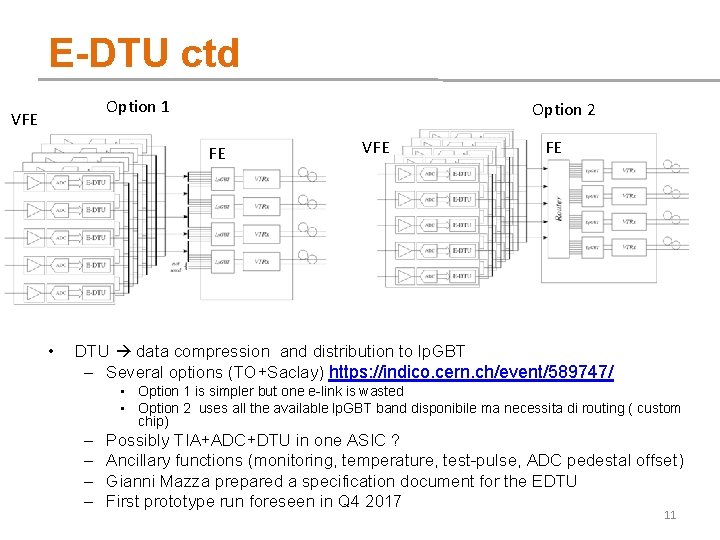

E-DTU ctd Option 1 VFE Option 2 FE • VFE FE DTU data compression and distribution to lp. GBT – Several options (TO+Saclay) https: //indico. cern. ch/event/589747/ • Option 1 is simpler but one e-link is wasted • Option 2 uses all the available lp. GBT band disponibile ma necessita di routing ( custom chip) – – Possibly TIA+ADC+DTU in one ASIC ? Ancillary functions (monitoring, temperature, test-pulse, ADC pedestal offset) Gianni Mazza prepared a specification document for the EDTU First prototype run foreseen in Q 4 2017 11

- Slides: 11