ECal Readout Boards 8 Boards total Design Fabrication

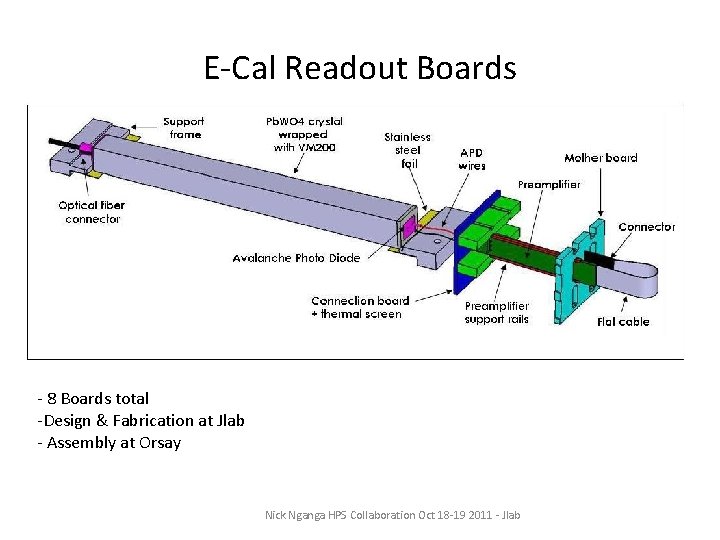

E-Cal Readout Boards - 8 Boards total -Design & Fabrication at Jlab - Assembly at Orsay Nick Nganga HPS Collaboration Oct 18 -19 2011 - Jlab

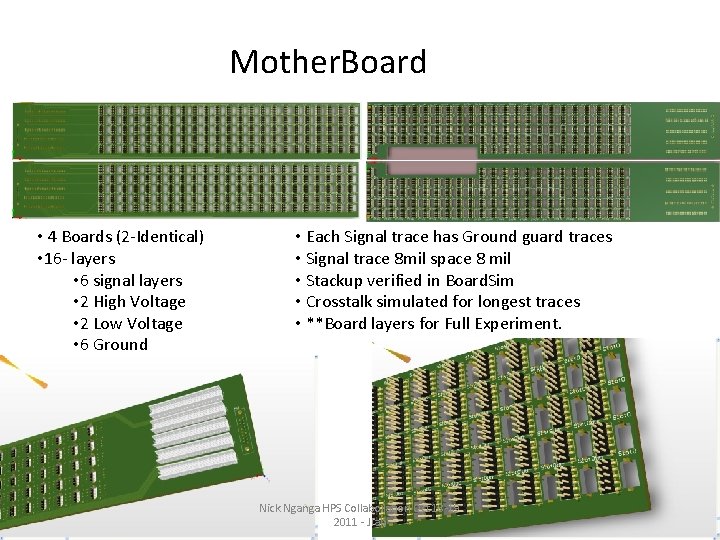

Mother. Board • 4 Boards (2 -Identical) • 16 - layers • 6 signal layers • 2 High Voltage • 2 Low Voltage • 6 Ground • Each Signal trace has Ground guard traces • Signal trace 8 mil space 8 mil • Stackup verified in Board. Sim • Crosstalk simulated for longest traces • **Board layers for Full Experiment. Nick Nganga HPS Collaboration Oct 18 -19 2011 - Jlab

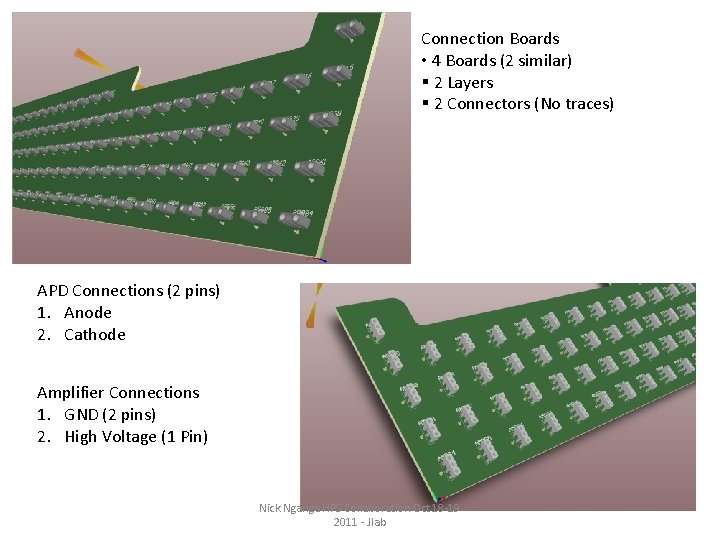

Connection Boards • 4 Boards (2 similar) § 2 Layers § 2 Connectors (No traces) APD Connections (2 pins) 1. Anode 2. Cathode Amplifier Connections 1. GND (2 pins) 2. High Voltage (1 Pin) Nick Nganga HPS Collaboration Oct 18 -19 2011 - Jlab

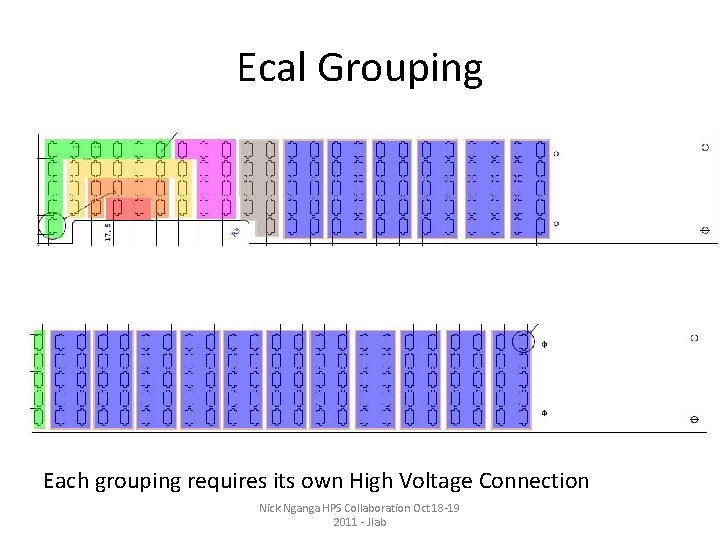

Ecal Grouping Each grouping requires its own High Voltage Connection Nick Nganga HPS Collaboration Oct 18 -19 2011 - Jlab

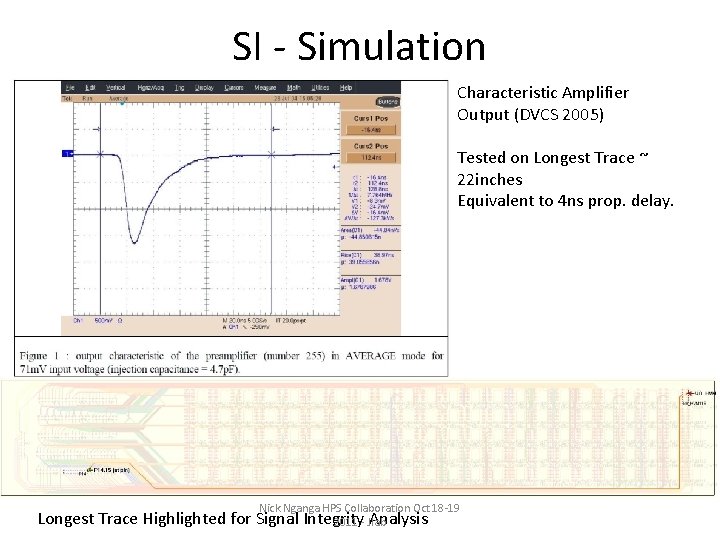

SI - Simulation Characteristic Amplifier Output (DVCS 2005) Tested on Longest Trace ~ 22 inches Equivalent to 4 ns prop. delay. Longest Trace Highlighted for Nick Nganga HPS Collaboration Oct 18 -19 Signal Integrity Analysis 2011 - Jlab

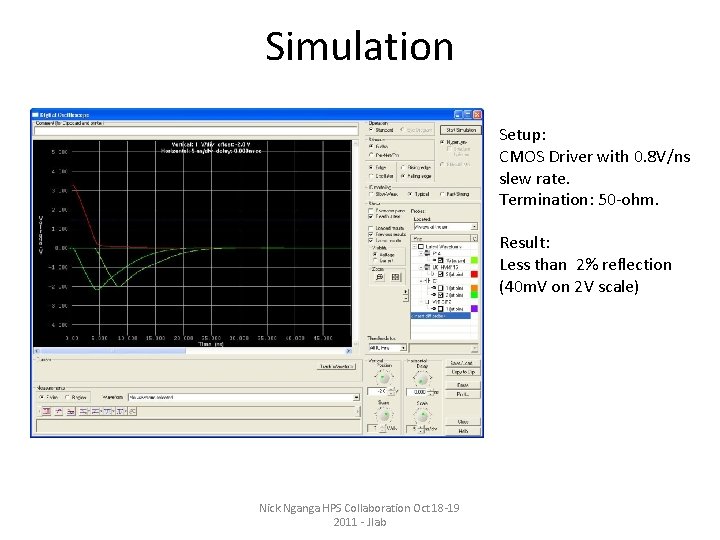

Simulation Setup: CMOS Driver with 0. 8 V/ns slew rate. Termination: 50 -ohm. Result: Less than 2% reflection (40 m. V on 2 V scale) Nick Nganga HPS Collaboration Oct 18 -19 2011 - Jlab

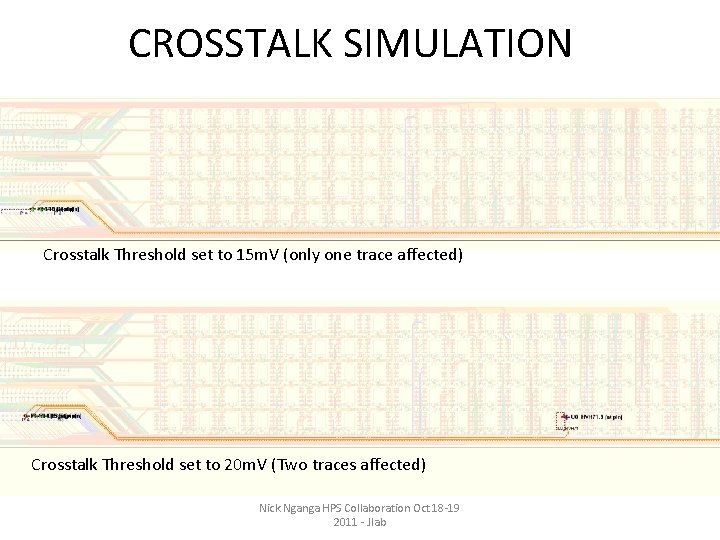

CROSSTALK SIMULATION Crosstalk Threshold set to 15 m. V (only one trace affected) Crosstalk Threshold set to 20 m. V (Two traces affected) Nick Nganga HPS Collaboration Oct 18 -19 2011 - Jlab

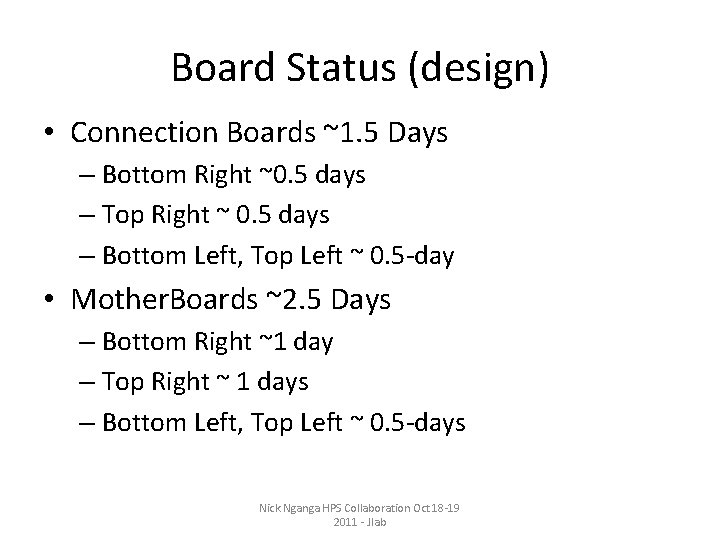

Board Status (design) • Connection Boards ~1. 5 Days – Bottom Right ~0. 5 days – Top Right ~ 0. 5 days – Bottom Left, Top Left ~ 0. 5 -day • Mother. Boards ~2. 5 Days – Bottom Right ~1 day – Top Right ~ 1 days – Bottom Left, Top Left ~ 0. 5 -days Nick Nganga HPS Collaboration Oct 18 -19 2011 - Jlab

- Slides: 8