DYNAMIC SYNCHRONIZER FLIPFLOP PERFORMANCE IN FINFET TECHNOLOGIES NOCS

- Slides: 18

DYNAMIC SYNCHRONIZER FLIP-FLOP PERFORMANCE IN FINFET TECHNOLOGIES NOCS 2014 Mark Buckler 1, Arpan Vaidya 2, Xiaobin Liu 2, Wayne Burleson 2, 3 Cornell University 1, University of Mass. Amherst 2, AMD Research 3 September 18, 2014

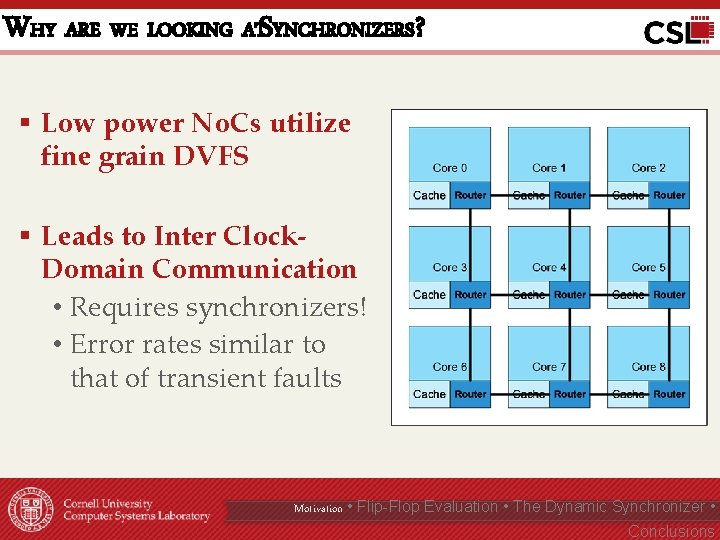

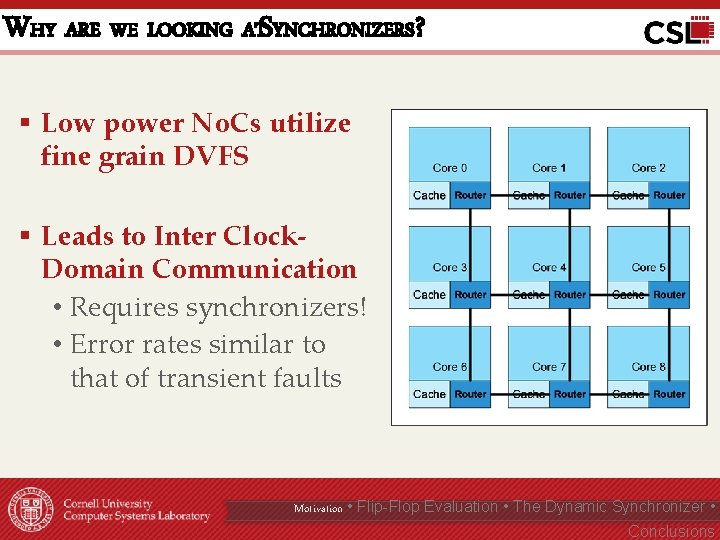

WHY ARE WE LOOKING ATSYNCHRONIZERS? § Low power No. Cs utilize fine grain DVFS § Leads to Inter Clock. Domain Communication • Requires synchronizers! • Error rates similar to that of transient faults Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Page 2 of 35 Conclusions

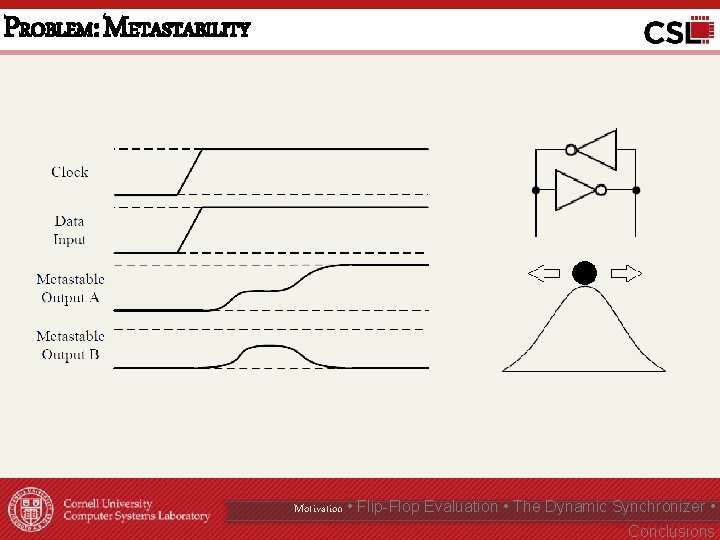

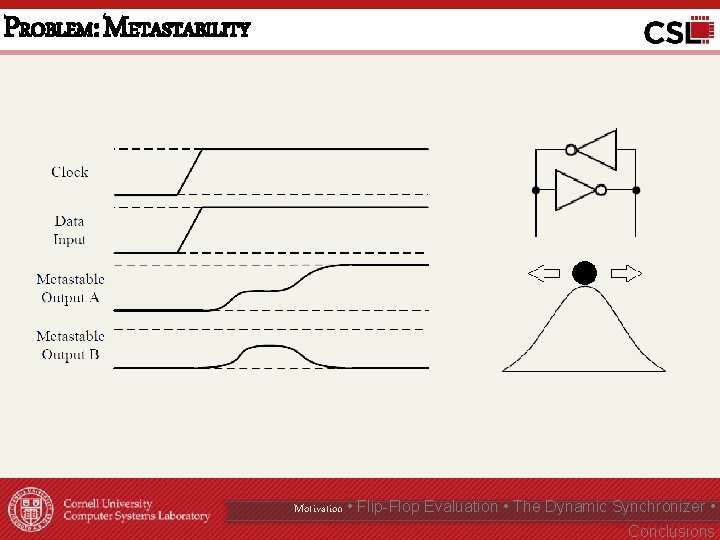

PROBLEM: METASTABILITY Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Page 3 of 35 Conclusions

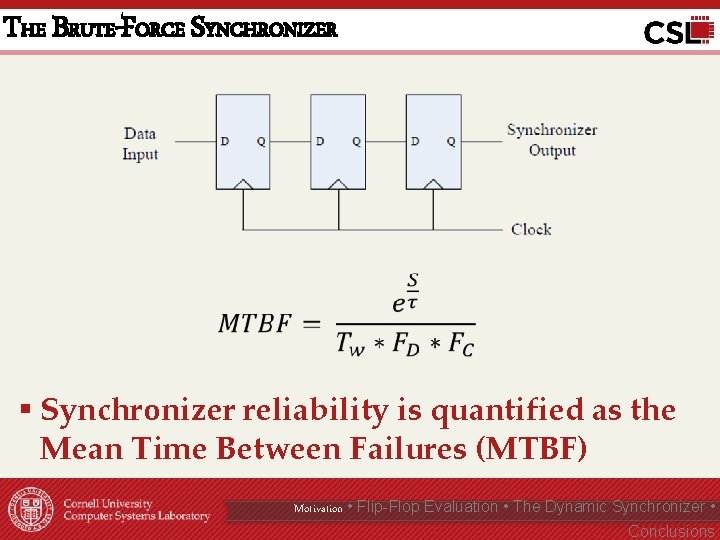

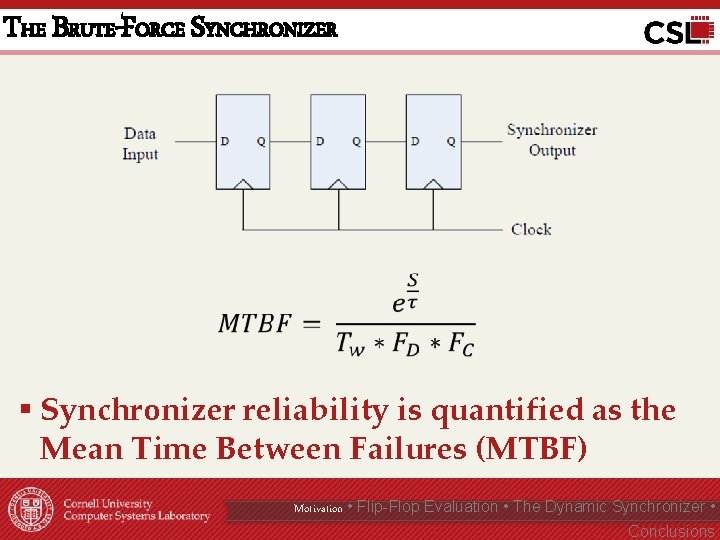

THE BRUTE-FORCE SYNCHRONIZER § Synchronizer reliability is quantified as the Mean Time Between Failures (MTBF) Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Page 4 of 35 Conclusions

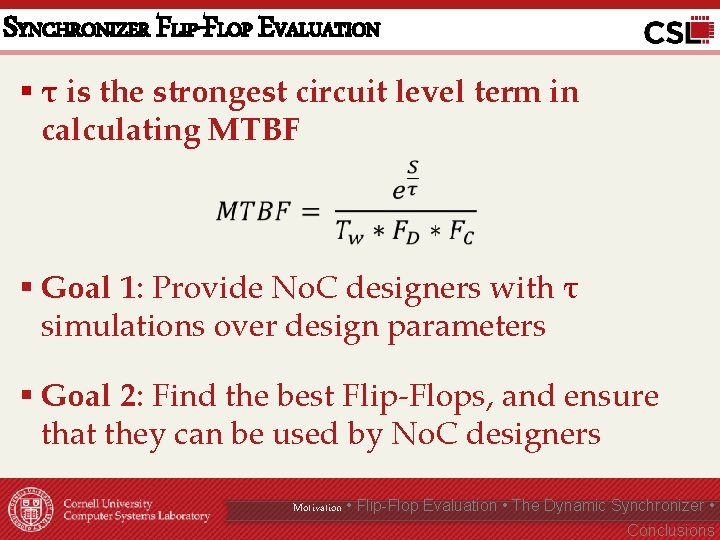

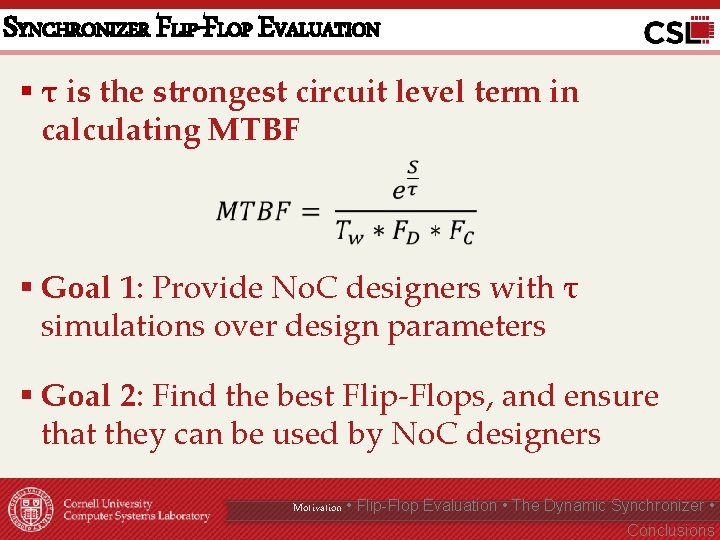

SYNCHRONIZER FLIP-FLOP EVALUATION § τ is the strongest circuit level term in calculating MTBF § Goal 1: Provide No. C designers with τ simulations over design parameters § Goal 2: Find the best Flip-Flops, and ensure that they can be used by No. C designers Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Page 5 of 35 Conclusions

SYNCHRONIZER FLIP-FLOP EVALUATION § Flip-Flops: • Power. PC Flip-Flop • Dynamic Latch Flip-Flop • Psuedo-NMOS Flip-Flop § Technology Nodes • Planar (50 nm and 22 nm) • Fin. FET (20 nm, 10 nm and 7 nm) Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Conclusions Page 6 of 35

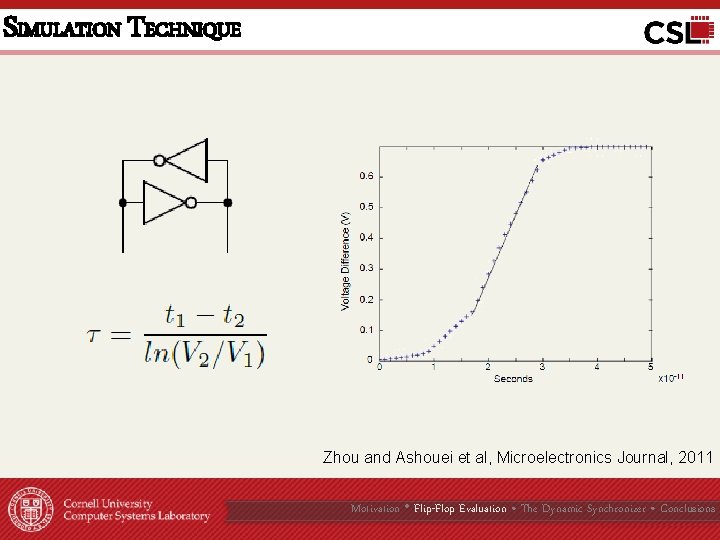

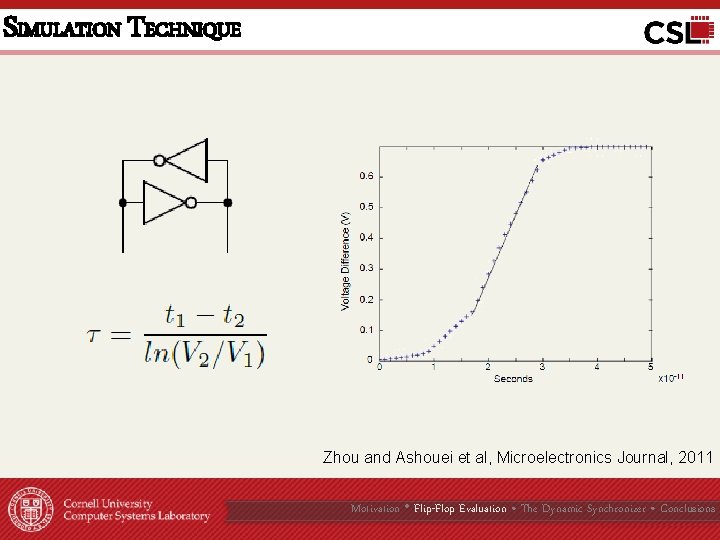

SIMULATION TECHNIQUE Zhou and Ashouei et al, Microelectronics Journal, 2011 Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Conclusions Page 7 of 35

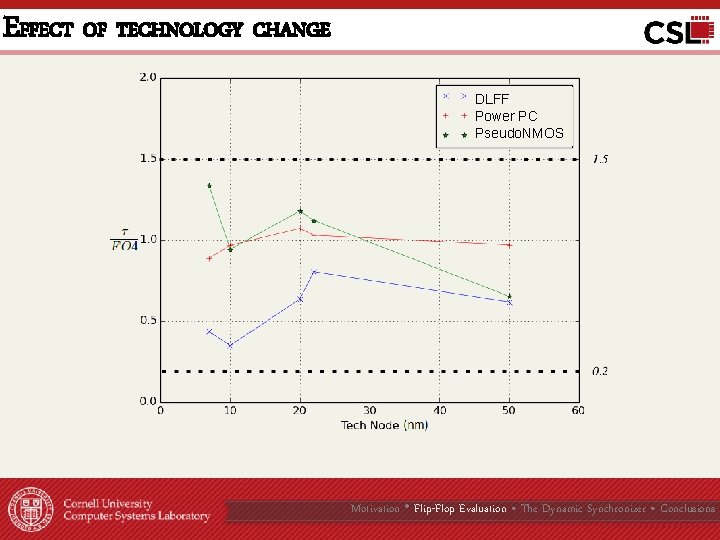

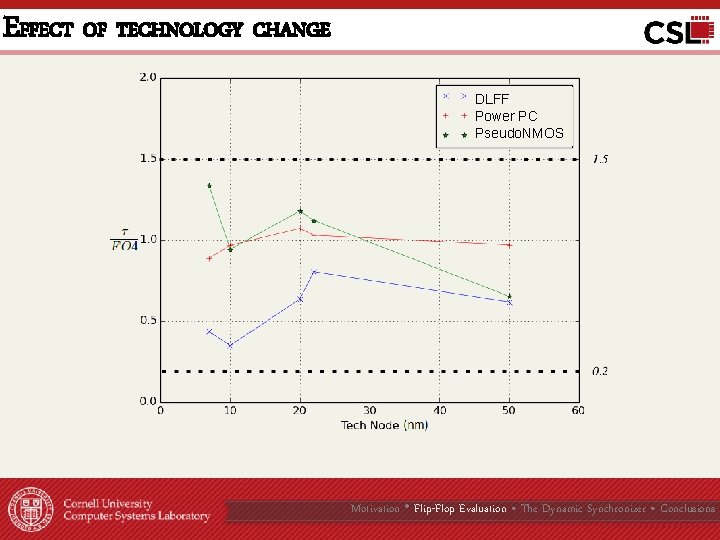

EFFECT OF TECHNOLOGY CHANGE DLFF Power PC Pseudo. NMOS Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Conclusions Page 8 of 35

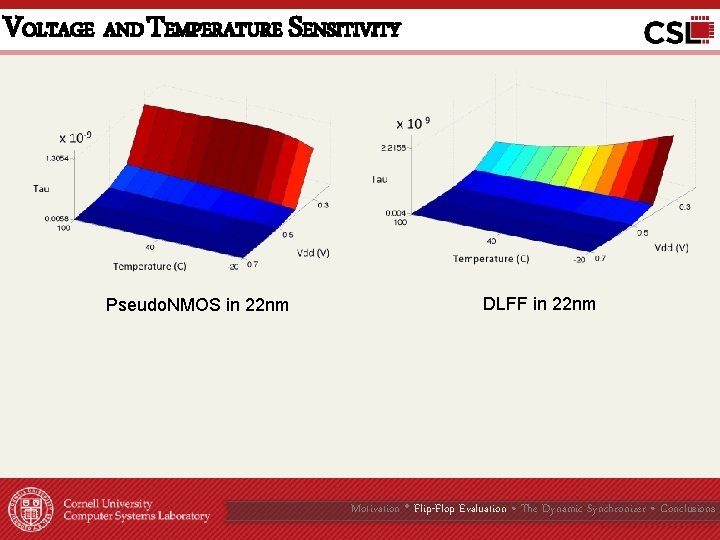

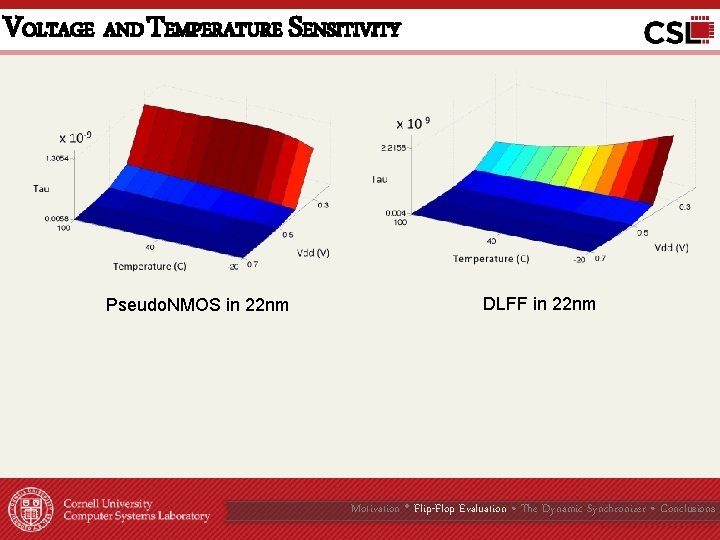

VOLTAGE AND TEMPERATURE SENSITIVITY Pseudo. NMOS in 22 nm DLFF in 22 nm Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Conclusions Page 9 of 35

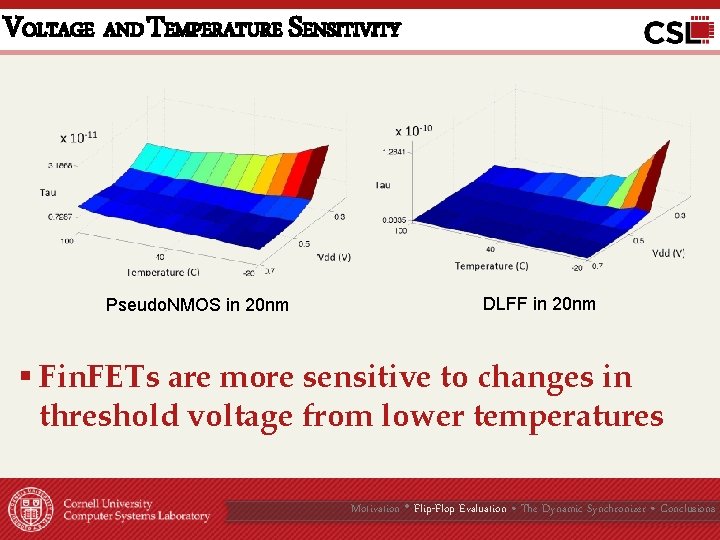

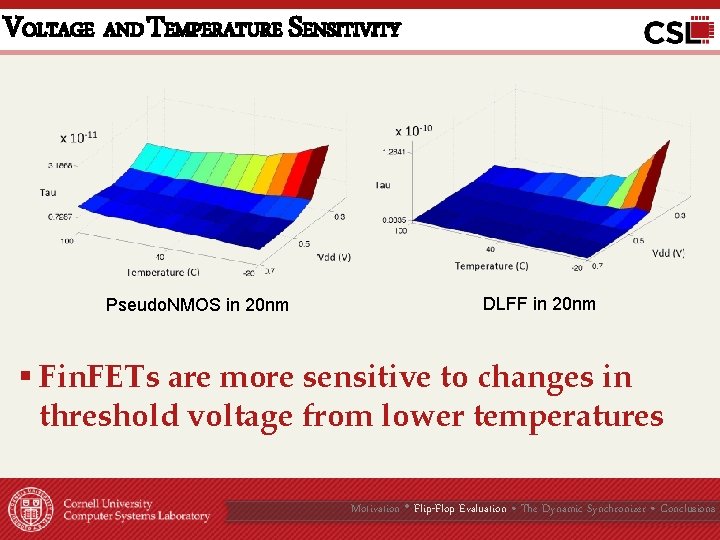

VOLTAGE AND TEMPERATURE SENSITIVITY Pseudo. NMOS in 20 nm DLFF in 20 nm § Fin. FETs are more sensitive to changes in threshold voltage from lower temperatures Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Conclusions Page 10 of 35

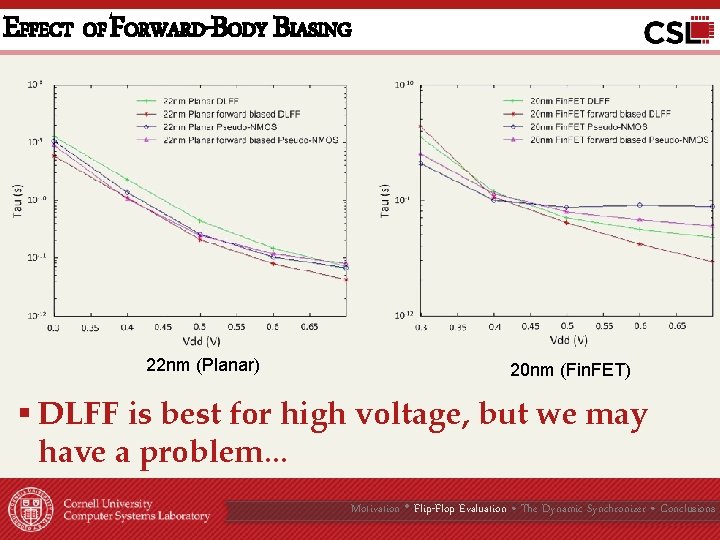

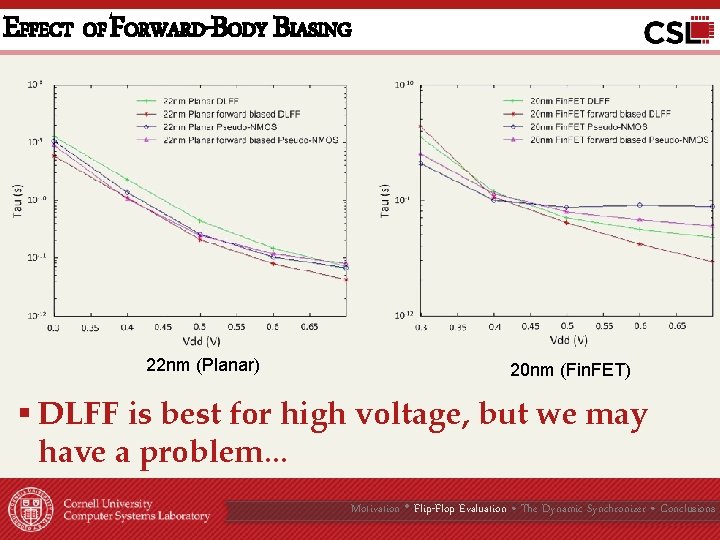

EFFECT OF FORWARD-BODY BIASING 22 nm (Planar) 20 nm (Fin. FET) § DLFF is best for high voltage, but we may have a problem. . . Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Conclusions Page 11 of 35

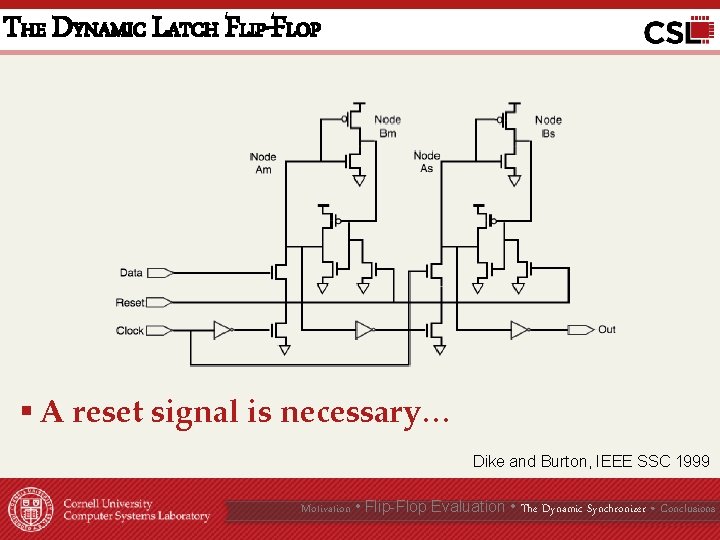

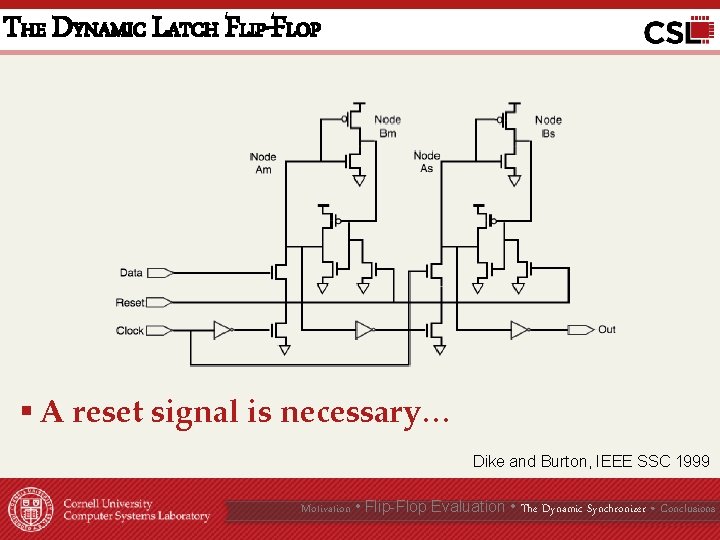

THE DYNAMIC LATCH FLIP-FLOP § A reset signal is necessary… Dike and Burton, IEEE SSC 1999 Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Conclusions Page 12 of 35

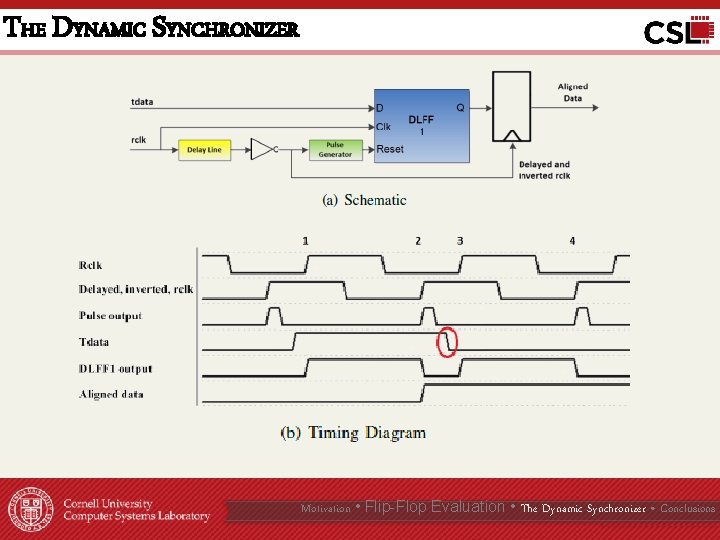

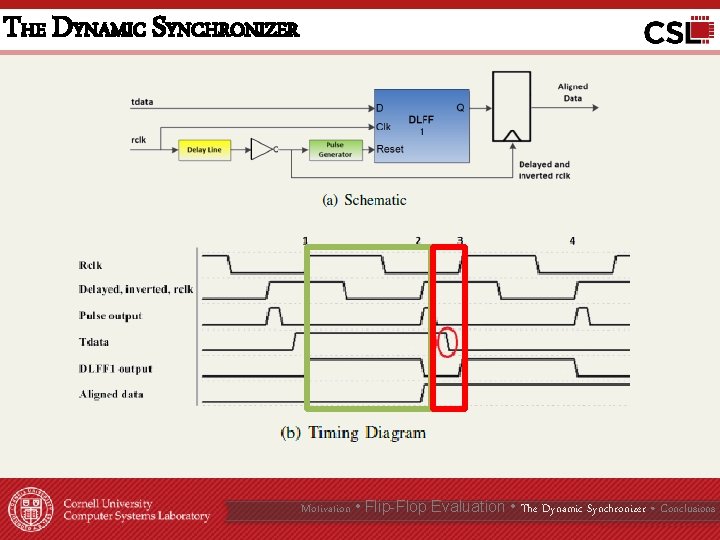

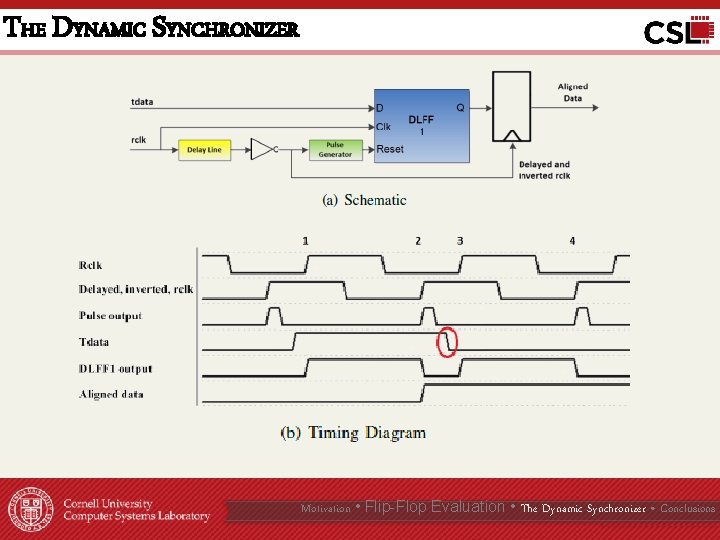

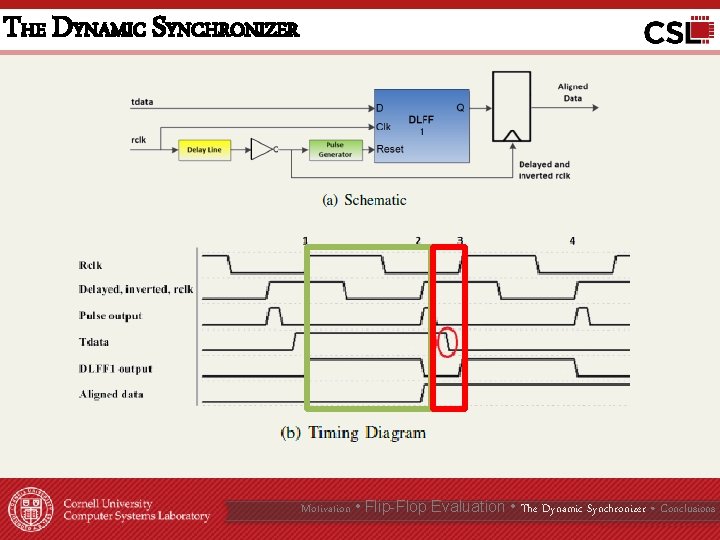

THE DYNAMIC SYNCHRONIZER Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Conclusions Page 13 of 35

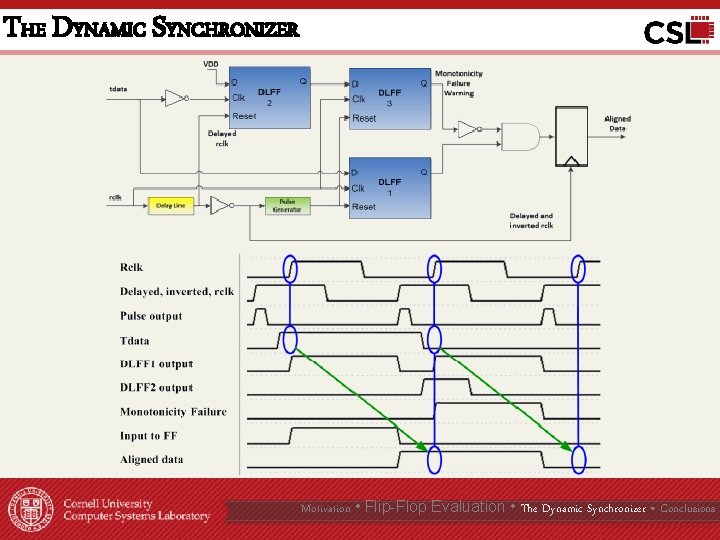

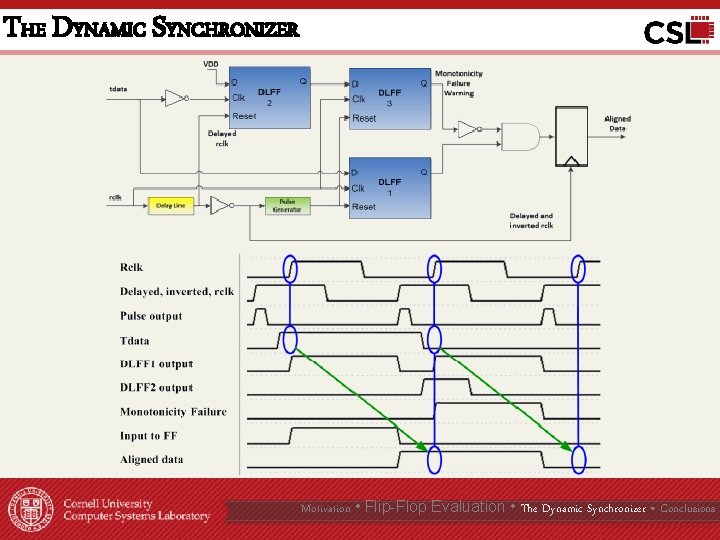

THE DYNAMIC SYNCHRONIZER Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Conclusions Page 14 of 35

THE DYNAMIC SYNCHRONIZER Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Conclusions Page 15 of 35

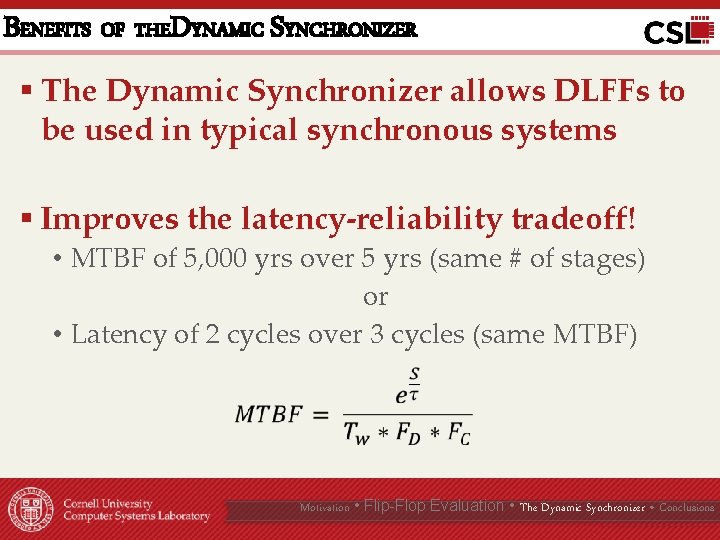

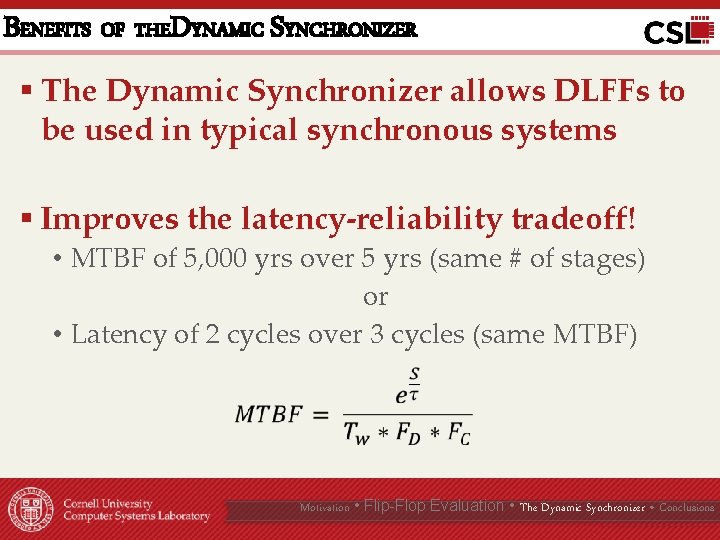

BENEFITS OF THEDYNAMIC SYNCHRONIZER § The Dynamic Synchronizer allows DLFFs to be used in typical synchronous systems § Improves the latency-reliability tradeoff! • MTBF of 5, 000 yrs over 5 yrs (same # of stages) or • Latency of 2 cycles over 3 cycles (same MTBF) Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Conclusions Page 16 of 35

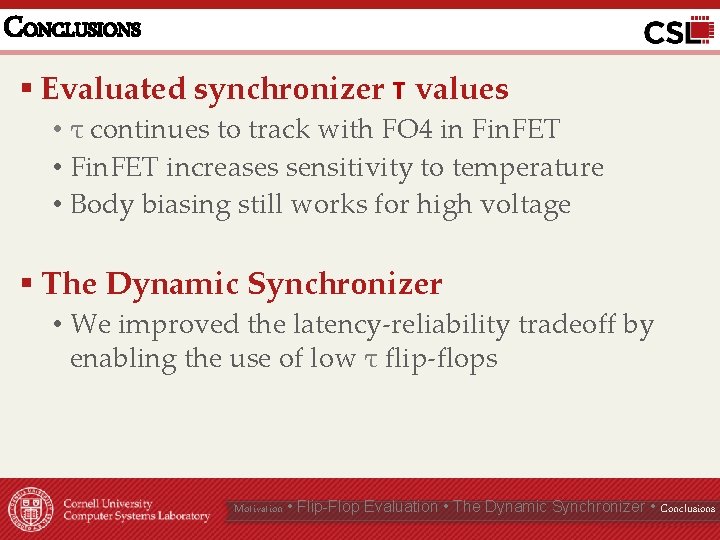

CONCLUSIONS § Evaluated synchronizer τ values • τ continues to track with FO 4 in Fin. FET • Fin. FET increases sensitivity to temperature • Body biasing still works for high voltage § The Dynamic Synchronizer • We improved the latency-reliability tradeoff by enabling the use of low τ flip-flops Motivation • Flip-Flop Evaluation • The Dynamic Synchronizer • Conclusions Page 17 of 35