Dynamic power supply design for highefficiency wireless transmitters

- Slides: 1

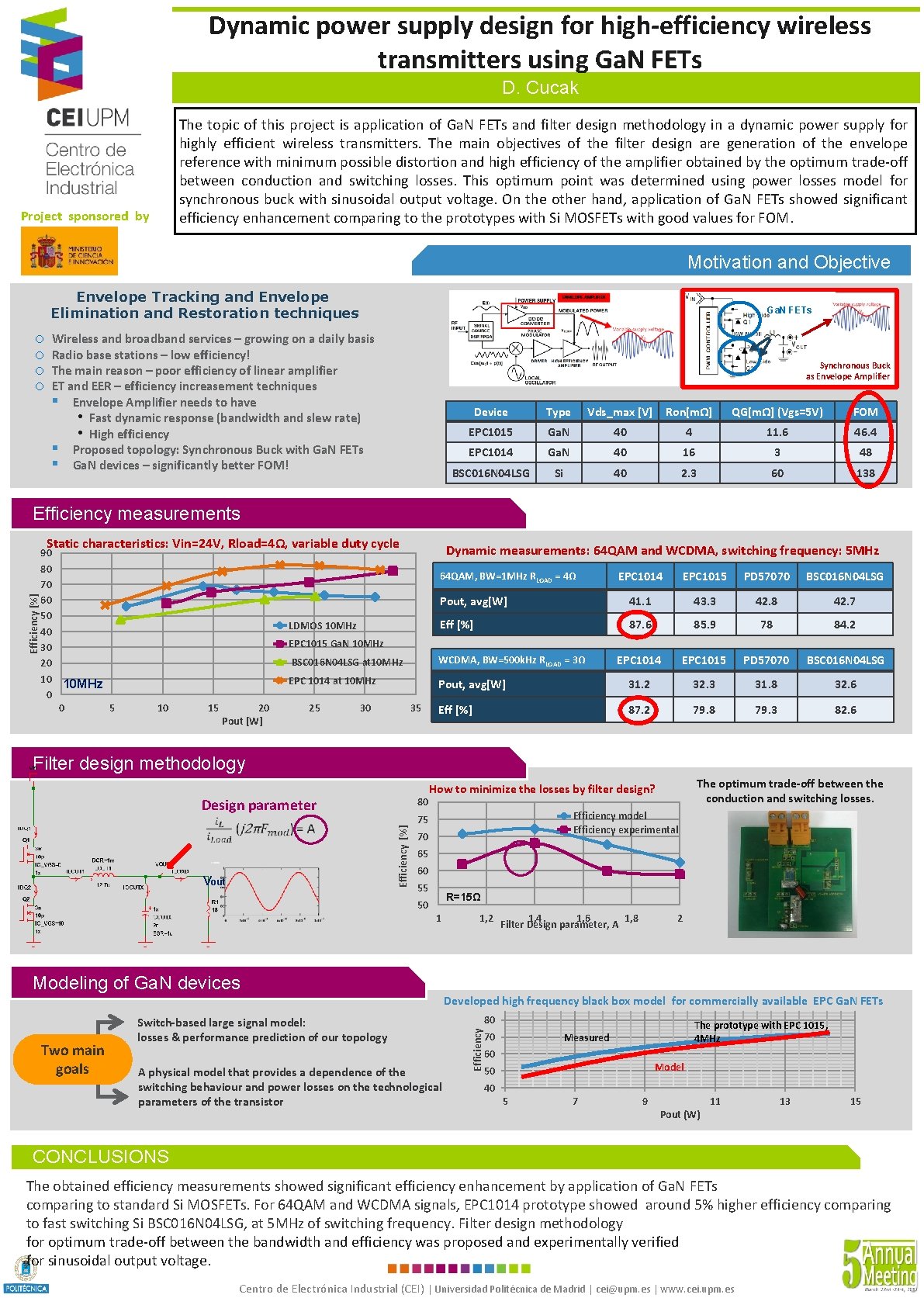

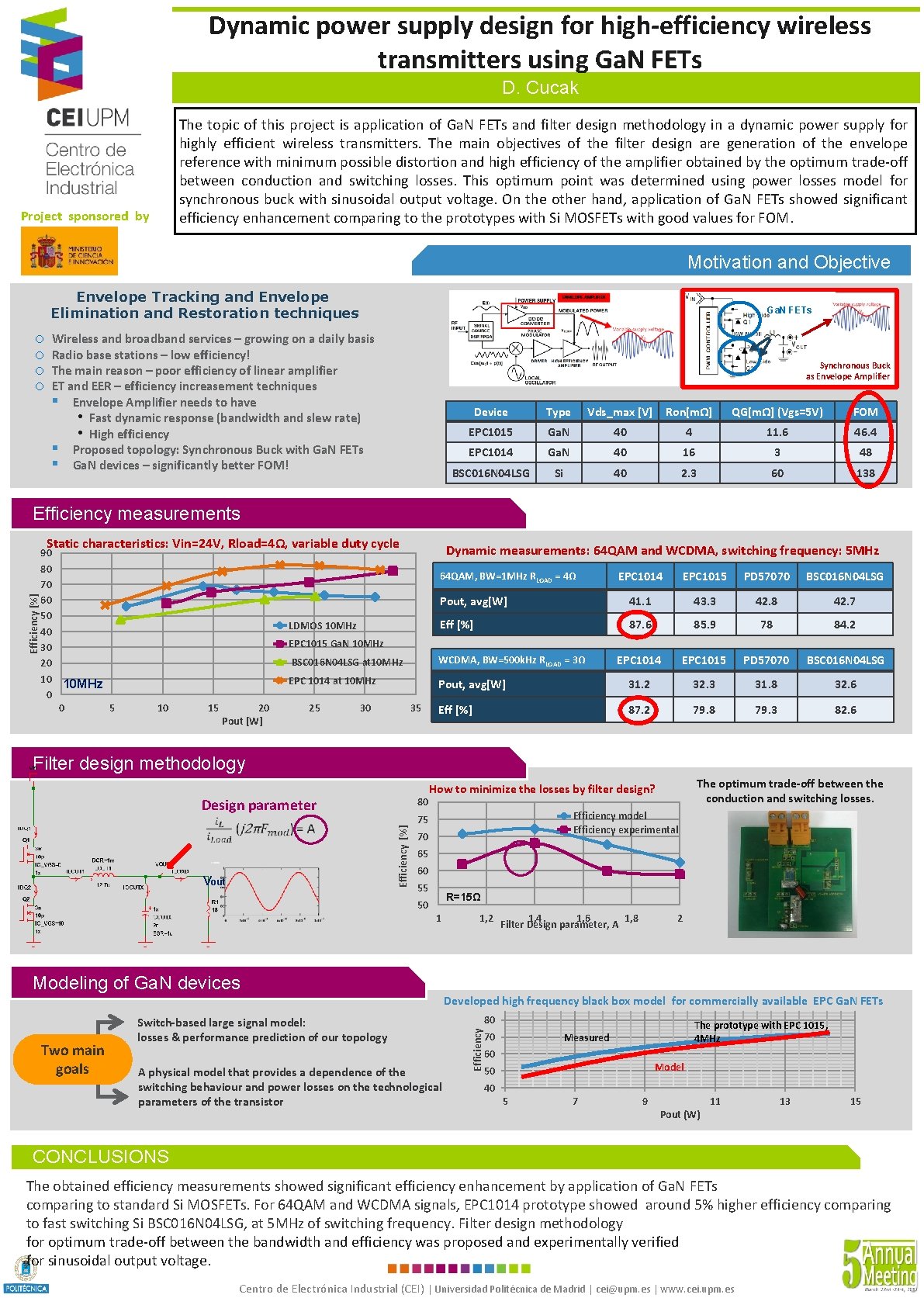

Dynamic power supply design for high-efficiency wireless transmitters using Ga. N FETs D. Cucak The topic of this project is application of Ga. N FETs and filter design methodology in a dynamic power supply for highly efficient wireless transmitters. The main objectives of the filter design are generation of the envelope reference with minimum possible distortion and high efficiency of the amplifier obtained by the optimum trade-off between conduction and switching losses. This optimum point was determined using power losses model for synchronous buck with sinusoidal output voltage. On the other hand, application of Ga. N FETs showed significant efficiency enhancement comparing to the prototypes with Si MOSFETs with good values for FOM. Project sponsored by Motivation and Objective Envelope Tracking and Envelope Elimination and Restoration techniques o o Ga. N FETs Wireless and broadband services – growing on a daily basis Radio base stations – low efficiency! The main reason – poor efficiency of linear amplifier ET and EER – efficiency increasement techniques § Envelope Amplifier needs to have • Fast dynamic response (bandwidth and slew rate) • High efficiency § Proposed topology: Synchronous Buck with Ga. N FETs § Ga. N devices – significantly better FOM! Synchronous Buck as Envelope Amplifier Device Type Vds_max [V] Ron[mΩ] QG[mΩ] (Vgs=5 V) FOM EPC 1015 Ga. N 40 4 11. 6 46. 4 EPC 1014 Ga. N 40 16 3 48 BSC 016 N 04 LSG Si 40 2. 3 60 138 Efficiency measurements Efficiency [%] Static characteristics: Vin=24 V, Rload=4Ω, variable duty cycle 90 80 70 60 50 40 30 20 10 0 Dynamic measurements: 64 QAM and WCDMA, switching frequency: 5 MHz EPC 1014 EPC 1015 PD 57070 BSC 016 N 04 LSG Pout, avg[W] 41. 1 43. 3 42. 8 42. 7 Eff [%] 87. 6 85. 9 78 84. 2 EPC 1014 EPC 1015 PD 57070 BSC 016 N 04 LSG 64 QAM, BW=1 MHz RLOAD = 4Ω LDMOS 10 MHz EPC 1015 Ga. N 10 MHz 0 5 10 15 20 Pout [W] BSC 016 N 04 LSG at 10 MHz WCDMA, BW=500 k. Hz RLOAD = 3Ω EPC 1014 at 10 MHz Pout, avg[W] 31. 2 32. 3 31. 8 32. 6 Eff [%] 87. 2 79. 8 79. 3 82. 6 25 30 35 Filter design methodology Efficiency [%] 80 Vout Efficiency model Efficiency experimental 75 70 65 60 55 R=15Ω 50 1 Modeling of Ga. N devices Two main goals Switch-based large signal model: losses & performance prediction of our topology Modeling of Ga. N devices A physical model that provides a dependence of the switching behaviour and power losses on the technological parameters of the transistor 1, 2 1, 4 1, 6 1, 8 Filter Design parameter, A 2 Developed high frequency black box model for commercially available EPC Ga. N FETs 80 Efficiency Design parameter The optimum trade-off between the conduction and switching losses. How to minimize the losses by filter design? 70 The prototype with EPC 1015, 4 MHz Measured 60 Model 50 40 5 7 9 Pout (W) 11 13 15 CONCLUSIONS The obtained efficiency measurements showed significant efficiency enhancement by application of Ga. N FETs comparing to standard Si MOSFETs. For 64 QAM and WCDMA signals, EPC 1014 prototype showed around 5% higher efficiency comparing to fast switching Si BSC 016 N 04 LSG, at 5 MHz of switching frequency. Filter design methodology for optimum trade-off between the bandwidth and efficiency was proposed and experimentally verified for sinusoidal output voltage. Centro de Electrónica Industrial (CEI) | Universidad Politécnica de Madrid | cei@upm. es | www. cei. upm. es