DualVoltage Supply for Power Reduction ELEC 6970 Low

- Slides: 21

Dual-Voltage Supply for Power Reduction ELEC 6970 – Low Power Design Project Presentation by Muthubalaji Ramkumar December 1, 2005 ELEC 6970 - Project Presentation 1

Problem Statement To Use a dual-supply voltage in order to reduce the power consumption of the 32 x 32 bit integer array multiplier circuit without compromising the overall delay December 1, 2005 ELEC 6970 - Project Presentation 2

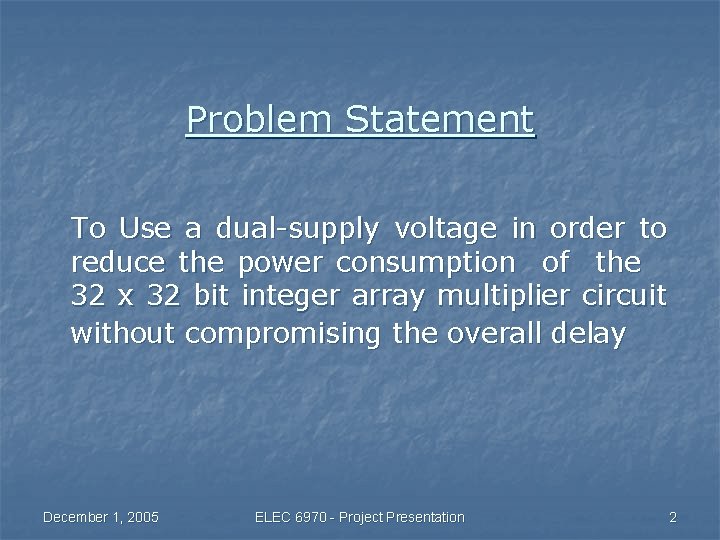

Power and Delay Power → Delay → December 1, 2005 VDD 2 KVDD ─────── (VDD – Vt)α ELEC 6970 - Project Presentation 3

Approach Ø Ø Ø Low Voltage Assignment to as many cells as possible The interconnections in this multiplier circuit makes it difficult Therefore assign Low Voltage Supply to as many gates as possible December 1, 2005 ELEC 6970 - Project Presentation 4

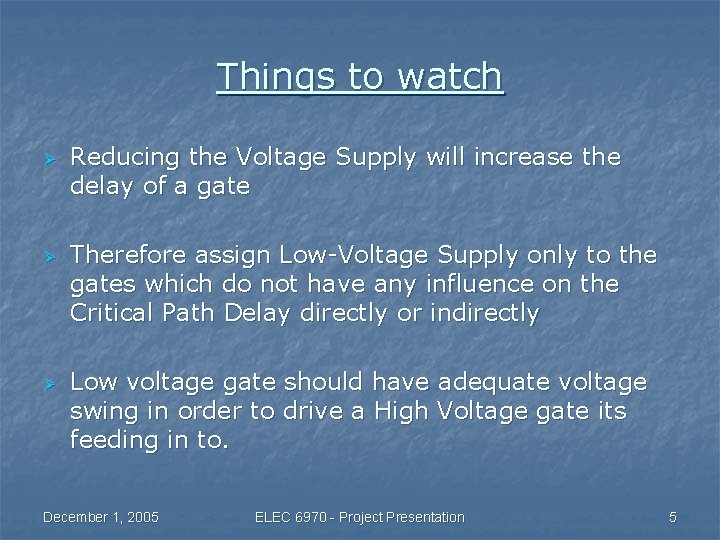

Things to watch Ø Ø Ø Reducing the Voltage Supply will increase the delay of a gate Therefore assign Low-Voltage Supply only to the gates which do not have any influence on the Critical Path Delay directly or indirectly Low voltage gate should have adequate voltage swing in order to drive a High Voltage gate its feeding in to. December 1, 2005 ELEC 6970 - Project Presentation 5

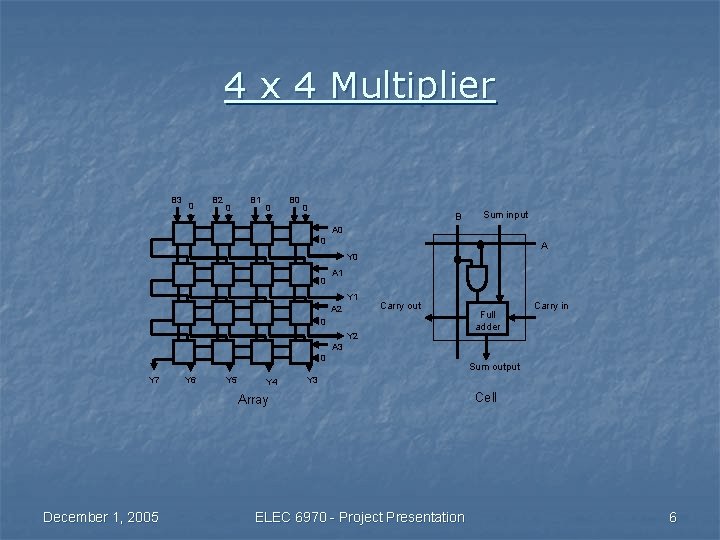

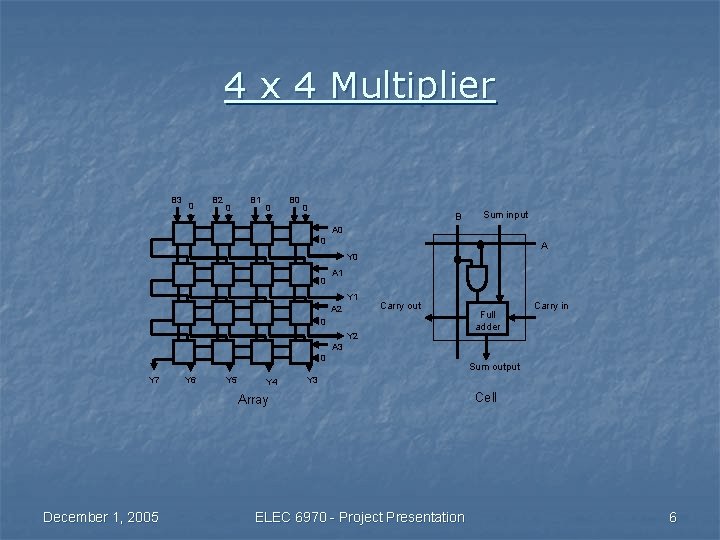

4 x 4 Multiplier B 3 0 B 2 0 B 1 0 B 0 0 B Sum input A 0 0 A Y 0 0 A 1 Y 1 A 2 Carry out 0 Y 2 Full adder Carry in A 3 0 Y 7 Y 6 Y 5 Y 4 Array December 1, 2005 Sum output Y 3 ELEC 6970 - Project Presentation Cell 6

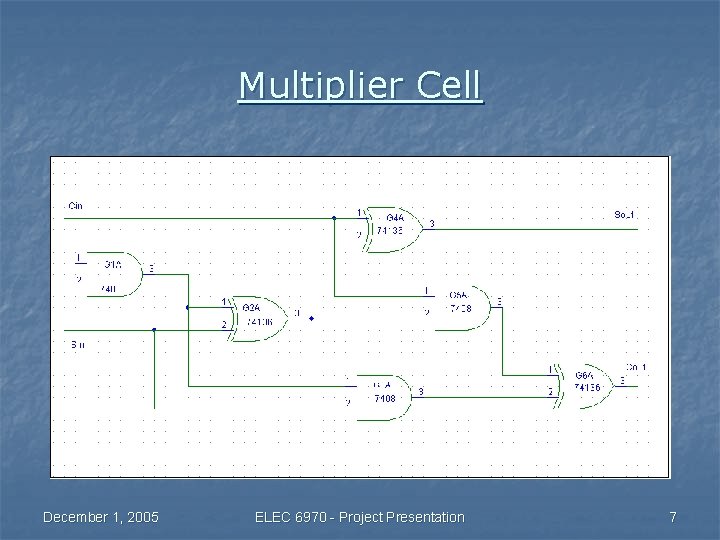

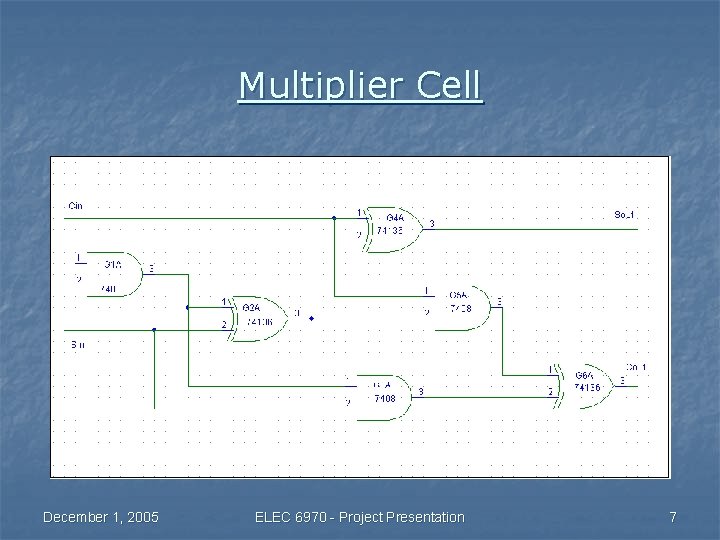

Multiplier Cell December 1, 2005 ELEC 6970 - Project Presentation 7

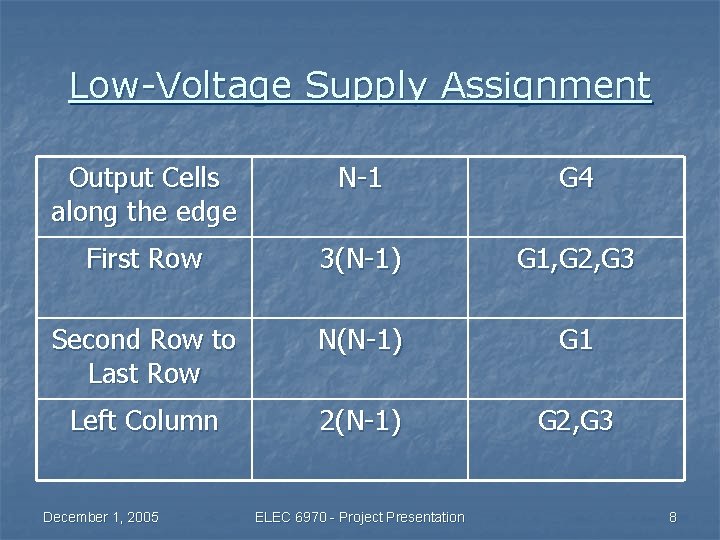

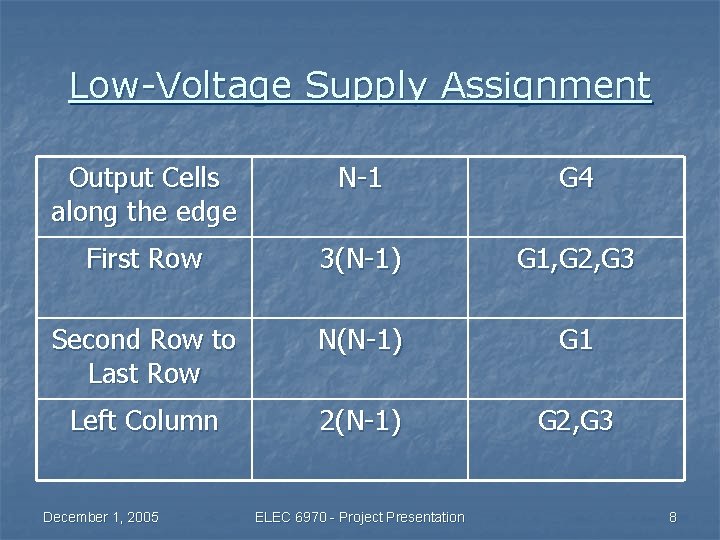

Low-Voltage Supply Assignment Output Cells along the edge N-1 G 4 First Row 3(N-1) G 1, G 2, G 3 Second Row to Last Row N(N-1) G 1 Left Column 2(N-1) G 2, G 3 December 1, 2005 ELEC 6970 - Project Presentation 8

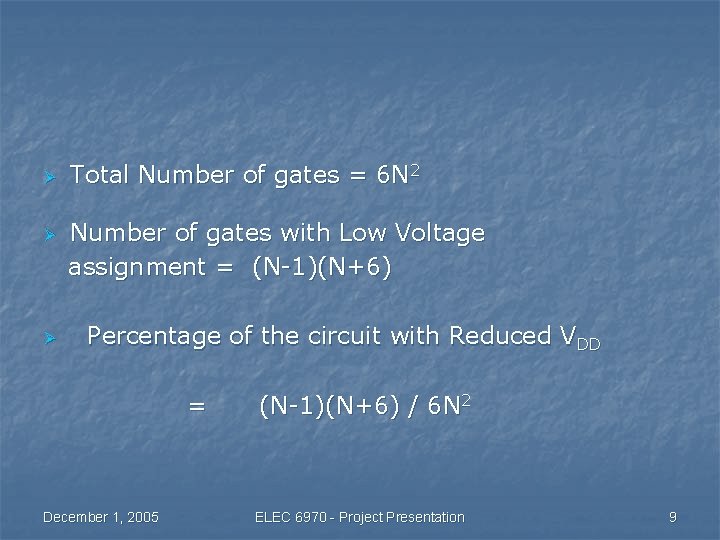

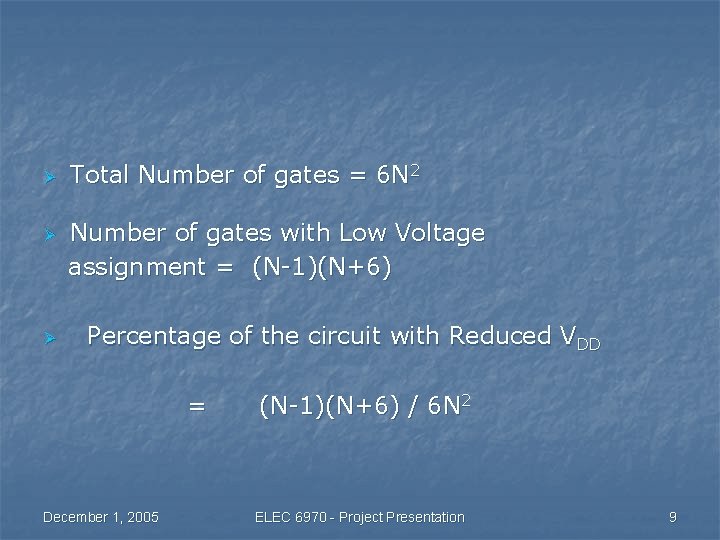

Ø Ø Ø Total Number of gates = 6 N 2 Number of gates with Low Voltage assignment = (N-1)(N+6) Percentage of the circuit with Reduced VDD = December 1, 2005 (N-1)(N+6) / 6 N 2 ELEC 6970 - Project Presentation 9

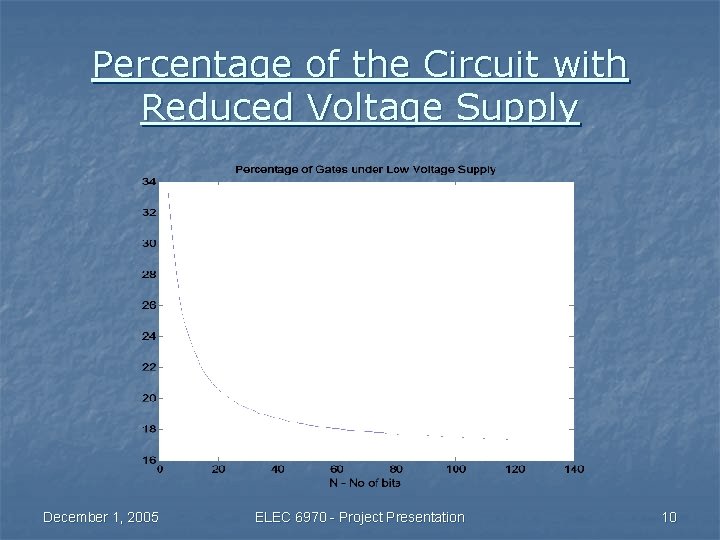

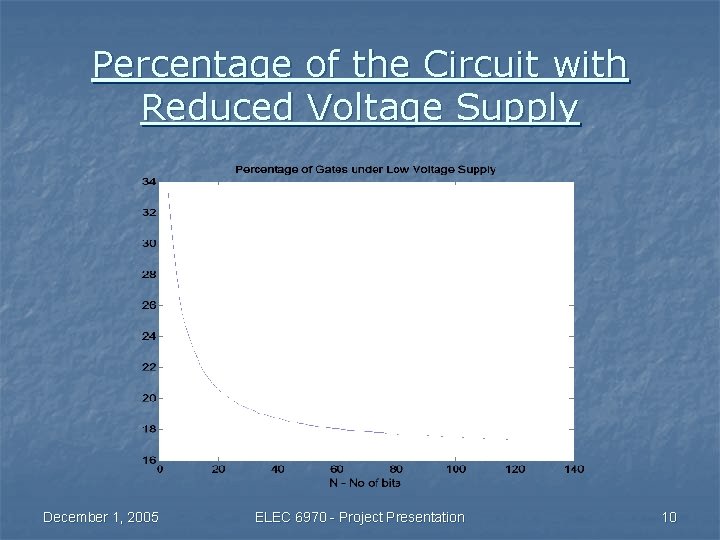

Percentage of the Circuit with Reduced Voltage Supply December 1, 2005 ELEC 6970 - Project Presentation 10

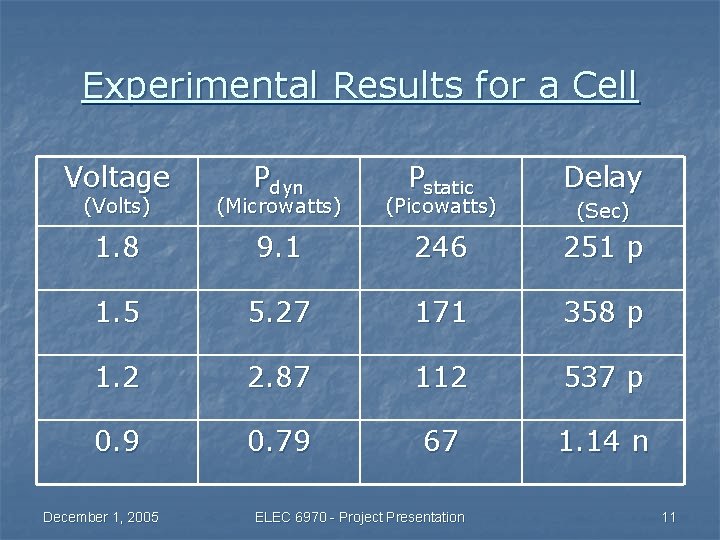

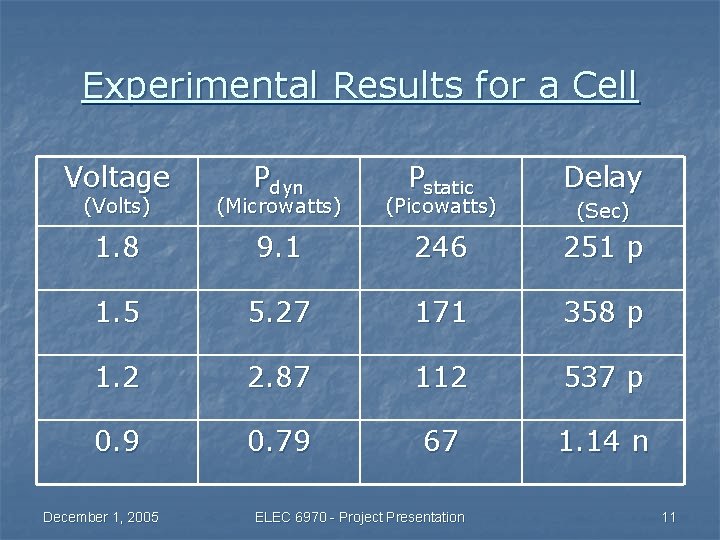

Experimental Results for a Cell Voltage Pdyn Pstatic Delay (Volts) (Microwatts) (Picowatts) 1. 8 9. 1 246 251 p 1. 5 5. 27 171 358 p 1. 2 2. 87 112 537 p 0. 9 0. 79 67 1. 14 n December 1, 2005 ELEC 6970 - Project Presentation (Sec) 11

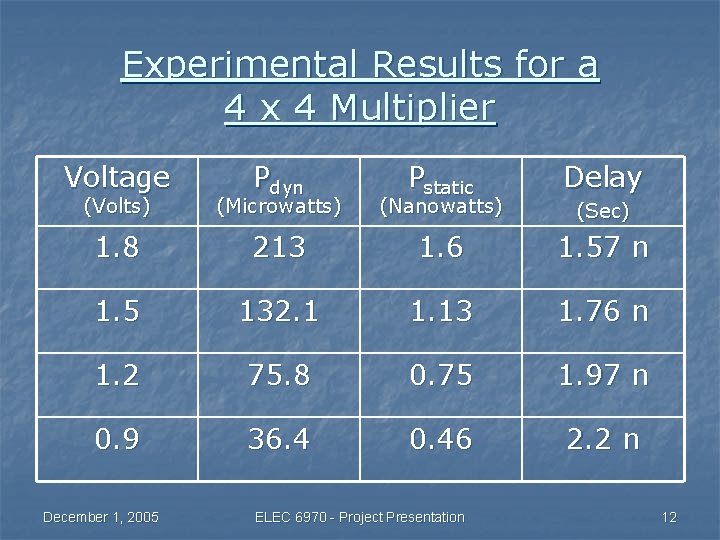

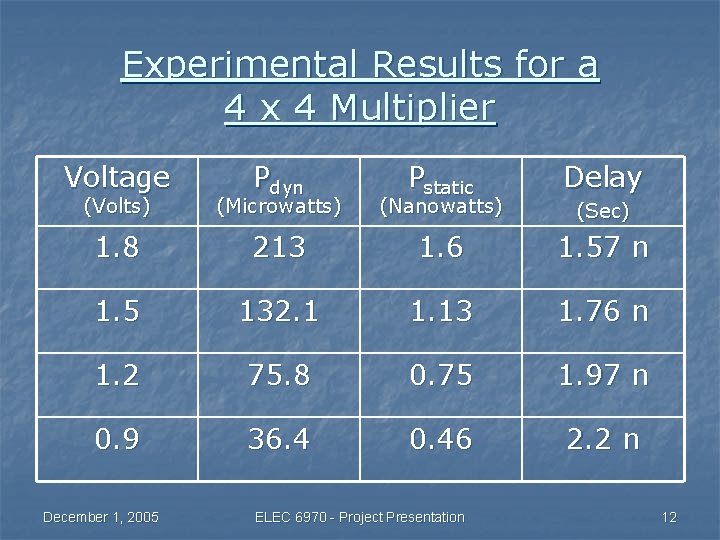

Experimental Results for a 4 x 4 Multiplier Voltage Pdyn Pstatic Delay (Volts) (Microwatts) (Nanowatts) 1. 8 213 1. 6 1. 57 n 1. 5 132. 1 1. 13 1. 76 n 1. 2 75. 8 0. 75 1. 97 n 0. 9 36. 4 0. 46 2. 2 n December 1, 2005 ELEC 6970 - Project Presentation (Sec) 12

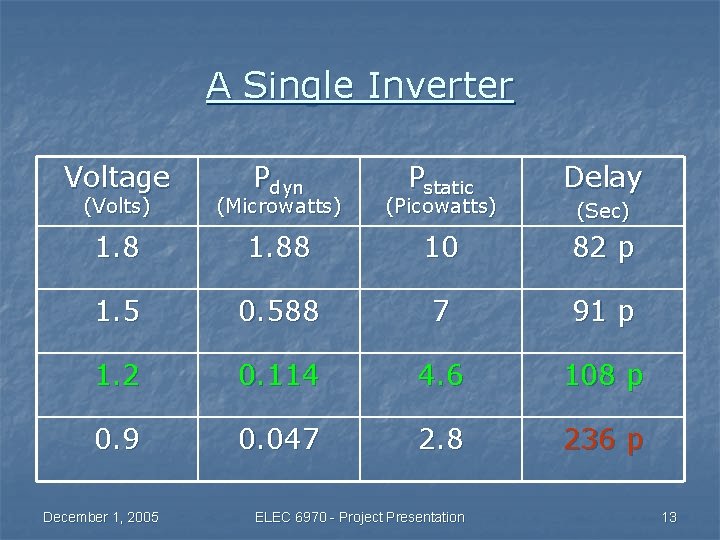

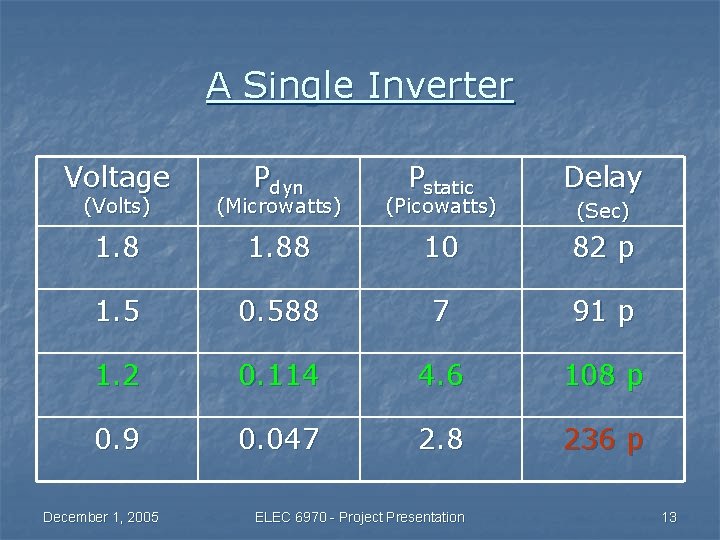

A Single Inverter Voltage Pdyn Pstatic Delay (Volts) (Microwatts) (Picowatts) 1. 88 10 82 p 1. 5 0. 588 7 91 p 1. 2 0. 114 4. 6 108 p 0. 9 0. 047 2. 8 236 p December 1, 2005 ELEC 6970 - Project Presentation (Sec) 13

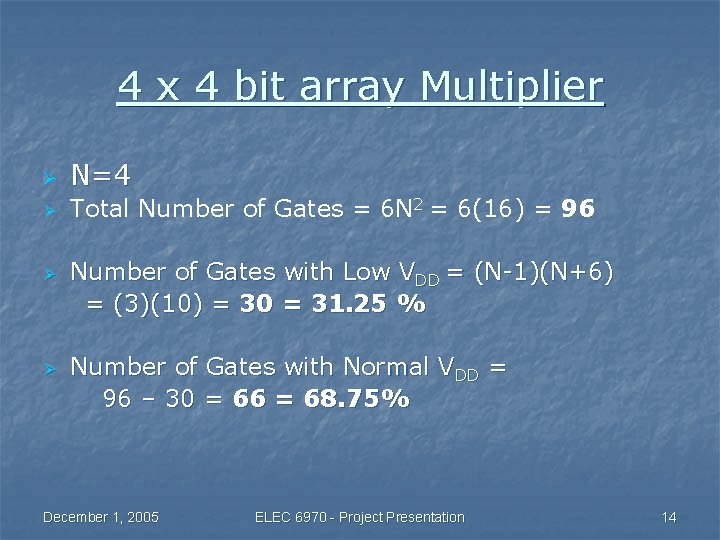

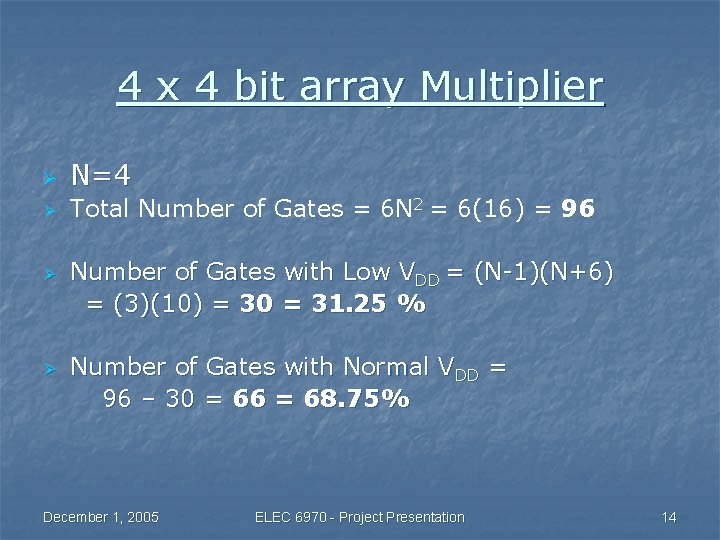

4 x 4 bit array Multiplier Ø N=4 Ø Total Number of Gates = 6 N 2 = 6(16) = 96 Ø Ø Number of Gates with Low VDD = (N-1)(N+6) = (3)(10) = 30 = 31. 25 % Number of Gates with Normal VDD = 96 – 30 = 66 = 68. 75% December 1, 2005 ELEC 6970 - Project Presentation 14

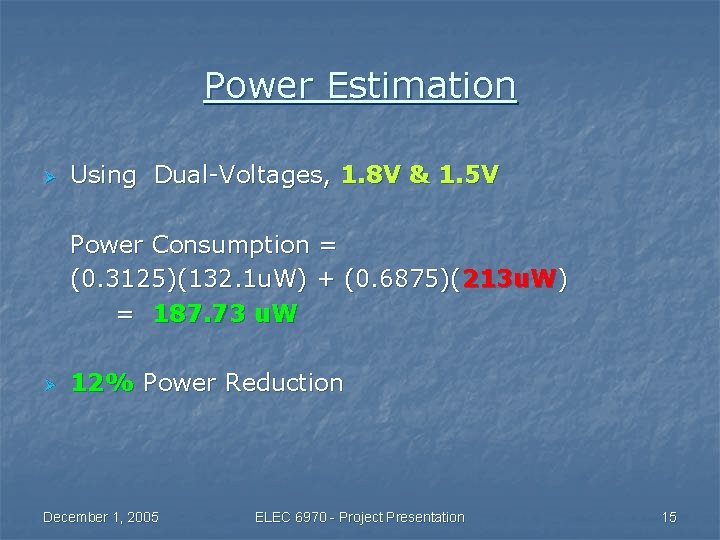

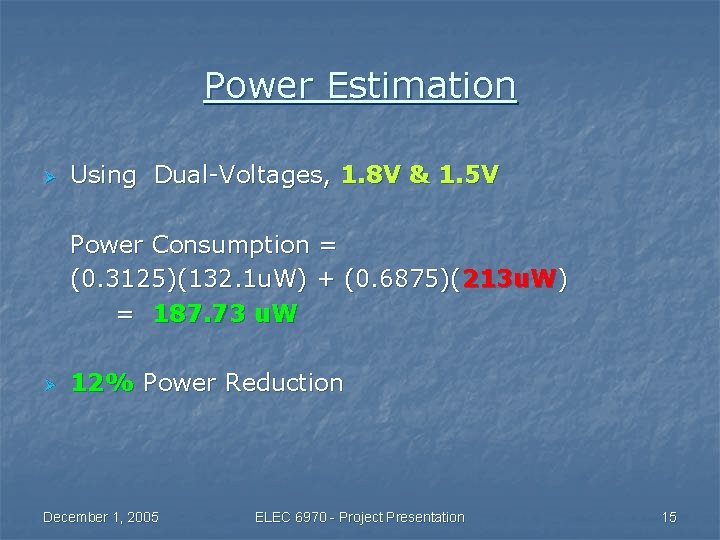

Power Estimation Ø Using Dual-Voltages, 1. 8 V & 1. 5 V Power Consumption = (0. 3125)(132. 1 u. W) + (0. 6875)(213 u. W) = 187. 73 u. W Ø 12% Power Reduction December 1, 2005 ELEC 6970 - Project Presentation 15

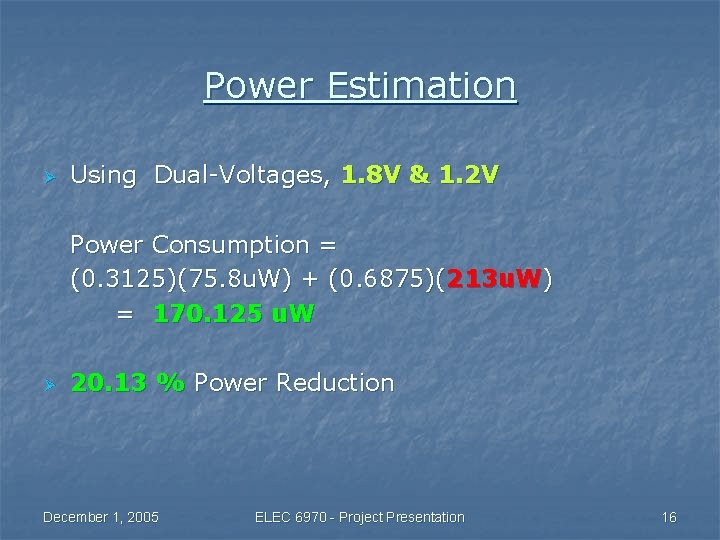

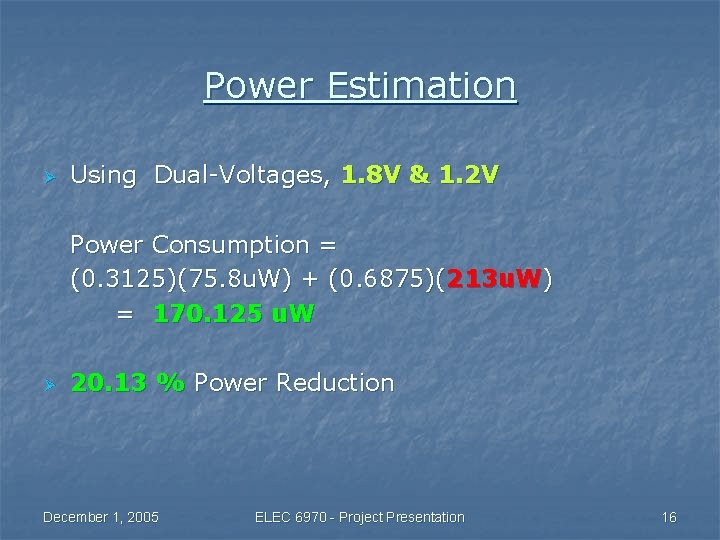

Power Estimation Ø Using Dual-Voltages, 1. 8 V & 1. 2 V Power Consumption = (0. 3125)(75. 8 u. W) + (0. 6875)(213 u. W) = 170. 125 u. W Ø 20. 13 % Power Reduction December 1, 2005 ELEC 6970 - Project Presentation 16

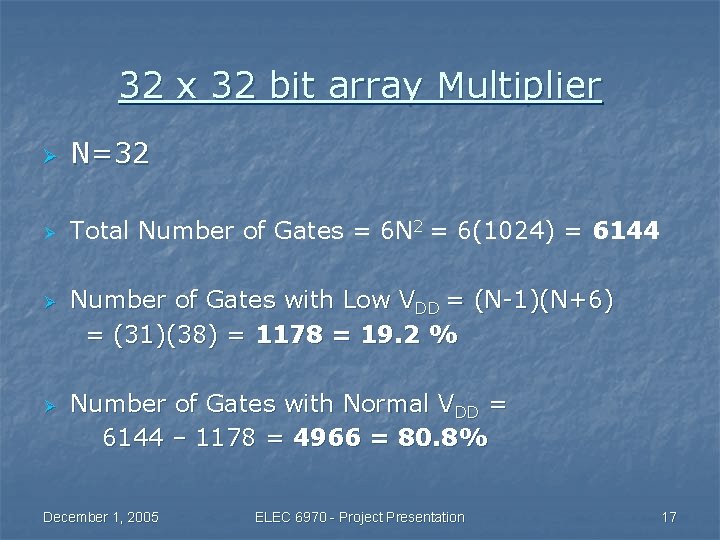

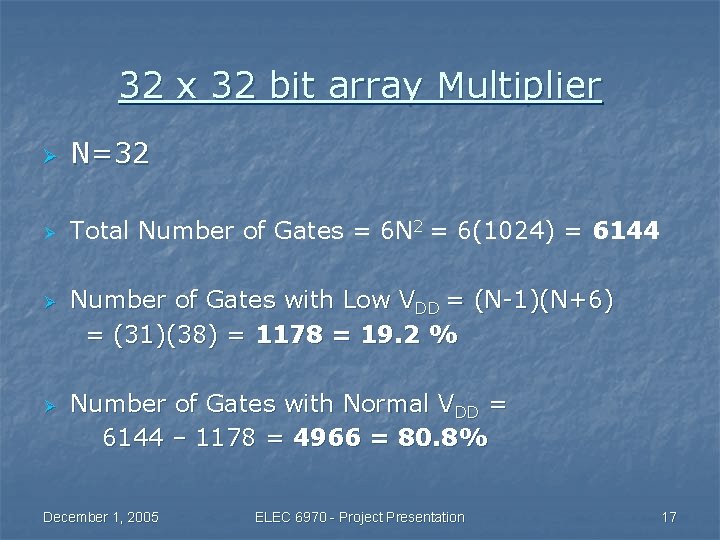

32 x 32 bit array Multiplier Ø N=32 Ø Total Number of Gates = 6 N 2 = 6(1024) = 6144 Ø Ø Number of Gates with Low VDD = (N-1)(N+6) = (31)(38) = 1178 = 19. 2 % Number of Gates with Normal VDD = 6144 – 1178 = 4966 = 80. 8% December 1, 2005 ELEC 6970 - Project Presentation 17

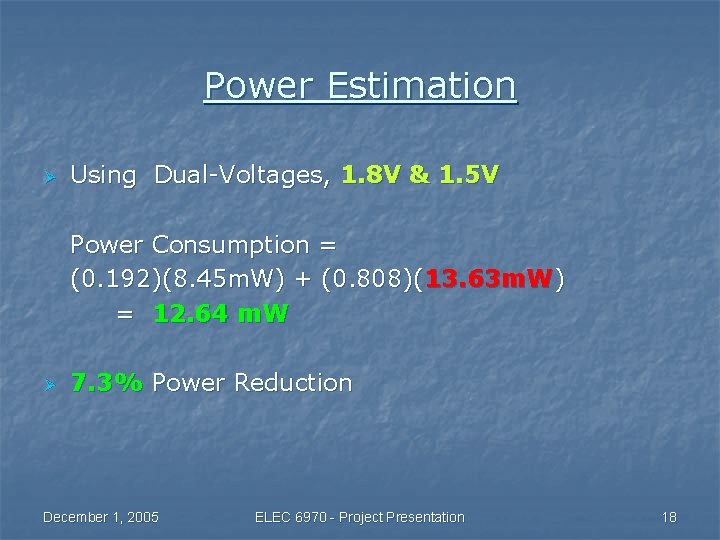

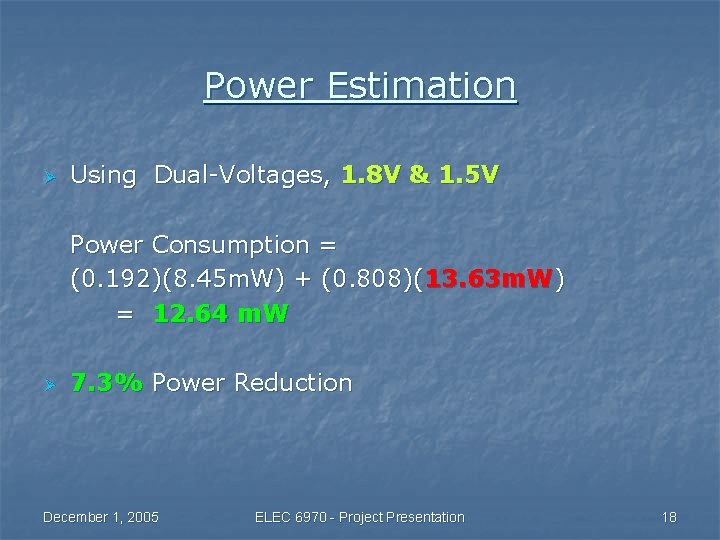

Power Estimation Ø Using Dual-Voltages, 1. 8 V & 1. 5 V Power Consumption = (0. 192)(8. 45 m. W) + (0. 808)(13. 63 m. W) = 12. 64 m. W Ø 7. 3% Power Reduction December 1, 2005 ELEC 6970 - Project Presentation 18

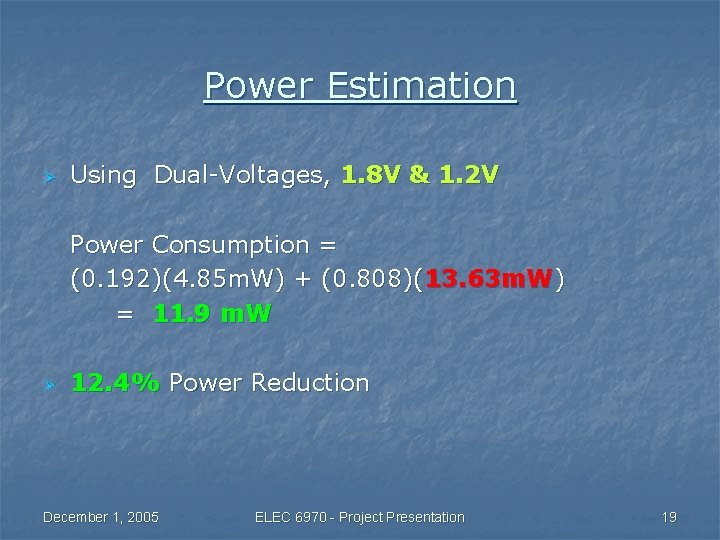

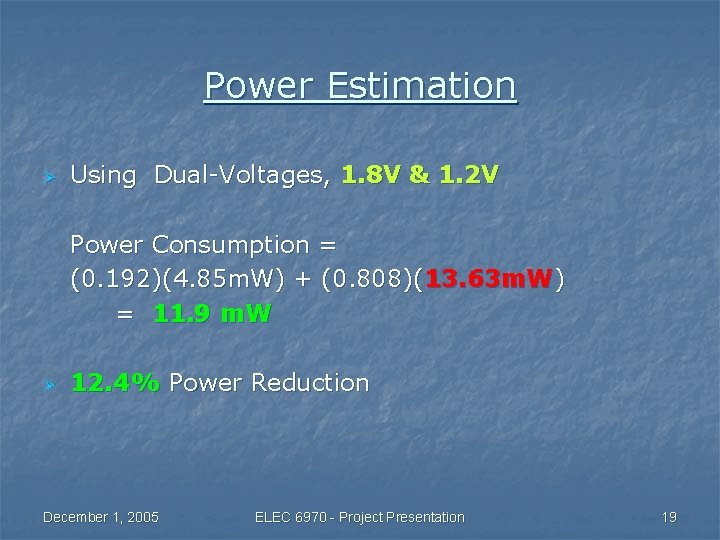

Power Estimation Ø Using Dual-Voltages, 1. 8 V & 1. 2 V Power Consumption = (0. 192)(4. 85 m. W) + (0. 808)(13. 63 m. W) = 11. 9 m. W Ø 12. 4% Power Reduction December 1, 2005 ELEC 6970 - Project Presentation 19

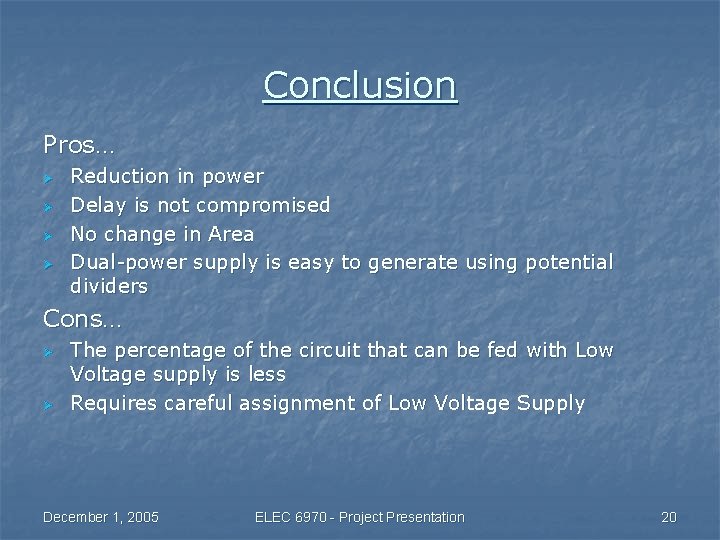

Conclusion Pros… Ø Ø Reduction in power Delay is not compromised No change in Area Dual-power supply is easy to generate using potential dividers Cons… Ø Ø The percentage of the circuit that can be fed with Low Voltage supply is less Requires careful assignment of Low Voltage Supply December 1, 2005 ELEC 6970 - Project Presentation 20

Comments Ø Learnt VHDL basics Ø Introduction to very useful EDA tools Ø Get a feel of VLSI Design Ø Appreciation of Low Power Design Ø Time Consuming but worth it December 1, 2005 ELEC 6970 - Project Presentation 21