DS Analog to Digital Converters Alex Doboli Ph

DS Analog to Digital Converters Alex Doboli, Ph. D. Department of Electrical and Computer Engineering State University of New York at Stony Brook Email: adoboli@ece. sunysb. edu ©Alex Doboli 2006

DS ADC The chapter introduces the following aspects: • Basic concepts of DS ADC & 1 sr and 2 nd order ADCs • ADC are main subsystems in any embedded system • DS ADC offer high resolution through two mechanisms: – Oversampling: reduces in-band quantization noise – Noiseshaping: eliminates in-band quantization noise • PSo. C implementation of DS ADC: modulator, decimator, API ©Alex Doboli 2006

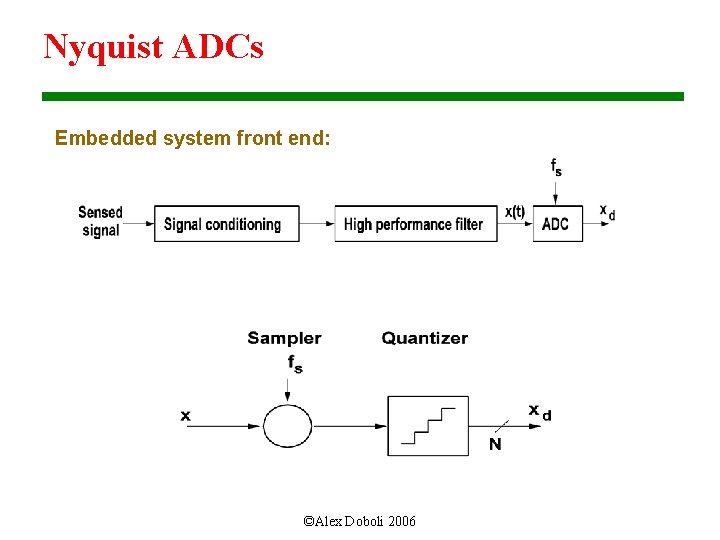

Nyquist ADCs Embedded system front end: ©Alex Doboli 2006

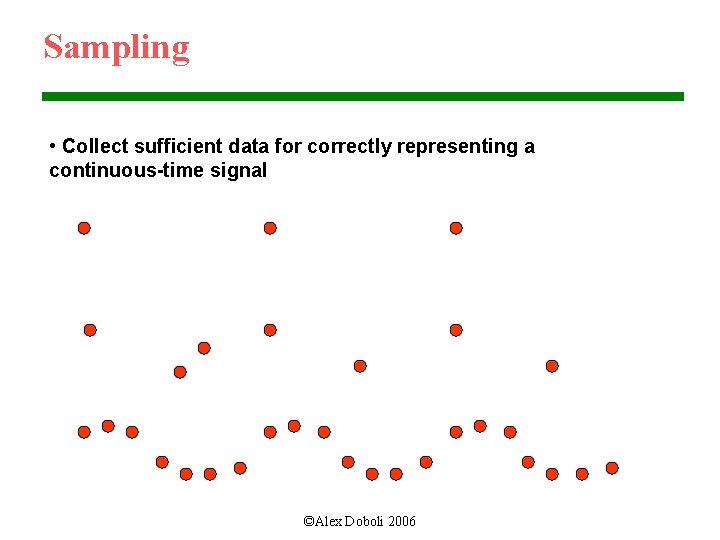

Sampling • Collect sufficient data for correctly representing a continuous-time signal ©Alex Doboli 2006

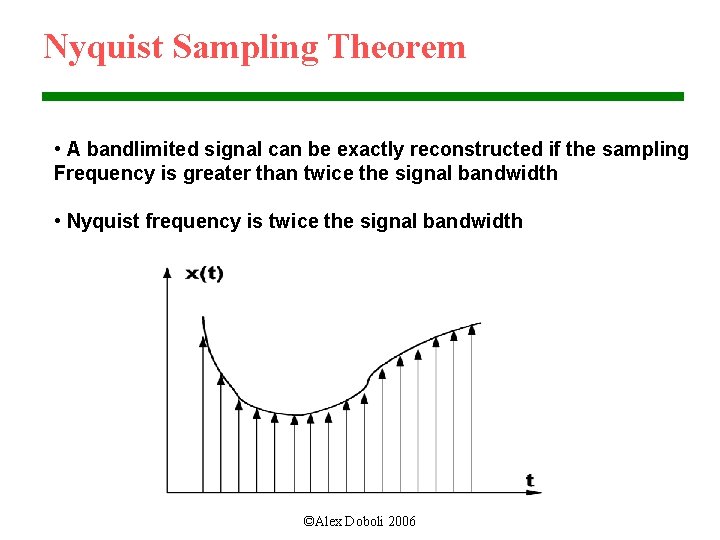

Nyquist Sampling Theorem • A bandlimited signal can be exactly reconstructed if the sampling Frequency is greater than twice the signal bandwidth • Nyquist frequency is twice the signal bandwidth ©Alex Doboli 2006

Sampling Xs(f) = X(f) + X(f+/-fs) + X(f+/-2 fs) + X(f+/-3 fs) + X(f+/-4 fs) + … aliasing ©Alex Doboli 2006

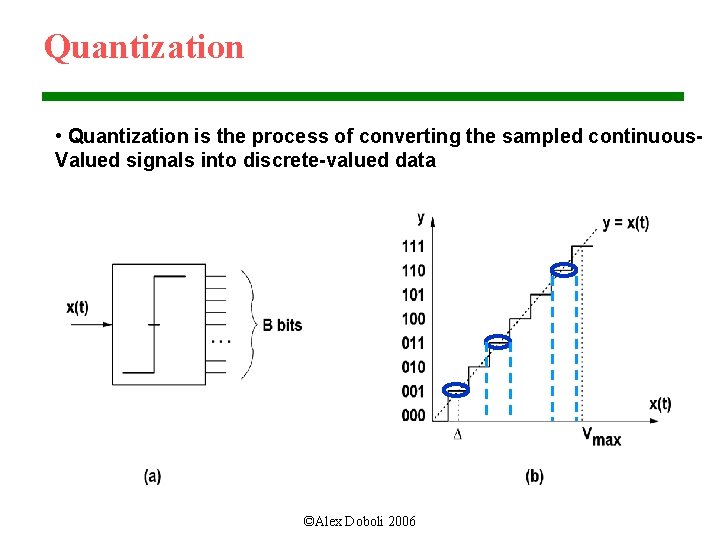

Quantization • Quantization is the process of converting the sampled continuous. Valued signals into discrete-valued data ©Alex Doboli 2006

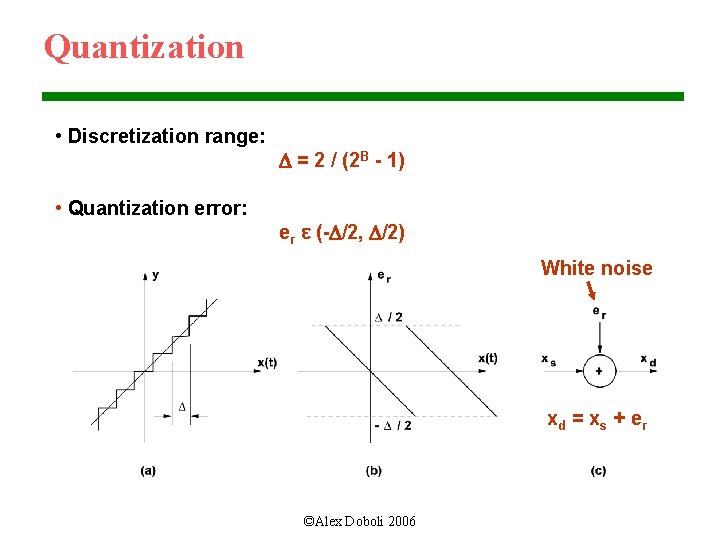

Quantization • Discretization range: • Quantization error: D = 2 / (2 B - 1) er ε (-D/2, D/2) White noise xd = xs + er ©Alex Doboli 2006

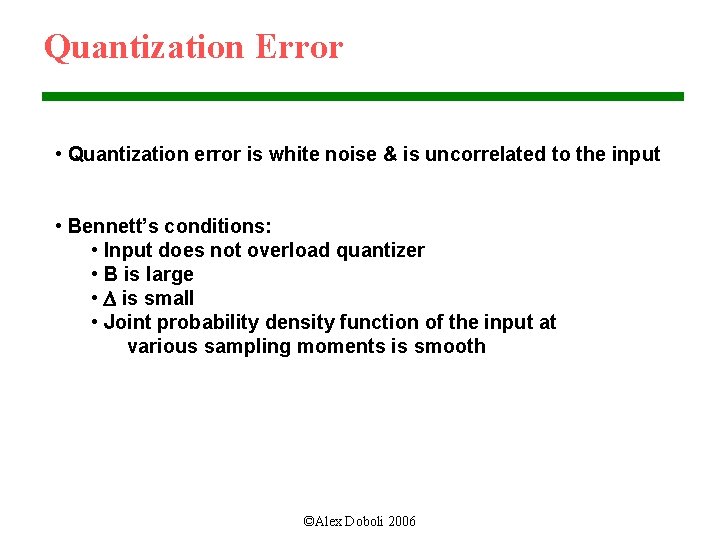

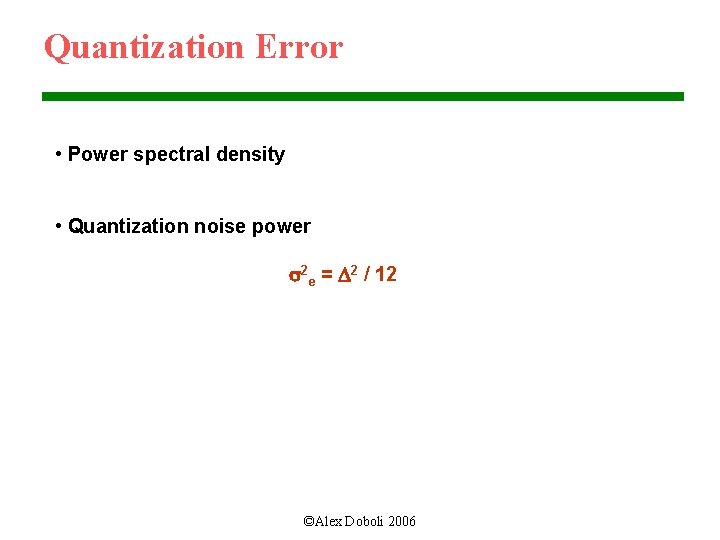

Quantization Error • Quantization error is white noise & is uncorrelated to the input • Bennett’s conditions: • Input does not overload quantizer • B is large • D is small • Joint probability density function of the input at various sampling moments is smooth ©Alex Doboli 2006

Quantization Error • Power spectral density • Quantization noise power s 2 e = D 2 / 12 ©Alex Doboli 2006

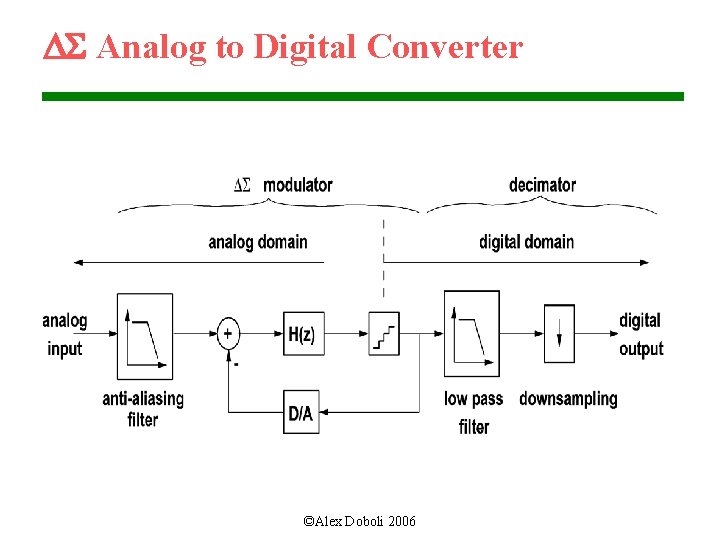

DS Analog to Digital Converter ©Alex Doboli 2006

Oversampling • Oversampling frequency • Oversampling Ratio (OSR) • Advantages of high OSR: • simplifies elimination of the images • reduced in-band noise power Pin-band = s 2 e / OSR ©Alex Doboli 2006

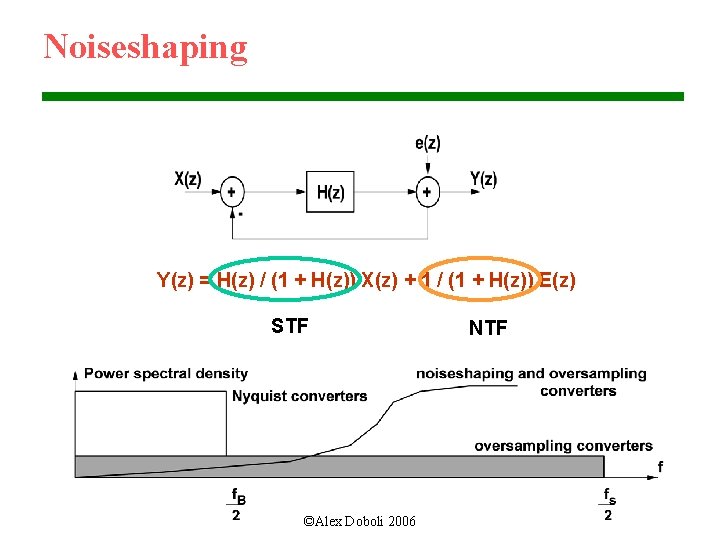

Noiseshaping Y(z) = H(z) / (1 + H(z)) X(z) + 1 / (1 + H(z)) E(z) STF ©Alex Doboli 2006 NTF

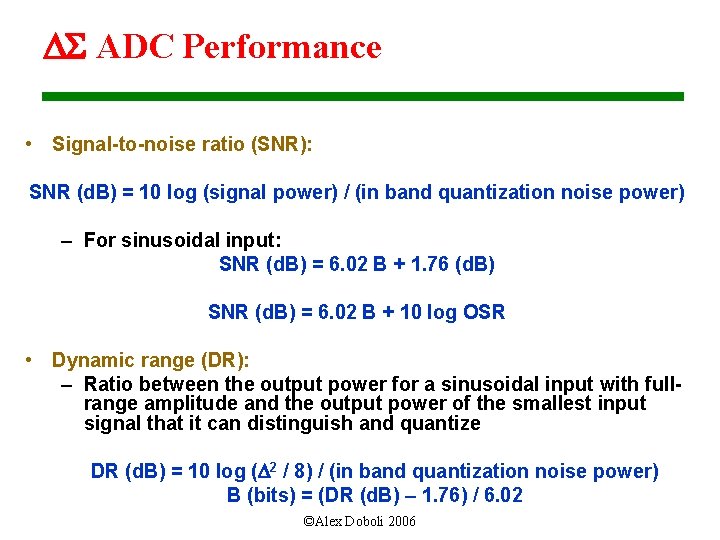

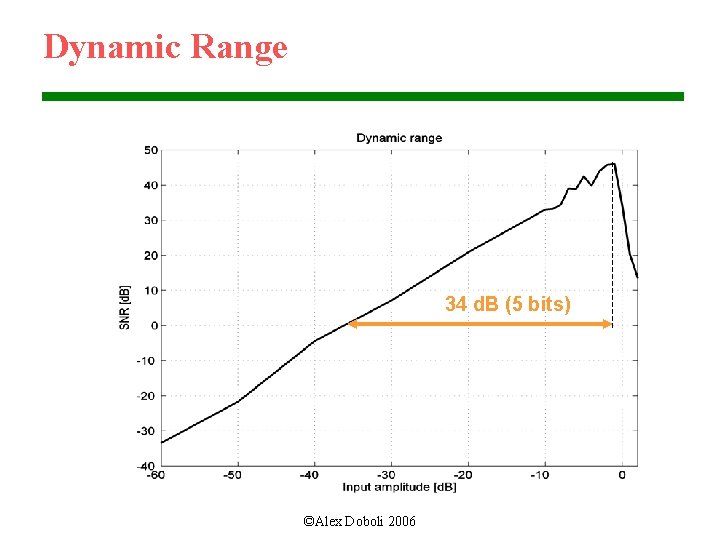

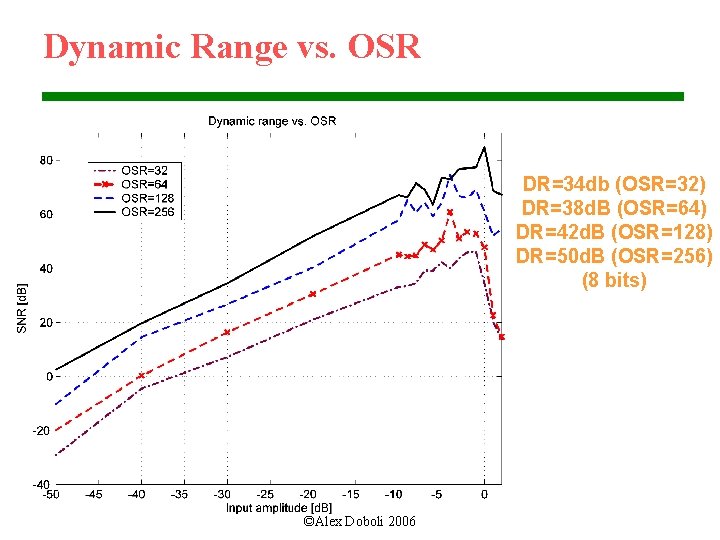

DS ADC Performance • Signal-to-noise ratio (SNR): SNR (d. B) = 10 log (signal power) / (in band quantization noise power) – For sinusoidal input: SNR (d. B) = 6. 02 B + 1. 76 (d. B) SNR (d. B) = 6. 02 B + 10 log OSR • Dynamic range (DR): – Ratio between the output power for a sinusoidal input with fullrange amplitude and the output power of the smallest input signal that it can distinguish and quantize DR (d. B) = 10 log (D 2 / 8) / (in band quantization noise power) B (bits) = (DR (d. B) – 1. 76) / 6. 02 ©Alex Doboli 2006

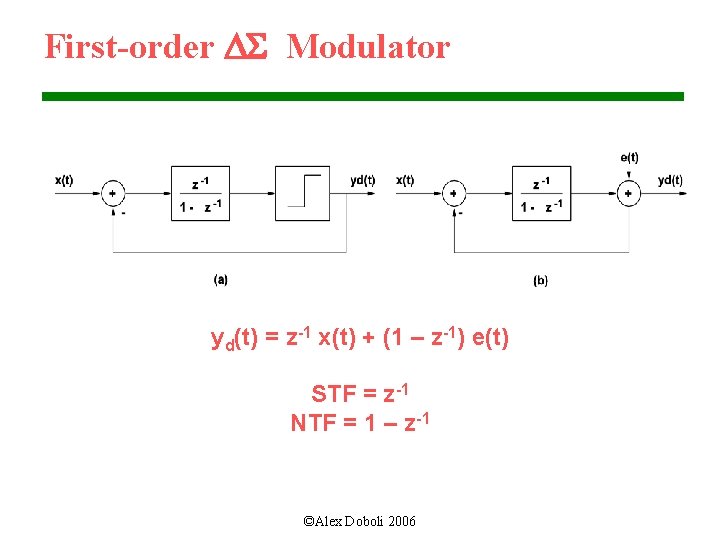

First-order DS Modulator yd(t) = z-1 x(t) + (1 – z-1) e(t) STF = z-1 NTF = 1 – z-1 ©Alex Doboli 2006

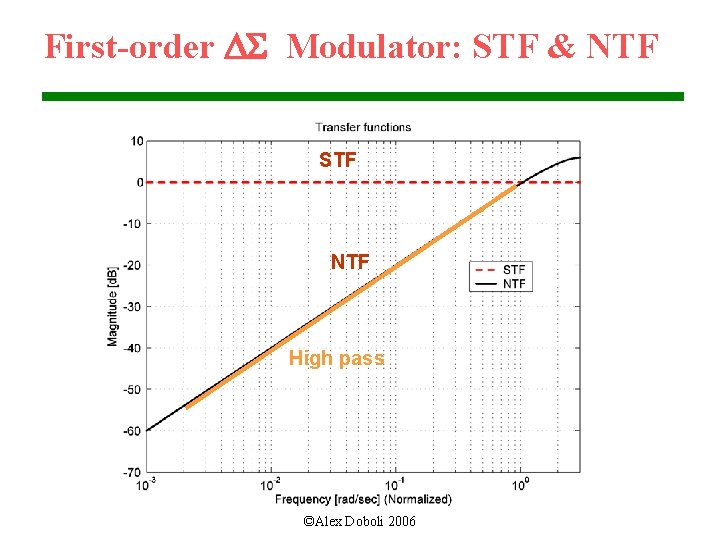

First-order DS Modulator: STF & NTF STF NTF High pass ©Alex Doboli 2006

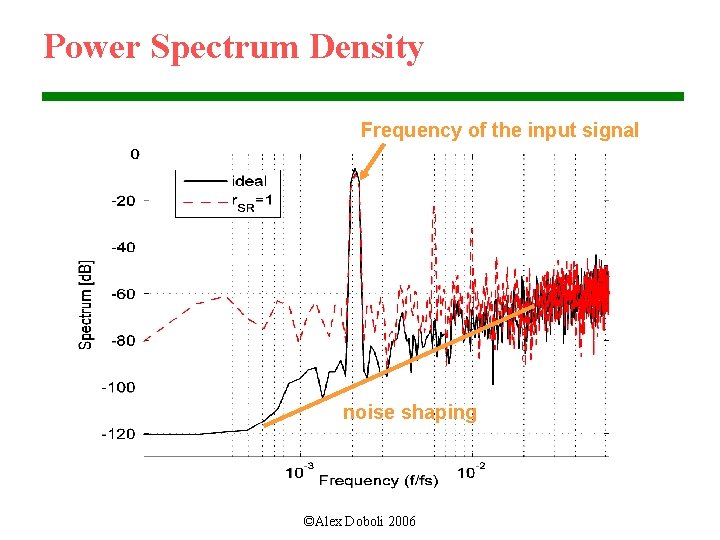

Power Spectrum Density Frequency of the input signal noise shaping ©Alex Doboli 2006

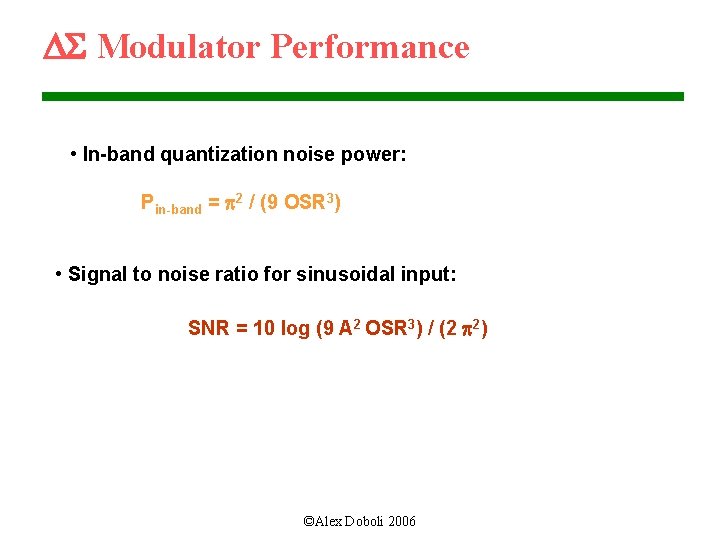

DS Modulator Performance • In-band quantization noise power: Pin-band = p 2 / (9 OSR 3) • Signal to noise ratio for sinusoidal input: SNR = 10 log (9 A 2 OSR 3) / (2 p 2) ©Alex Doboli 2006

Dynamic Range 34 d. B (5 bits) ©Alex Doboli 2006

Dynamic Range vs. OSR DR=34 db (OSR=32) DR=38 d. B (OSR=64) DR=42 d. B (OSR=128) DR=50 d. B (OSR=256) (8 bits) ©Alex Doboli 2006

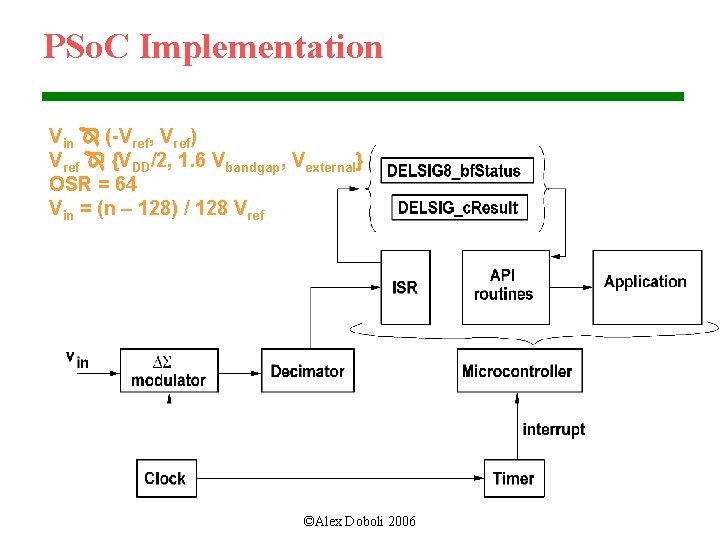

PSo. C Implementation Vin (-Vref, Vref) Vref {VDD/2, 1. 6 Vbandgap, Vexternal} OSR = 64 Vin = (n – 128) / 128 Vref ©Alex Doboli 2006

PSo. C Implementation • DS modulator – Uses programmable SC blocks • Decimator – Low pass filtering (eliminates high frequency images) – Downconversion by factor OSR – Sinc 2 filter – Implementation: hardware (integration) – software (differentiation) – Downconversion: timer produces an interrupt after OSR clock cycles & ISR implements differentiations • API routines • Clocks ©Alex Doboli 2006

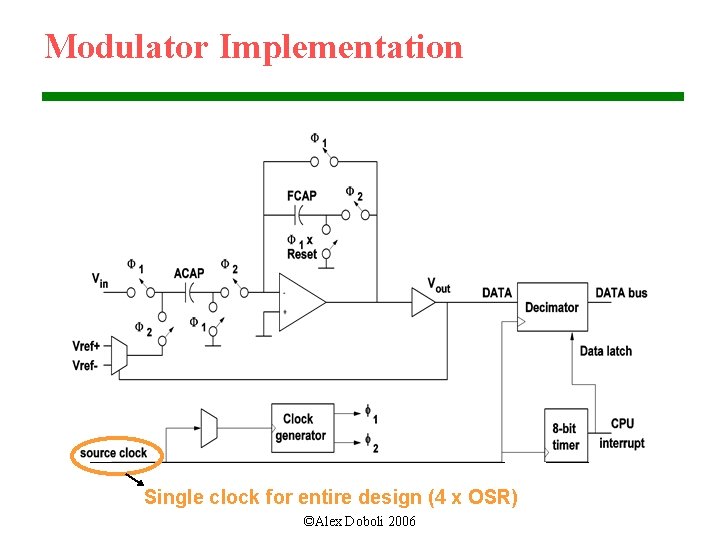

Modulator Implementation Single clock for entire design (4 x OSR) ©Alex Doboli 2006

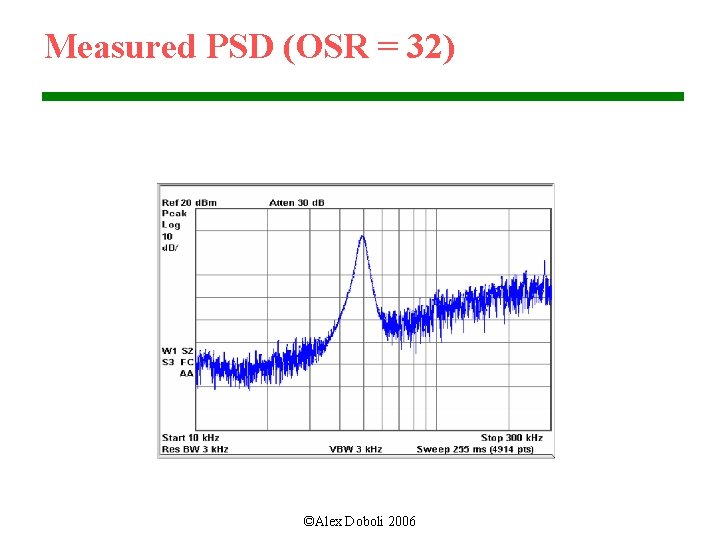

Measured PSD (OSR = 32) ©Alex Doboli 2006

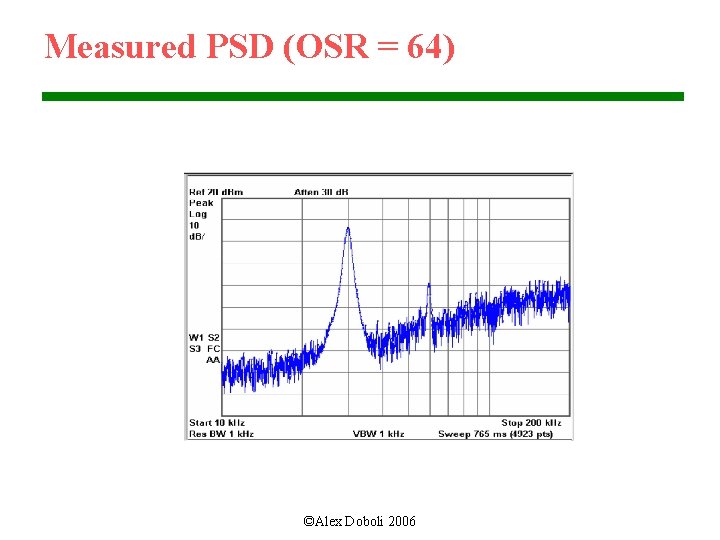

Measured PSD (OSR = 64) ©Alex Doboli 2006

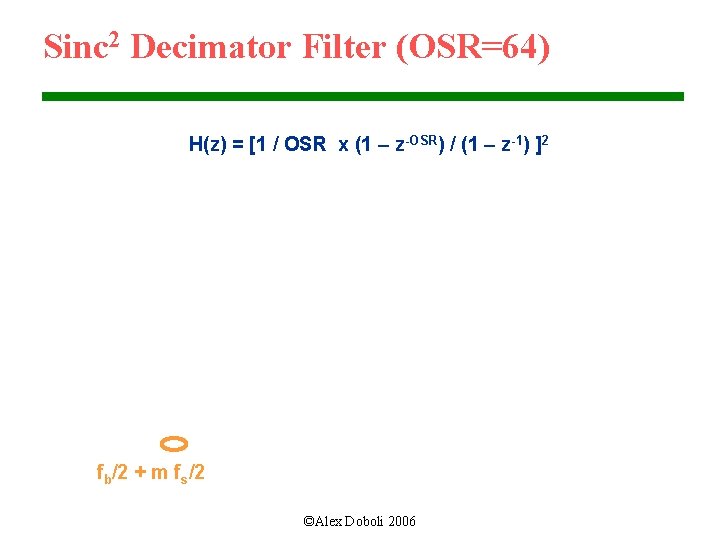

Sinc 2 Decimator Filter (OSR=64) H(z) = [1 / OSR x (1 – z-OSR) / (1 – z-1) ]2 fb/2 + m fs/2 ©Alex Doboli 2006

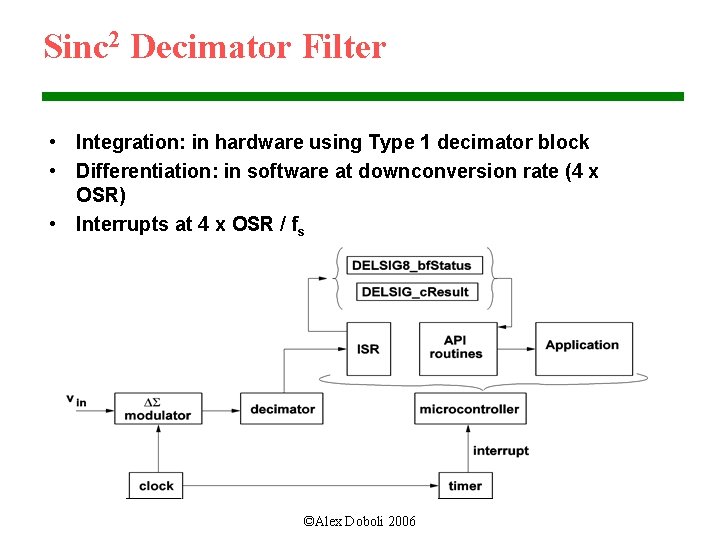

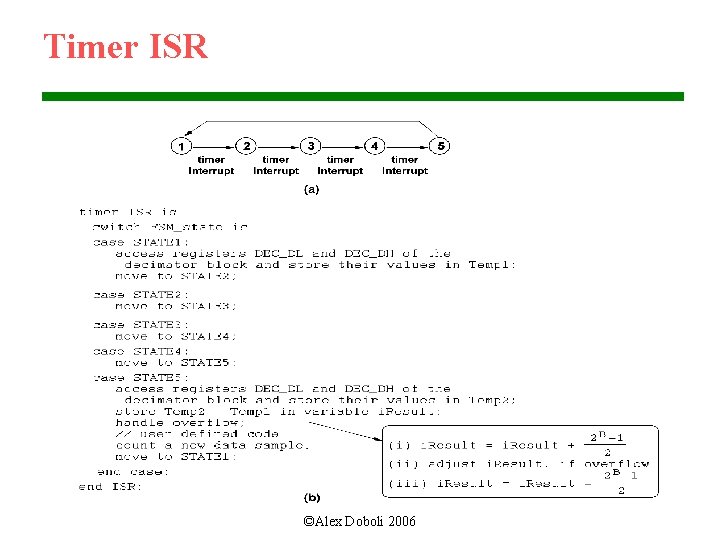

Sinc 2 Decimator Filter • Integration: in hardware using Type 1 decimator block • Differentiation: in software at downconversion rate (4 x OSR) • Interrupts at 4 x OSR / fs ©Alex Doboli 2006

Timer ISR ©Alex Doboli 2006

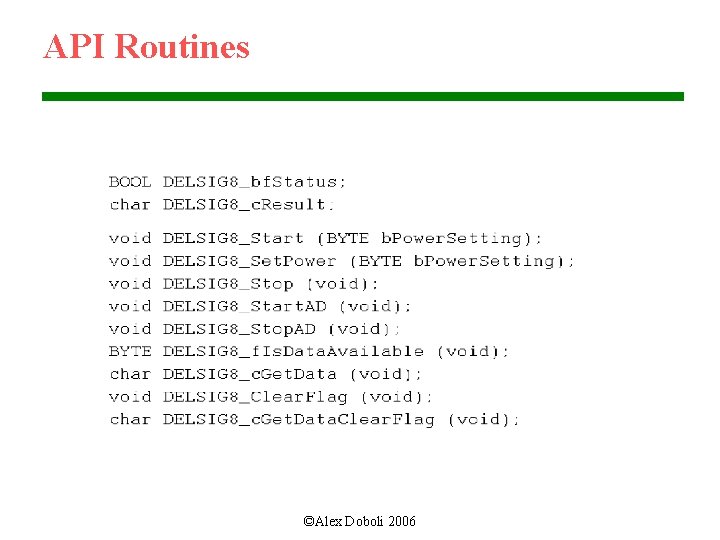

API Routines ©Alex Doboli 2006

API Routines ©Alex Doboli 2006

Example ©Alex Doboli 2006

Modeling of jitter noise ©Alex Doboli 2006

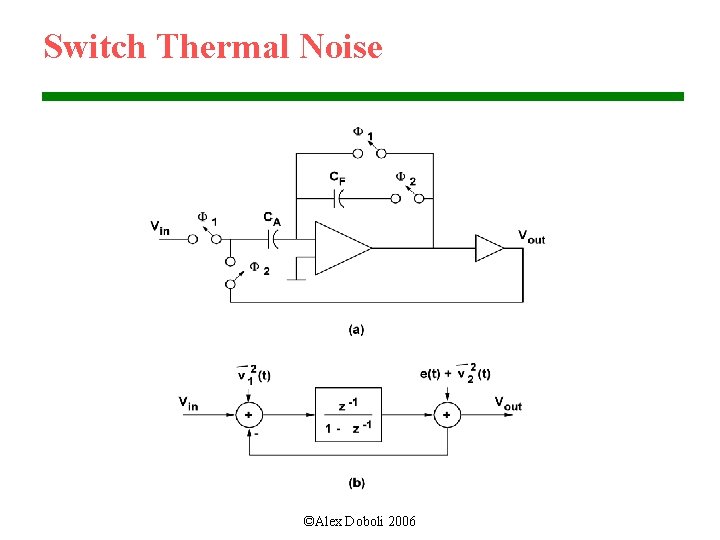

Switch Thermal Noise ©Alex Doboli 2006

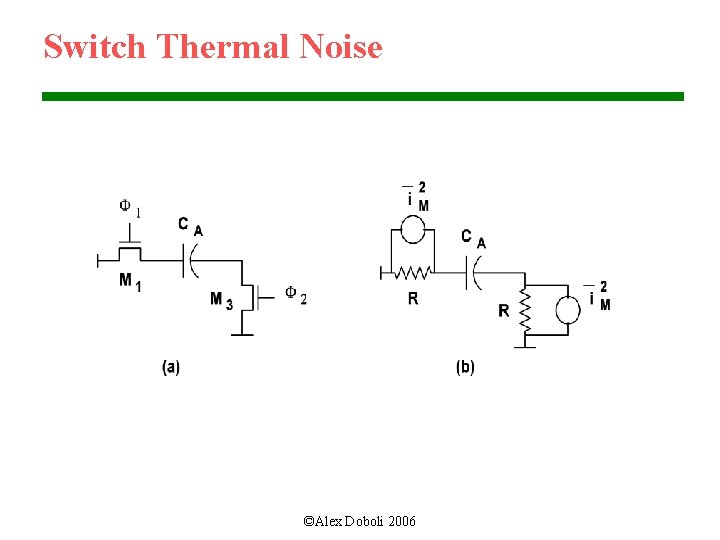

Switch Thermal Noise ©Alex Doboli 2006

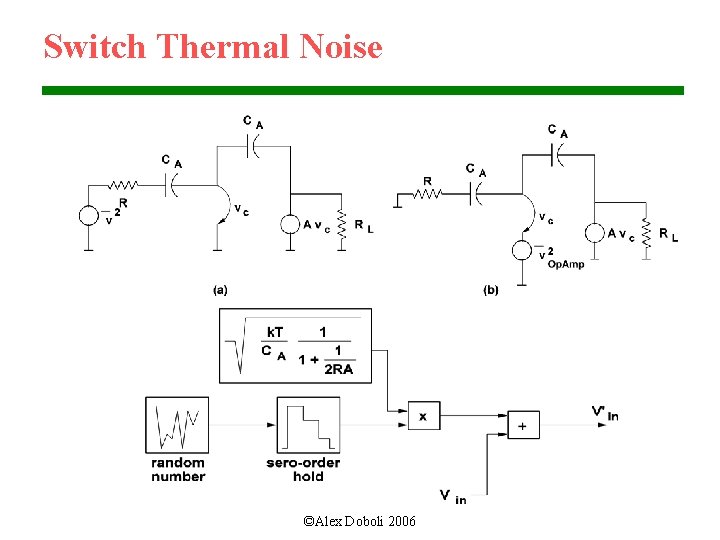

Switch Thermal Noise ©Alex Doboli 2006

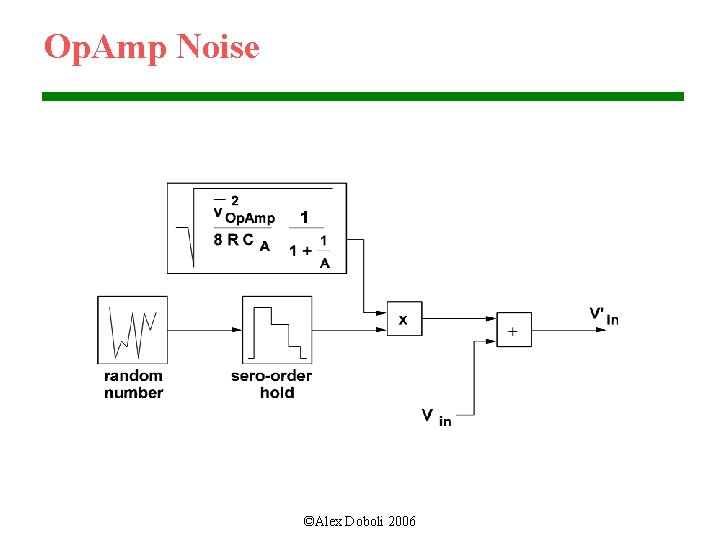

Op. Amp Noise ©Alex Doboli 2006

Modeling of Slew Rate & Saturation ©Alex Doboli 2006

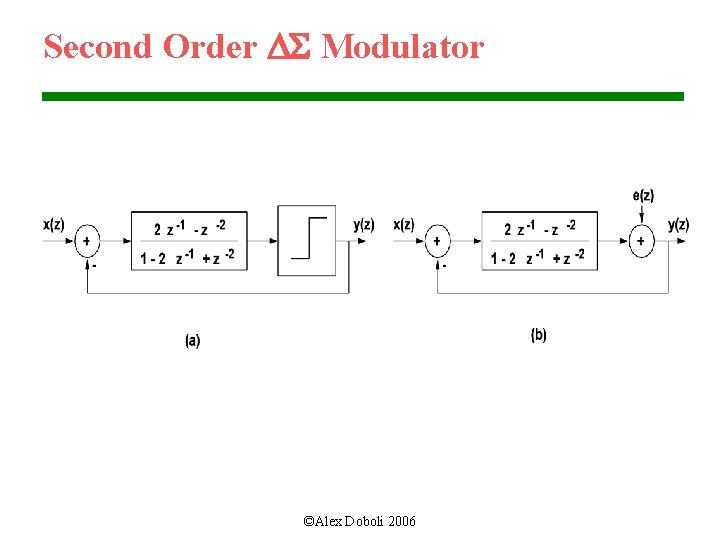

Second Order DS Modulator ©Alex Doboli 2006

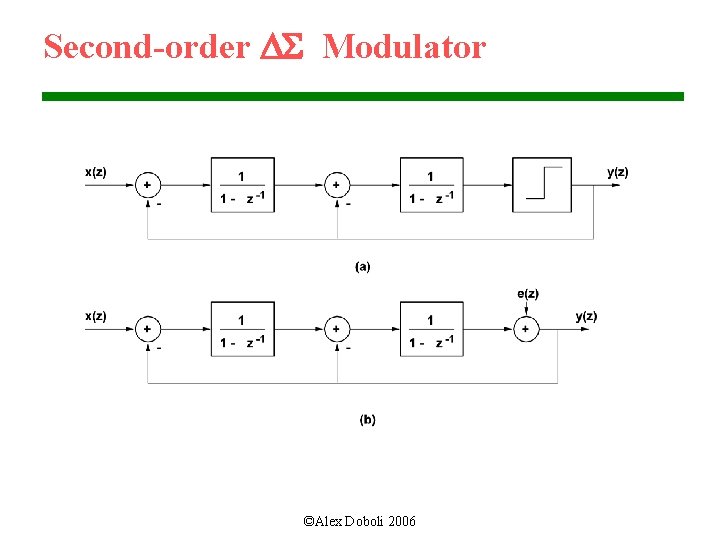

Second-order DS Modulator ©Alex Doboli 2006

PSo. C Implementation ©Alex Doboli 2006

- Slides: 40