Dr Faisal Alzyoud 2152022 INSTRUCTION SET ARCHITECTURE ISA

- Slides: 40

Dr. Faisal Alzyoud 2/15/2022 INSTRUCTION SET ARCHITECTURE (ISA) AND LANGUAGES

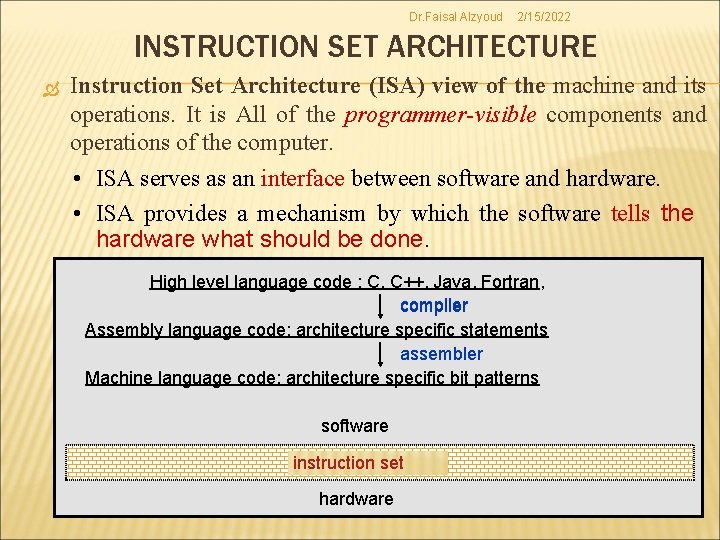

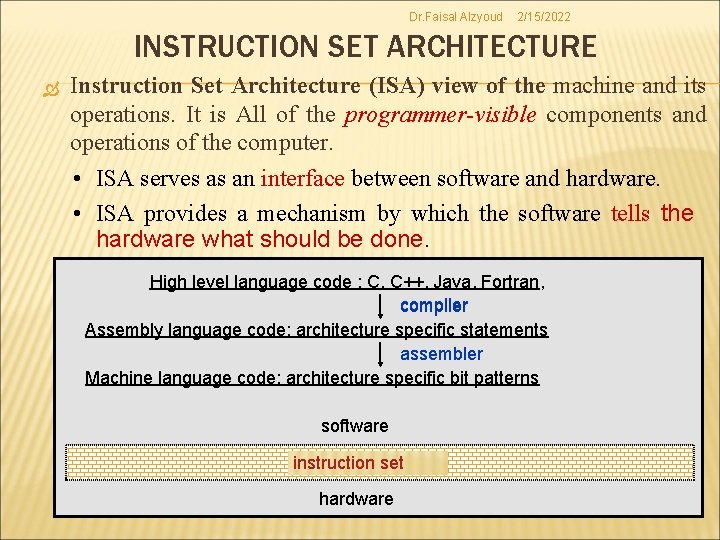

Dr. Faisal Alzyoud 2/15/2022 INSTRUCTION SET ARCHITECTURE Instruction Set Architecture (ISA) view of the machine and its operations. It is All of the programmer-visible components and operations of the computer. • ISA serves as an interface between software and hardware. • ISA provides a mechanism by which the software tells the hardware what should be done. High level language code : C, C++, Java, Fortran, compiler Assembly language code: architecture specific statements assembler Machine language code: architecture specific bit patterns software instruction set hardware

Dr. Faisal Alzyoud 2/15/2022 A compiler translates a high level language, which is architecture independent, into assembly language, which is architecture dependent. An assembler translates assembly language programs into executable binary codes. For fully compiled languages like C and Fortran, the binary codes are executed directly by the target machine. Java stops the translation at the byte code level. The Java virtual machine, which is at the assembly language level, interprets the byte codes (hardware implementations of the JVM also exist, in which Java byte codes are executed directly. ) A compiled program is copied from a hard disk to the memory. The CPU reads instructions and data from the memory, executes the instructions,

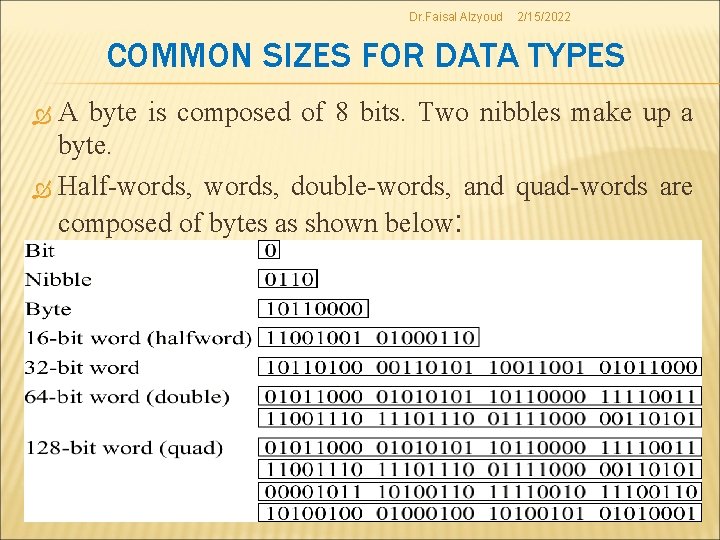

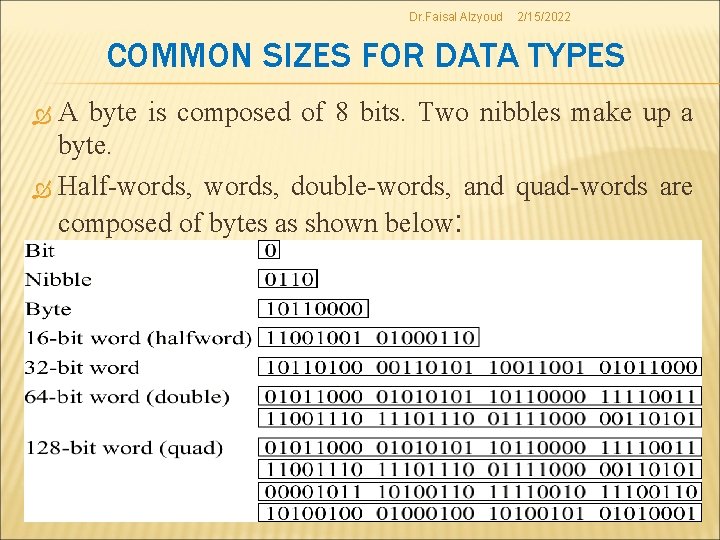

Dr. Faisal Alzyoud 2/15/2022 COMMON SIZES FOR DATA TYPES A byte is composed of 8 bits. Two nibbles make up a byte. Half-words, double-words, and quad-words are composed of bytes as shown below:

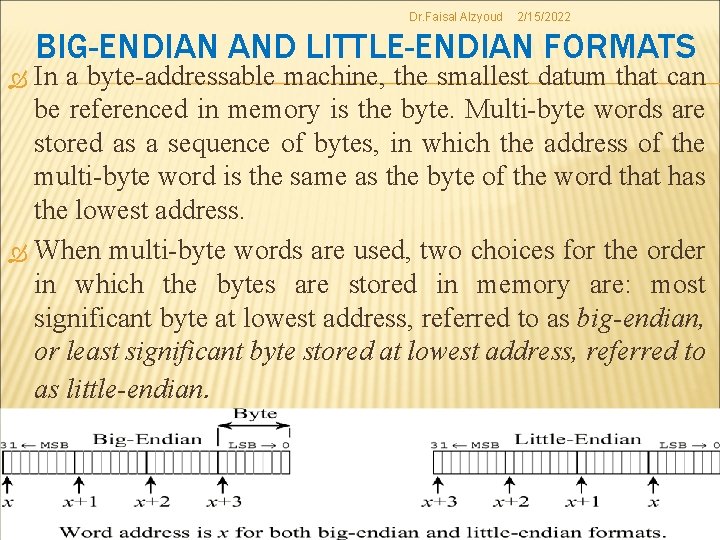

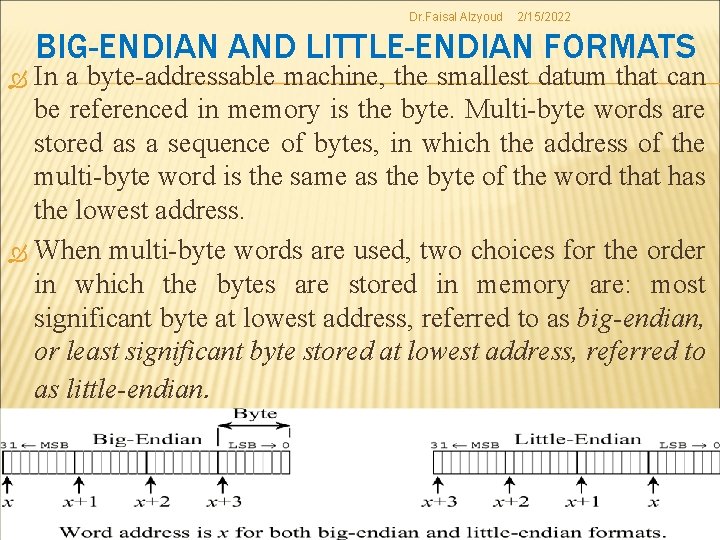

Dr. Faisal Alzyoud 2/15/2022 BIG-ENDIAN AND LITTLE-ENDIAN FORMATS In a byte-addressable machine, the smallest datum that can be referenced in memory is the byte. Multi-byte words are stored as a sequence of bytes, in which the address of the multi-byte word is the same as the byte of the word that has the lowest address. When multi-byte words are used, two choices for the order in which the bytes are stored in memory are: most significant byte at lowest address, referred to as big-endian, or least significant byte stored at lowest address, referred to as little-endian.

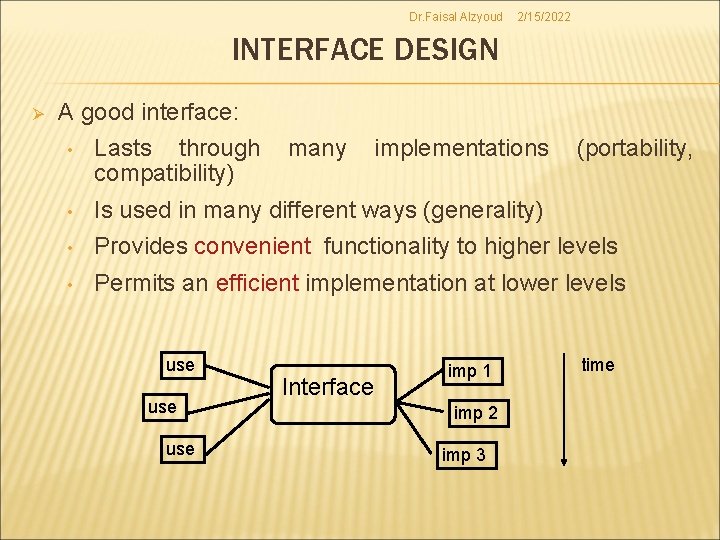

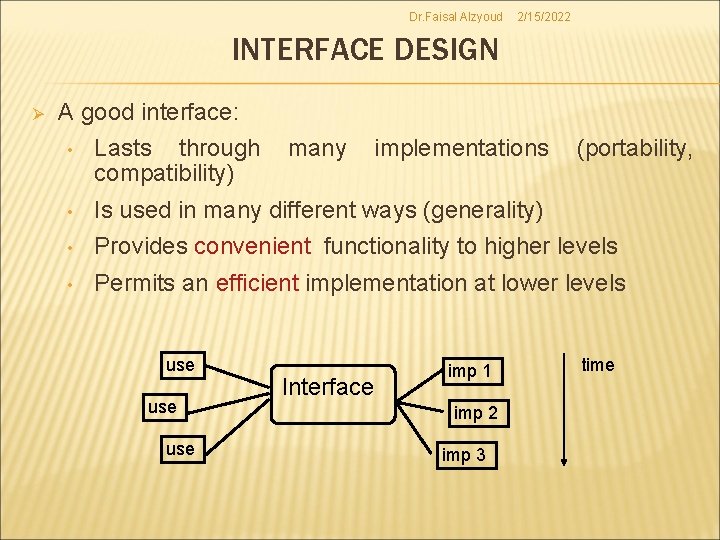

Dr. Faisal Alzyoud 2/15/2022 INTERFACE DESIGN Ø A good interface: • Lasts through compatibility) • Is used in many different ways (generality) • Provides convenient functionality to higher levels • Permits an efficient implementation at lower levels use use many implementations Interface imp 1 imp 2 imp 3 (portability, time

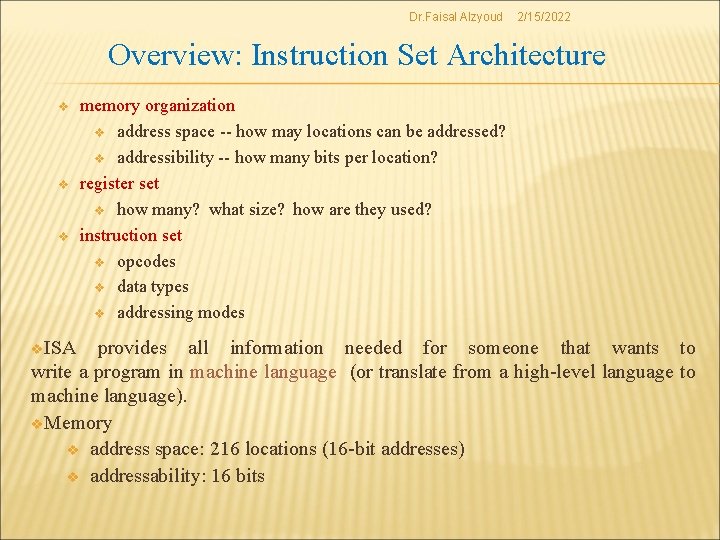

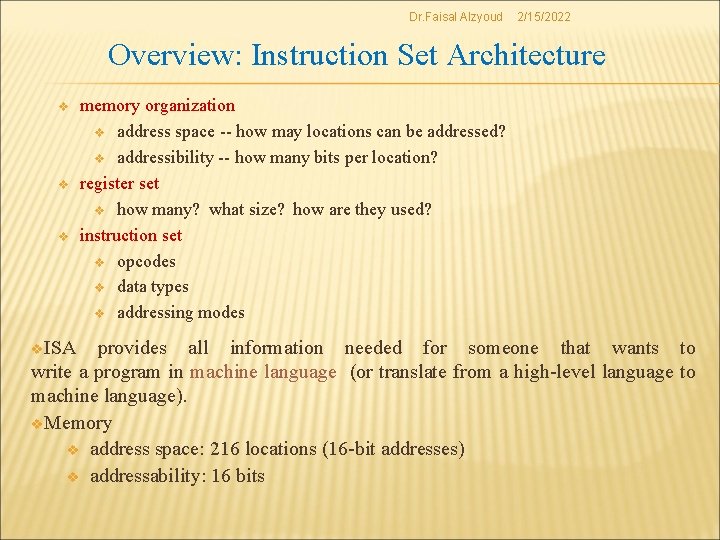

Dr. Faisal Alzyoud 2/15/2022 Overview: Instruction Set Architecture v v. ISA memory organization v address space -- how may locations can be addressed? v addressibility -- how many bits per location? register set v how many? what size? how are they used? instruction set v opcodes v data types v addressing modes provides all information needed for someone that wants to write a program in machine language (or translate from a high-level language to machine language). v. Memory v address space: 216 locations (16 -bit addresses) v addressability: 16 bits

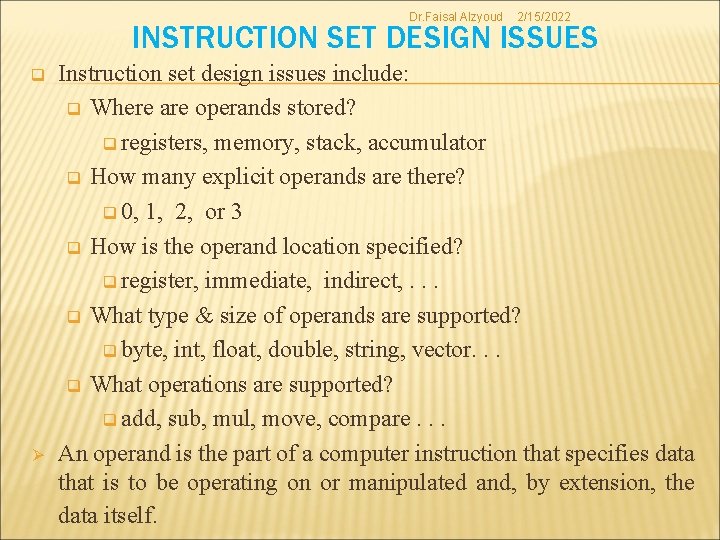

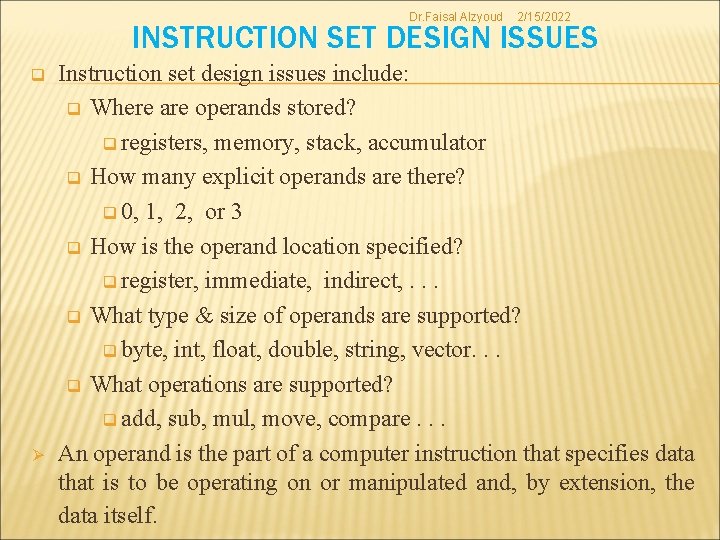

Dr. Faisal Alzyoud 2/15/2022 INSTRUCTION SET DESIGN ISSUES q Ø Instruction set design issues include: q Where are operands stored? q registers, memory, stack, accumulator q How many explicit operands are there? q 0, 1, 2, or 3 q How is the operand location specified? q register, immediate, indirect, . . . q What type & size of operands are supported? q byte, int, float, double, string, vector. . . q What operations are supported? q add, sub, mul, move, compare. . . An operand is the part of a computer instruction that specifies data that is to be operating on or manipulated and, by extension, the data itself.

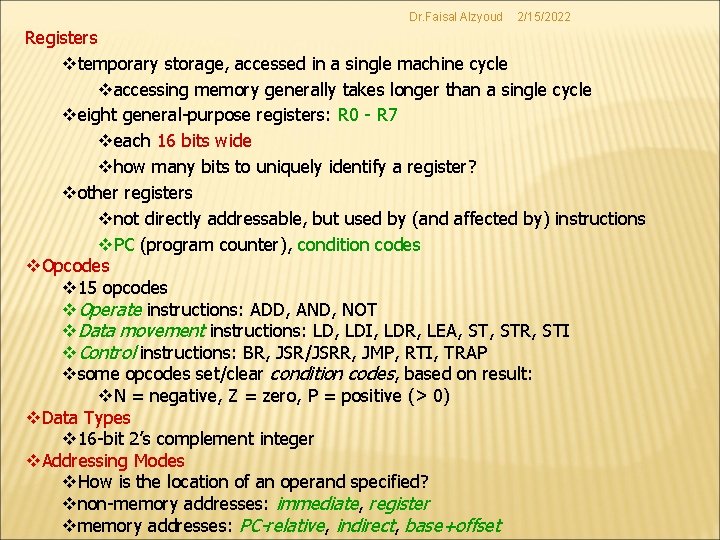

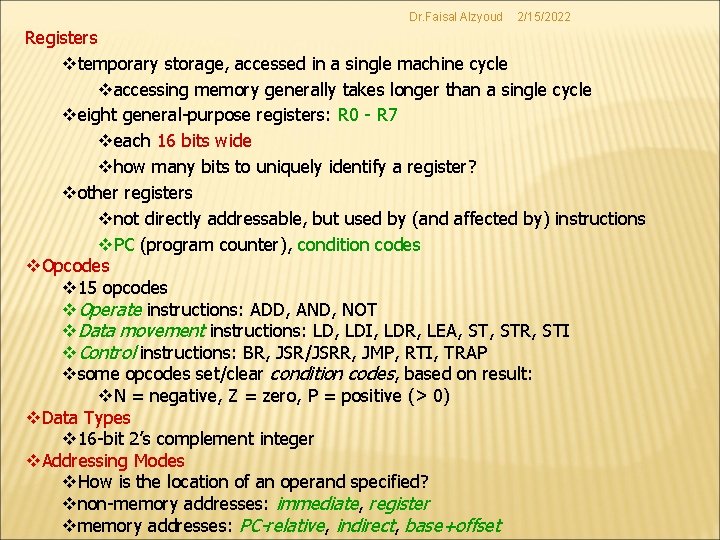

Dr. Faisal Alzyoud 2/15/2022 Registers vtemporary storage, accessed in a single machine cycle vaccessing memory generally takes longer than a single cycle veight general-purpose registers: R 0 - R 7 veach 16 bits wide vhow many bits to uniquely identify a register? vother registers vnot directly addressable, but used by (and affected by) instructions v. PC (program counter), condition codes v. Opcodes v 15 opcodes v. Operate instructions: ADD, AND, NOT v. Data movement instructions: LD, LDI, LDR, LEA, STR, STI v. Control instructions: BR, JSR/JSRR, JMP, RTI, TRAP vsome opcodes set/clear condition codes, based on result: v. N = negative, Z = zero, P = positive (> 0) v. Data Types v 16 -bit 2’s complement integer v. Addressing Modes v. How is the location of an operand specified? vnon-memory addresses: immediate, register vmemory addresses: PC-relative, indirect, base+offset

Dr. Faisal Alzyoud 2/15/2022 What is ARC ? ARC: (Additional architectural models) is a simplification of the commercial SPARC architecture common to Sun computers. ARC: A RISC Computer (where RISC: Reduced Instruction Set Computer). ARC is a subset of SPARC. (where SPARCis Scalable Processor Architecture developed by Sun Microsystems in the 1980’s). The ARC is a 32 -bit machine with byte-addressable memory: it can manipulate 32 -bit data types, but all data is stored in memory as bytes, and the address of a 32 -bit word is the address of its byte that has the lowest address. The ARC has a 32 -bit address space, in which our example architecture is divided into distinct regions for use by the operating system code, user program code, the system stack (used to store temporary data), and input and output, (I/O).

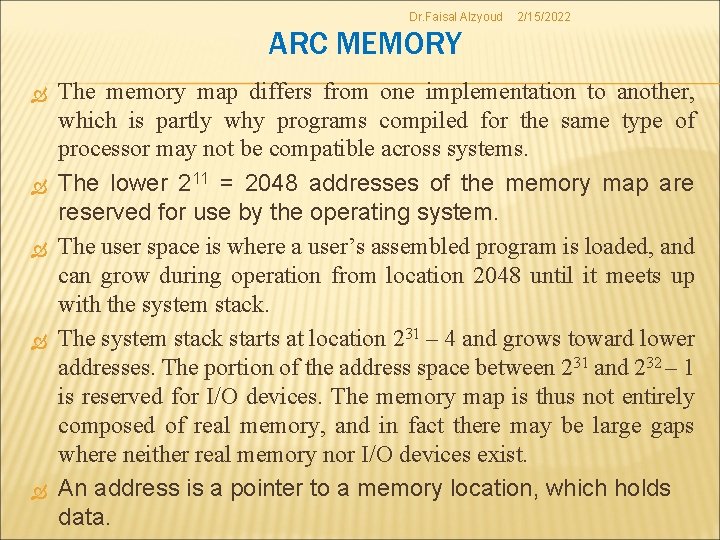

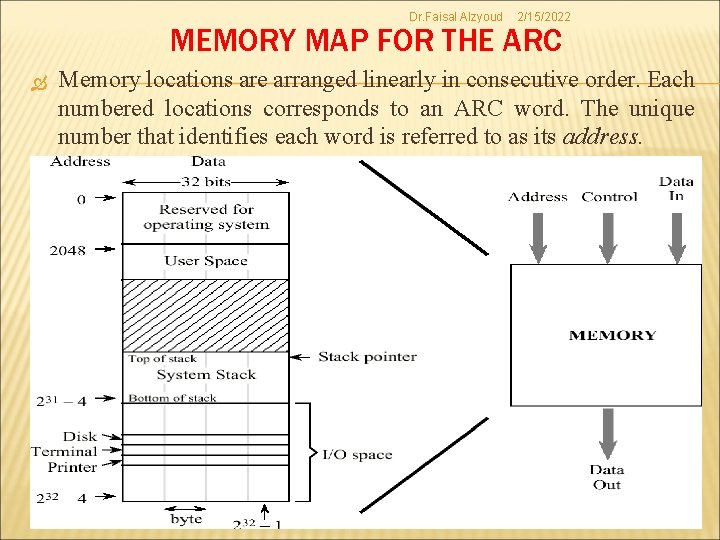

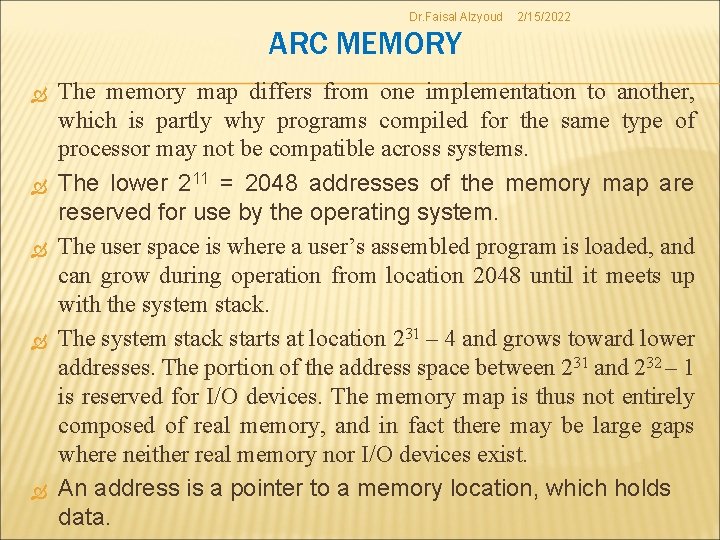

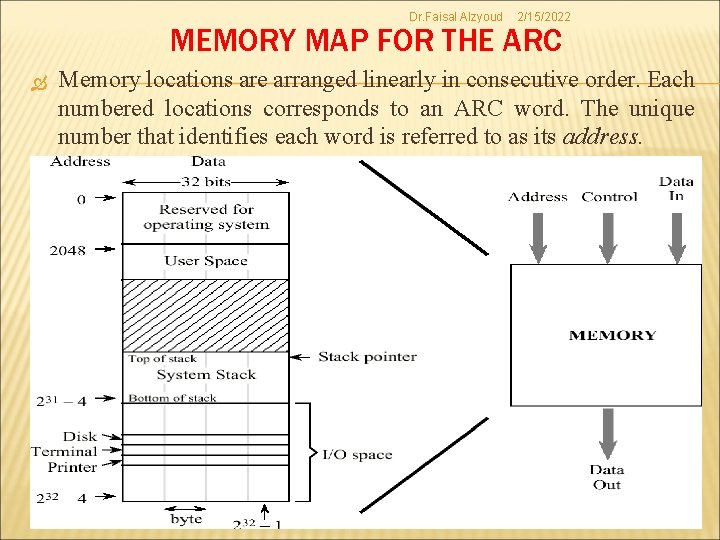

Dr. Faisal Alzyoud 2/15/2022 ARC MEMORY The memory map differs from one implementation to another, which is partly why programs compiled for the same type of processor may not be compatible across systems. The lower 211 = 2048 addresses of the memory map are reserved for use by the operating system. The user space is where a user’s assembled program is loaded, and can grow during operation from location 2048 until it meets up with the system stack. The system stack starts at location 231 – 4 and grows toward lower addresses. The portion of the address space between 231 and 232 – 1 is reserved for I/O devices. The memory map is thus not entirely composed of real memory, and in fact there may be large gaps where neither real memory nor I/O devices exist. An address is a pointer to a memory location, which holds data.

Dr. Faisal Alzyoud 2/15/2022 MEMORY MAP FOR THE ARC Memory locations are arranged linearly in consecutive order. Each numbered locations corresponds to an ARC word. The unique number that identifies each word is referred to as its address.

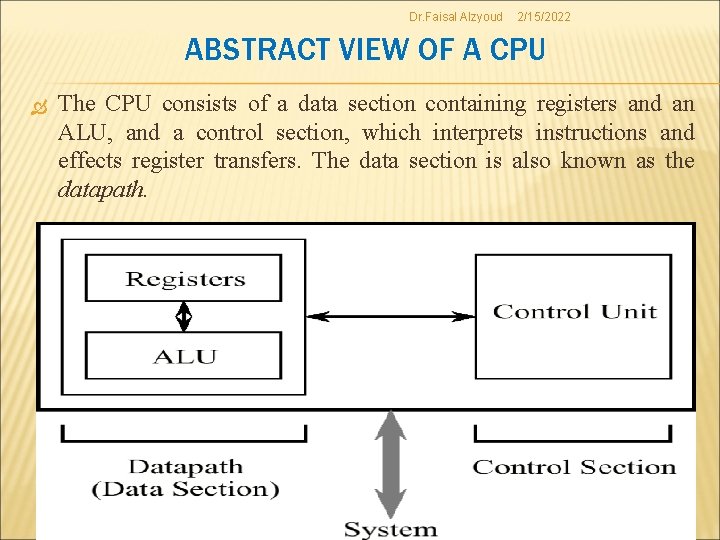

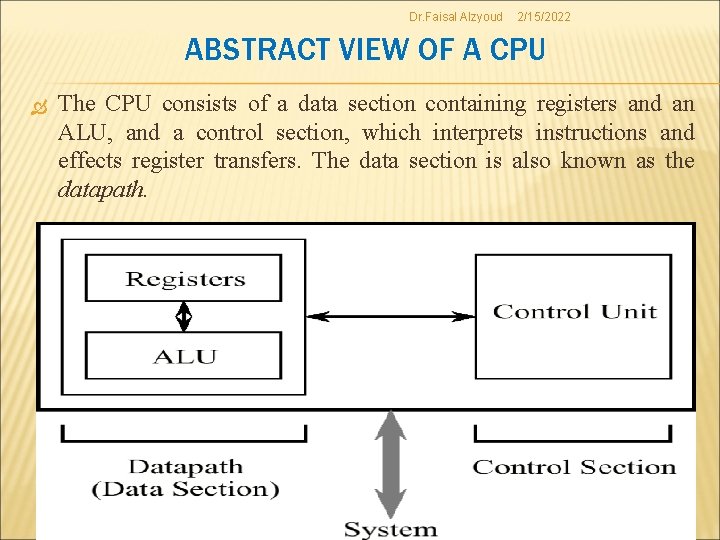

Dr. Faisal Alzyoud 2/15/2022 ABSTRACT VIEW OF A CPU The CPU consists of a data section containing registers and an ALU, and a control section, which interprets instructions and effects register transfers. The data section is also known as the datapath.

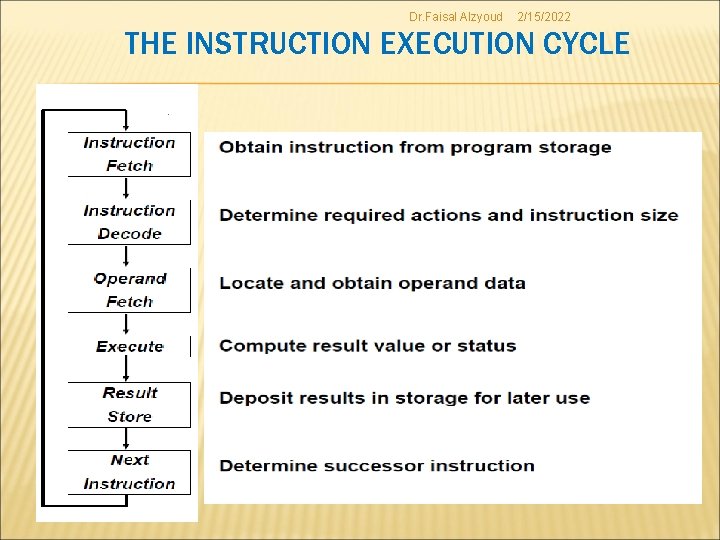

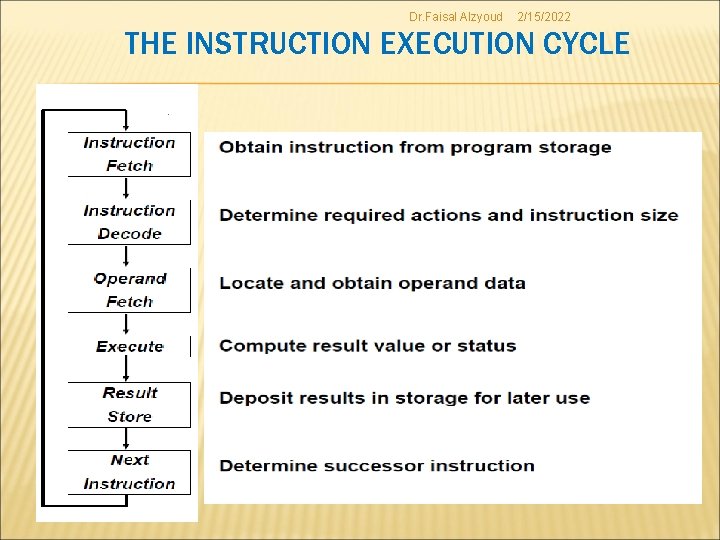

Dr. Faisal Alzyoud 2/15/2022 THE INSTRUCTION EXECUTION CYCLE

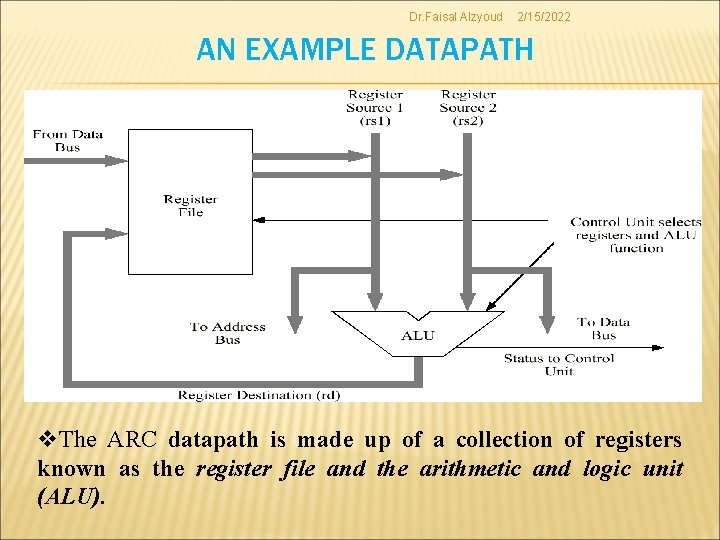

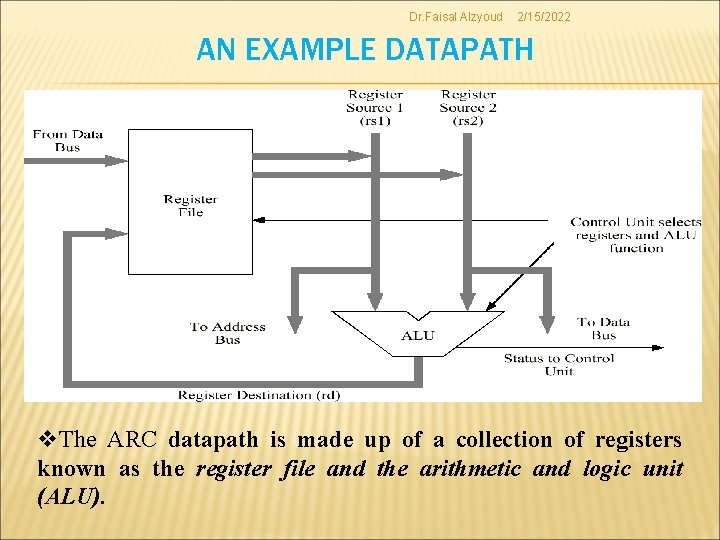

Dr. Faisal Alzyoud 2/15/2022 AN EXAMPLE DATAPATH v. The ARC datapath is made up of a collection of registers known as the register file and the arithmetic and logic unit (ALU).

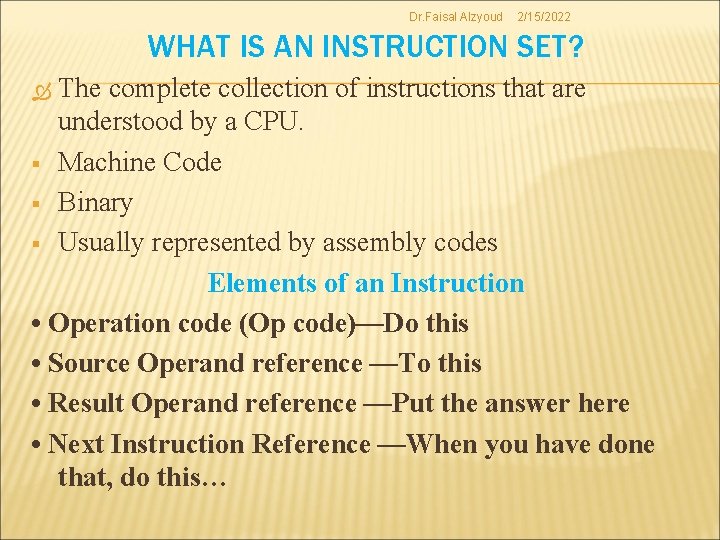

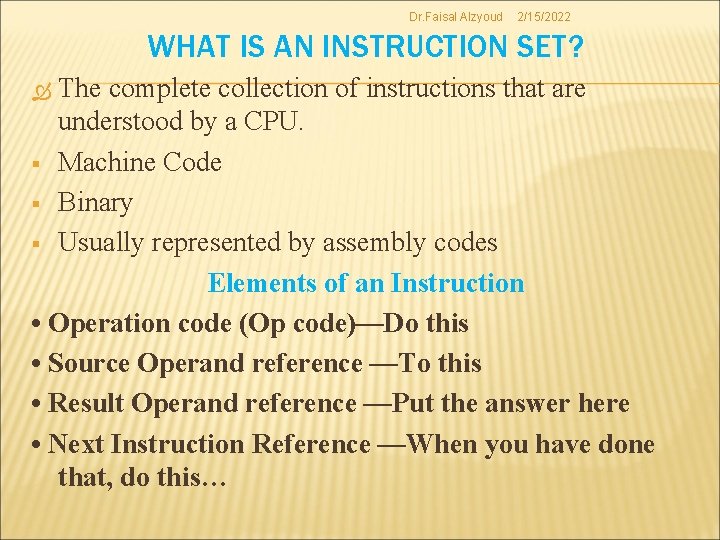

Dr. Faisal Alzyoud 2/15/2022 WHAT IS AN INSTRUCTION SET? The complete collection of instructions that are understood by a CPU. § Machine Code § Binary § Usually represented by assembly codes Elements of an Instruction • Operation code (Op code)—Do this • Source Operand reference —To this • Result Operand reference —Put the answer here • Next Instruction Reference —When you have done that, do this…

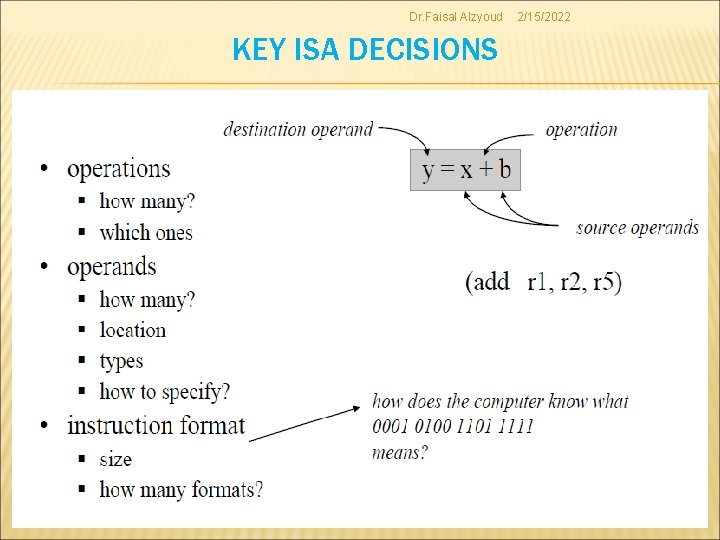

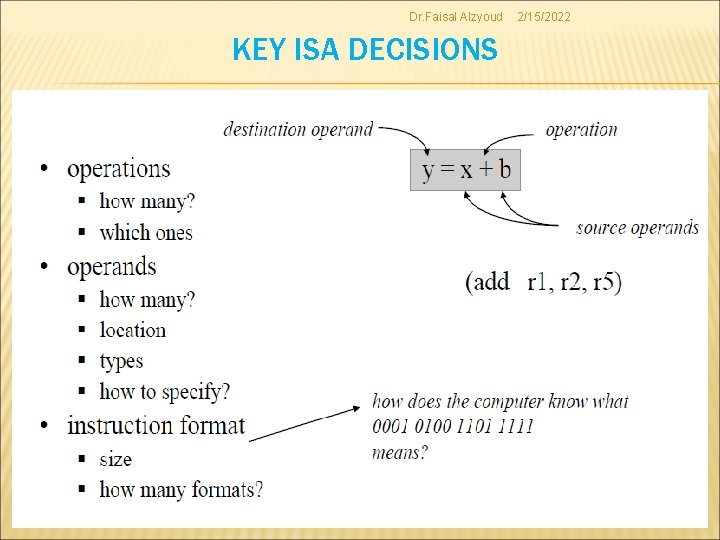

Dr. Faisal Alzyoud KEY ISA DECISIONS 2/15/2022

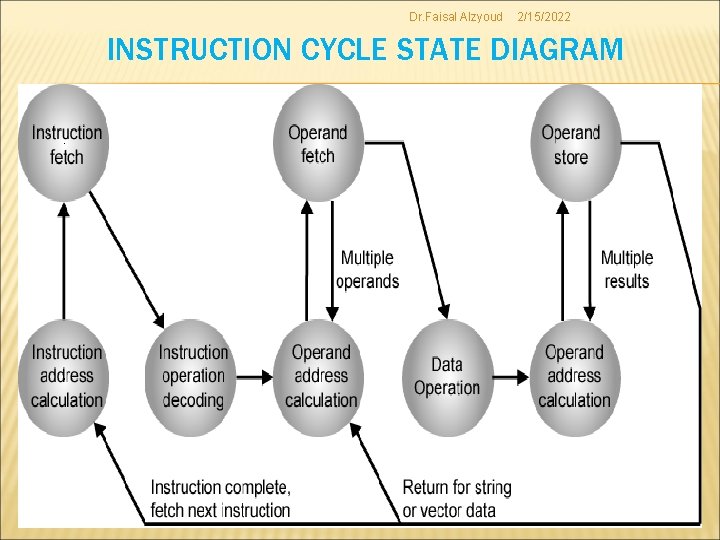

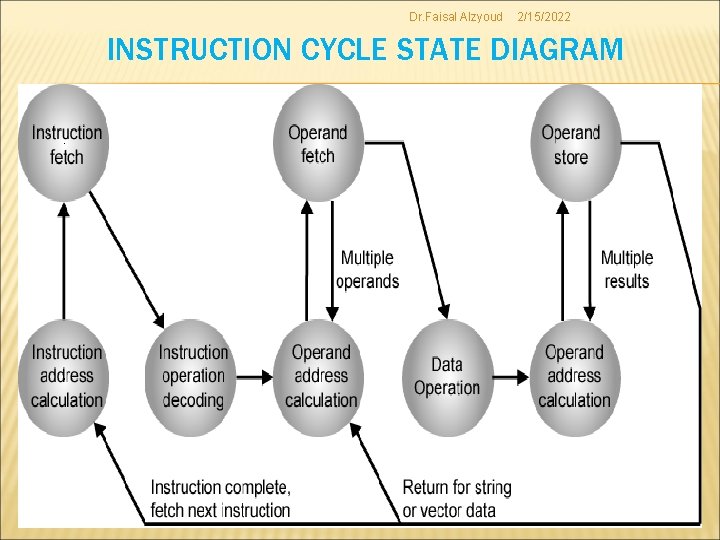

Dr. Faisal Alzyoud 2/15/2022 INSTRUCTION CYCLE STATE DIAGRAM

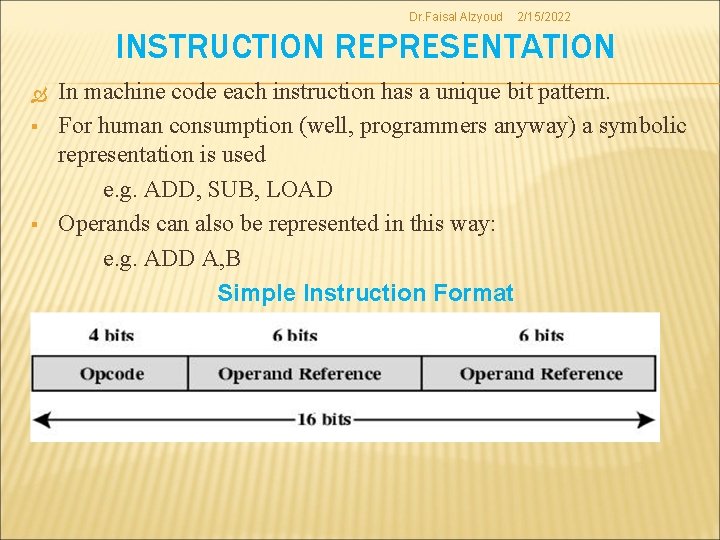

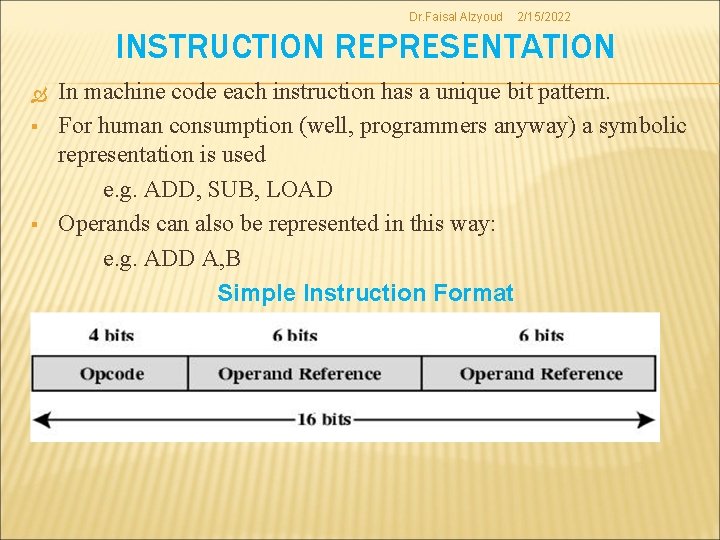

Dr. Faisal Alzyoud 2/15/2022 INSTRUCTION REPRESENTATION § § In machine code each instruction has a unique bit pattern. For human consumption (well, programmers anyway) a symbolic representation is used e. g. ADD, SUB, LOAD Operands can also be represented in this way: e. g. ADD A, B Simple Instruction Format

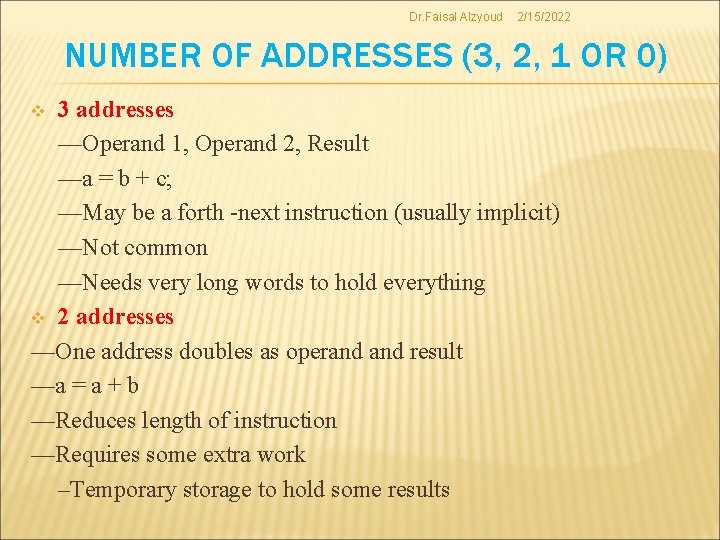

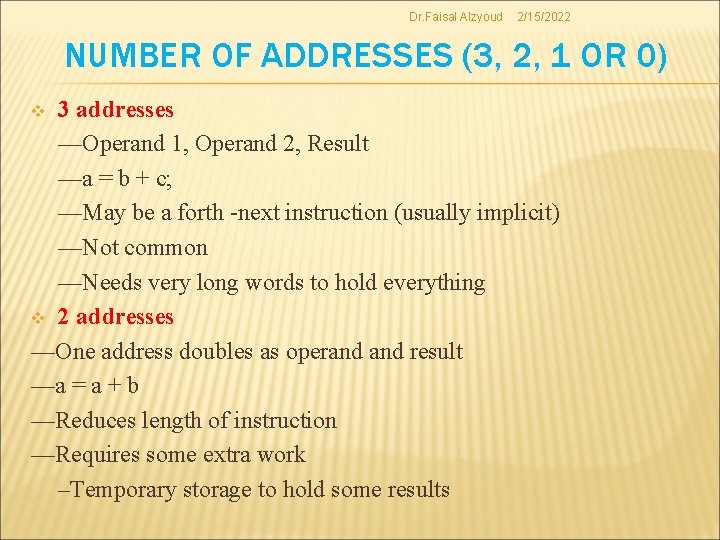

Dr. Faisal Alzyoud 2/15/2022 NUMBER OF ADDRESSES (3, 2, 1 OR 0) 3 addresses —Operand 1, Operand 2, Result —a = b + c; —May be a forth -next instruction (usually implicit) —Not common —Needs very long words to hold everything v 2 addresses —One address doubles as operand result —a = a + b —Reduces length of instruction —Requires some extra work –Temporary storage to hold some results v

Dr. Faisal Alzyoud 2/15/2022 NUMBER OF ADDRESSES (3, 2, 1 OR 0)…. CONT. 1 address —Implicit second address —Usually a register (accumulator) —Common on early machines v 0 (zero) addresses —All addresses implicit —Uses a stack e. g. push a, push b, add, pop c, in order to execute c = a + b v

Dr. Faisal Alzyoud 2/15/2022 HOW MANY ADDRESSES v o o o More addresses More complex (powerful? ) instructions More registers (Inter-register operations are quicker) Fewer instructions per program Fewer addresses Less complex (powerful? ) instructions More instructions per program Faster fetch/execution of instructions

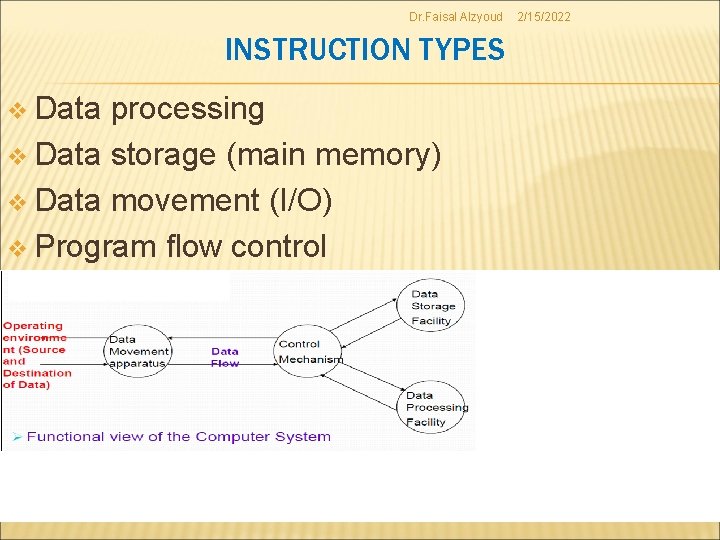

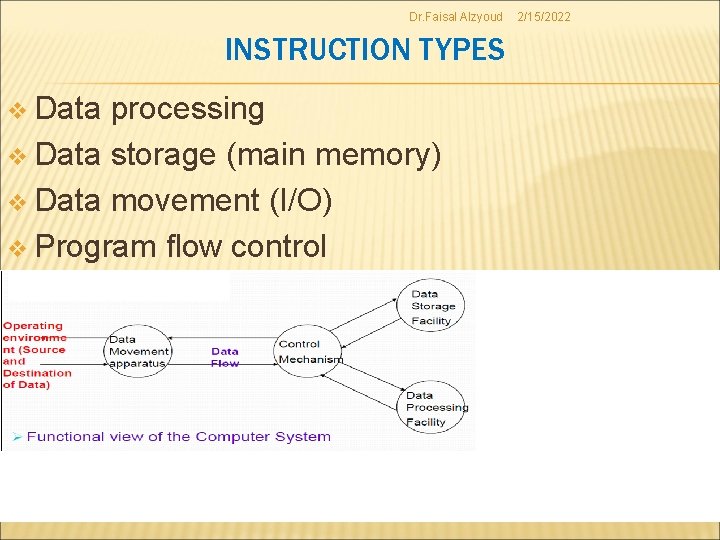

Dr. Faisal Alzyoud INSTRUCTION TYPES v Data processing v Data storage (main memory) v Data movement (I/O) v Program flow control 2/15/2022

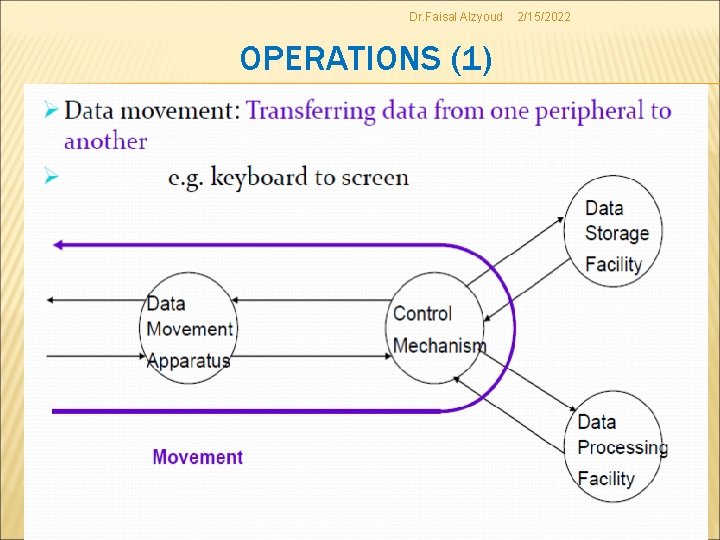

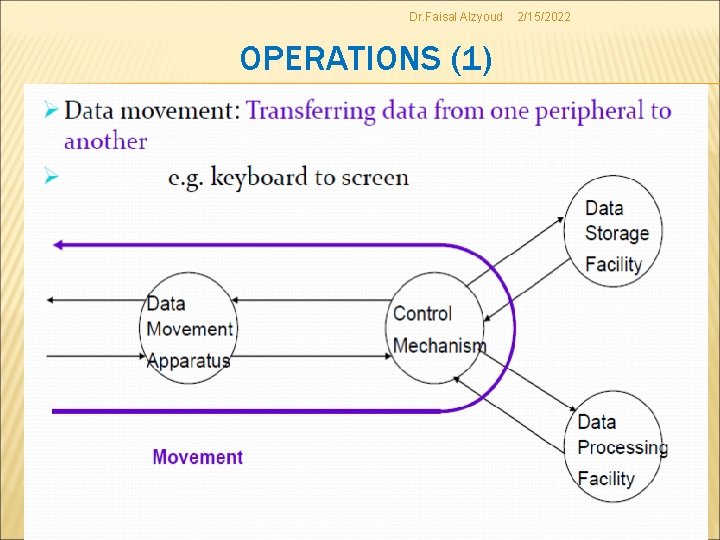

Dr. Faisal Alzyoud OPERATIONS (1) 2/15/2022

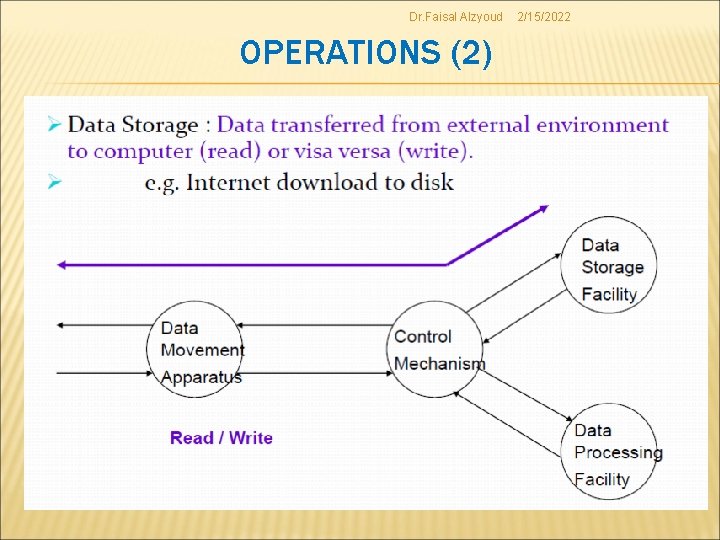

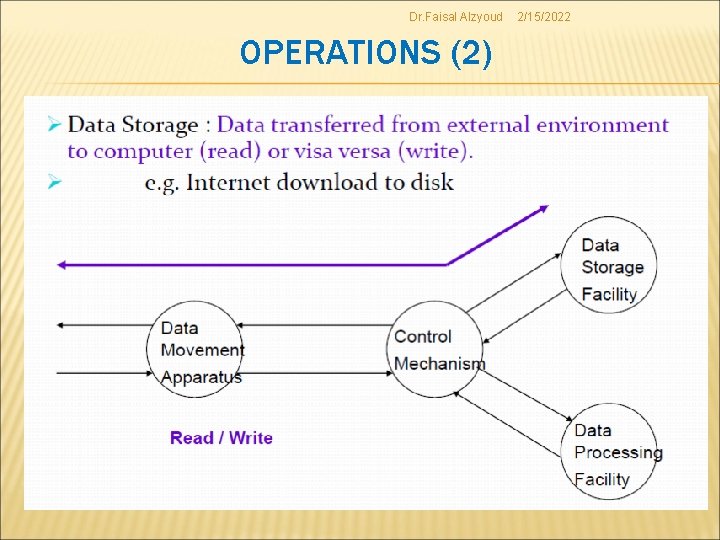

Dr. Faisal Alzyoud OPERATIONS (2) 2/15/2022

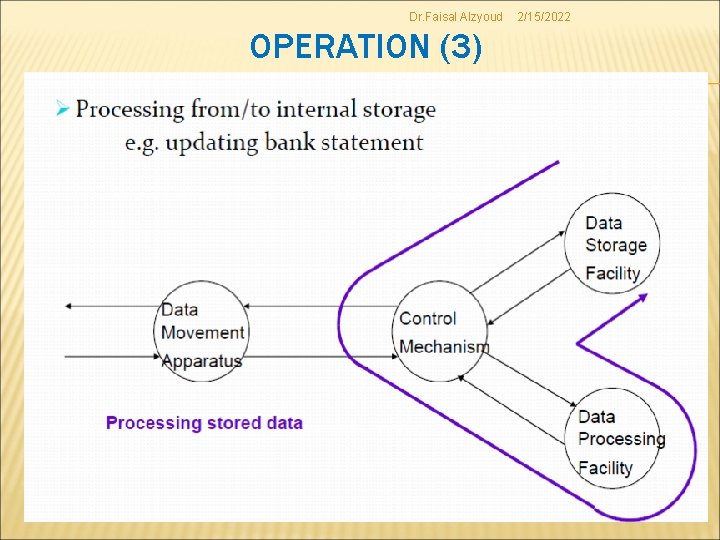

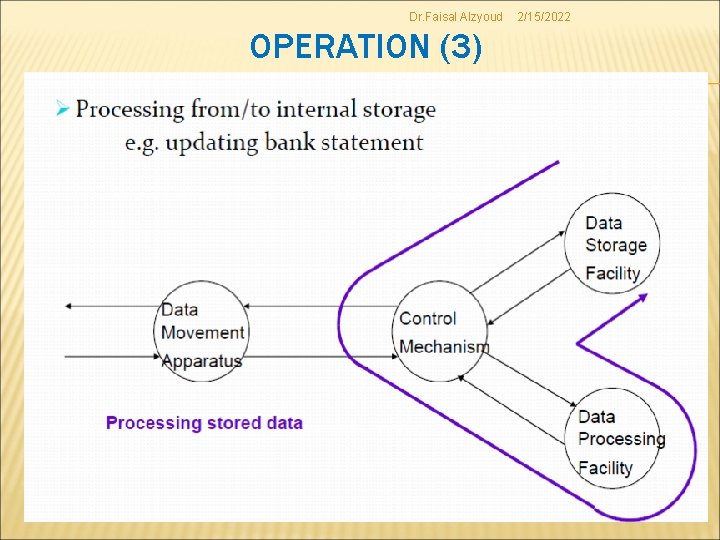

Dr. Faisal Alzyoud OPERATION (3) 2/15/2022

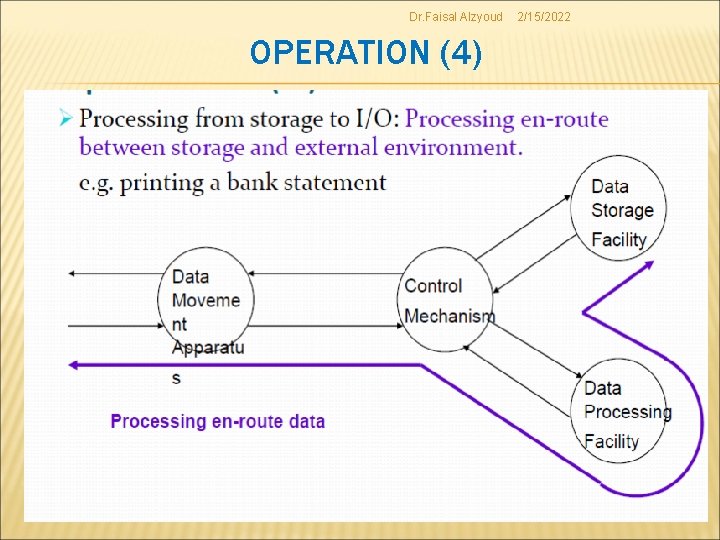

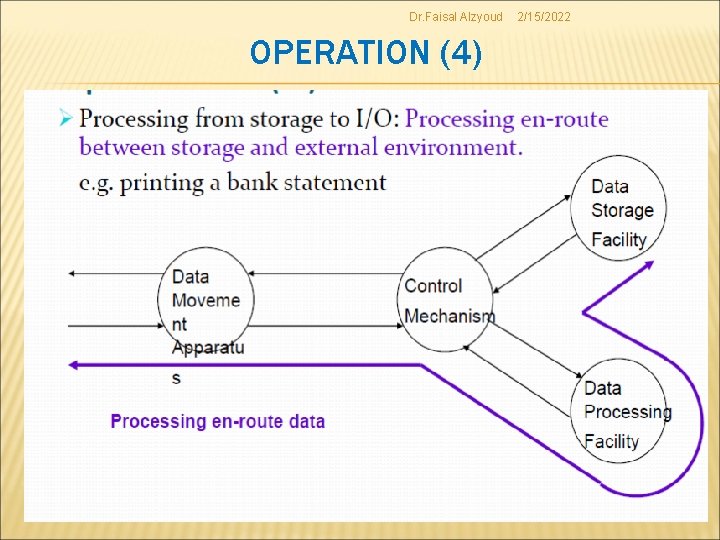

Dr. Faisal Alzyoud OPERATION (4) 2/15/2022

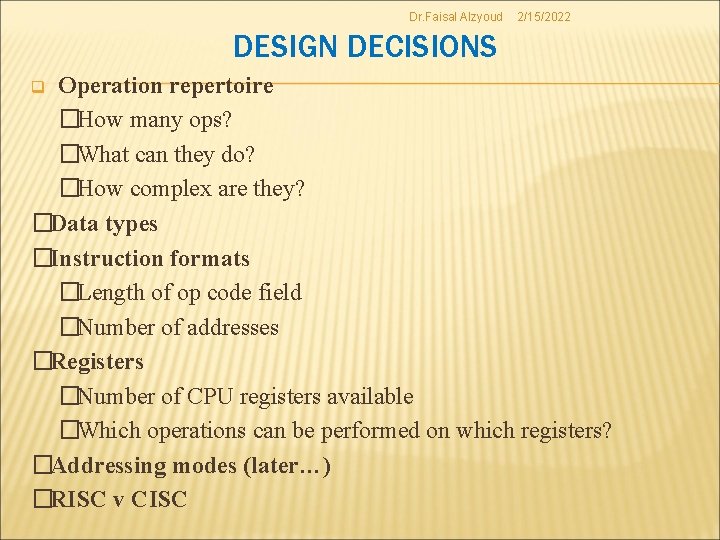

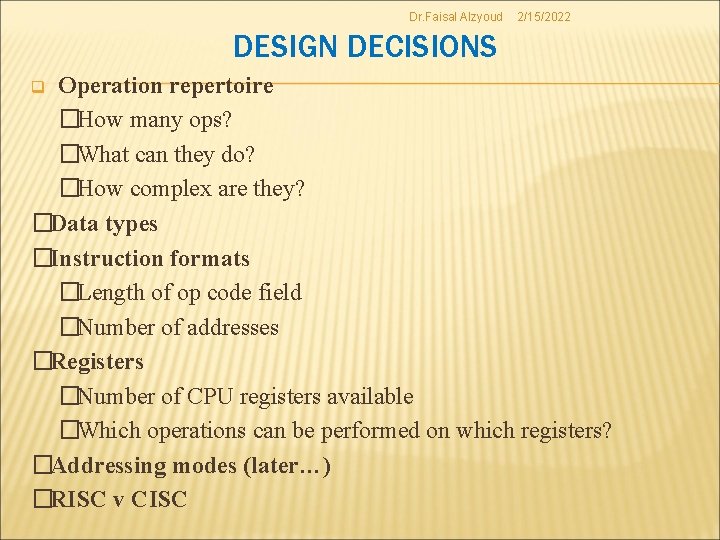

Dr. Faisal Alzyoud 2/15/2022 DESIGN DECISIONS Operation repertoire �How many ops? �What can they do? �How complex are they? �Data types �Instruction formats �Length of op code field �Number of addresses �Registers �Number of CPU registers available �Which operations can be performed on which registers? �Addressing modes (later…) �RISC v CISC q

Dr. Faisal Alzyoud 2/15/2022 TYPES OF OPERAND Addresses �Numbers �Integer/floating point �Characters �ASCII etc. �Logical Data �Bits or flags �(Aside: Is there any difference between numbers and characters? Ask a C programmer!) q

Dr. Faisal Alzyoud 2/15/2022 TYPES OF OPERATION q Data Transfer �Arithmetic �Logical Types of operations �Conversion �I/O �System Control �Transfer of Control

Dr. Faisal Alzyoud DATA TRANSFER 2/15/2022 Specify �Source �Destination �Amount of data �May be different instructions for different movements �e. g. IBM 370 �Or one instruction and different addresses �e. g. VAX (Variable-length instructions (Intel 80 x 86, VAX) require multi-step fetch and decode, but allow for a much more flexible and compact instruction set. Fixed-length instructions allow easy fetch and decode, and simplify pipelining and parallelism. All MIPS instructions are 32 bits long. –this decision impacts every other ISA decision we make because it makes instruction bits scarce. q

Dr. Faisal Alzyoud Arithmetic �Add, Subtract, Multiply, Divide �Signed Integer �Floating point ? �May include �Increment (a++) �Decrement (a--) �Negate (-a) q Logical �Bitwise operations �AND, OR, NOT Conversion �E. g. Binary to Decimal q 2/15/2022

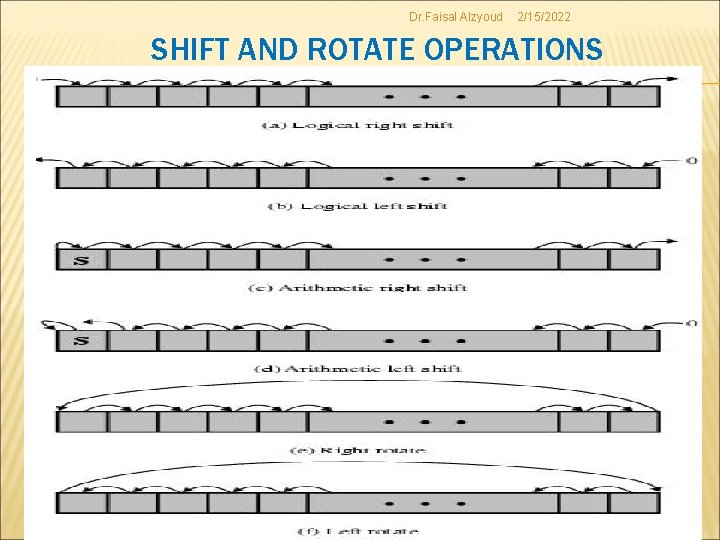

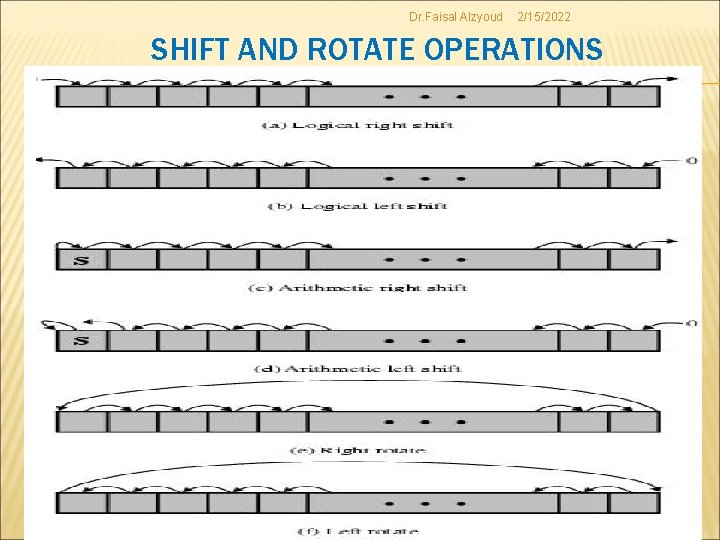

Dr. Faisal Alzyoud 2/15/2022 SHIFT AND ROTATE OPERATIONS

Dr. Faisal Alzyoud 2/15/2022 Input/Output �May be specific instructions �May be done using data movement instructions (memory mapped) �May be done by a separate controller (DMA) q �Systems Control �Privileged instructions �CPU needs to be in specific state —Ring 0 on 80386+ —Kernel mode �For operating systems use

Dr. Faisal Alzyoud Transfer of Control � Branch —e. g. branch to x if result is zero � Skip —e. g. increment and skip if zero q —ISZ Register 1 —Branch xxxx —ADD A � Subroutine call —c. f. interrupt call (next slide) 2/15/2022

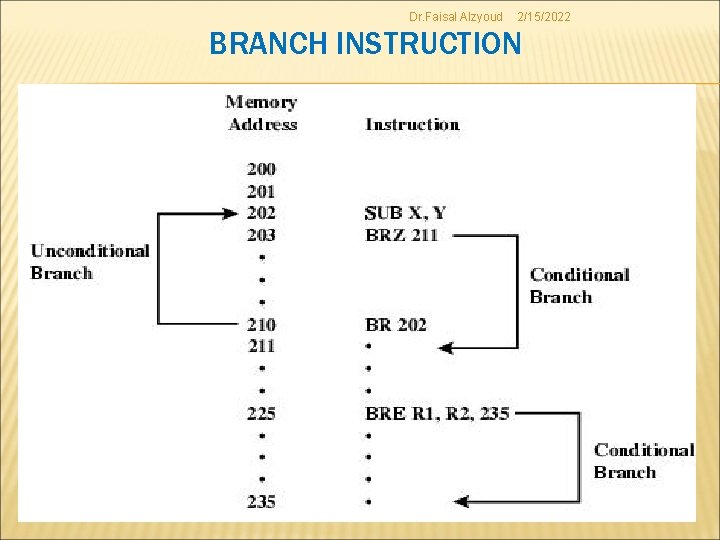

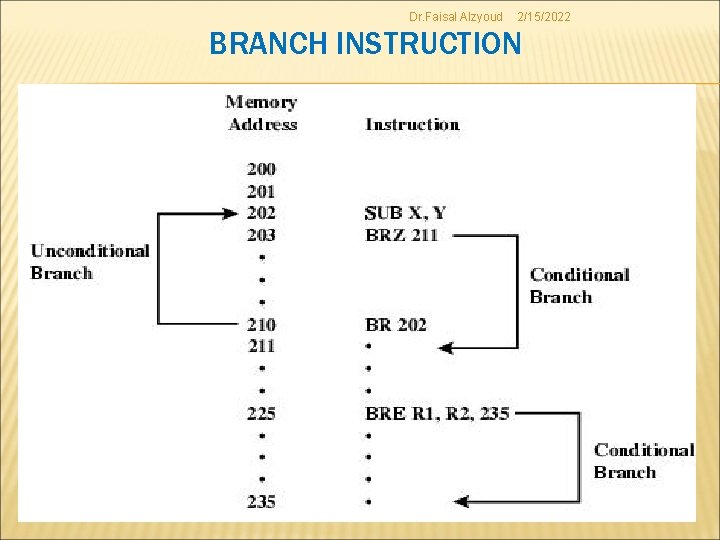

Dr. Faisal Alzyoud 2/15/2022 BRANCH INSTRUCTION

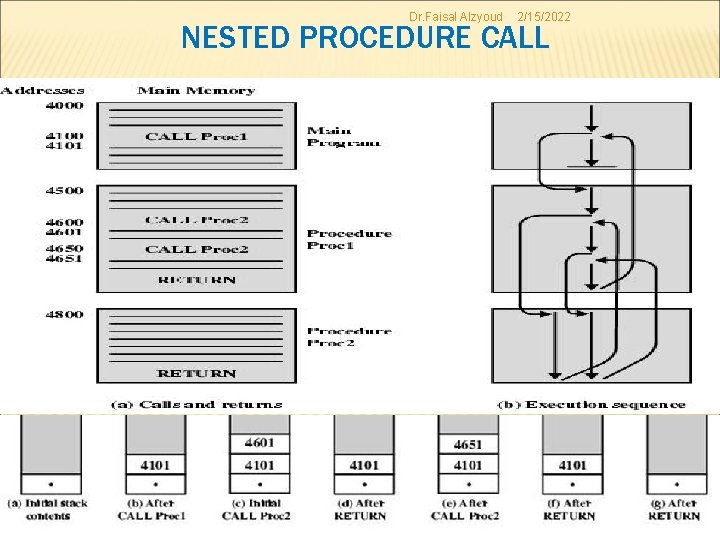

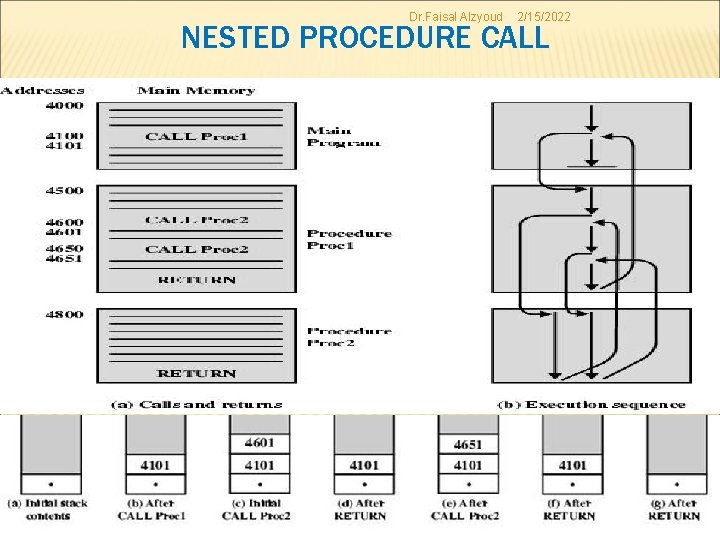

Dr. Faisal Alzyoud 2/15/2022 NESTED PROCEDURE CALL

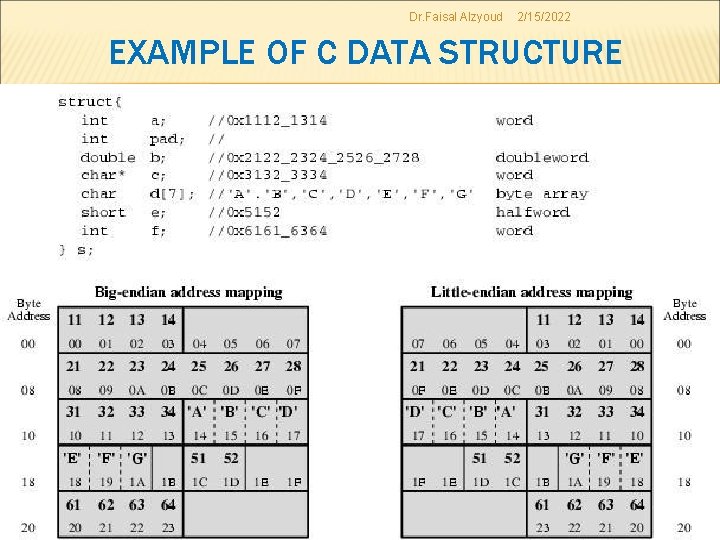

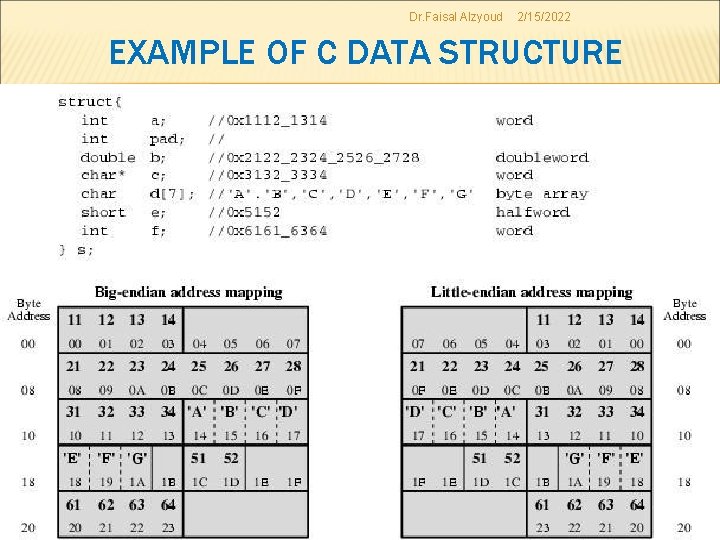

Dr. Faisal Alzyoud 2/15/2022 EXAMPLE OF C DATA STRUCTURE

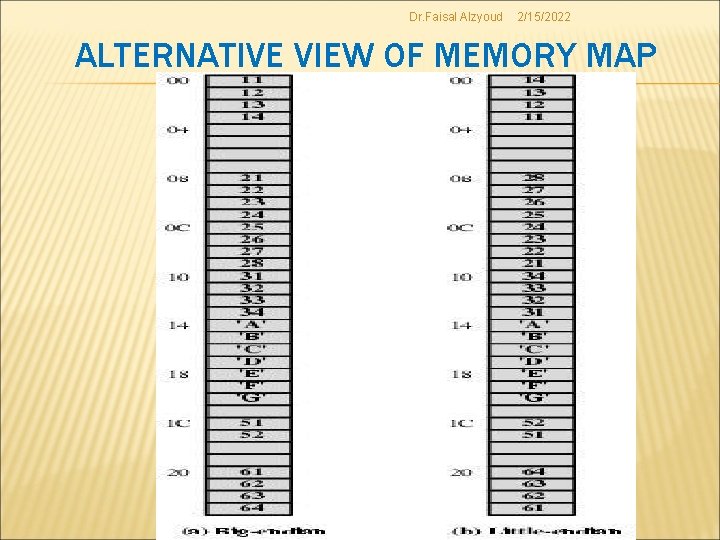

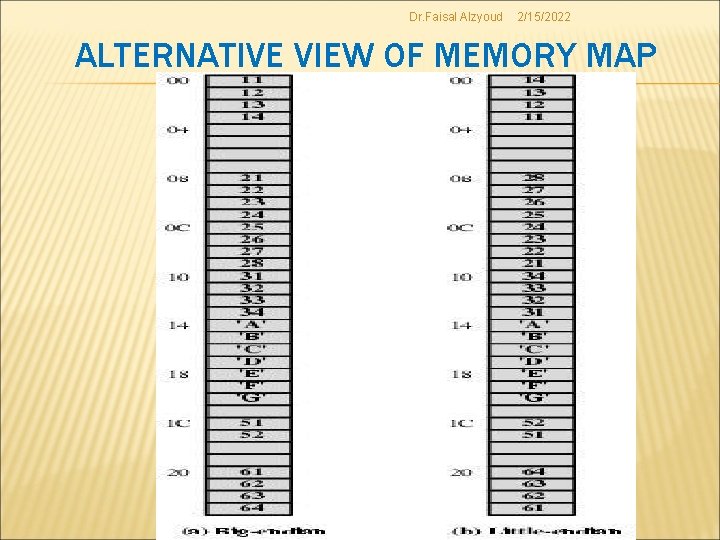

Dr. Faisal Alzyoud 2/15/2022 ALTERNATIVE VIEW OF MEMORY MAP

Dr. Faisal Alzyoud 2/15/2022 STANDARD…WHAT STANDARD? q Pentium (80 x 86), VAX are little-endian �IBM 370, Moterola 680 x 0 (Mac), and most RISC are big-endian �Internet is big-endian —Makes writing Internet programs on PC more awkward! —Win. Sock provides htoiand itoh(Host to Internet & Internet to Host) functions to convert