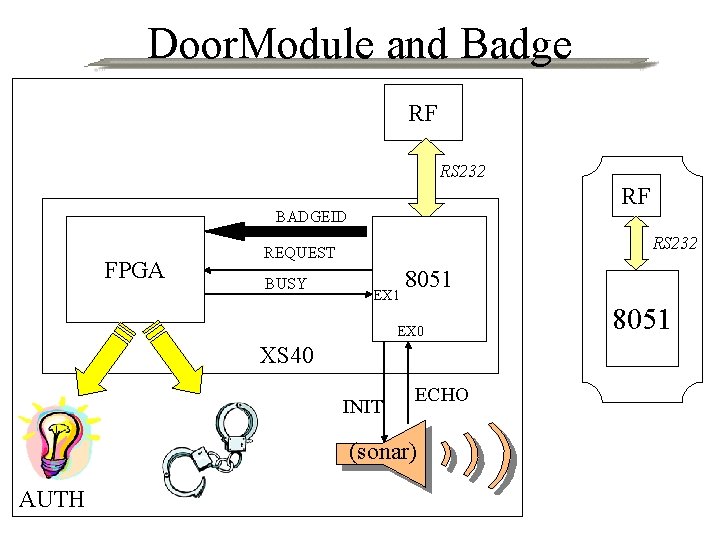

Door Module and Badge RF RS 232 RF

Door. Module and Badge RF RS 232 RF BADGEID FPGA RS 232 REQUEST BUSY XS 40 EX 1 8051 EX 0 XS 40 INIT ECHO (sonar) AUTH 8051

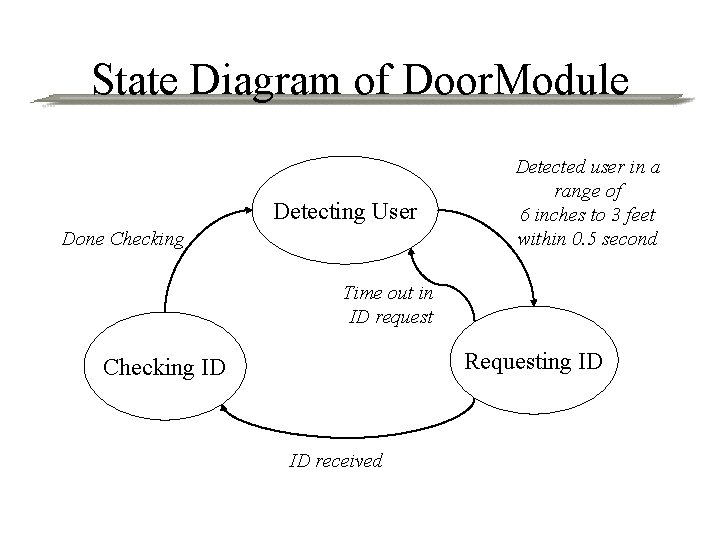

State Diagram of Door. Module Detecting User Done Checking Detected user in a range of 6 inches to 3 feet within 0. 5 second Time out in ID request Requesting ID Checking ID ID received

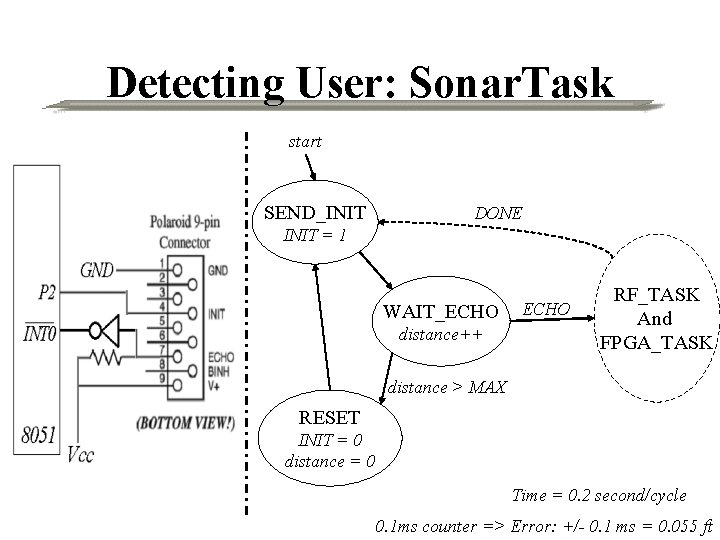

Detecting User: Sonar. Task start SEND_INIT DONE INIT = 1 WAIT_ECHO distance++ ECHO RF_TASK And FPGA_TASK distance > MAX RESET INIT = 0 distance = 0 Time = 0. 2 second/cycle 0. 1 ms counter => Error: +/- 0. 1 ms = 0. 055 ft

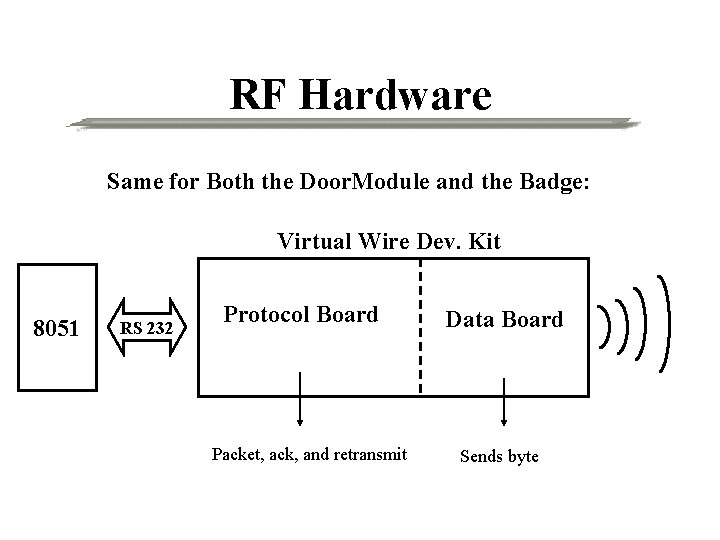

RF Hardware Same for Both the Door. Module and the Badge: Virtual Wire Dev. Kit 8051 RS 232 Protocol Board Packet, ack, and retransmit Data Board Sends byte

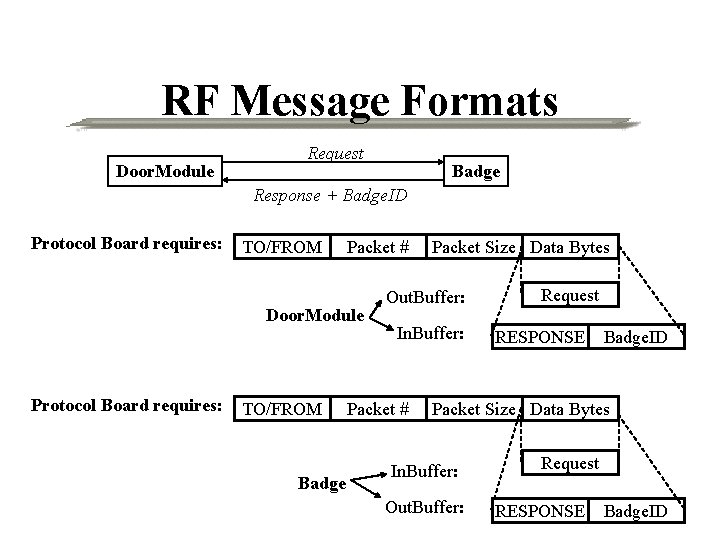

RF Message Formats Door. Module Request Badge Response + Badge. ID Protocol Board requires: TO/FROM Packet # Door. Module Protocol Board requires: TO/FROM Badge Packet Size Data Bytes Out. Buffer: In. Buffer: Packet # Request RESPONSE Badge. ID Packet Size Data Bytes In. Buffer: Out. Buffer: Request RESPONSE Badge. ID

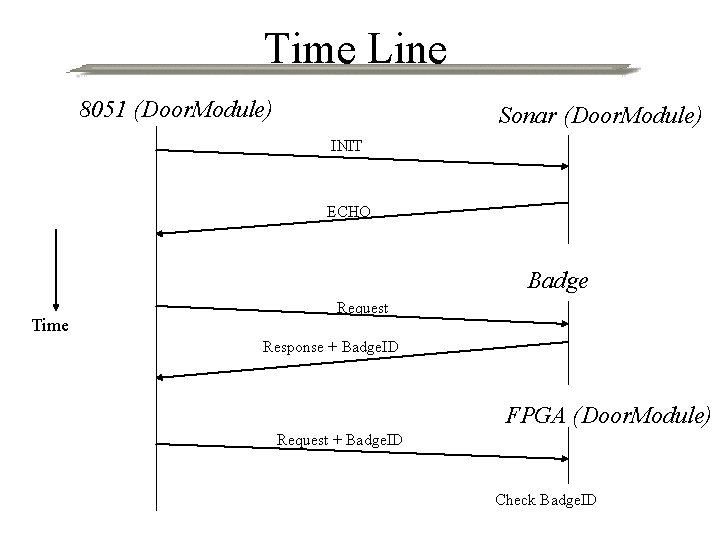

Time Line 8051 (Door. Module) Sonar (Door. Module) INIT ECHO Badge Time Request Response + Badge. ID FPGA (Door. Module) Request + Badge. ID Check Badge. ID

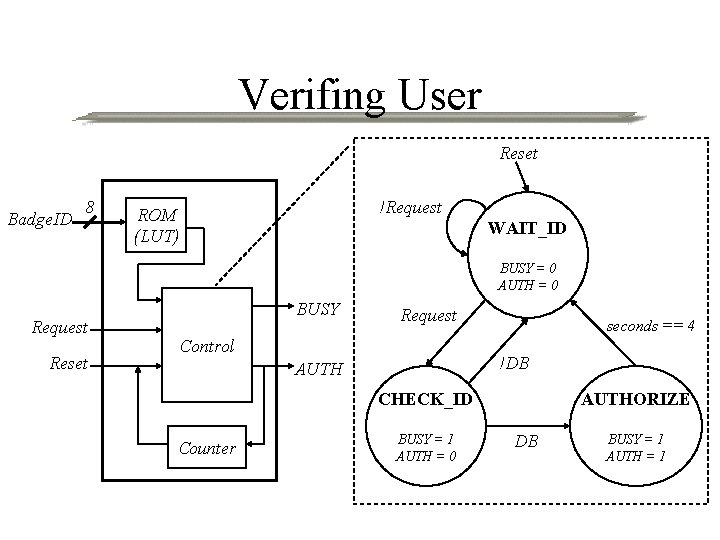

Verifing User Reset Badge. ID 8 !Request ROM (LUT) WAIT_ID BUSY = 0 AUTH = 0 Request Reset BUSY Request Control seconds == 4 !DB AUTH CHECK_ID Counter BUSY = 1 AUTH = 0 AUTHORIZE DB BUSY = 1 AUTH = 1

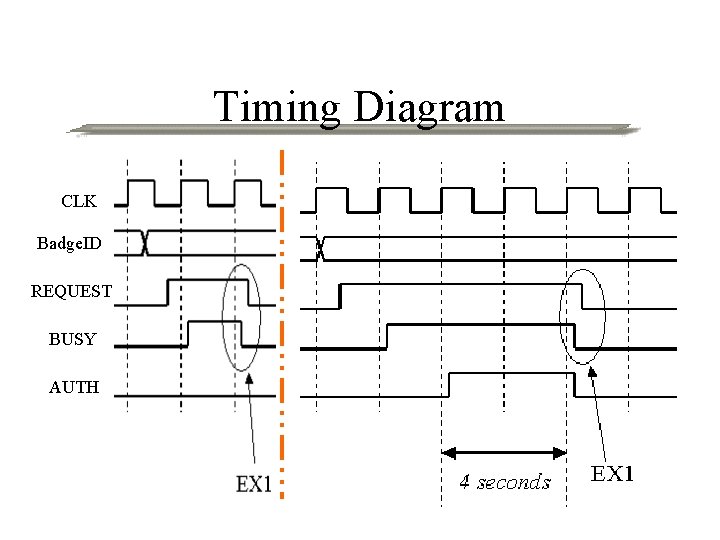

Timing Diagram CLK Badge. ID REQUEST BUSY AUTH

Current Status Done: • • Detect a user within 6 inches to 3 feet. Detect a user within 0. 5 second. RF messaging protocol. Built the badge. In progress: • Debugging the badge. • Implementation and debugging of FPGA.

Summary • Hand-free and preserve security checking. • Final technical design of the Door. Module and the Badge. – Sonar detects user intention. – RF exchanges user information. – FPGA does the checking. • Analysis/data/results show our design will meet the requirement. • Current schedule • Coming soon…… – Product demo.

- Slides: 10