DMA Direct Memory Access Chapter 19 Sepehr Naimi

- Slides: 17

DMA (Direct Memory Access) Chapter 19 Sepehr Naimi www. Nicer. Land. com

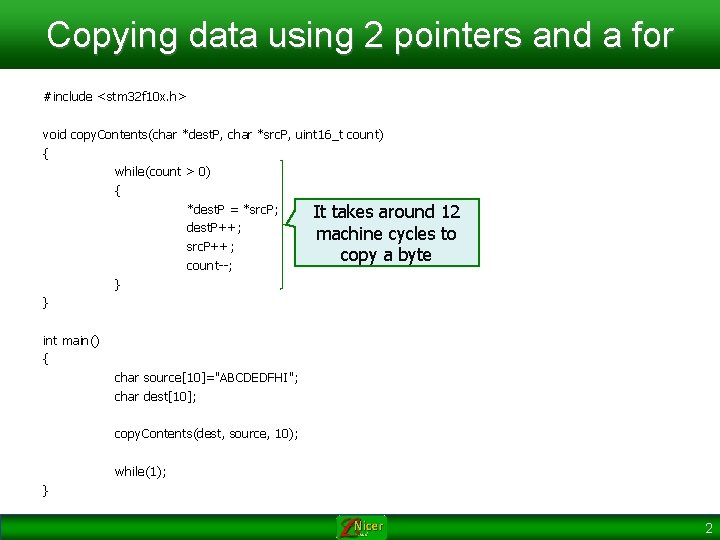

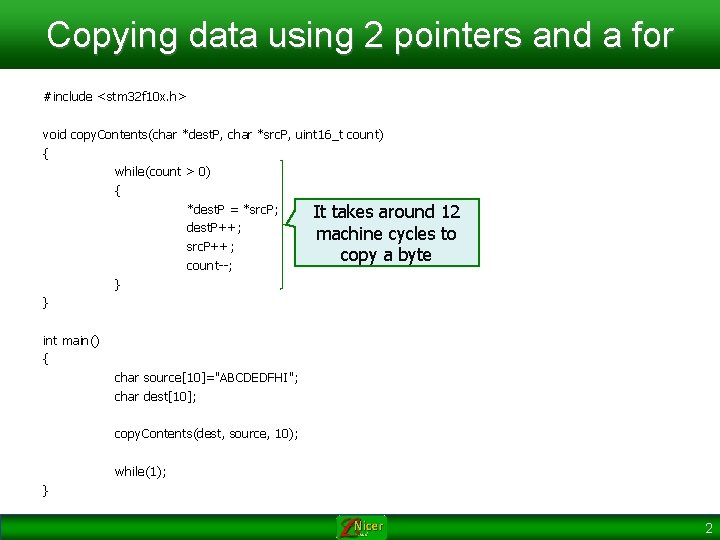

Copying data using 2 pointers and a for #include <stm 32 f 10 x. h> void copy. Contents(char *dest. P, char *src. P, uint 16_t count) { while(count > 0) { *dest. P = *src. P; It takes around dest. P++; machine cycles src. P++; copy a byte count--; } } 12 to int main() { char source[10]="ABCDEDFHI"; char dest[10]; copy. Contents(dest, source, 10); while(1); } 2

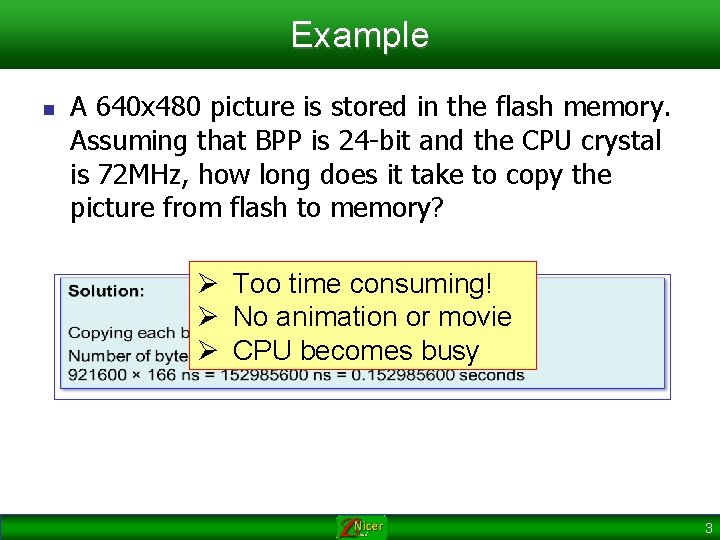

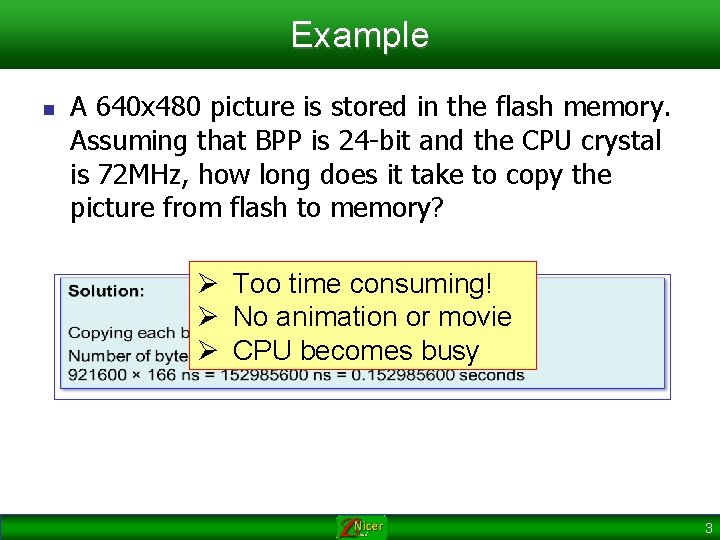

Example n A 640 x 480 picture is stored in the flash memory. Assuming that BPP is 24 -bit and the CPU crystal is 72 MHz, how long does it take to copy the picture from flash to memory? Ø Too time consuming! Ø No animation or movie Ø CPU becomes busy 3

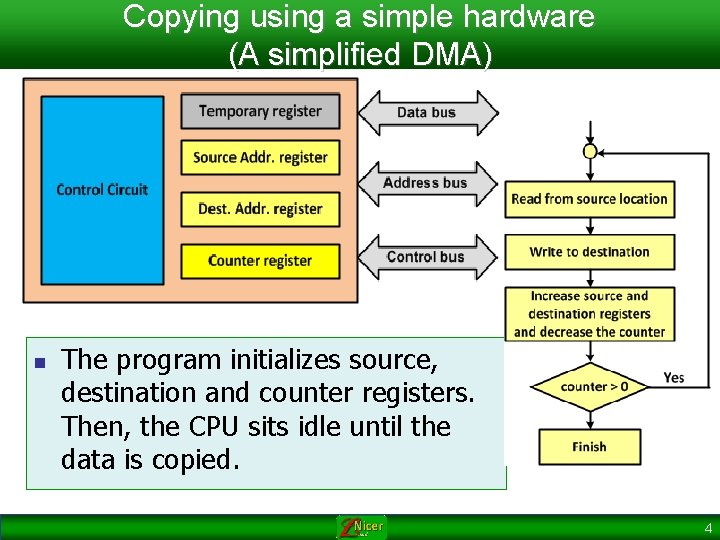

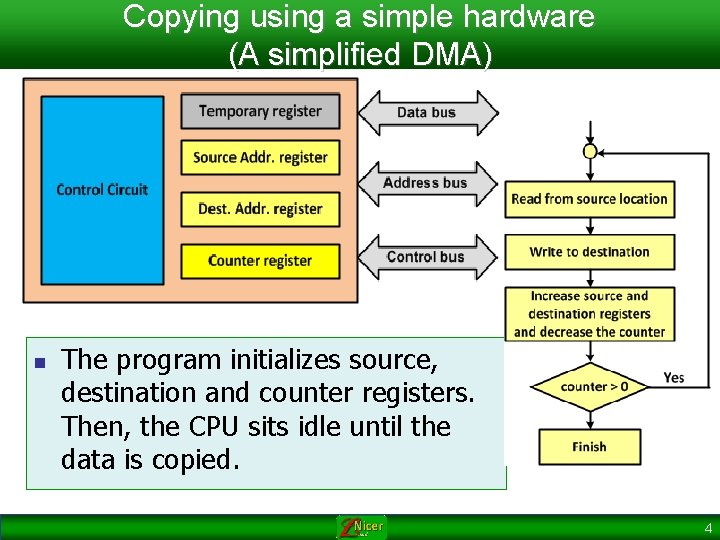

Copying using a simple hardware (A simplified DMA) n The program initializes source, destination and counter registers. Then, the CPU sits idle until the data is copied. 4

In real DMA controllers n n There are more than 1 channel for copying Peripherals can ask the DMA to begin copying (they can send DMA request) 5

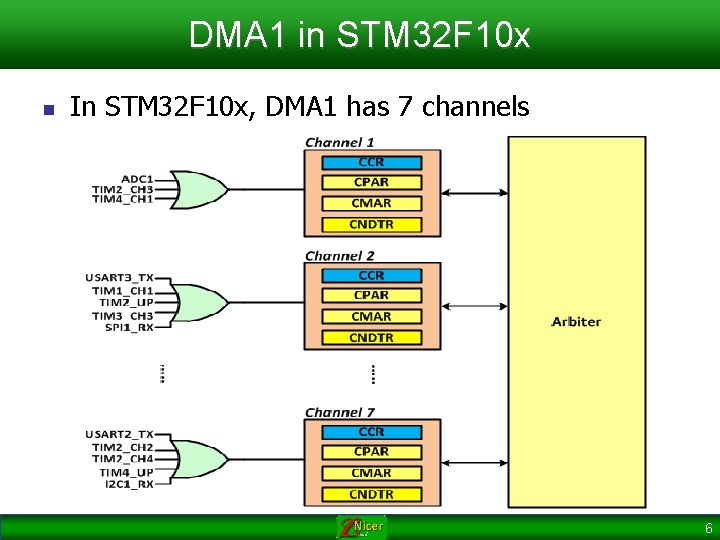

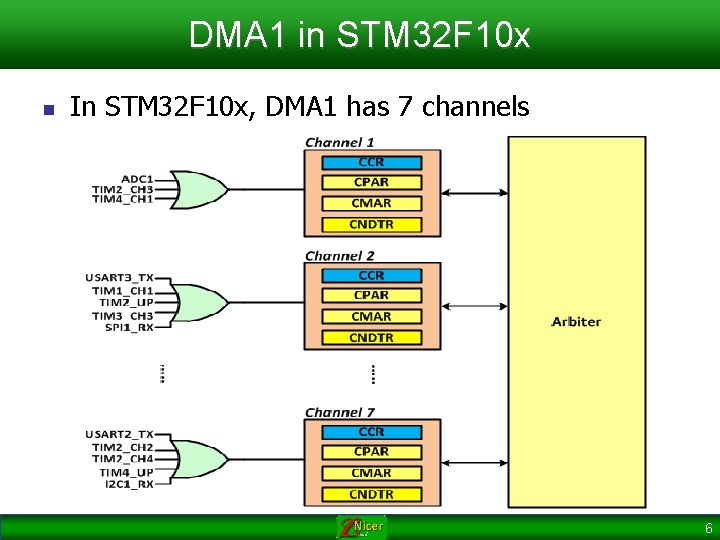

DMA 1 in STM 32 F 10 x n In STM 32 F 10 x, DMA 1 has 7 channels 6

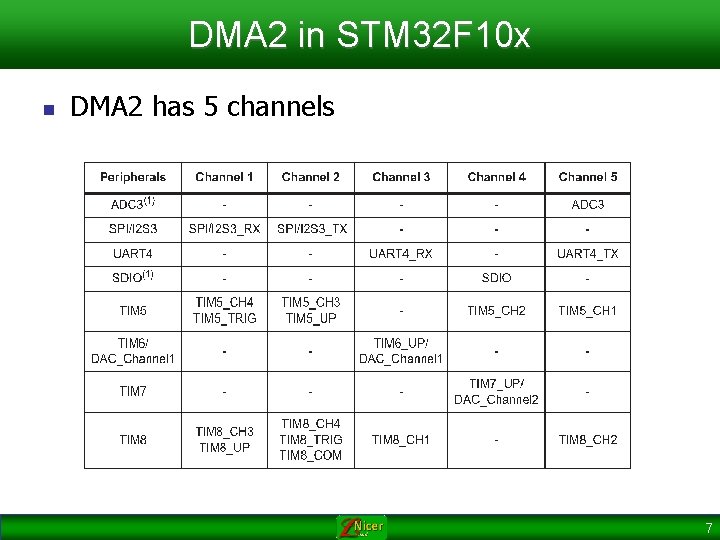

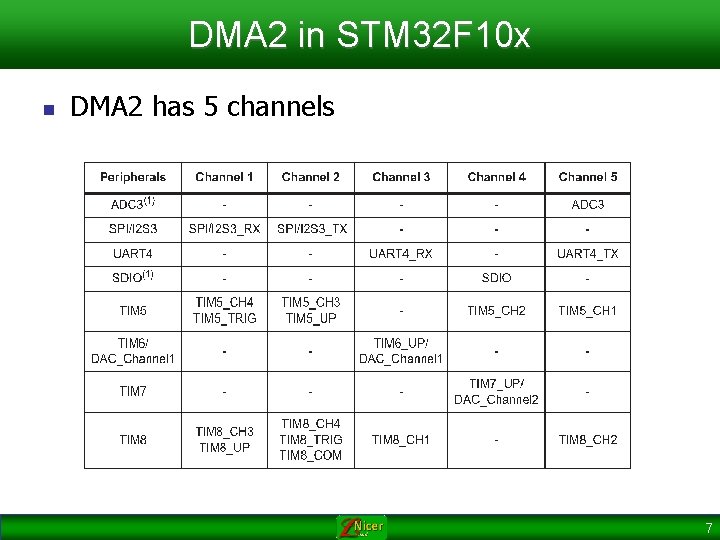

DMA 2 in STM 32 F 10 x n DMA 2 has 5 channels 7

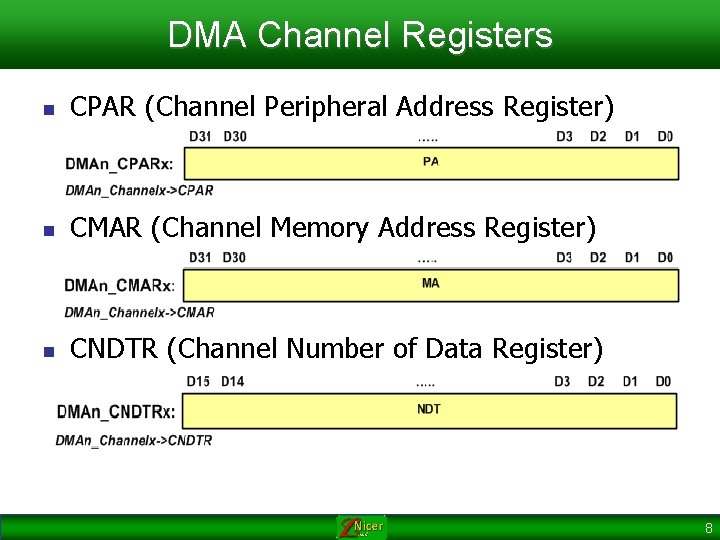

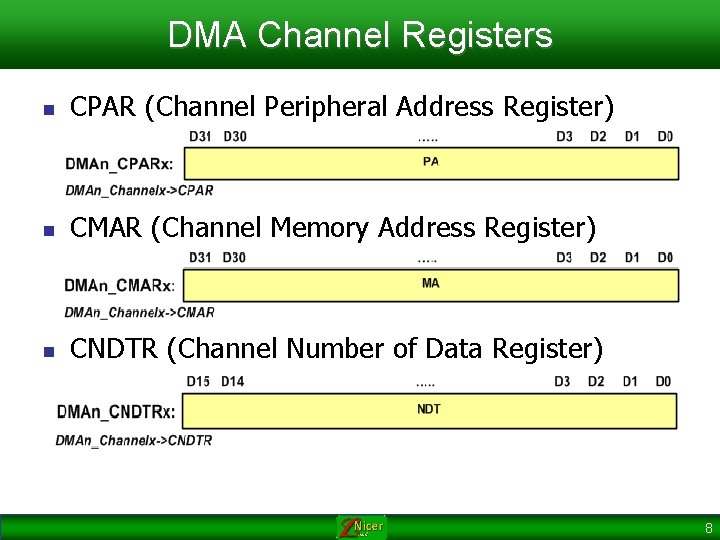

DMA Channel Registers n CPAR (Channel Peripheral Address Register) n CMAR (Channel Memory Address Register) n CNDTR (Channel Number of Data Register) 8

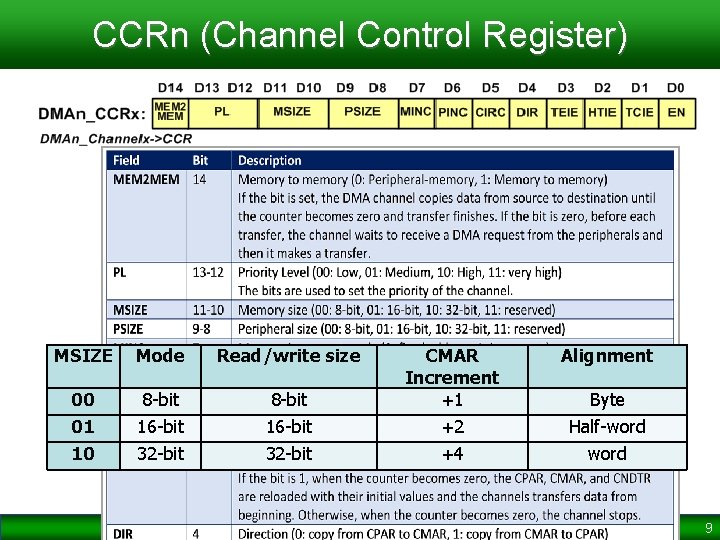

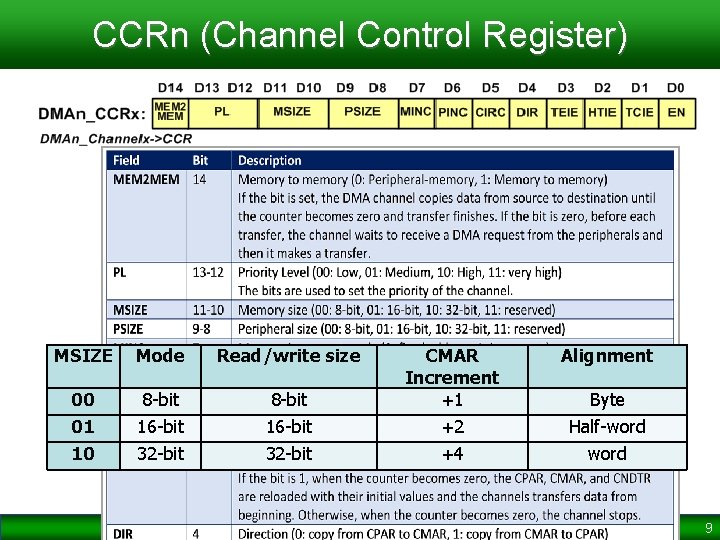

CCRn (Channel Control Register) MSIZE Mode Read/write size Alignment 8 -bit CMAR Increment +1 00 8 -bit 01 16 -bit +2 Half-word 10 32 -bit +4 word Byte 9

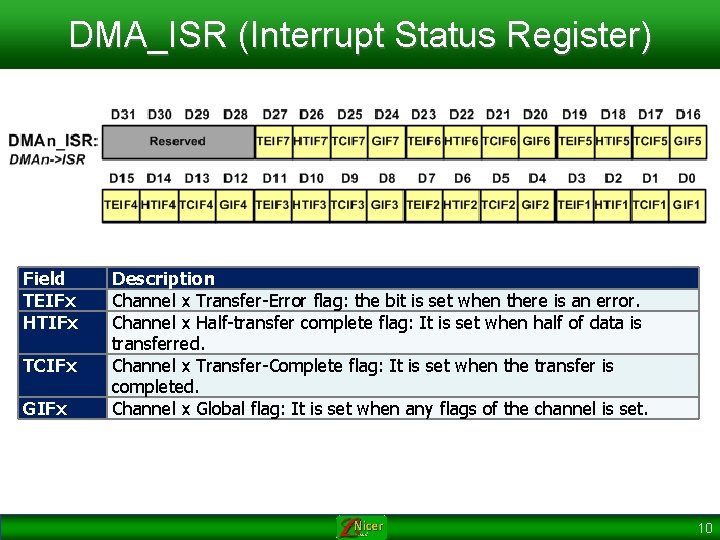

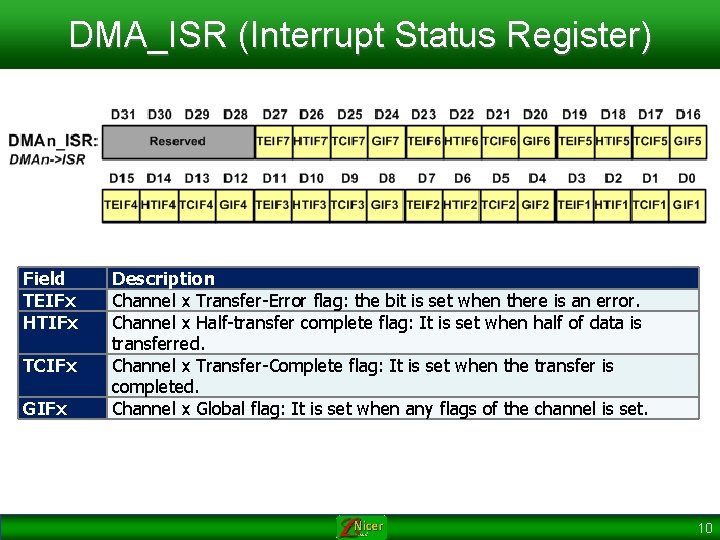

DMA_ISR (Interrupt Status Register) Field TEIFx HTIFx TCIFx GIFx Description Channel x Transfer-Error flag: the bit is set when there is an error. Channel x Half-transfer complete flag: It is set when half of data is transferred. Channel x Transfer-Complete flag: It is set when the transfer is completed. Channel x Global flag: It is set when any flags of the channel is set. 10

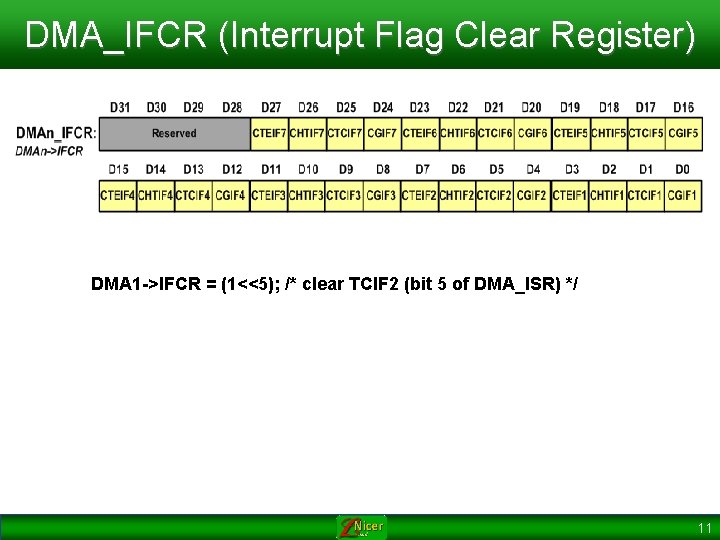

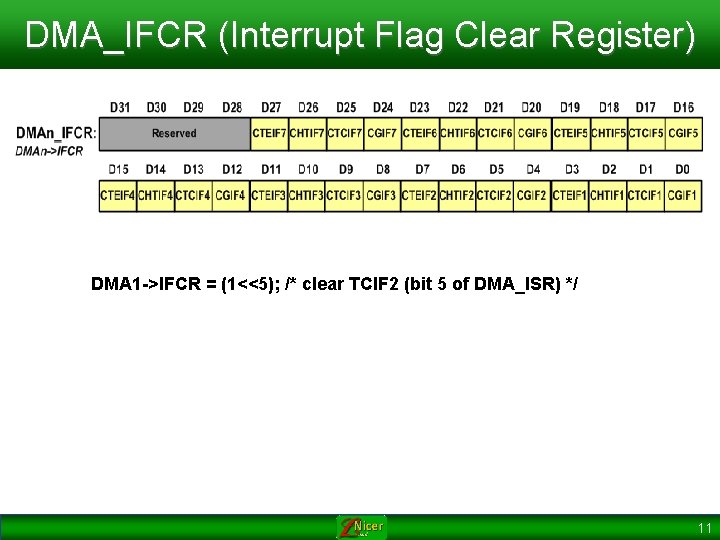

DMA_IFCR (Interrupt Flag Clear Register) DMA 1 ->IFCR = (1<<5); /* clear TCIF 2 (bit 5 of DMA_ISR) */ 11

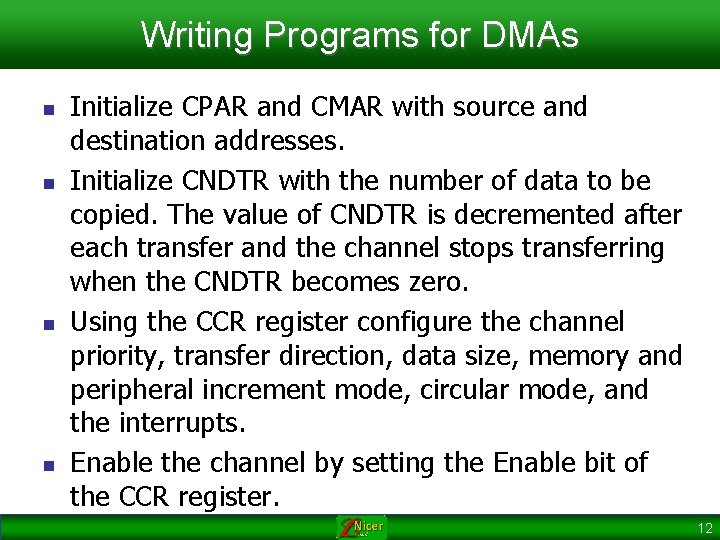

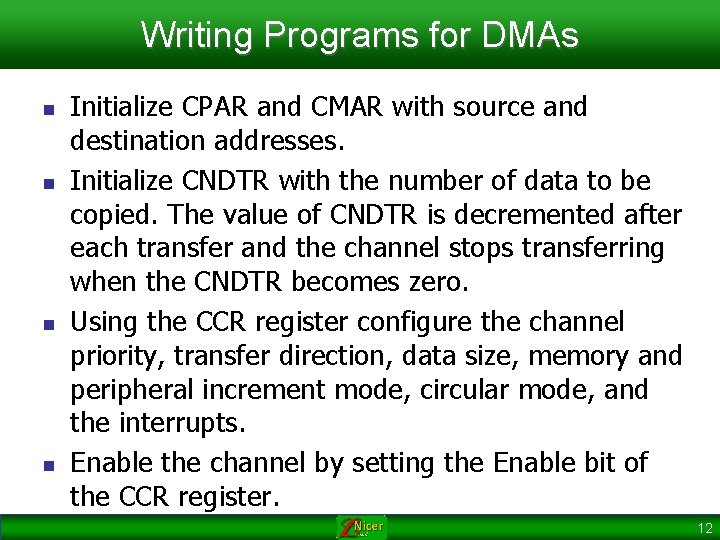

Writing Programs for DMAs n n Initialize CPAR and CMAR with source and destination addresses. Initialize CNDTR with the number of data to be copied. The value of CNDTR is decremented after each transfer and the channel stops transferring when the CNDTR becomes zero. Using the CCR register configure the channel priority, transfer direction, data size, memory and peripheral increment mode, circular mode, and the interrupts. Enable the channel by setting the Enable bit of the CCR register. 12

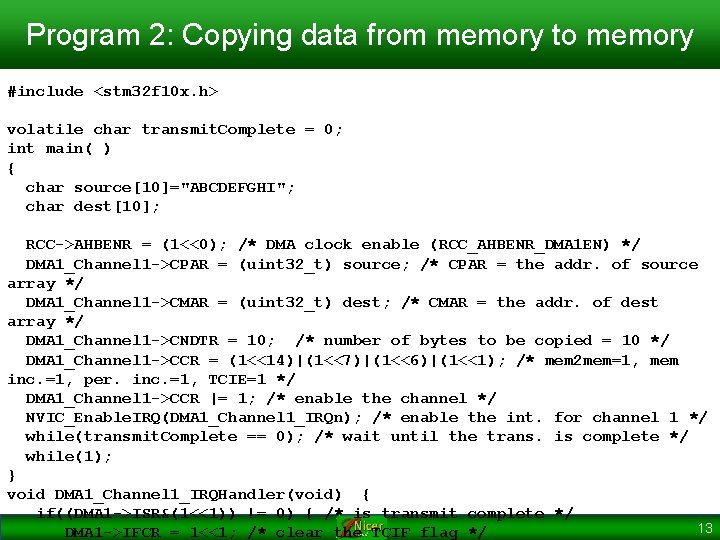

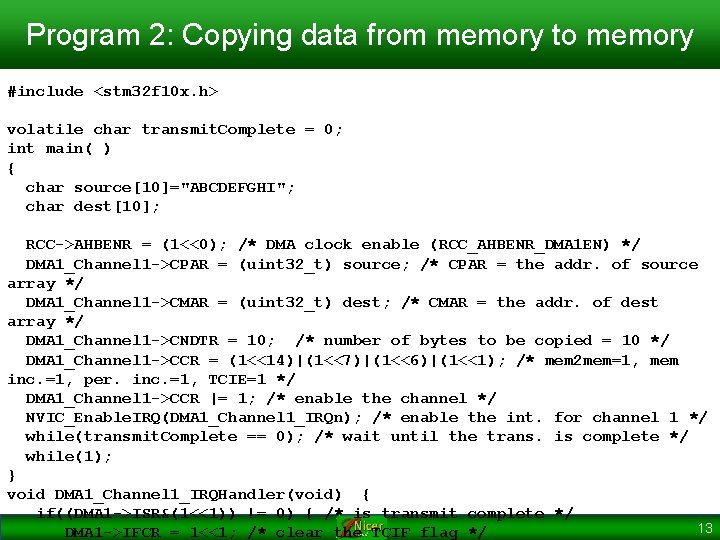

Program 2: Copying data from memory to memory #include <stm 32 f 10 x. h> volatile char transmit. Complete = 0; int main( ) { char source[10]="ABCDEFGHI"; char dest[10]; RCC->AHBENR = (1<<0); /* DMA clock enable (RCC_AHBENR_DMA 1 EN) */ DMA 1_Channel 1 ->CPAR = (uint 32_t) source; /* CPAR = the addr. of source array */ DMA 1_Channel 1 ->CMAR = (uint 32_t) dest; /* CMAR = the addr. of dest array */ DMA 1_Channel 1 ->CNDTR = 10; /* number of bytes to be copied = 10 */ DMA 1_Channel 1 ->CCR = (1<<14)|(1<<7)|(1<<6)|(1<<1); /* mem 2 mem=1, mem inc. =1, per. inc. =1, TCIE=1 */ DMA 1_Channel 1 ->CCR |= 1; /* enable the channel */ NVIC_Enable. IRQ(DMA 1_Channel 1_IRQn); /* enable the int. for channel 1 */ while(transmit. Complete == 0); /* wait until the trans. is complete */ while(1); } void DMA 1_Channel 1_IRQHandler(void) { if((DMA 1 ->ISR&(1<<1)) != 0) { /* is transmit complete */ 13 DMA 1 ->IFCR = 1<<1; /* clear the TCIF flag */

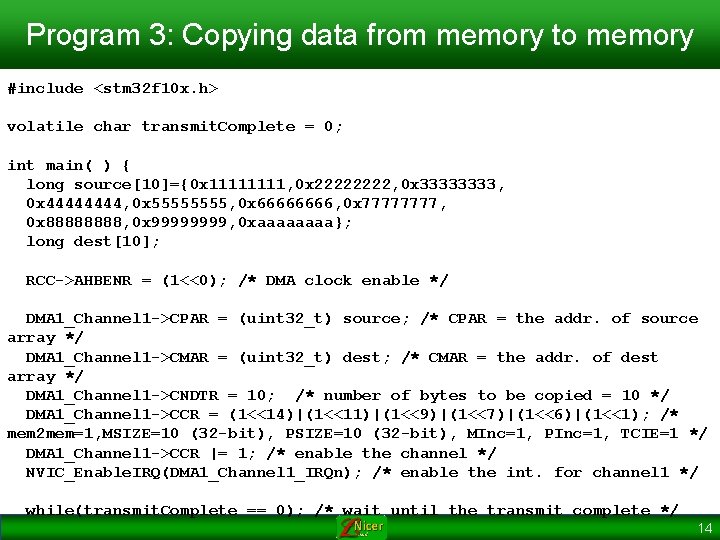

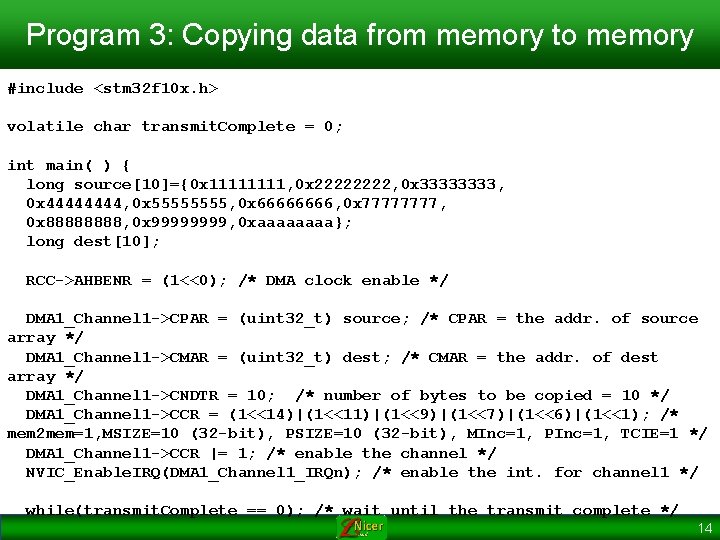

Program 3: Copying data from memory to memory #include <stm 32 f 10 x. h> volatile char transmit. Complete = 0; int main( ) { long source[10]={0 x 1111, 0 x 2222, 0 x 3333, 0 x 4444, 0 x 5555, 0 x 6666, 0 x 7777, 0 x 8888, 0 x 9999, 0 xaaaa}; long dest[10]; RCC->AHBENR = (1<<0); /* DMA clock enable */ DMA 1_Channel 1 ->CPAR = (uint 32_t) source; /* CPAR = the addr. of source array */ DMA 1_Channel 1 ->CMAR = (uint 32_t) dest; /* CMAR = the addr. of dest array */ DMA 1_Channel 1 ->CNDTR = 10; /* number of bytes to be copied = 10 */ DMA 1_Channel 1 ->CCR = (1<<14)|(1<<11)|(1<<9)|(1<<7)|(1<<6)|(1<<1); /* mem 2 mem=1, MSIZE=10 (32 -bit), PSIZE=10 (32 -bit), MInc=1, PInc=1, TCIE=1 */ DMA 1_Channel 1 ->CCR |= 1; /* enable the channel */ NVIC_Enable. IRQ(DMA 1_Channel 1_IRQn); /* enable the int. for channel 1 */ while(transmit. Complete == 0); /* wait until the transmit complete */ 14

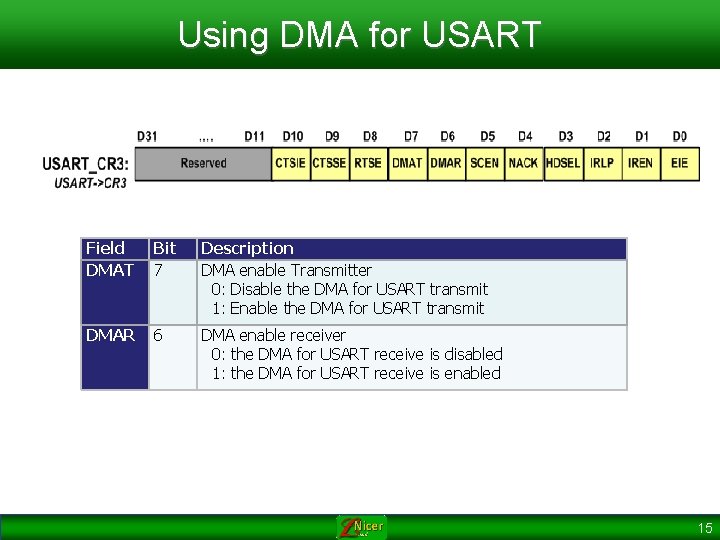

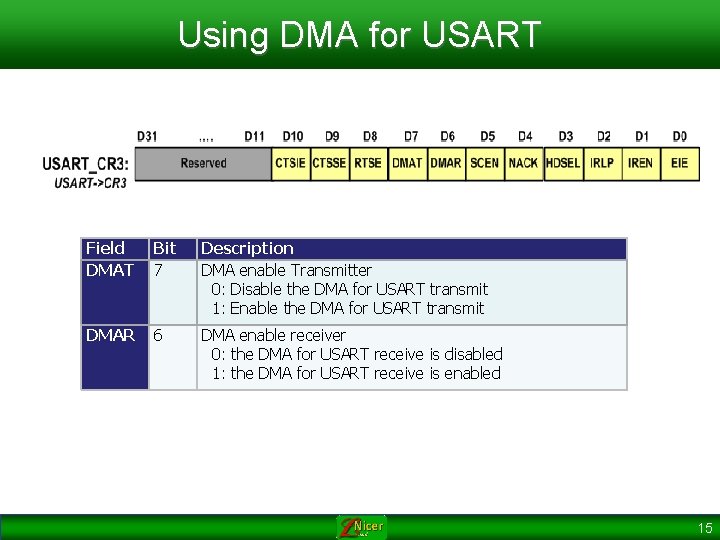

Using DMA for USART Field DMAT Bit 7 Description DMA enable Transmitter 0: Disable the DMA for USART transmit 1: Enable the DMA for USART transmit DMAR 6 DMA enable receiver 0: the DMA for USART receive is disabled 1: the DMA for USART receive is enabled 15

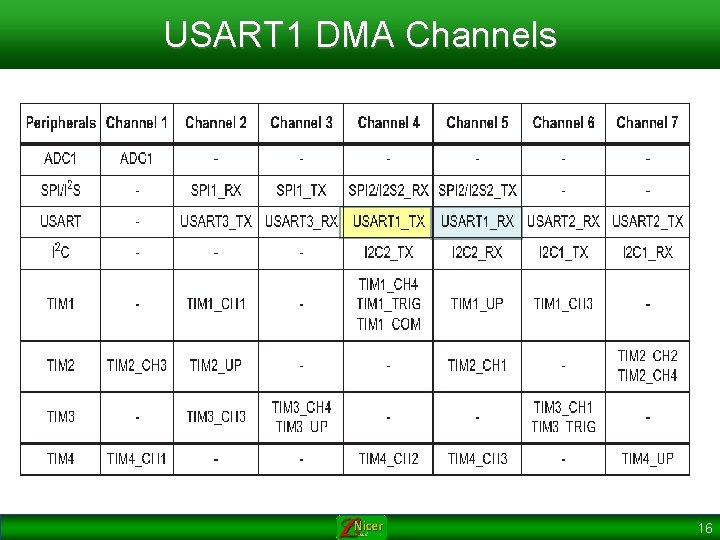

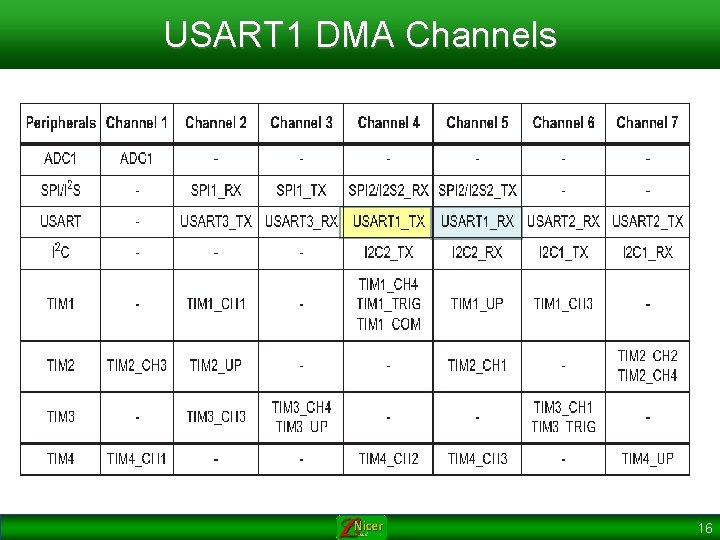

USART 1 DMA Channels 16

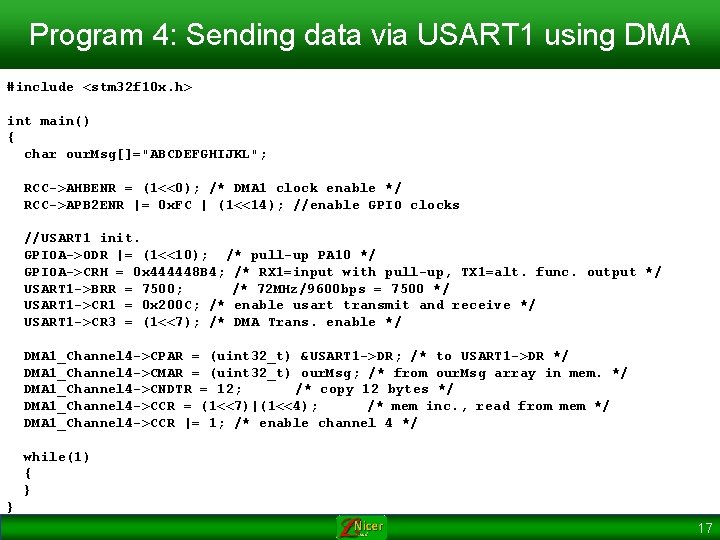

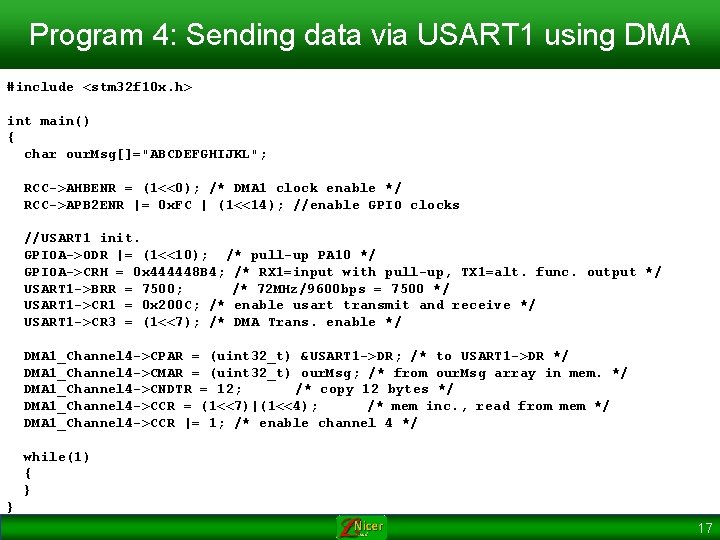

Program 4: Sending data via USART 1 using DMA #include <stm 32 f 10 x. h> int main() { char our. Msg[]="ABCDEFGHIJKL"; RCC->AHBENR = (1<<0); /* DMA 1 clock enable */ RCC->APB 2 ENR |= 0 x. FC | (1<<14); //enable GPIO clocks //USART 1 init. GPIOA->ODR |= (1<<10); /* pull-up PA 10 */ GPIOA->CRH = 0 x 444448 B 4; /* RX 1=input with pull-up, TX 1=alt. func. output */ USART 1 ->BRR = 7500; /* 72 MHz/9600 bps = 7500 */ USART 1 ->CR 1 = 0 x 200 C; /* enable usart transmit and receive */ USART 1 ->CR 3 = (1<<7); /* DMA Trans. enable */ DMA 1_Channel 4 ->CPAR = (uint 32_t) &USART 1 ->DR; /* to USART 1 ->DR */ DMA 1_Channel 4 ->CMAR = (uint 32_t) our. Msg; /* from our. Msg array in mem. */ DMA 1_Channel 4 ->CNDTR = 12; /* copy 12 bytes */ DMA 1_Channel 4 ->CCR = (1<<7)|(1<<4); /* mem inc. , read from mem */ DMA 1_Channel 4 ->CCR |= 1; /* enable channel 4 */ while(1) { } } 17