DLS Digital Controller Tony Dobbing Head of Power

DLS Digital Controller Tony Dobbing Head of Power Supplies Group

Content of talk • Features and overview • Problem of resolution • FPGA program structure • Performance • Development program • Conclusions J A Dobbing

DLS Digital Controller Features • Implemented on Xilink Spartan FPGA (low cost). • Backward compatible with original PSI digital controller. • Direct Ethernet connection to computer control network via Colibri PXA 270 processor board running EPICS, 312 MHz clock, 64 MB RAM, 32 MB Flash. • Direct Ethernet port for Fast Orbit Feedback, with low latency (150 ms less than original PSI controller). • Remote parameter loading. • FPGA program loaded from PXA 270 – remote software changes. • USB port for local control via Labview application. • 64 MB Flash memory (non-volatile), 64 MB DDR SRAM. • 50 MHz Clock Oscillator. J A Dobbing

ADC/DAC Components • 4 off 18 bit ADC AD 7691, for current measurement, with oversampling 22 bit precision is achieved. • 4 Channel 16 bit ADC AD 974, for DC link voltage and output voltage monitoring. • 4 Channel DAC LTC 2604, to monitor internal signals from front panel. J A Dobbing

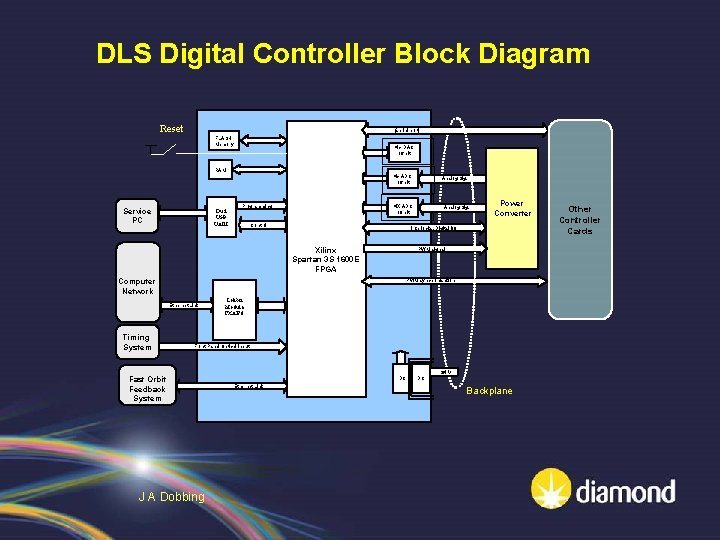

DLS Digital Controller Block Diagram Reset (serial port) FLASH Memory 4 x DAC 16 bit RAM 4 x ADC 16 bit Service PC Dual USB UART Programming 4 X ADC 18 bit Control Analog Sig. Power Converter Interlocks, Digital I/O Xilinx Spartan 3 S 1600 E FPGA PWM signal Computer Network PWM synchronisation Ethernet Link Timing System Analog Sig. Colibri Module PXA 270 Front Panel Optical Input Fast Orbit Feedback System J A Dobbing 24 V DC Ethernet Link DC Backplane Other Controller Cards

DLS Controller - Module FPGA USB Port Ethernet Ports Optical Trig DAC O/P 18 bit ADC Cover J A Dobbing PXA 270

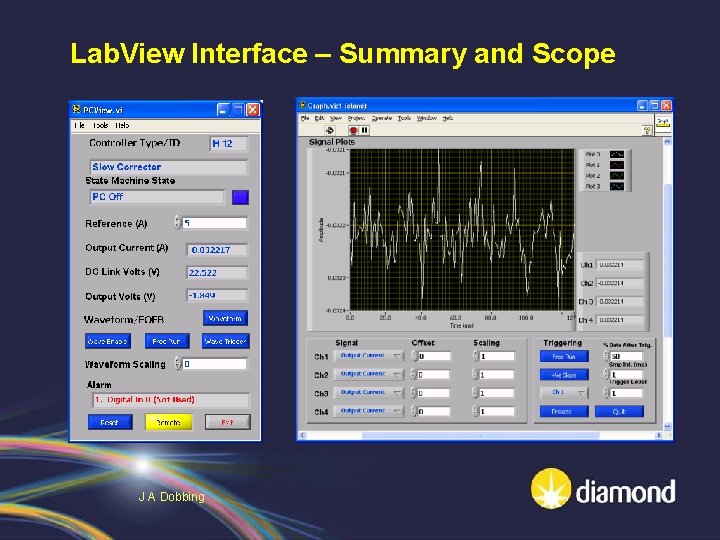

Lab. View Interface – Summary and Scope J A Dobbing

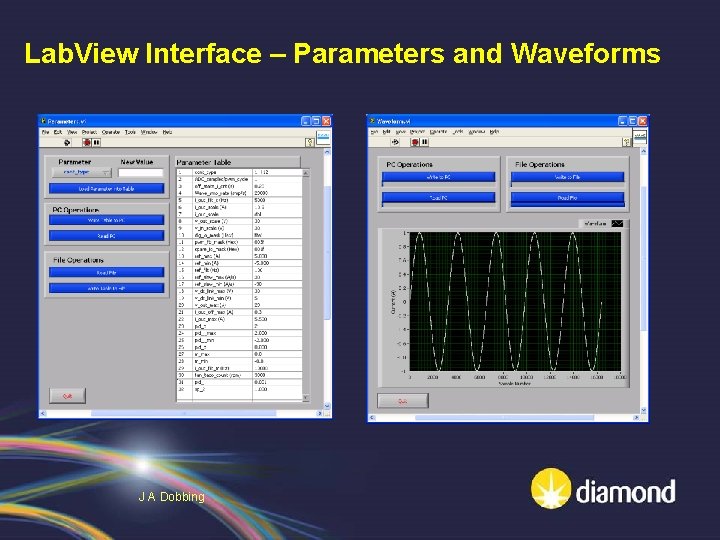

Lab. View Interface – Parameters and Waveforms J A Dobbing

The Problem of Resolution with a Digital Controller Resolution = Clock Period/PWM Period For a power supply operating with a PWM of 100 k. Hz and a 50 MHz processor clock. Resolution = 20 ns/10 ms = 0. 2% (which is not enough by far) J A Dobbing

Xilink Quadrant Phase Shift Solutions: - • Increase clock frequency. • Xilink output quadrant phase shift, effectively increases resolution to 4 times clock frequency. • E. g. 200 MHz clock with phase shifting gives 125 ppm resolution for 100 k. Hz PWM. Better but still not enough! J A Dobbing

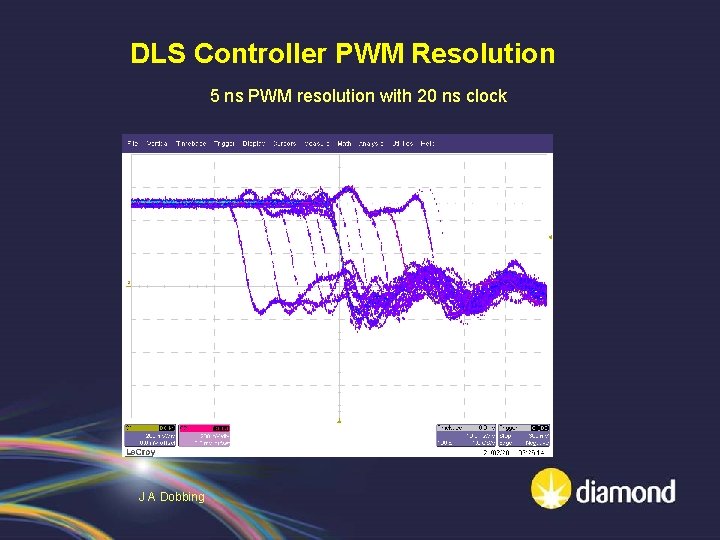

DLS Controller PWM Resolution 5 ns PWM resolution with 20 ns clock J A Dobbing

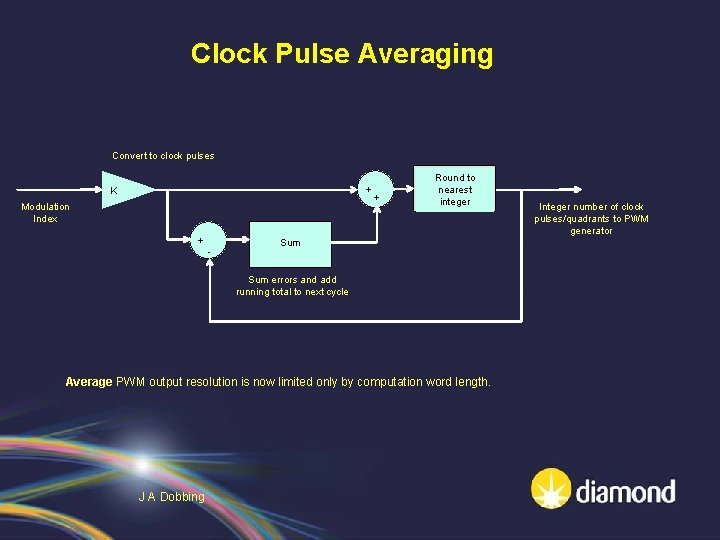

Clock Pulse Averaging Convert to clock pulses + K Modulation Index + - + Round to nearest integer Sum errors and add running total to next cycle Average PWM output resolution is now limited only by computation word length. J A Dobbing Integer number of clock pulses/quadrants to PWM generator

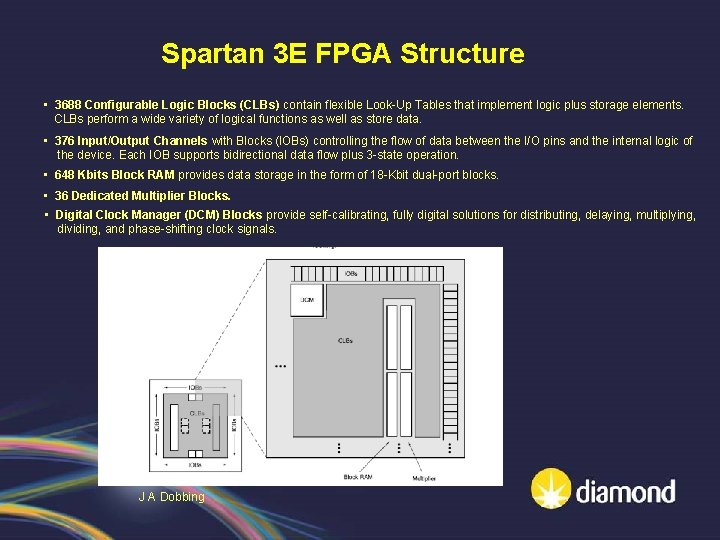

Spartan 3 E FPGA Structure • 3688 Configurable Logic Blocks (CLBs) contain flexible Look-Up Tables that implement logic plus storage elements. CLBs perform a wide variety of logical functions as well as store data. • 376 Input/Output Channels with Blocks (IOBs) controlling the flow of data between the I/O pins and the internal logic of the device. Each IOB supports bidirectional data flow plus 3 -state operation. • 648 Kbits Block RAM provides data storage in the form of 18 -Kbit dual-port blocks. • 36 Dedicated Multiplier Blocks. • Digital Clock Manager (DCM) Blocks provide self-calibrating, fully digital solutions for distributing, delaying, multiplying, dividing, and phase-shifting clock signals. J A Dobbing

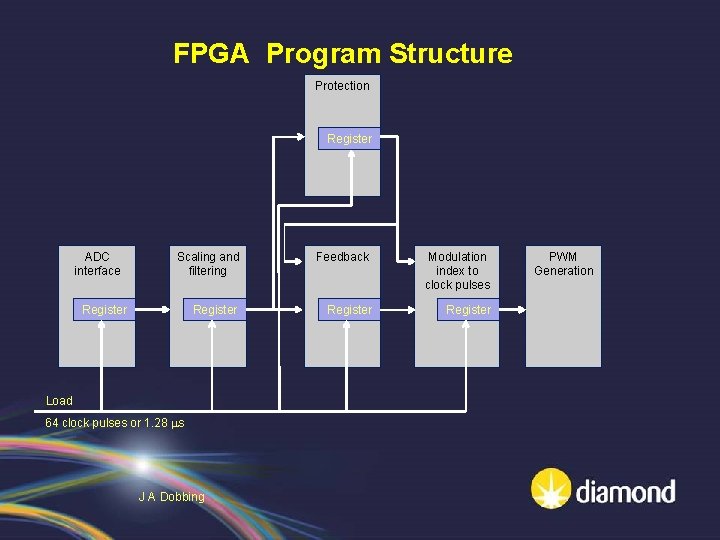

FPGA Program Structure Protection Register ADC interface Scaling and filtering Feedback Modulation index to clock pulses Register Load 64 clock pulses or 1. 28 ms J A Dobbing PWM Generation

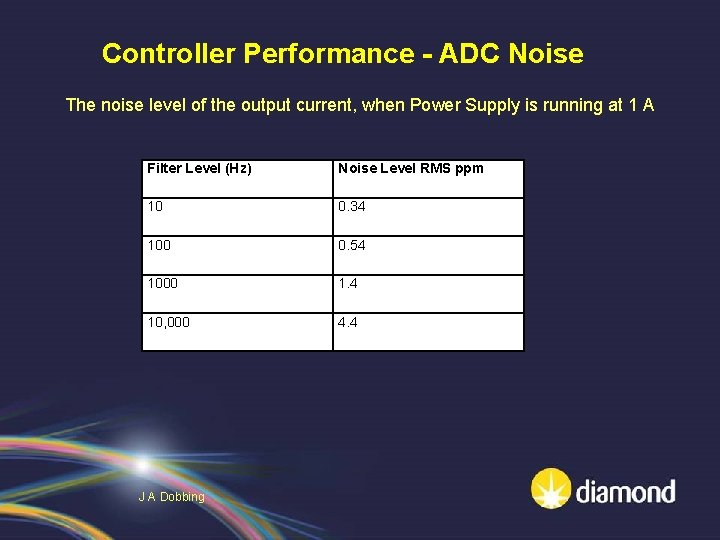

Controller Performance - ADC Noise The noise level of the output current, when Power Supply is running at 1 A Filter Level (Hz) Noise Level RMS ppm 10 0. 34 100 0. 54 1000 1. 4 10, 000 4. 4 J A Dobbing

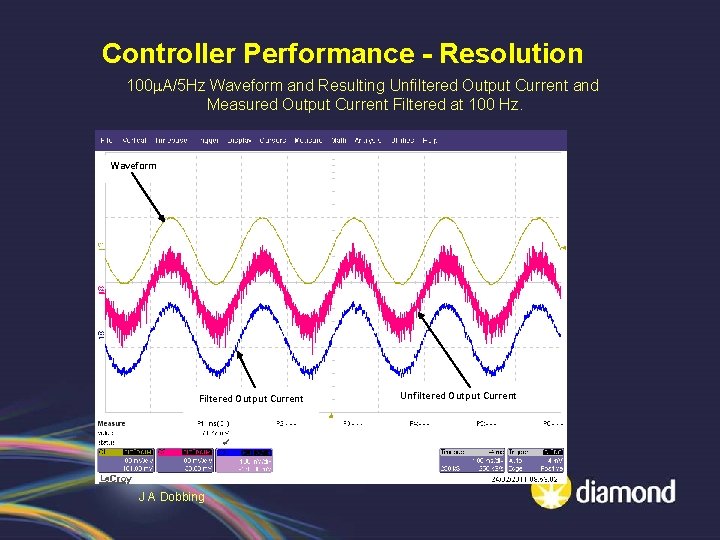

Controller Performance - Resolution 100 m. A/5 Hz Waveform and Resulting Unfiltered Output Current and Measured Output Current Filtered at 100 Hz. Waveform Filtered Output Current J A Dobbing Unfiltered Output Current

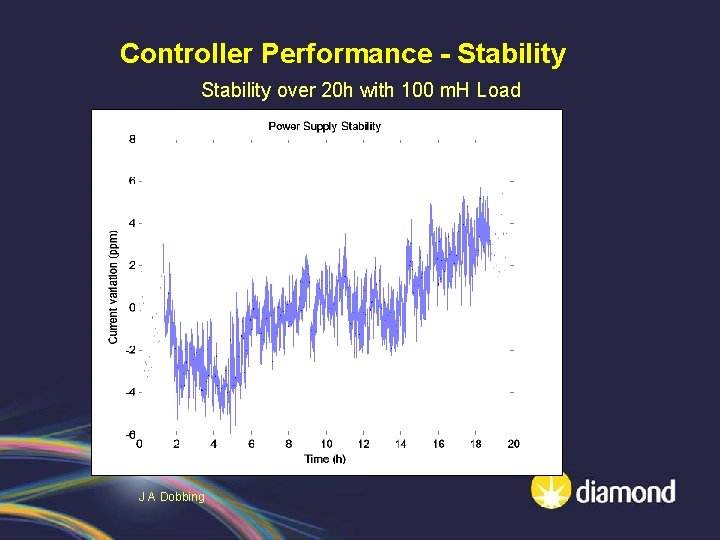

Controller Performance - Stability over 20 h with 100 m. H Load J A Dobbing

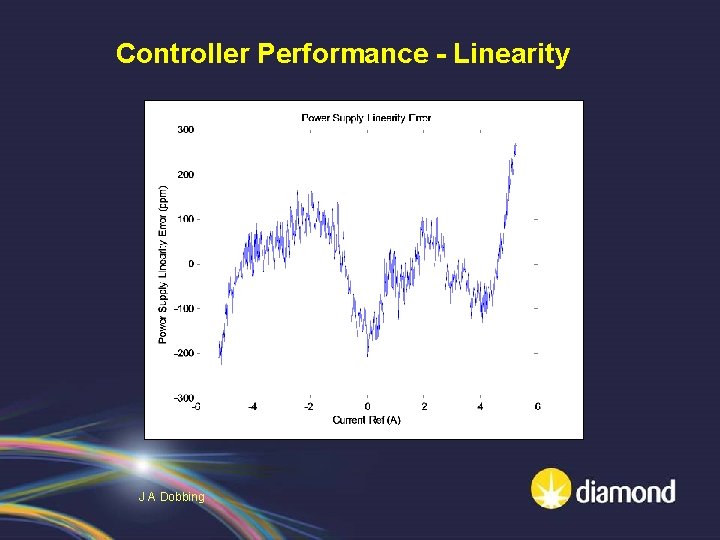

Controller Performance - Linearity J A Dobbing

Development Programme for Booster Fast Orbit Feedback System • One controller presently operating on Booster corrector. • Upgrade 11 Booster corrector controllers in June 2012. • Upgrade remaining 33 Booster corrector controllers in August 2012. • Develop feedback algorithm to exploit reduced latency. • Upgrade Storage Ring FOFB system. J A Dobbing

Conclusions • All diamond’s power supplies use the original very successful PSI digital controller. • The Cirrus ADC used in this controller is no longer available. • Diamond now has its own replacement, that is pin compatible and has significantly reduced latency, which makes it better for fast orbit feedback applications. • The PXA 270 processor eliminated the need for additional hardware between the power supply and computer control network. J A Dobbing

- Slides: 20