Dispositivos Lgicos Programables PLDs Cristian Sisterna Universidad Nacional

Dispositivos Lógicos Programables (PLDs) Cristian Sisterna Universidad Nacional de San Juan ARGENTINA

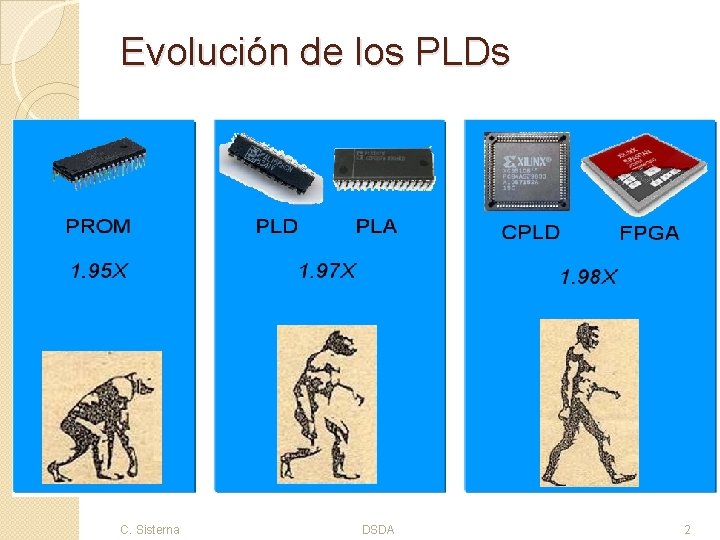

Evolución de los PLDs C. Sisterna DSDA 2

Familia de PLDs • Dispositivos Programables Simples (SPLD) • Dispositivos Programmables Complejos (CPLD) • Arreglo de Compuertas Programables en Campo (Field Programmable Gate Arrays, FPGAs) C. Sisterna DSDA 3

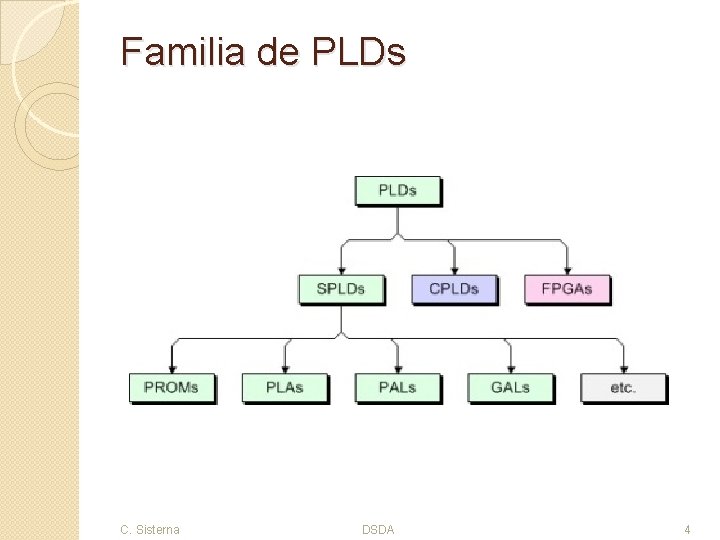

Familia de PLDs C. Sisterna DSDA 4

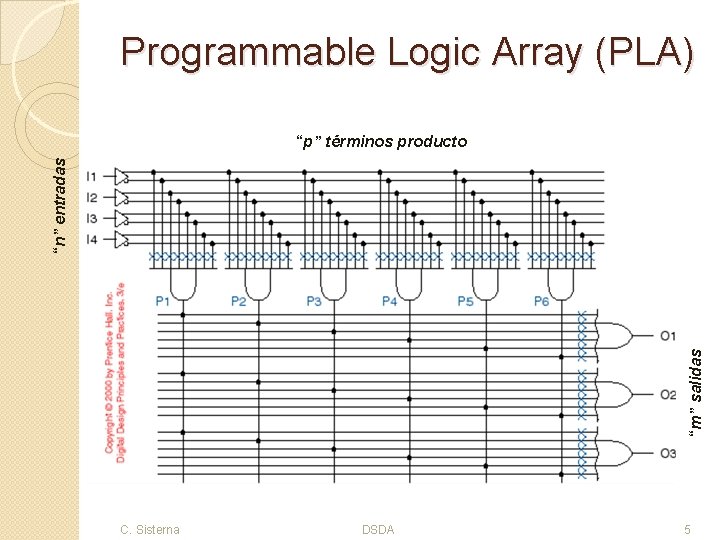

Programmable Logic Array (PLA) “m” salidas “n” entradas “p” términos producto C. Sisterna DSDA 5

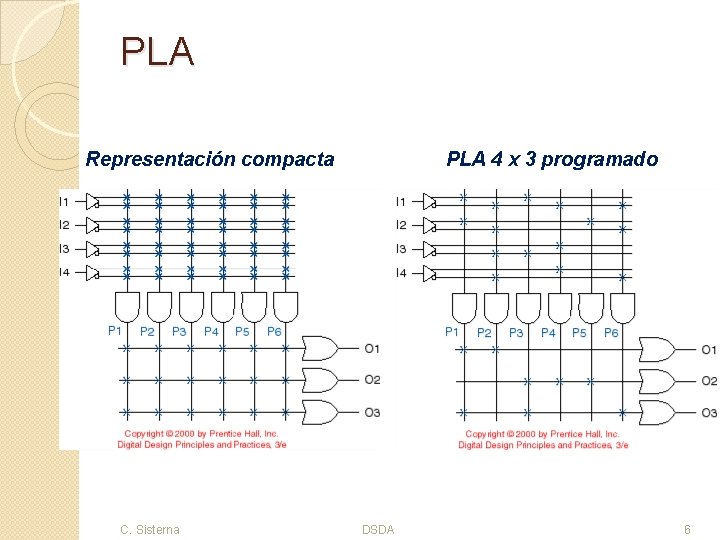

PLA Representación compacta C. Sisterna PLA 4 x 3 programado DSDA 6

GAL C. Sisterna DSDA 7

Field Programmable Gate Arrays

Celda de Configuración del FPGA Elemento básico no-lógico Determina la configuración de cada elemento lógico Determina la configuración de los elementos de ruteo e interconexiones C. Sisterna DSDA 9

Celdas de Configuración del FPGA Tipos de Celdas SRAM Anti-Fuse Flash y SRAM C. Sisterna DSDA 10

Celda de Configuración SRAM La configuración de los elementos lógicos y los de ruteo e interconexión son almacenados en celdas SRAMs Ventajas: Proceso de fabricación estándar Costos muy bajos Proceso súper-comprobado Alto rendimiento Infinitamente reprogramable Programable en circuito (In System Programable) Rápida y fácil actualización C. Sisterna DSDA 11

Celda de Configuración SRAM Desventajas: Celda volátil Simple glitch en Vcc desconfigura el FPGA Retardos en ruteo largos debido al retardo de la celda SRAM Necesidad de una memoria de configuración externa Tiempo de configuración lento ~500 ms Inseguridad debido a la conexión FPGA-Memoria de configuración que puede ser ‘leída’ C. Sisterna DSDA 12

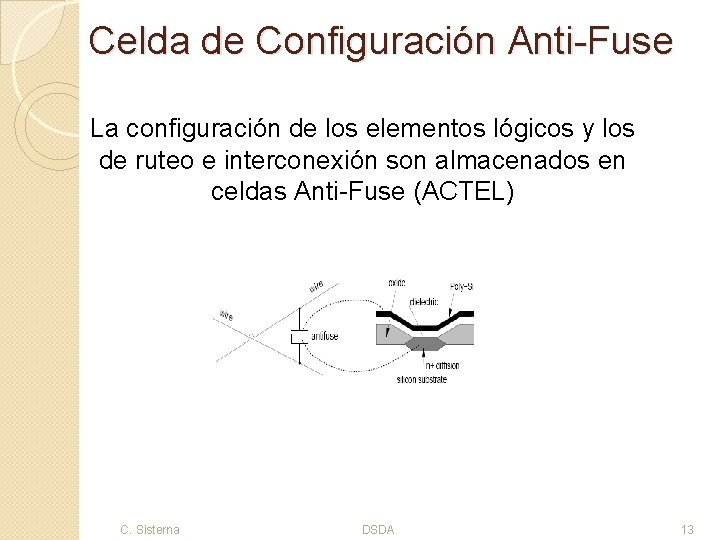

Celda de Configuración Anti-Fuse La configuración de los elementos lógicos y los de ruteo e interconexión son almacenados en celdas Anti-Fuse (ACTEL) C. Sisterna DSDA 13

Celda de Configuración Anti-Fuse Ventajas: No es volátil Retardos de conexiones de ruteo son pequeños No sensibles a bombardeo de partículas iónicas Muy usados en sistemas espaciales C. Sisterna DSDA 14

Celda de Configuración Anti-Fuse Desventajas: Proceso de fabricación específico Costos elevados One-Time-Programmable (OTP) Proceso de verificacion muy largo y riguroso Proceso muy caro No sensibles a bombardeo de partículas iónicas Muy usados en sistemas espaciales C. Sisterna DSDA 15

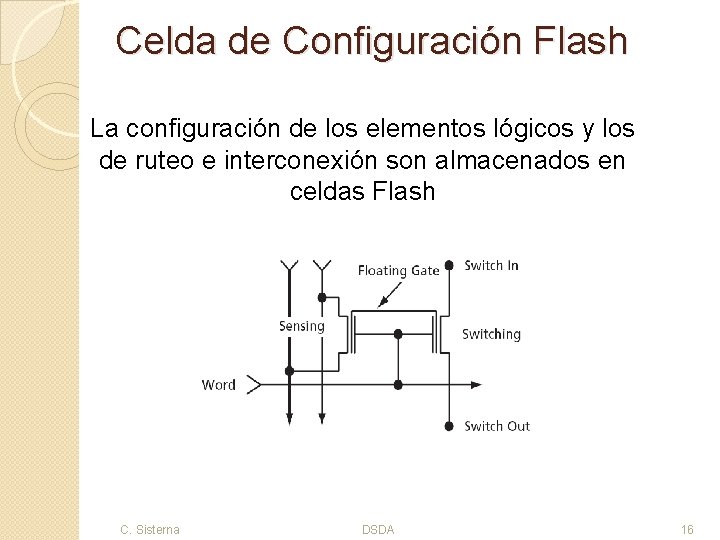

Celda de Configuración Flash La configuración de los elementos lógicos y los de ruteo e interconexión son almacenados en celdas Flash C. Sisterna DSDA 16

Celda de Configuración Flash Ventajas: No es volátil Retardos de conexiones de ruteo son pequeños Sensibilidad baja a bombardeo de partículas iónicas Usados en sistemas espaciales C. Sisterna DSDA 17

Celda de Configuración Flash Desventajas: FPGA es bastante caro Proceso se esta haciendo mas común últimamente Proceso de reconfiguración bastante largo (~3 -5 seg) C. Sisterna DSDA 18

Celda de Configuración Flash-SRAM Las celdas Flash se usan para guardar los datos de configuración del FPGA Las celdas SRAM para la configuración de los elementos lógicos y los de ruteo e interconexión Cuando de alimenta el FPGA, las celdas SRAM se configuran en forma casi instantanea desde las celdas Flash. C. Sisterna DSDA 19

Celda de Configuración Flash-SRAM Ventajas: Prácticamente ‘no es volátil’ Tiempo de configuración es bastante bajo (~<1 ms) Se pueden configurar solo las celdas SRAM Durante el proceso de debug o prototipo No se necesita una memoria de configuración externa Menos espacio en el PCB Sistema no vulnerable – Sistema seguro C. Sisterna DSDA 20

Celda de Configuración Flash-SRAM Desventajas: FPGA es caro Proceso se esta haciendo mas común últimamente C. Sisterna DSDA 21

CYCLONE IV FPGA C. Sisterna DSDA 22

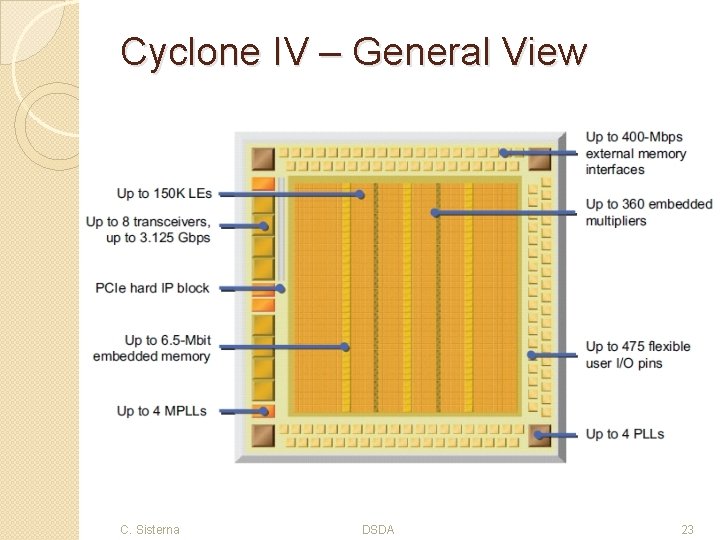

Cyclone IV – General View C. Sisterna DSDA 23

Cyclone FPGA Familiy �Cyclone IV devices are targeted to highvolume, cost-sensitive applications, enabling system designers to meet increasing bandwidth requirements while lowering costs Built on an optimized low-power process, the Cyclone IV device family offers the following two variants: � Cyclone IV E—lowest power, high functionality with the lowest cost C. Sisterna DSDA 24

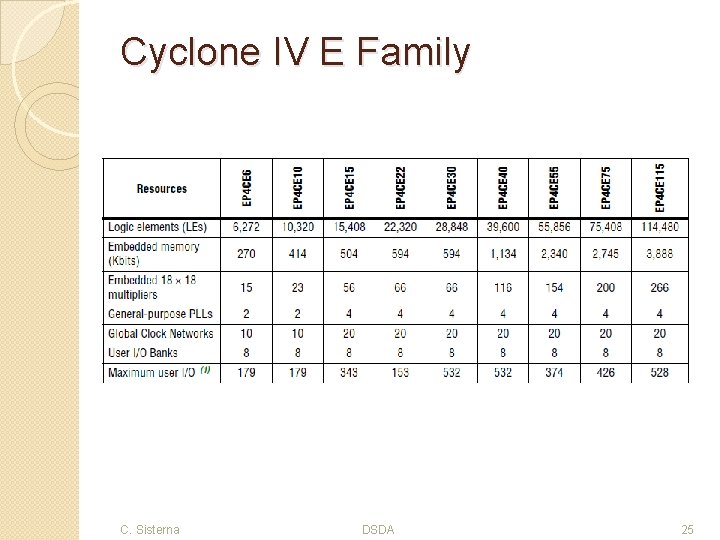

Cyclone IV E Family C. Sisterna DSDA 25

Cyclone Core Fabric �Logic Elements: 4 -input look up tables �M 9 K Memory Blocks: 9 Kbits of embedded SRAM �Embedded Multiplier: 18 x 18 or two 9 x 9 multipliers in a single block C. Sisterna DSDA 26

LOGIC ELEMENT C. Sisterna DSDA 27

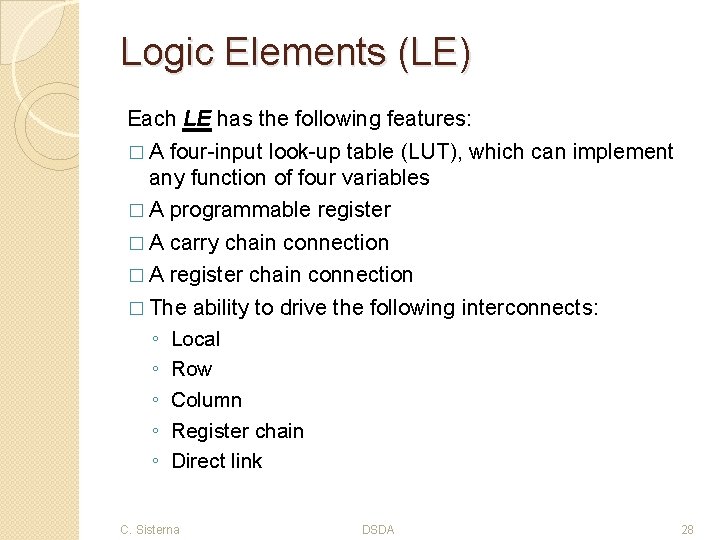

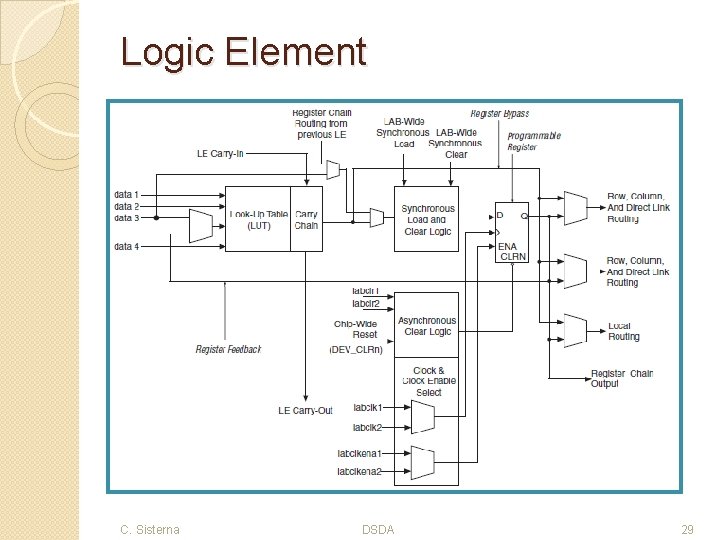

Logic Elements (LE) Each LE has the following features: � A four-input look-up table (LUT), which can implement any function of four variables � A programmable register � A carry chain connection � A register chain connection � The ability to drive the following interconnects: ◦ Local ◦ Row ◦ Column ◦ Register chain ◦ Direct link C. Sisterna DSDA 28

Logic Element C. Sisterna DSDA 29

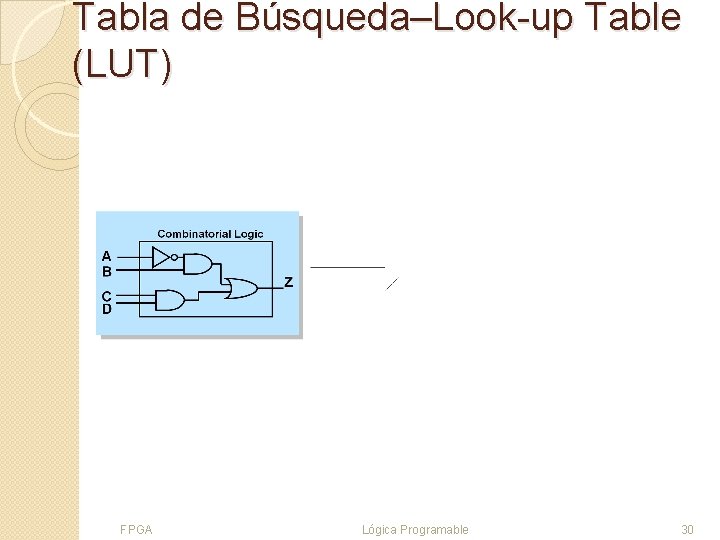

Tabla de Búsqueda–Look-up Table (LUT) FPGA Lógica Programable 30

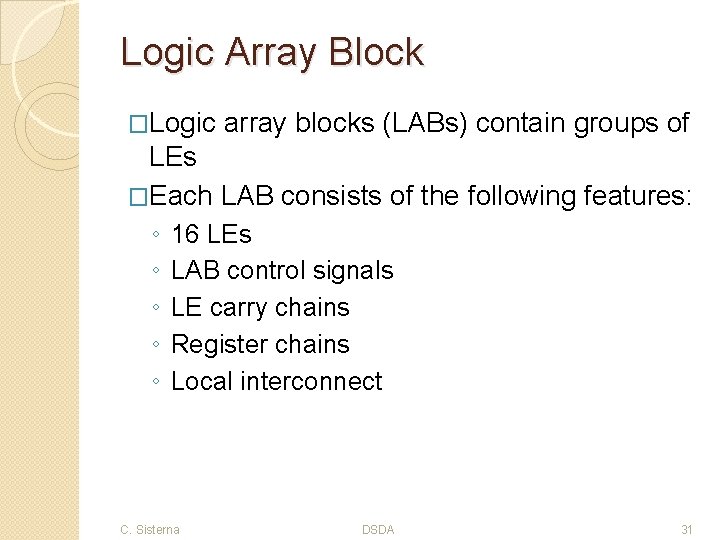

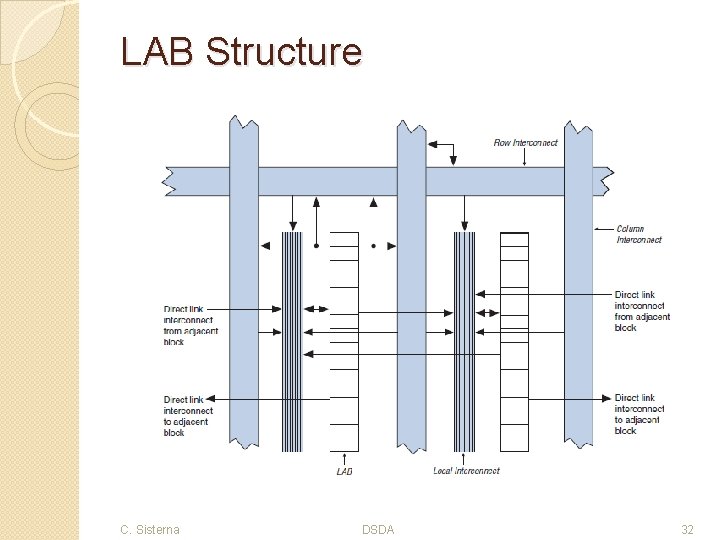

Logic Array Block �Logic array blocks (LABs) contain groups of LEs �Each LAB consists of the following features: ◦ ◦ ◦ 16 LEs LAB control signals LE carry chains Register chains Local interconnect C. Sisterna DSDA 31

LAB Structure C. Sisterna DSDA 32

FPGA ROUTING C. Sisterna DSDA 33

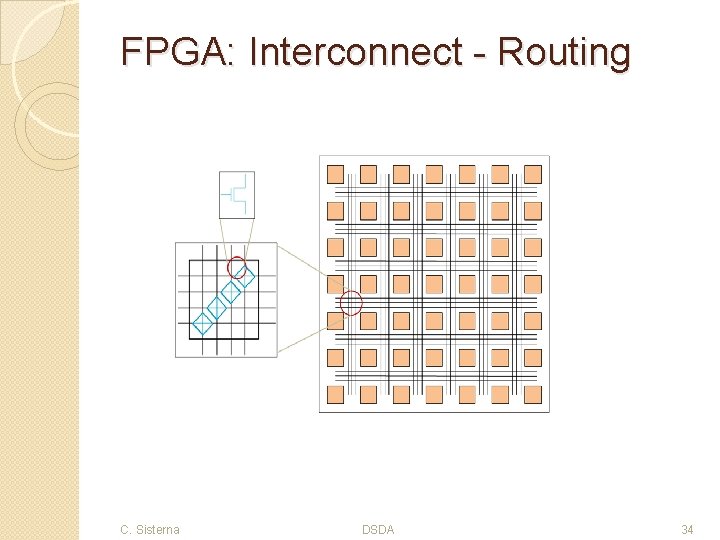

FPGA: Interconnect - Routing C. Sisterna DSDA 34

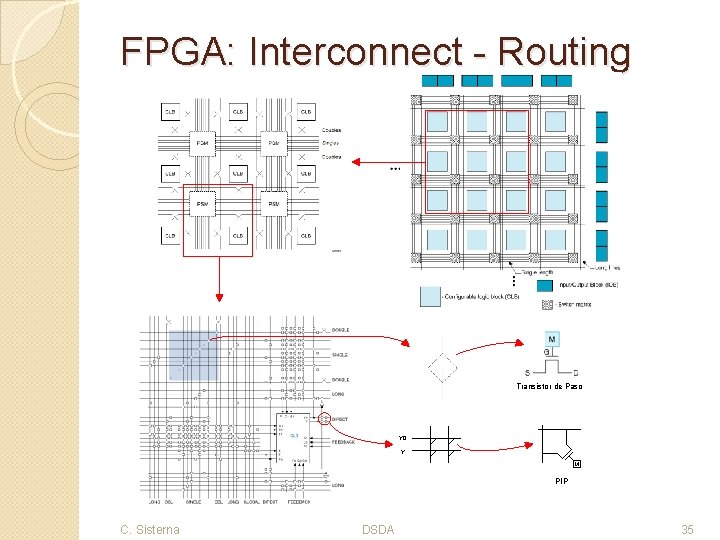

FPGA: Interconnect - Routing Transistor de Paso Y 0 Y M PIP C. Sisterna DSDA 35

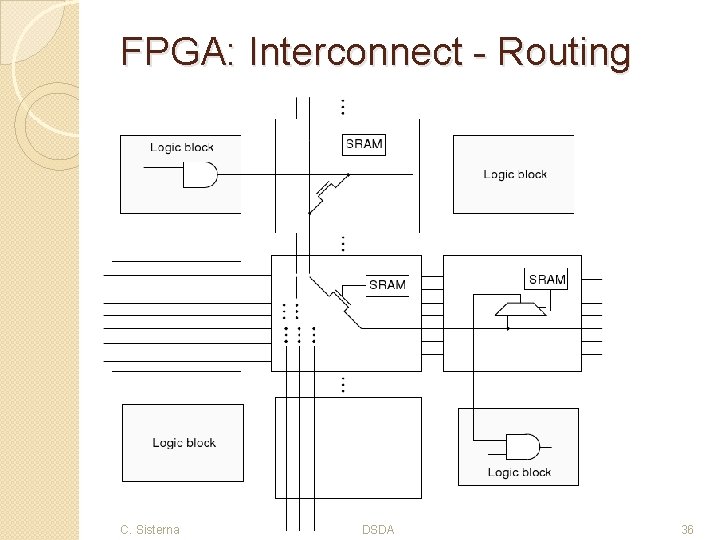

FPGA: Interconnect - Routing C. Sisterna DSDA 36

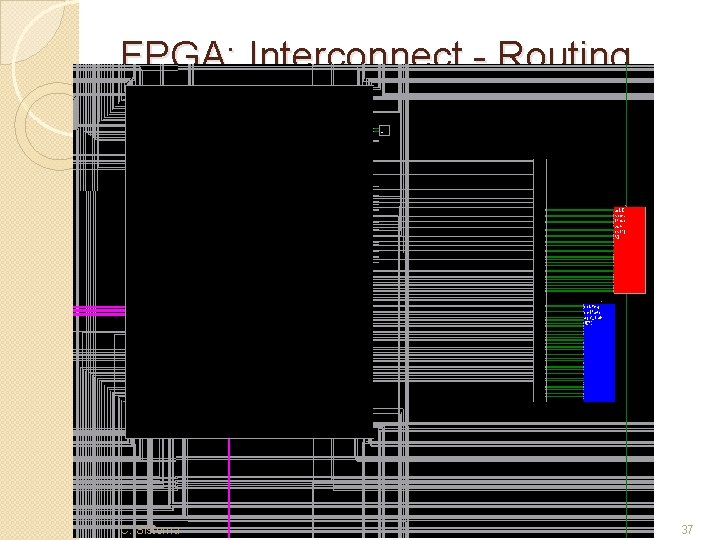

FPGA: Interconnect - Routing C. Sisterna DSDA 37

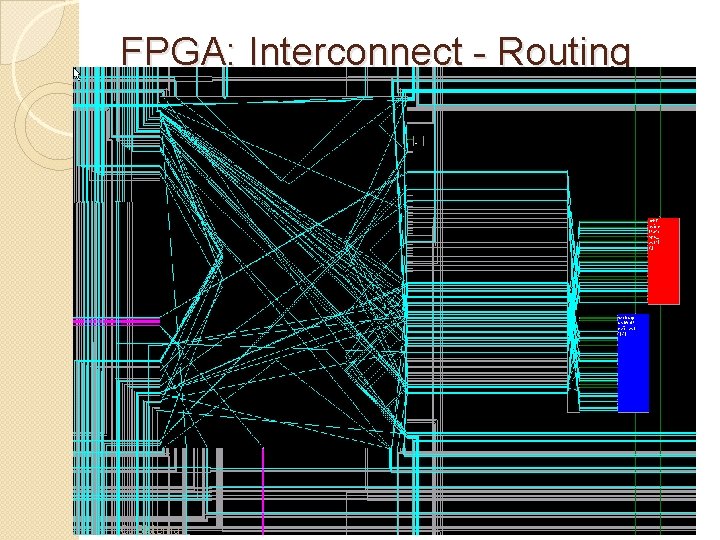

FPGA: Interconnect - Routing C. Sisterna DSDA 38

IMPLEMENTATION OF MEMORY IN FPGA C. Sisterna DSDA 39

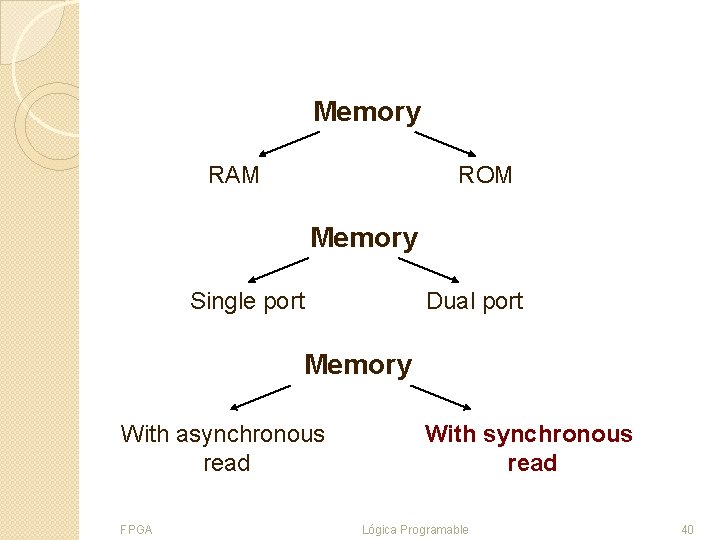

Memory RAM ROM Memory Single port Dual port Memory With asynchronous read FPGA With synchronous read Lógica Programable 40

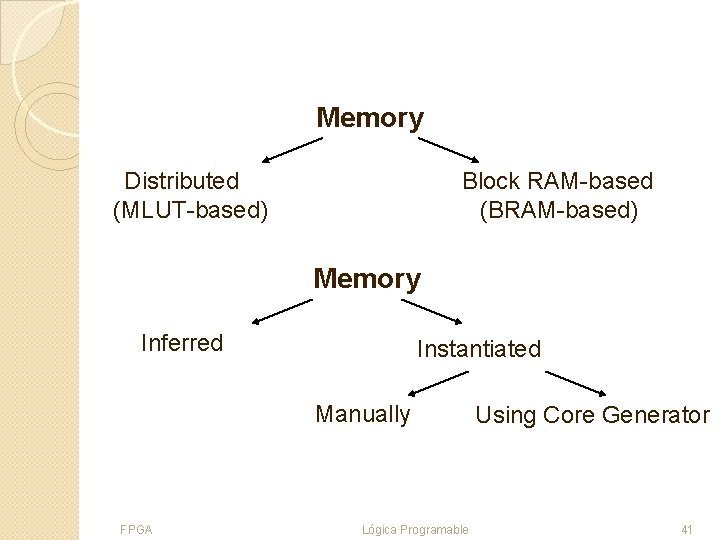

Memory Distributed (MLUT-based) Block RAM-based (BRAM-based) Memory Inferred Instantiated Manually FPGA Lógica Programable Using Core Generator 41

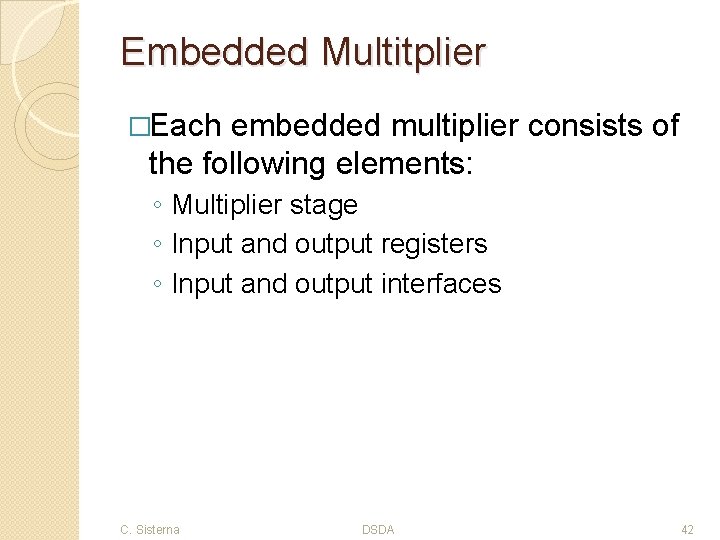

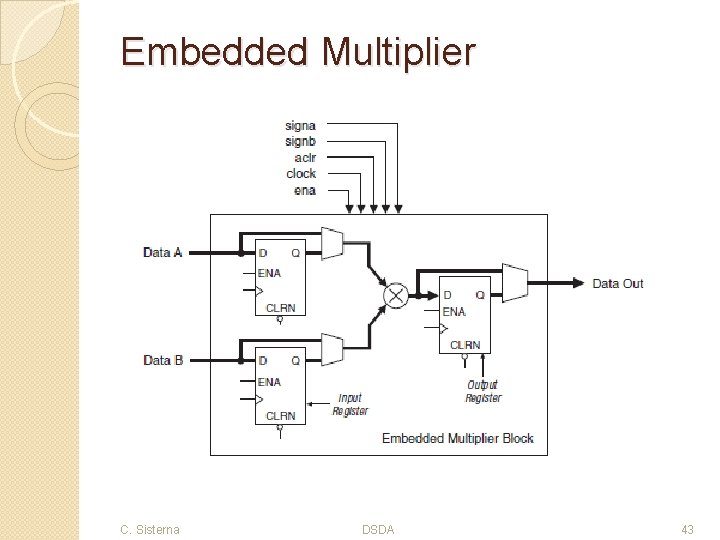

Embedded Multitplier �Each embedded multiplier consists of the following elements: ◦ Multiplier stage ◦ Input and output registers ◦ Input and output interfaces C. Sisterna DSDA 42

Embedded Multiplier C. Sisterna DSDA 43

INPUT/OUTPUT FEATURES C. Sisterna DSDA 44

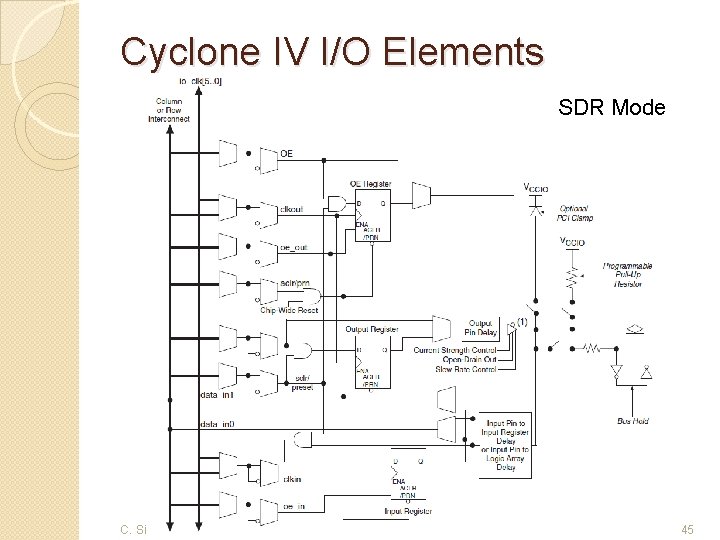

Cyclone IV I/O Elements SDR Mode C. Sisterna DSDA 45

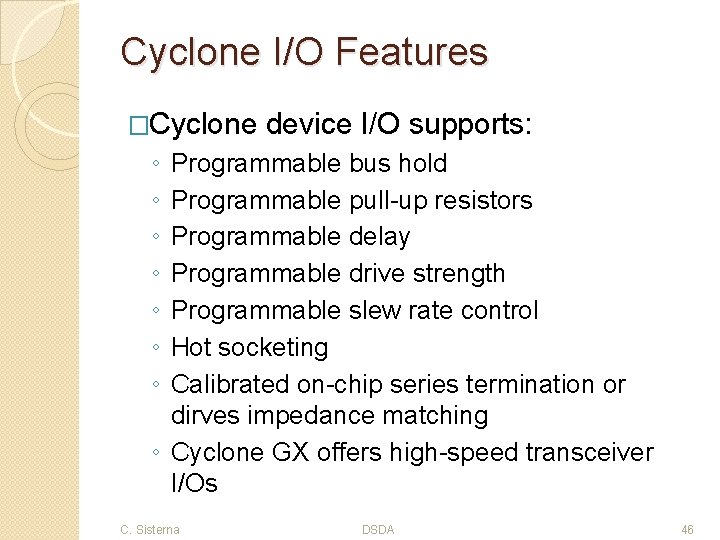

Cyclone I/O Features �Cyclone device I/O supports: ◦ ◦ ◦ ◦ Programmable bus hold Programmable pull-up resistors Programmable delay Programmable drive strength Programmable slew rate control Hot socketing Calibrated on-chip series termination or dirves impedance matching ◦ Cyclone GX offers high-speed transceiver I/Os C. Sisterna DSDA 46

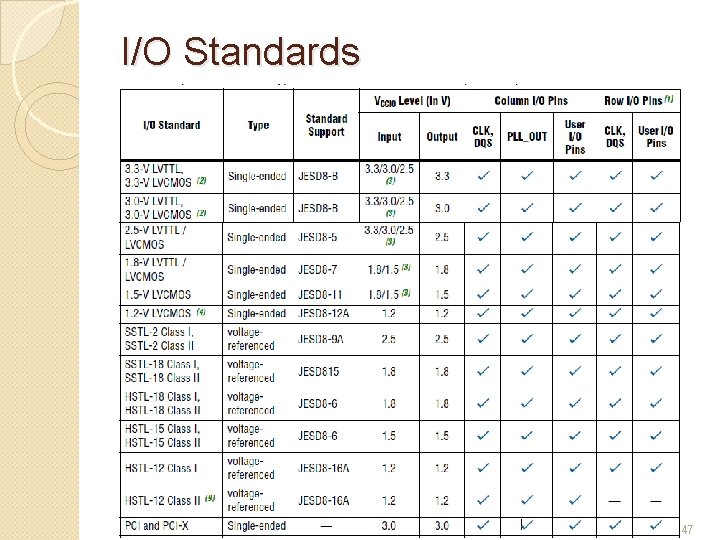

I/O Standards C. Sisterna DSDA 47

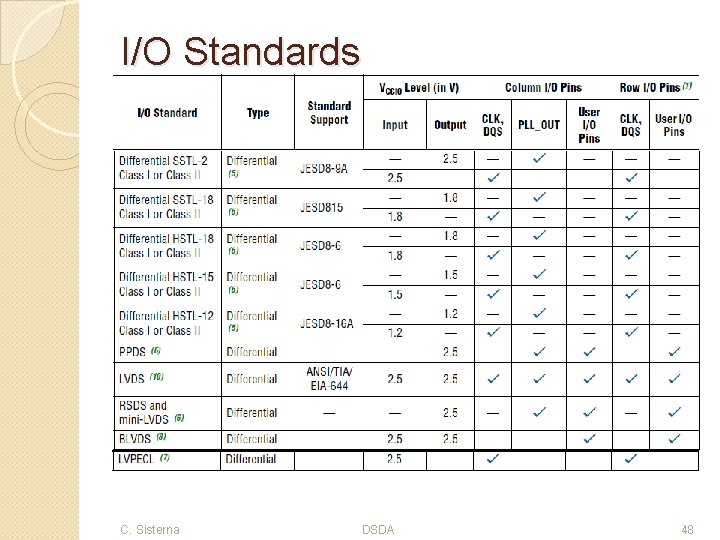

I/O Standards C. Sisterna DSDA 48

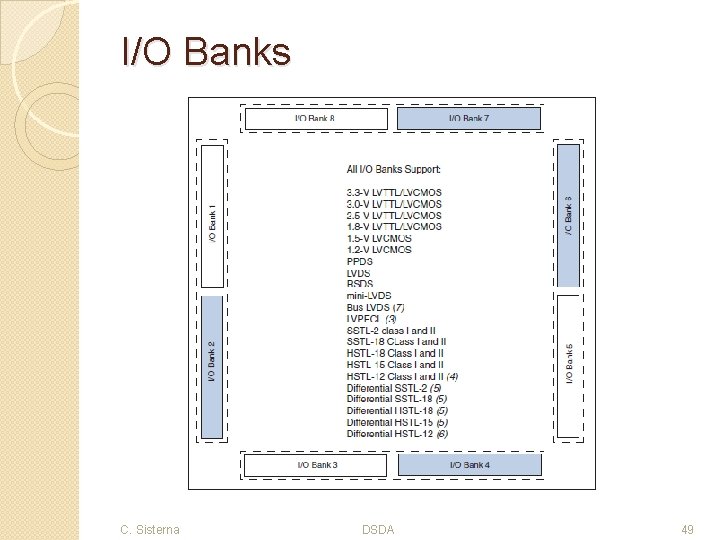

I/O Banks C. Sisterna DSDA 49

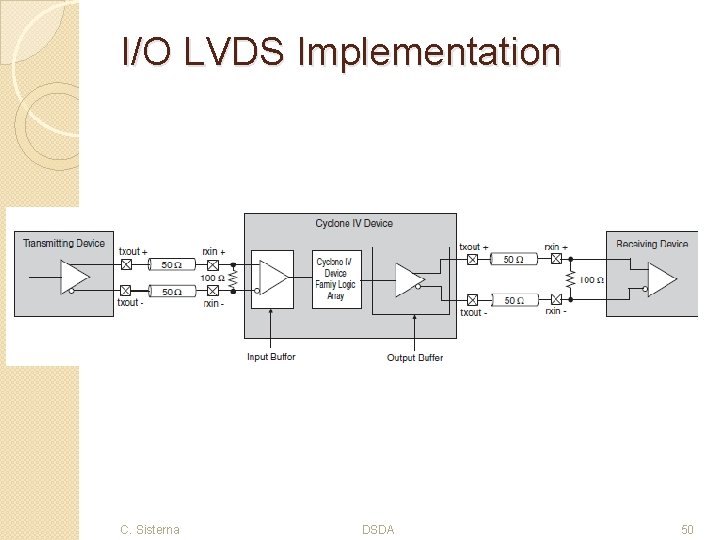

I/O LVDS Implementation C. Sisterna DSDA 50

FPGA CONFIGURATION C. Sisterna DSDA 51

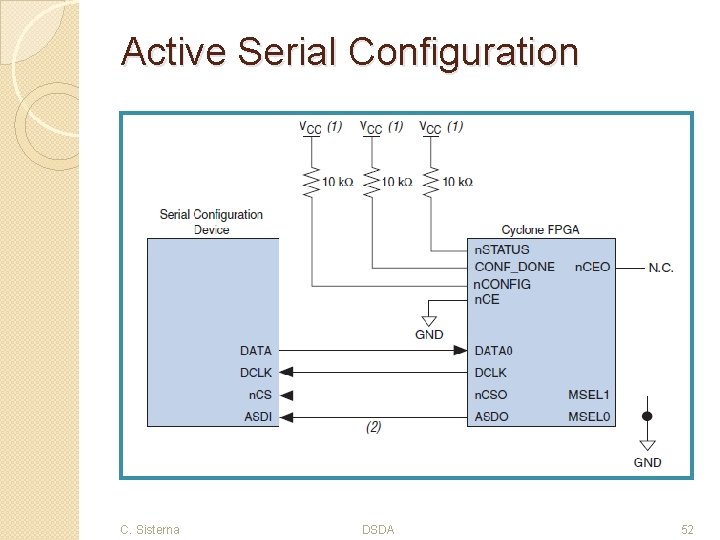

Active Serial Configuration C. Sisterna DSDA 52

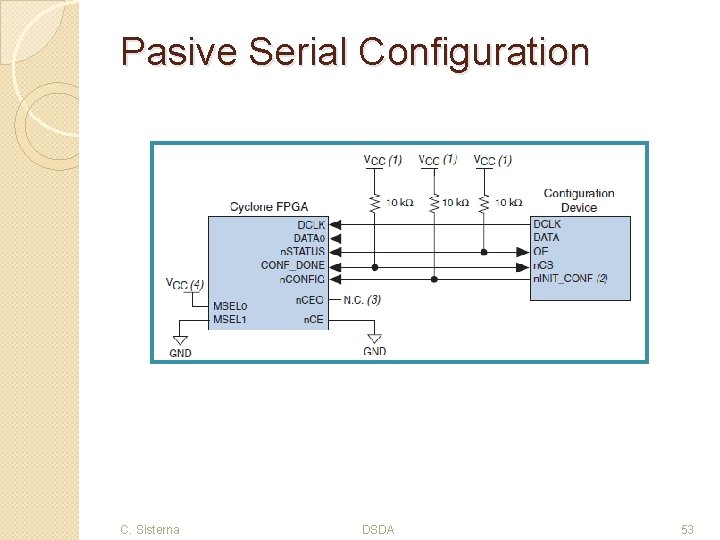

Pasive Serial Configuration C. Sisterna DSDA 53

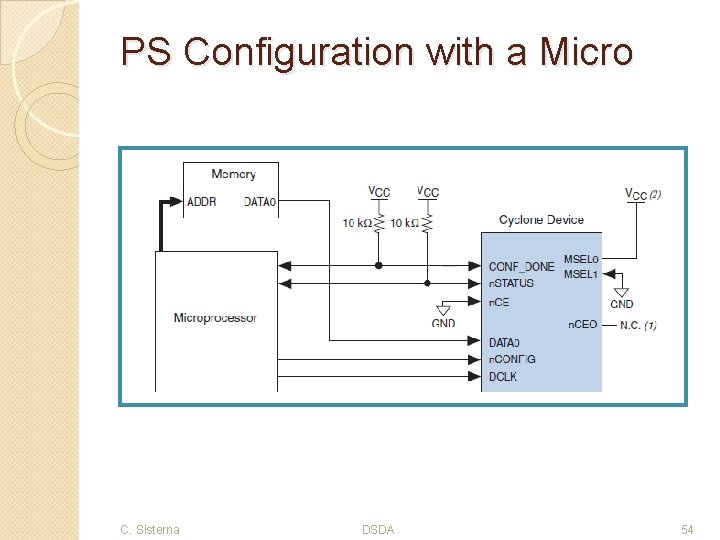

PS Configuration with a Micro C. Sisterna DSDA 54

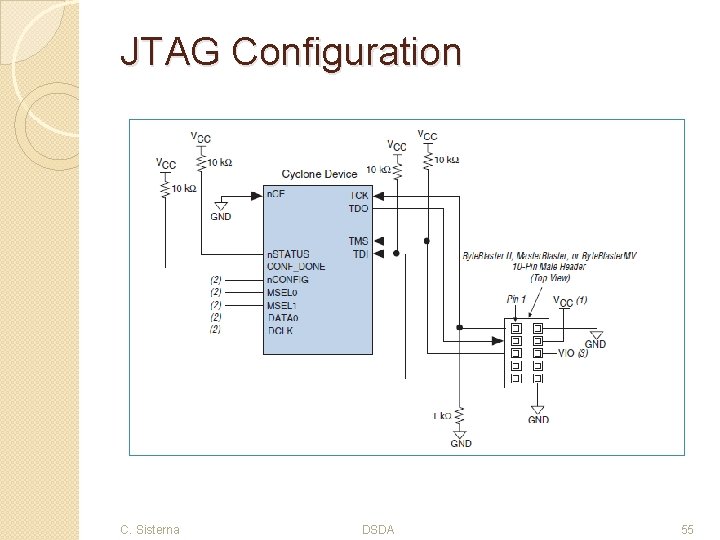

JTAG Configuration C. Sisterna DSDA 55

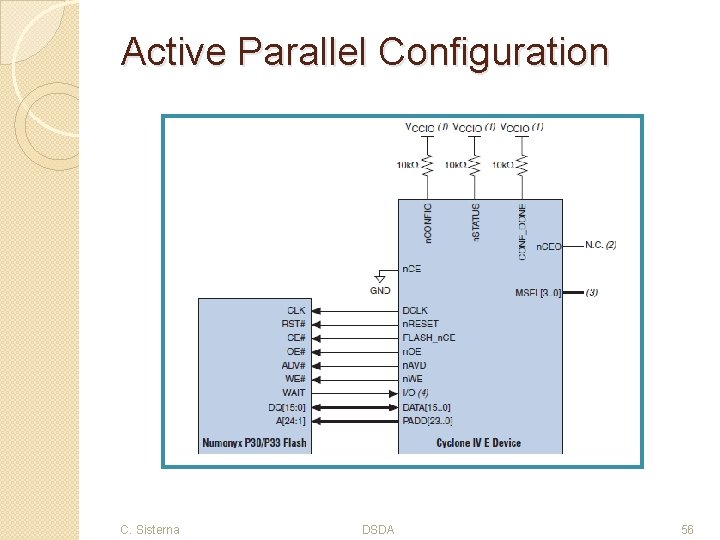

Active Parallel Configuration C. Sisterna DSDA 56

- Slides: 56