DISPLAY AND VGA PHOTO DISPLAY AND DISTORTION Hailey

- Slides: 1

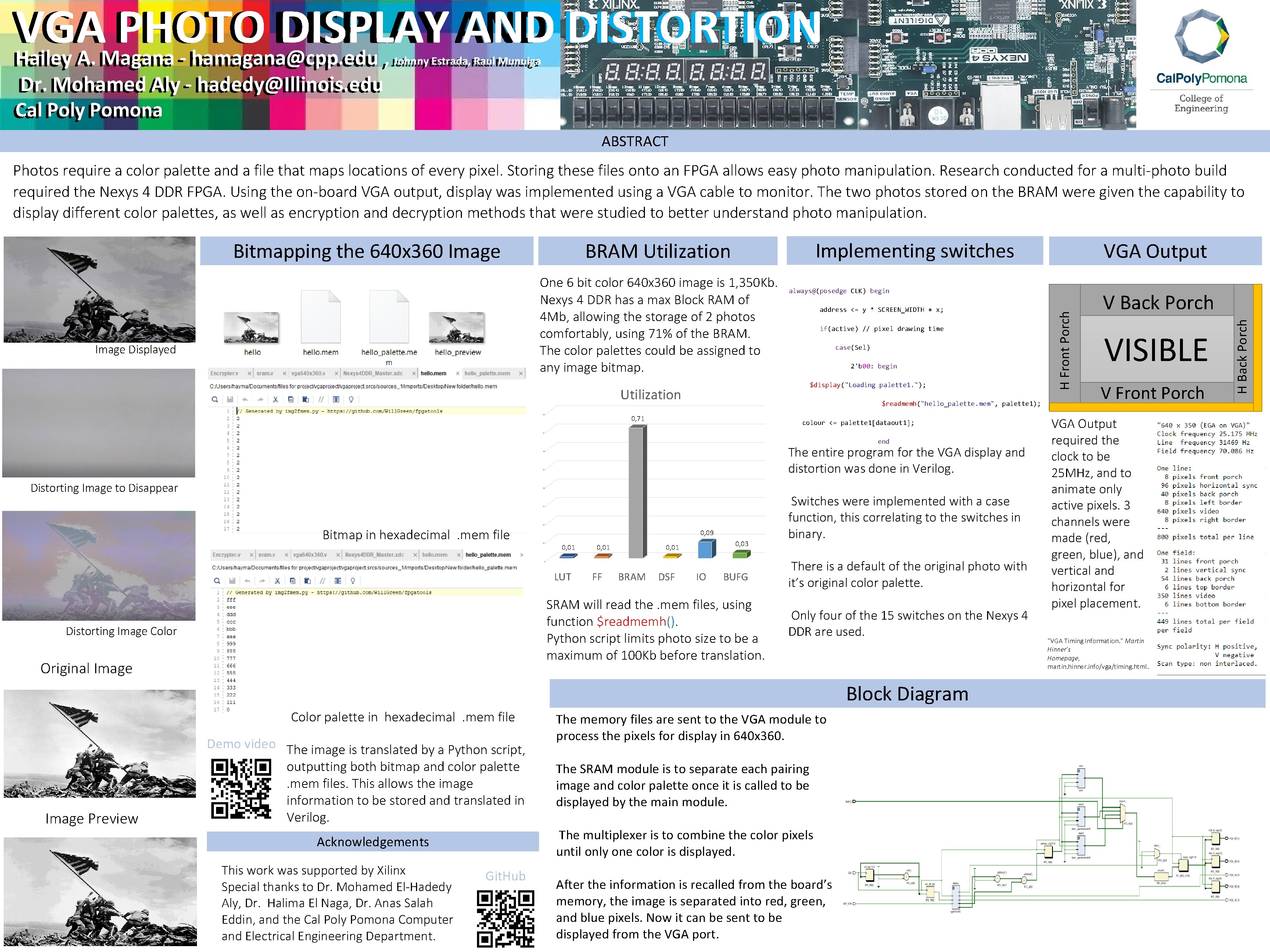

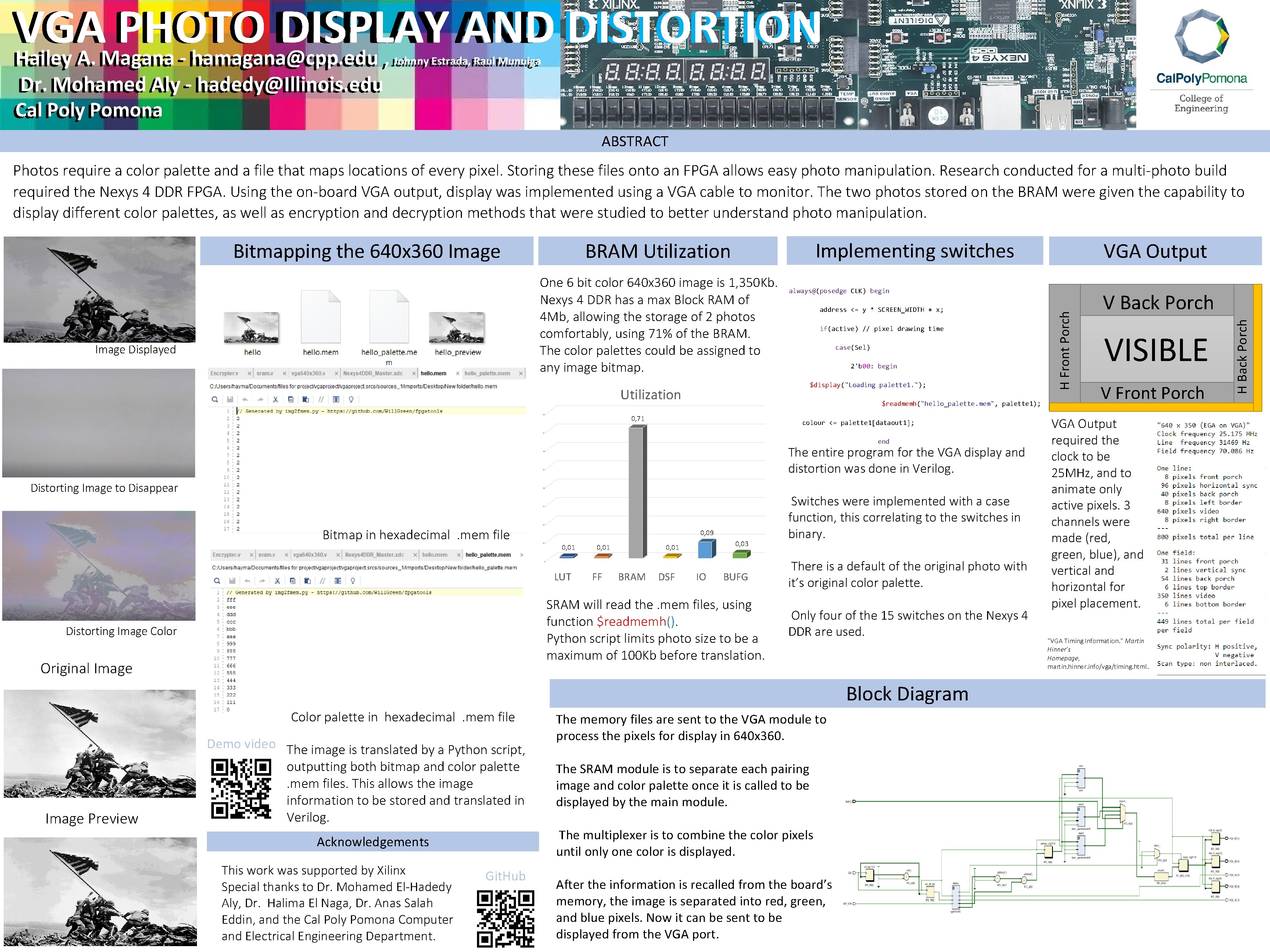

DISPLAY AND VGA PHOTO DISPLAY AND DISTORTION Hailey A. A. Magana -- hamagana@cpp. edu Hailey Johnny. Estrada, Raul. Munuiga , , Johnny Dr. Mohamed Aly -- hadedy@Illinois. edu Dr. Cal Poly Pomona Cal ABSTRACT Photos require a color palette and a file that maps locations of every pixel. Storing these files onto an FPGA allows easy photo manipulation. Research conducted for a multi-photo build required the Nexys 4 DDR FPGA. Using the on-board VGA output, display was implemented using a VGA cable to monitor. The two photos stored on the BRAM were given the capability to display different color palettes, as well as encryption and decryption methods that were studied to better understand photo manipulation. Implementing switches One 6 bit color 640 x 360 image is 1, 350 Kb. Nexys 4 DDR has a max Block RAM of 4 Mb, allowing the storage of 2 photos comfortably, using 71% of the BRAM. The color palettes could be assigned to any image bitmap. Image Displayed always@(posedge CLK) begin address <= y * SCREEN_WIDTH + x; if(active) // pixel drawing time case(Sel) 2'b 00: begin $display("Loading palette 1. "); Utilization 0, 8 $readmemh("hello_palette. mem", palette 1); 0, 71 colour <= palette 1[dataout 1]; 0, 7 end The entire program for the VGA display and distortion was done in Verilog. 0, 6 0, 5 Distorting Image to Disappear 0, 4 0, 3 0, 2 Bitmap in hexadecimal. mem file 0, 09 0, 1 0, 01 0, 03 0, 01 0 LUT FF BRAM DSF IO BUFG SRAM will read the. mem files, using function $readmemh(). Python script limits photo size to be a maximum of 100 Kb before translation. Distorting Image Color Original Image Switches were implemented with a case function, this correlating to the switches in binary. There is a default of the original photo with it’s original color palette. Only four of the 15 switches on the Nexys 4 DDR are used. Block Diagram Color palette in hexadecimal. mem file Image Preview Demo video The image is translated by a Python script, outputting both bitmap and color palette. mem files. This allows the image information to be stored and translated in Verilog. This work was supported by Xilinx Special thanks to Dr. Mohamed El-Hadedy Aly, Dr. Halima El Naga, Dr. Anas Salah Eddin, and the Cal Poly Pomona Computer and Electrical Engineering Department. The memory files are sent to the VGA module to process the pixels for display in 640 x 360. The SRAM module is to separate each pairing image and color palette once it is called to be displayed by the main module. The multiplexer is to combine the color pixels until only one color is displayed. Acknowledgements Git. Hub VGA Output After the information is recalled from the board’s memory, the image is separated into red, green, and blue pixels. Now it can be sent to be displayed from the VGA port. V Back Porch VISIBLE V Front Porch VGA Output required the clock to be 25 MHz, and to animate only active pixels. 3 channels were made (red, green, blue), and vertical and horizontal for pixel placement. “VGA Timing Information. ” Martin Hinner’s Homepage, martin. hinner. info/vga/timing. html. H Back Porch BRAM Utilization H Front Porch Bitmapping the 640 x 360 Image