Diseo lgico combinacional mediante VHDL Ing Diego Barragn

Diseño lógico combinacional mediante VHDL Ing. Diego Barragán Guerrero http: //www. decom. fee. unicamp. br/~diego/

Introducción �La lógica combinacional es probablemente la más fácil de diseñar. �En cada momento las salidas de un circuito combinacional sólo dependen del estado actual de sus entradas. �El circuito no tiene memoria.

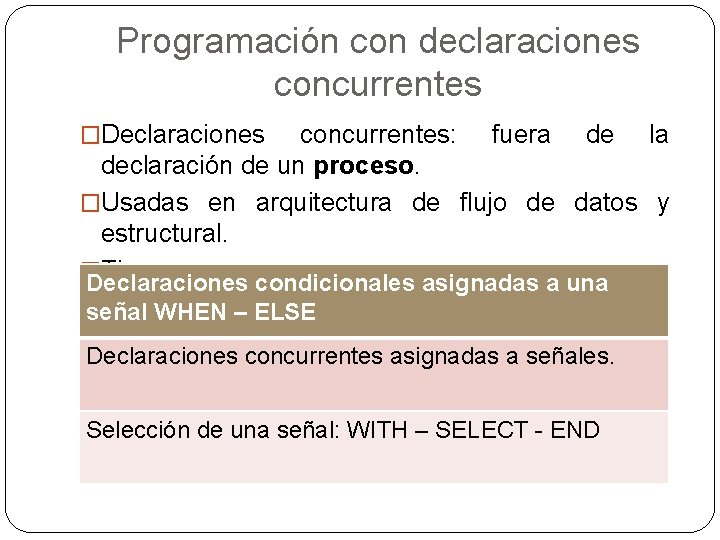

Programación con declaraciones concurrentes �Declaraciones concurrentes: fuera de la declaración de un proceso. �Usadas en arquitectura de flujo de datos y estructural. �Tipos: Declaraciones condicionales asignadas a una señal WHEN – ELSE Declaraciones concurrentes asignadas a señales. Selección de una señal: WITH – SELECT - END

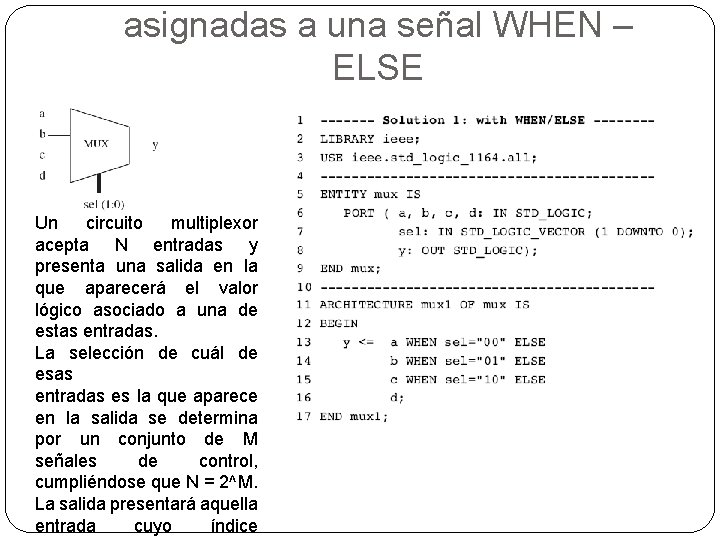

asignadas a una señal WHEN – ELSE Un circuito multiplexor acepta N entradas y presenta una salida en la que aparecerá el valor lógico asociado a una de estas entradas. La selección de cuál de esas entradas es la que aparece en la salida se determina por un conjunto de M señales de control, cumpliéndose que N = 2^M. La salida presentará aquella entrada cuyo índice

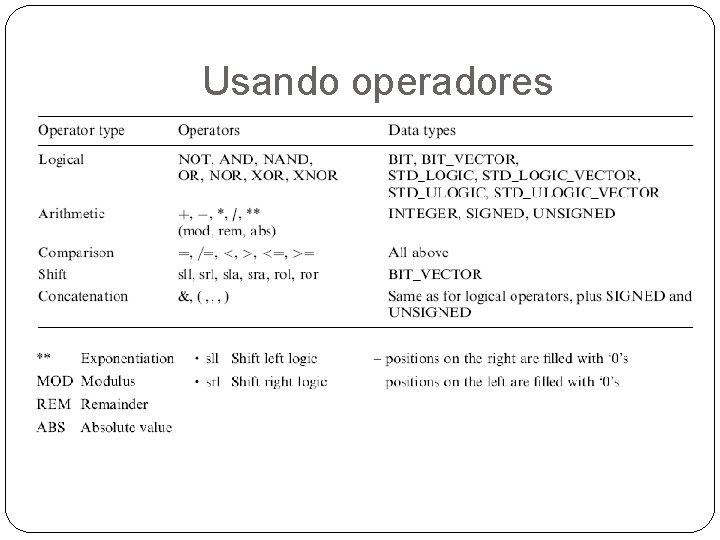

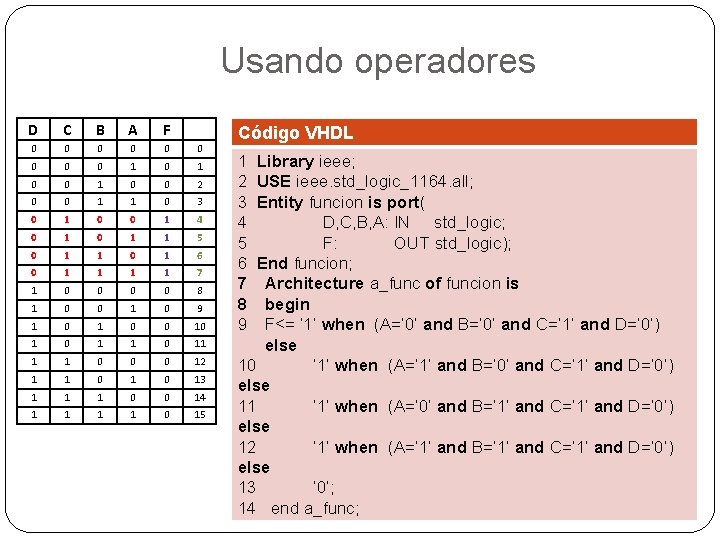

Usando operadores

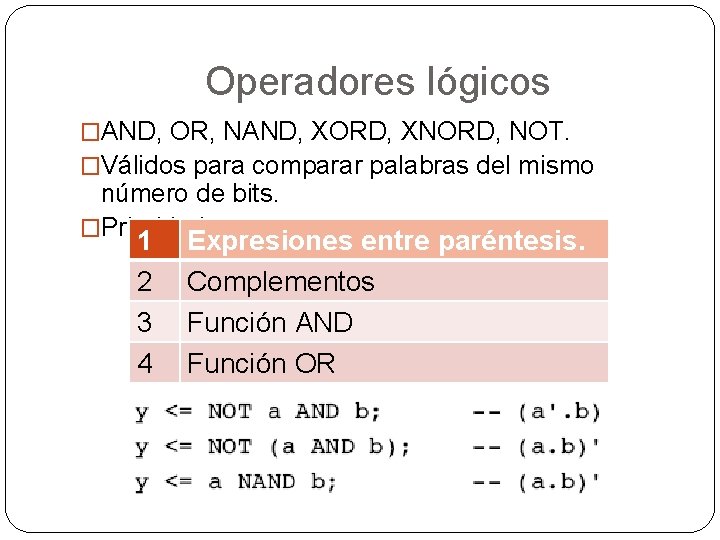

Operadores lógicos �AND, OR, NAND, XORD, XNORD, NOT. �Válidos para comparar palabras del mismo número de bits. �Prioridad: 1 2 3 4 Expresiones entre paréntesis. Complementos Función AND Función OR

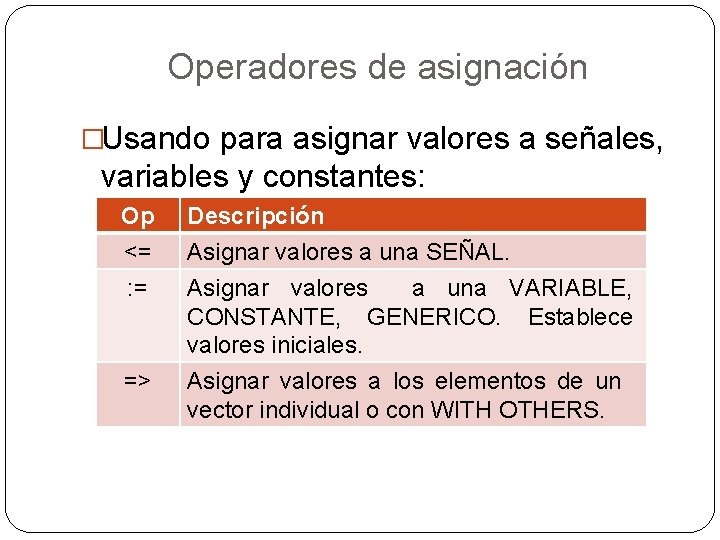

Operadores de asignación �Usando para asignar valores a señales, variables y constantes: Op <= : = Descripción Asignar valores a una SEÑAL. Asignar valores a una VARIABLE, CONSTANTE, GENERICO. Establece valores iniciales. => Asignar valores a los elementos de un vector individual o con WITH OTHERS.

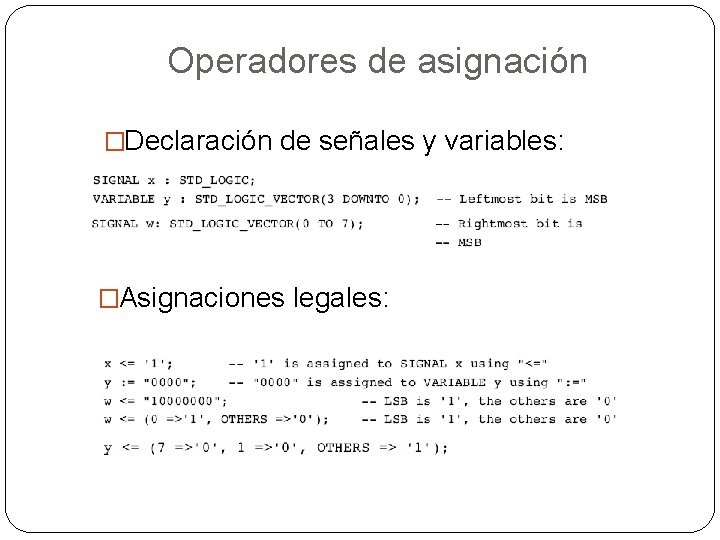

Operadores de asignación �Declaración de señales y variables: �Asignaciones legales:

Usando operadores D C B A F 0 0 0 0 0 1 0 0 2 0 0 1 1 0 3 0 1 0 0 1 4 0 1 1 5 0 1 1 0 1 6 0 1 1 7 1 0 0 8 1 0 0 1 0 9 1 0 0 10 1 1 0 11 1 1 0 0 0 12 1 1 0 13 1 1 1 0 0 14 1 1 0 15 Código VHDL 1 2 3 4 5 6 7 8 9 Library ieee; USE ieee. std_logic_1164. all; Entity funcion is port( D, C, B, A: IN std_logic; F: OUT std_logic); End funcion; Architecture a_func of funcion is begin F<= ‘ 1’ when (A=‘ 0’ and B=‘ 0’ and C=‘ 1’ and D=‘ 0’) else 10 ‘ 1’ when (A=‘ 1’ and B=‘ 0’ and C=‘ 1’ and D=‘ 0’) else 11 ‘ 1’ when (A=‘ 0’ and B=‘ 1’ and C=‘ 1’ and D=‘ 0’) else 12 ‘ 1’ when (A=‘ 1’ and B=‘ 1’ and C=‘ 1’ and D=‘ 0’) else 13 ‘ 0’; 14 end a_func;

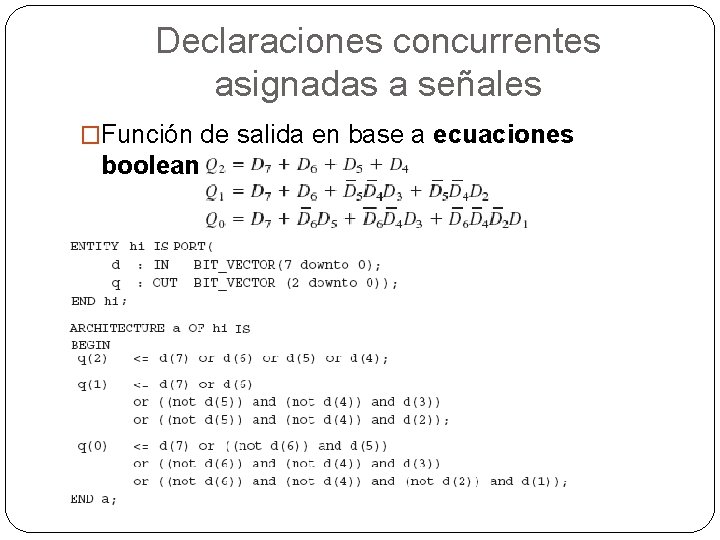

Declaraciones concurrentes asignadas a señales �Función de salida en base a ecuaciones booleanas.

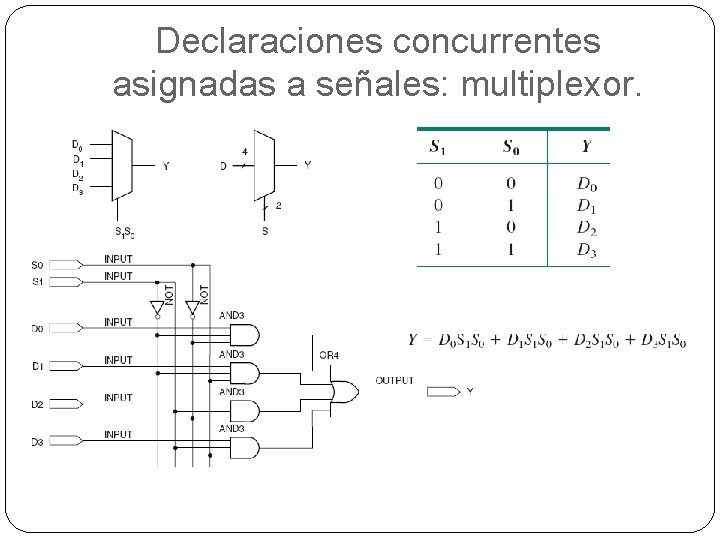

Declaraciones concurrentes asignadas a señales: multiplexor.

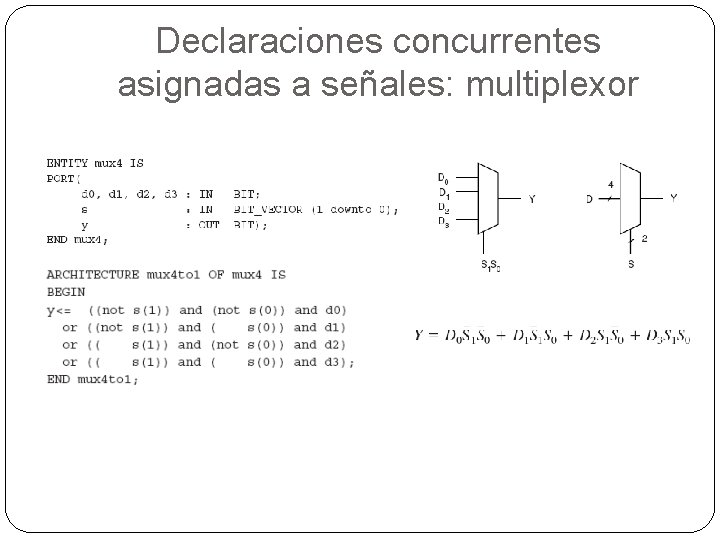

Declaraciones concurrentes asignadas a señales: multiplexor

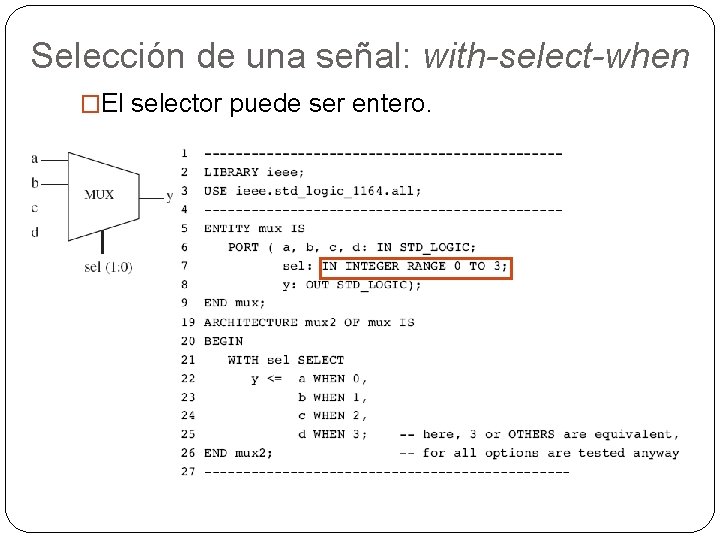

Selección de una señal: with-select-when �Whith-select-else se utiliza para asignar un valor a una señal con base en el valor de otra señal previamente seleccionada.

Selección de una señal: with-select-when �El selector puede ser entero.

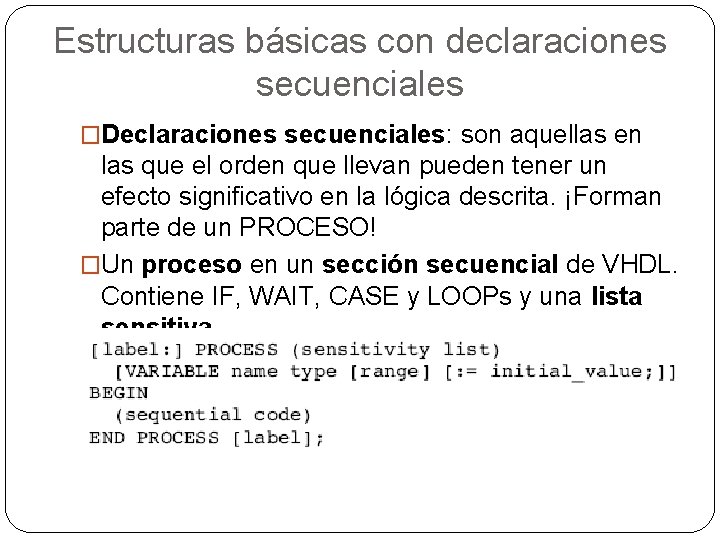

Estructuras básicas con declaraciones secuenciales �Declaraciones secuenciales: son aquellas en las que el orden que llevan pueden tener un efecto significativo en la lógica descrita. ¡Forman parte de un PROCESO! �Un proceso en un sección secuencial de VHDL. Contiene IF, WAIT, CASE y LOOPs y una lista sensitiva. �Sintaxis:

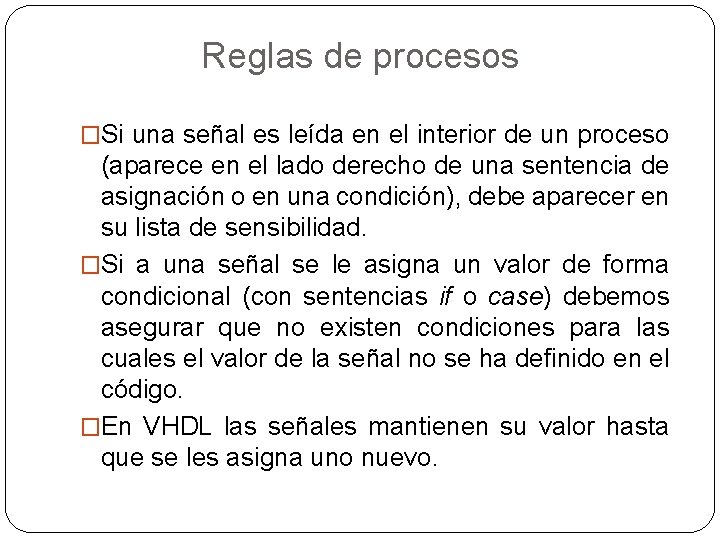

Reglas de procesos �Si una señal es leída en el interior de un proceso (aparece en el lado derecho de una sentencia de asignación o en una condición), debe aparecer en su lista de sensibilidad. �Si a una señal se le asigna un valor de forma condicional (con sentencias if o case) debemos asegurar que no existen condiciones para las cuales el valor de la señal no se ha definido en el código. �En VHDL las señales mantienen su valor hasta que se les asigna uno nuevo.

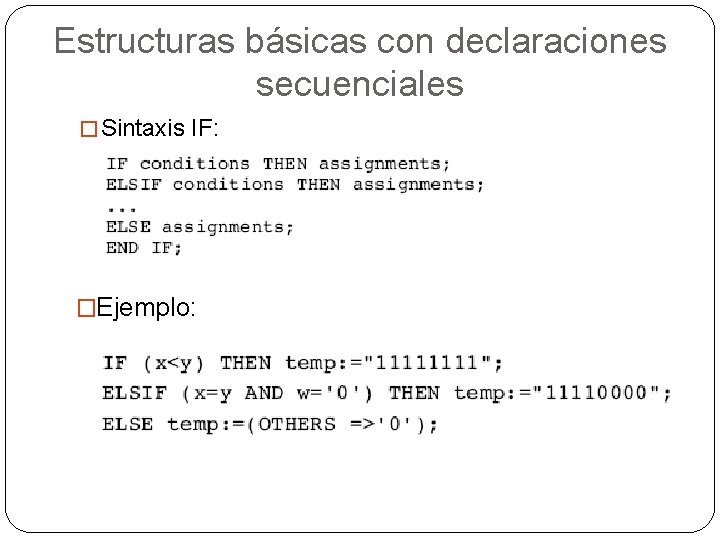

Estructuras básicas con declaraciones secuenciales � Sintaxis IF: �Ejemplo:

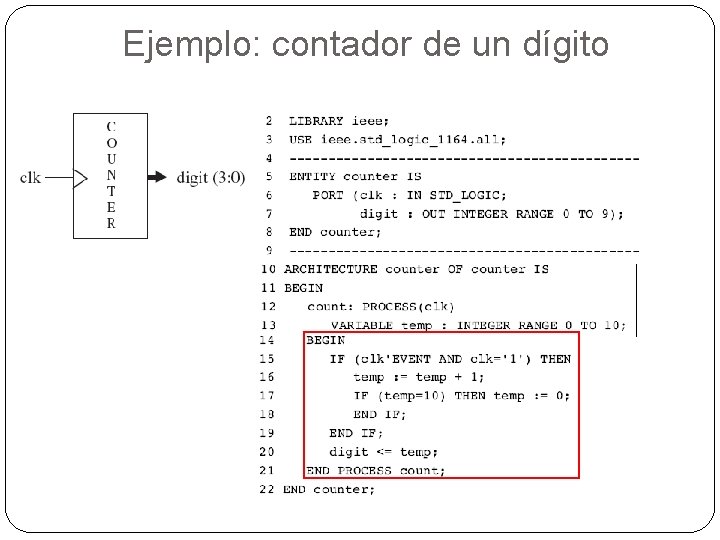

Ejemplo: contador de un dígito

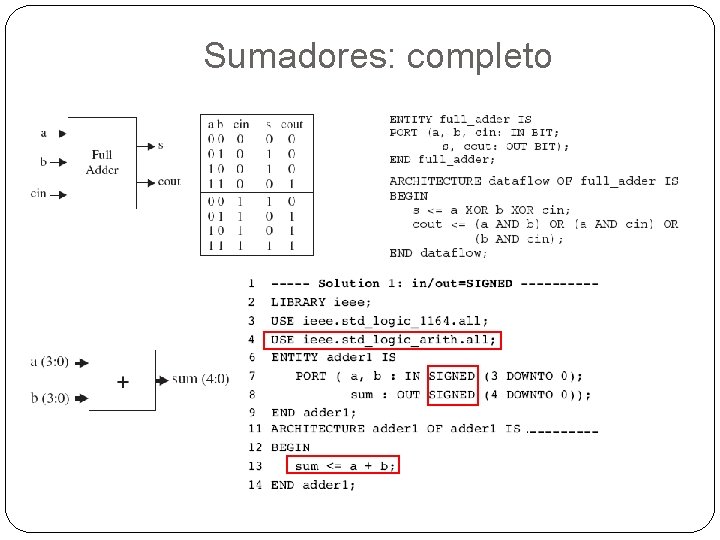

Sumadores: completo

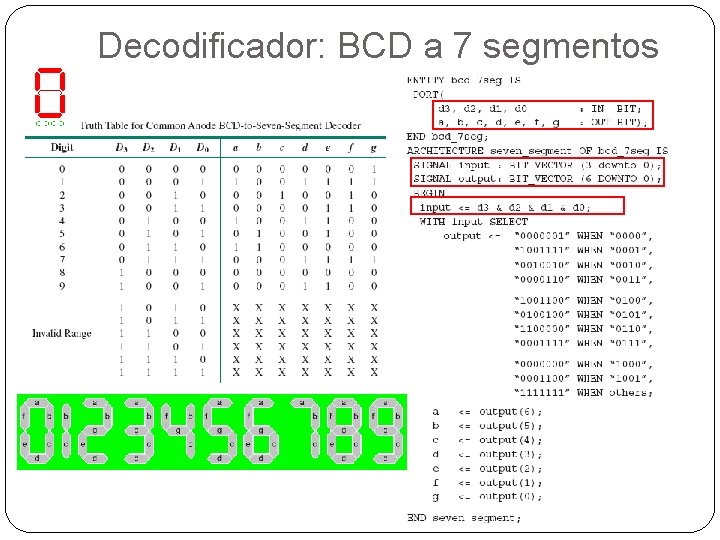

Decodificador: BCD a 7 segmentos

Referencias: �Volnei A. Pedroni. 2004. Circuit Design with VHDL. MIT Press, Cambridge, MA, USA. �Maxinez, D. G. , Alcalá, J. 2003. VHDL: el arte de programar sistemas digitales. Compañía Editorial Continental.

- Slides: 21