Diseo de microprocesadores para multimedia Procesadores de streams

- Slides: 63

Diseño de microprocesadores para multimedia Procesadores de streams Pedro Hernández Fernández Antonio Núñez Ordóñez Procesadores de streams

Procesadores de streams Contenido - Características generales - Arquitectura IMAGINE - Arquitectura MERRIMAC Procesadores de streams

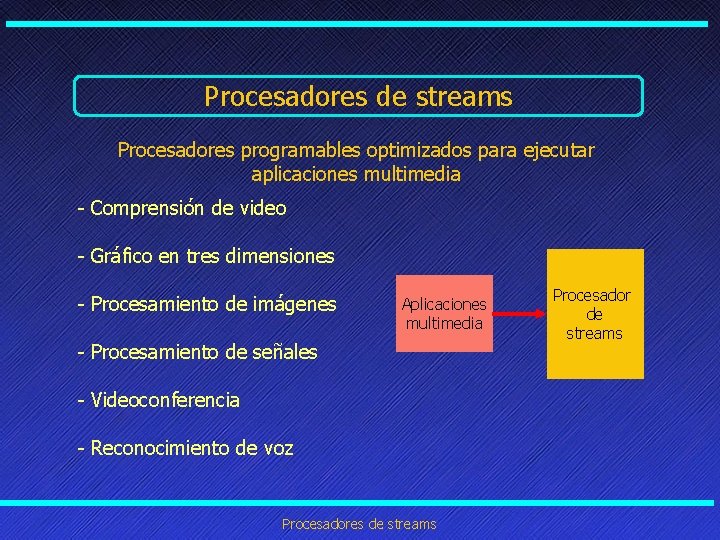

Procesadores de streams Procesadores programables optimizados para ejecutar aplicaciones multimedia - Comprensión de video - Gráfico en tres dimensiones - Procesamiento de imágenes Aplicaciones multimedia - Procesamiento de señales - Videoconferencia - Reconocimiento de voz Procesadores de streams Procesador de streams

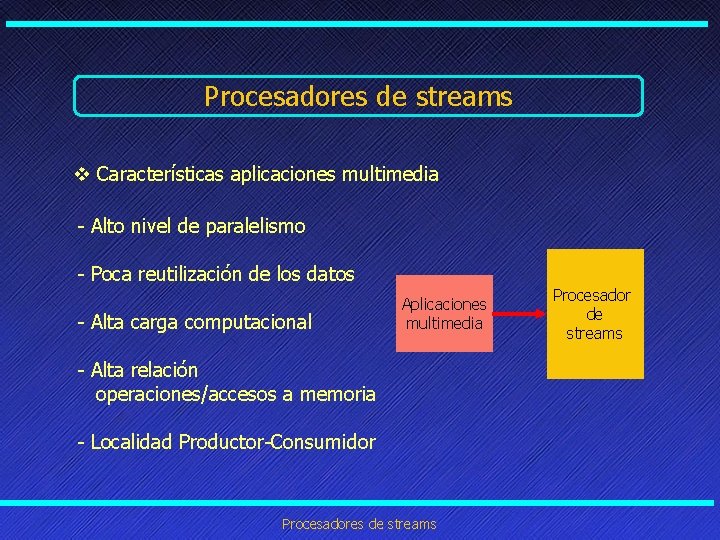

Procesadores de streams v Características aplicaciones multimedia - Alto nivel de paralelismo - Poca reutilización de los datos - Alta carga computacional Aplicaciones multimedia - Alta relación operaciones/accesos a memoria - Localidad Productor-Consumidor Procesadores de streams Procesador de streams

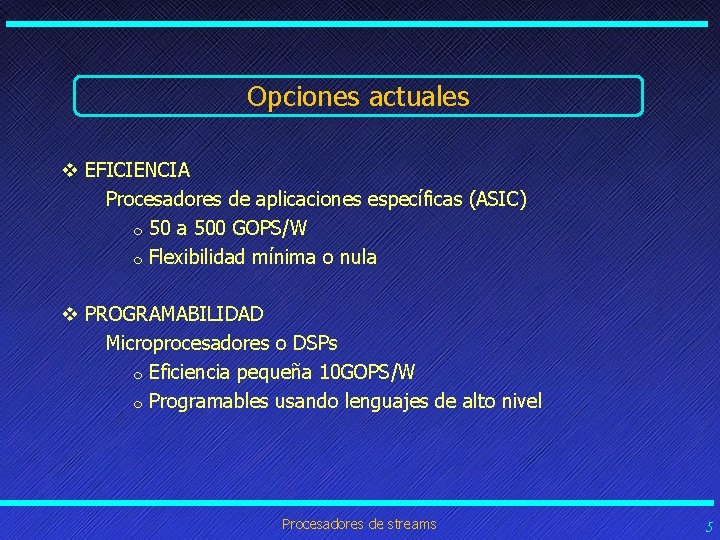

Opciones actuales v EFICIENCIA Procesadores de aplicaciones específicas (ASIC) m 50 a 500 GOPS/W m Flexibilidad mínima o nula v PROGRAMABILIDAD Microprocesadores o DSPs m Eficiencia pequeña 10 GOPS/W m Programables usando lenguajes de alto nivel Procesadores de streams 5

Opciones actuales Procesadores aplicaciones específicas Eficientes Flexibilidad mínima Procesadores de streams Eficientes Programables Procesadores de streams DSPs Microprocesadores Poco eficientes Programables 6

Fichero de registros central v Área proporcional al cubo del número de unidades funcionales v Potencia proporcional al cubo del número de unidades funcionales v Retardo proporcional 3/2 del número de unidades funcionales Procesadores de streams 7

1ª Solución: Fichero de registros múltiples v Sustituir el fichero único por múltiples ficheros de registros v Las unidades funcionales se agrupan v Se asigna a cada grupo su propio fichero de registros Procesadores de streams 8

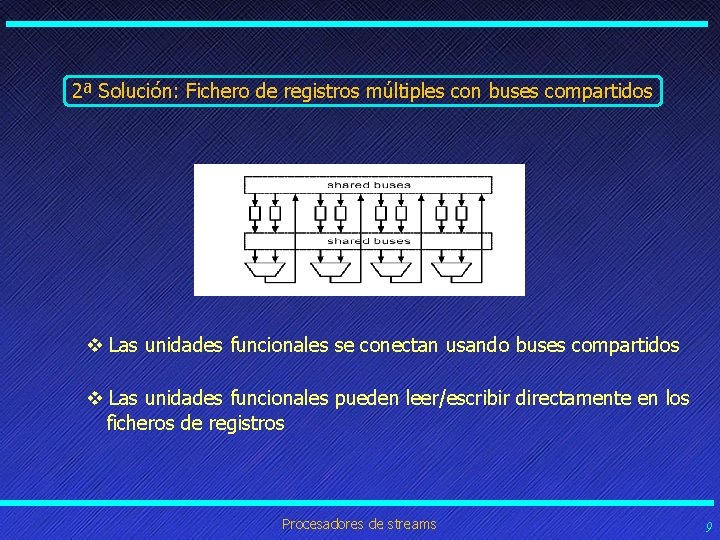

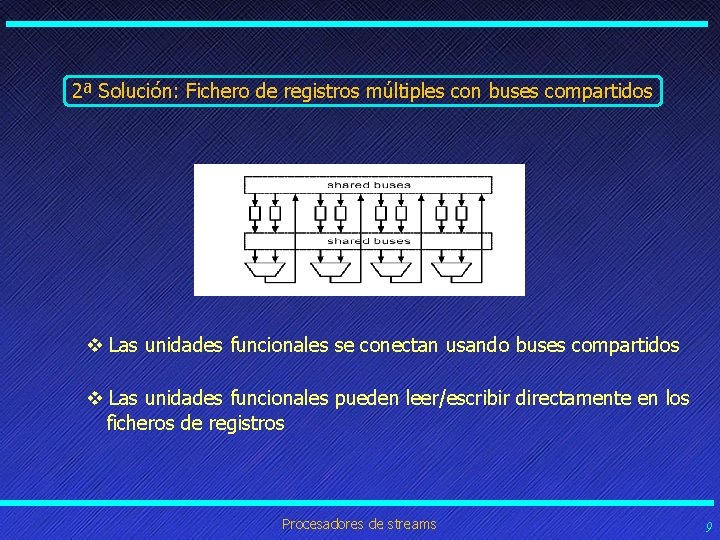

2ª Solución: Fichero de registros múltiples con buses compartidos v Las unidades funcionales se conectan usando buses compartidos v Las unidades funcionales pueden leer/escribir directamente en los ficheros de registros Procesadores de streams 9

Modelo de programación con streams Definiciones v El dato mínimo con el que se trabaja se denomina STREAM v STREAM: Conjunto de datos relacionados de longitud variable v KERNEL: Pequeño programa que realiza la misma operación sobre todos los elementos de un stream de entrada, produce un stream de salida para el siguiente kernel de la aplicación Procesadores de streams

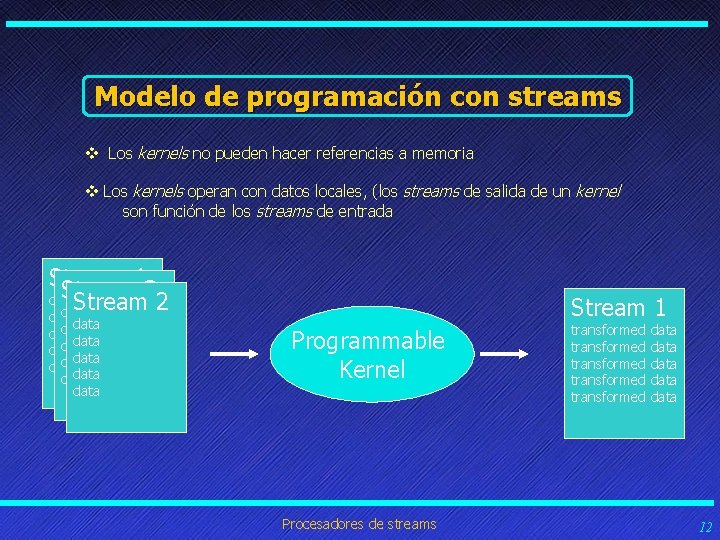

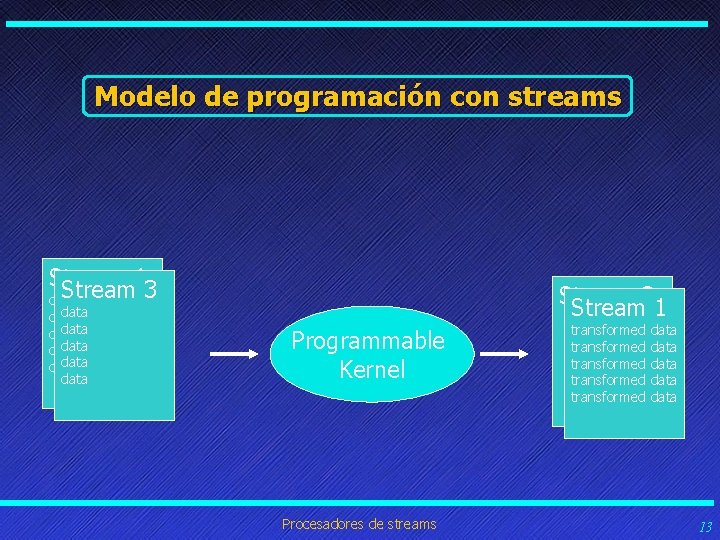

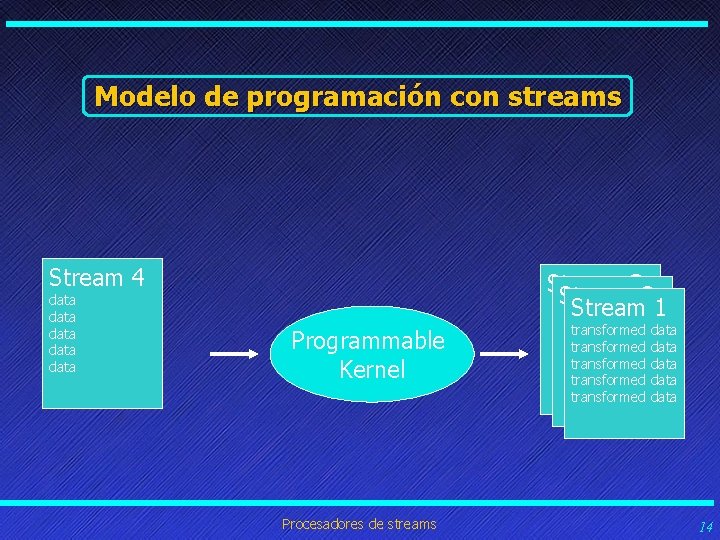

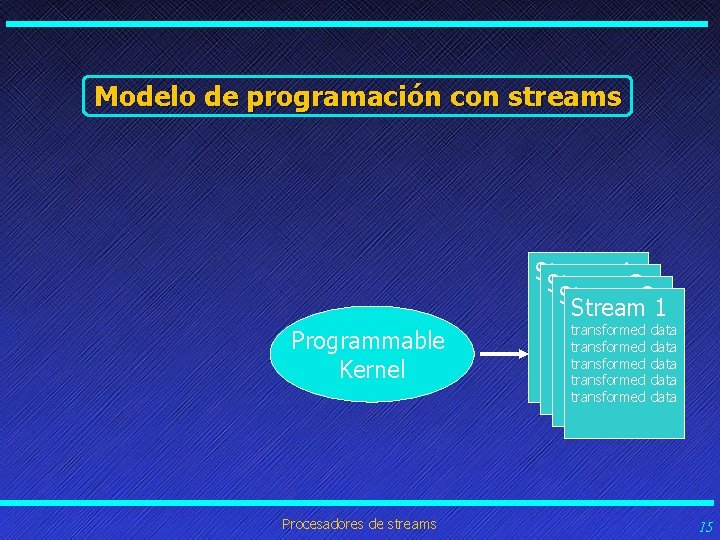

Modelo de programación con streams v Los programas se estructuran como una secuencia de streams de datos que pasan a través de unos kernels de cálculo v Las operaciones se realizan sobre el stream completo Stream 43 Stream data. Stream 2 data. Stream 1 data data data data data Programmable Kernel Procesadores de streams 11

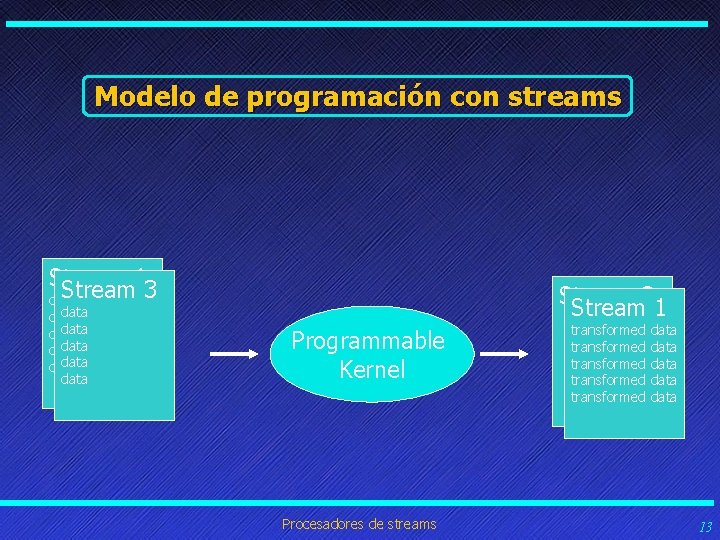

Modelo de programación con streams v Los kernels no pueden hacer referencias a memoria v Los kernels operan con datos locales, (los streams de salida de un kernel son función de los streams de entrada Stream 43 Stream data. Stream 2 data data data data Stream 1 Programmable Kernel Procesadores de streams transformed transformed data data 12

Modelo de programación con streams Stream 43 Stream data data data Programmable Kernel Procesadores de streams Stream 21 Stream data transformed data transformed data data 13

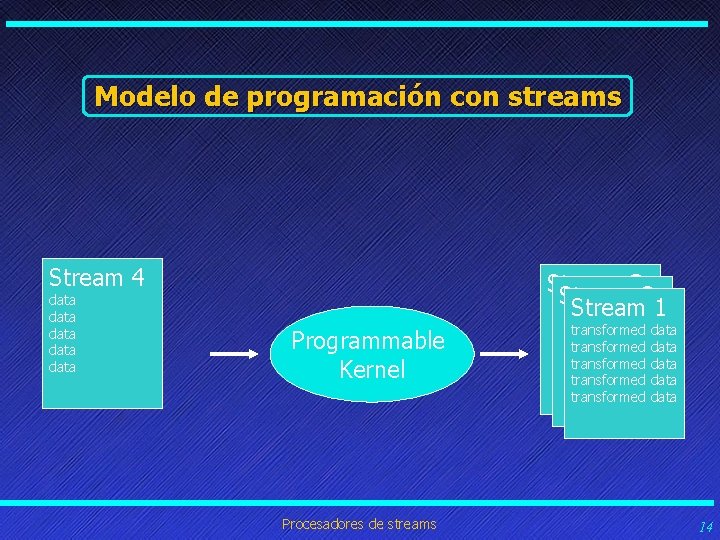

Modelo de programación con streams Stream 4 data data Programmable Kernel Procesadores de streams Stream 32 Stream data Stream 1 data data transformed data transformed data data 14

Modelo de programación con streams Programmable Kernel Procesadores de streams Stream 43 Stream data Stream 21 data Stream data data transformed data transformed data data 15

Modelo de programación con streams Los programas en este modelo se especifican en dos niveles v A nivel de streams - La secuencia de kernels que forman la aplicación - Como están conectados esos kernels - Nombre y tamaño de los streams con los que se opera v A nivel de kernel - Especifica las operaciones a realizar con los datos Procesadores de streams 16

Jerarquía de memoria v Las aplicaciones requieren un manejo adecuado del ancho de banda con memoria v La jerarquía de memoria tiene tres niveles: - Un nivel de memoria principal: datos grandes o que se acceden de forma no frecuente - Nivel intermedio : Aprovechar la localidad de los datos dentro del chip - Nivel local: Almacenar datos temporales en las operaciones de cálculo v Las aplicaciones multimedia se adaptan perfectamente a este jerarquía v La ejecución de los kernels es rápida y eficiente (sólo datos locales) v El 90% del movimiento de datos es local Procesadores de streams 17

Imagine Scott Rixner Universidad de Stanford Procesadores de streams

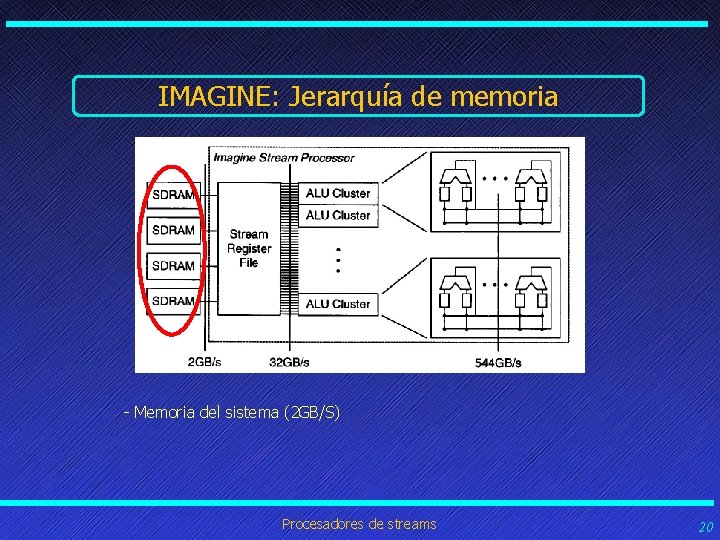

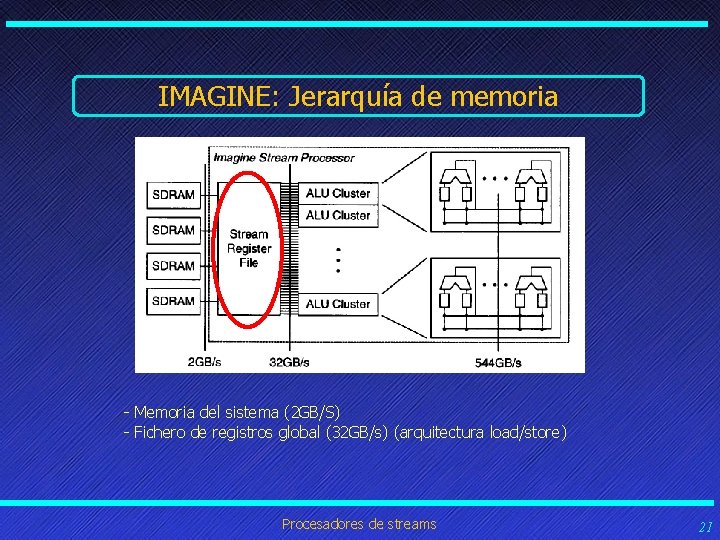

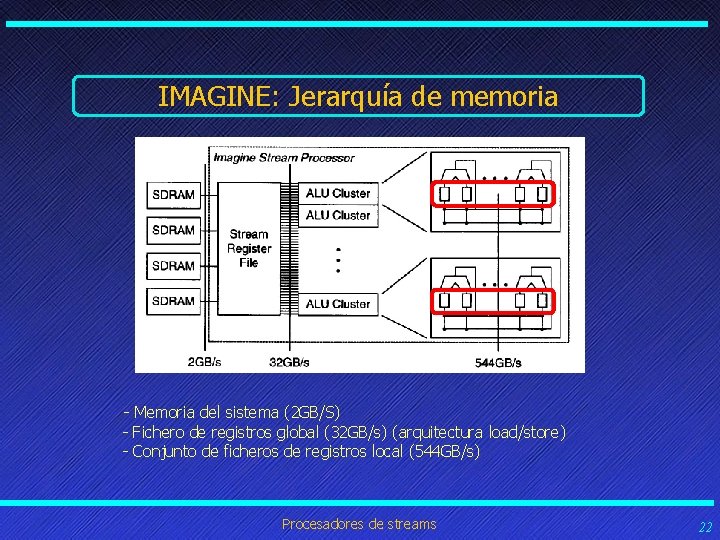

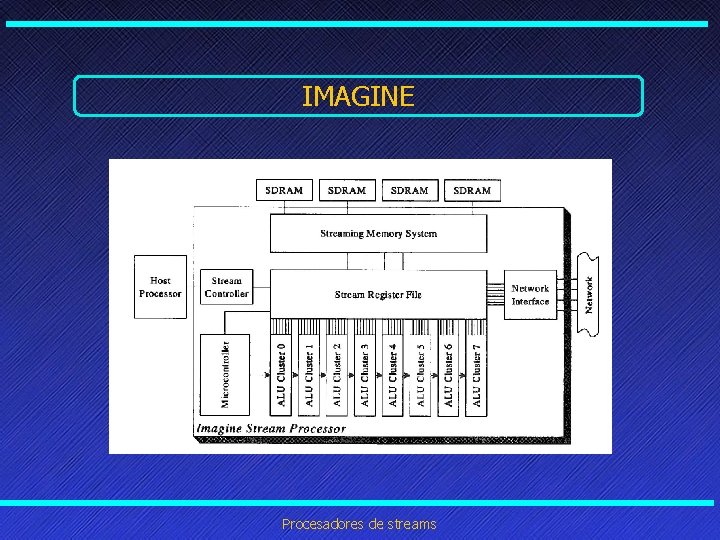

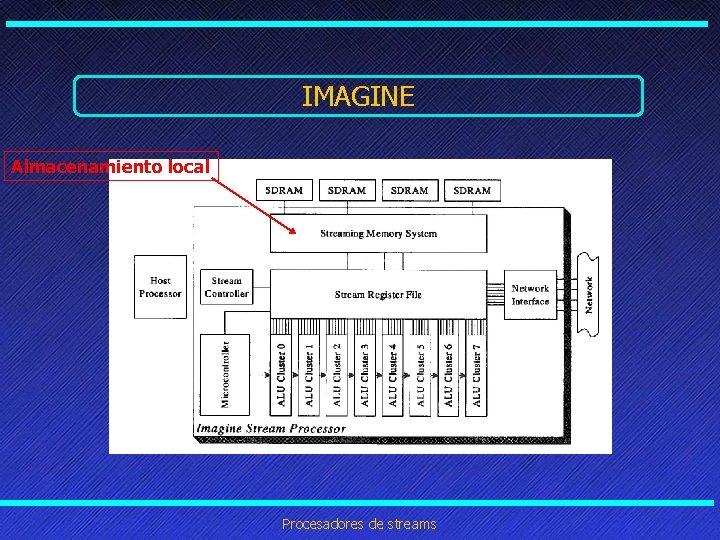

IMAGINE v Procesador multimedia programable diseñado para implementar el modelo de programación con streams v Diseñado para ser una prueba del concepto de procesador de streams programable, mostrando la viabilidad de las estructuras v Está pensado para actuar como un coprocesador que opera sobre streams de datos multimedia. v Diseño organizado alrededor de tres niveles de memoria - Memoria del sistema (memoria principal) - Un Fichero de registros global (nivel intermedio) - Un conjunto de ficheros de registros local (nivel local) Procesadores de streams

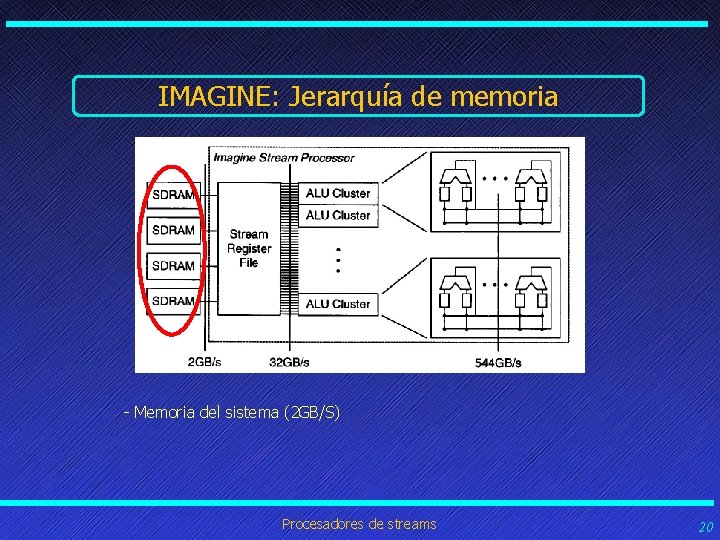

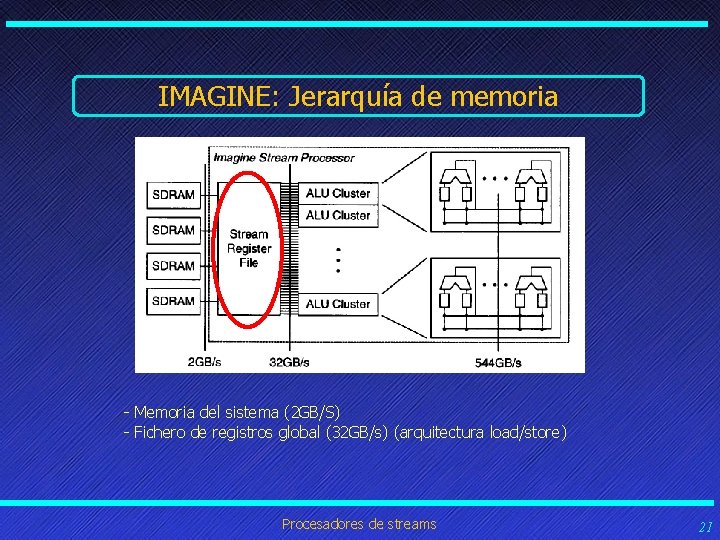

IMAGINE: Jerarquía de memoria - Memoria del sistema (2 GB/S) Procesadores de streams 20

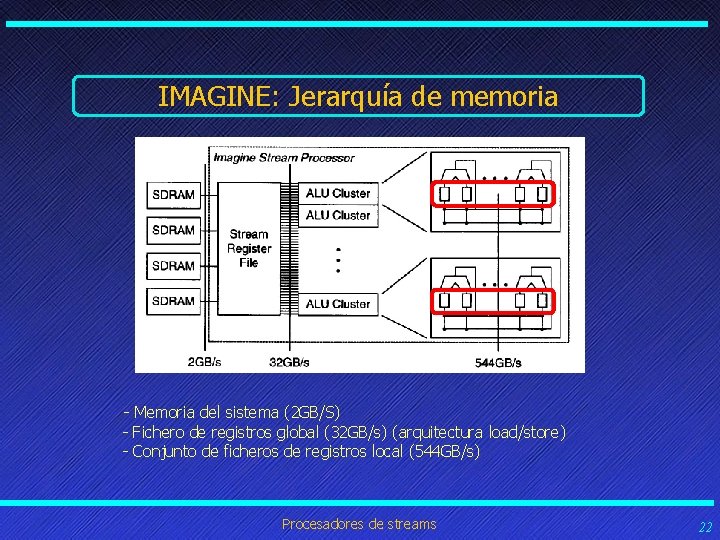

IMAGINE: Jerarquía de memoria - Memoria del sistema (2 GB/S) - Fichero de registros global (32 GB/s) (arquitectura load/store) Procesadores de streams 21

IMAGINE: Jerarquía de memoria - Memoria del sistema (2 GB/S) - Fichero de registros global (32 GB/s) (arquitectura load/store) - Conjunto de ficheros de registros local (544 GB/s) Procesadores de streams 22

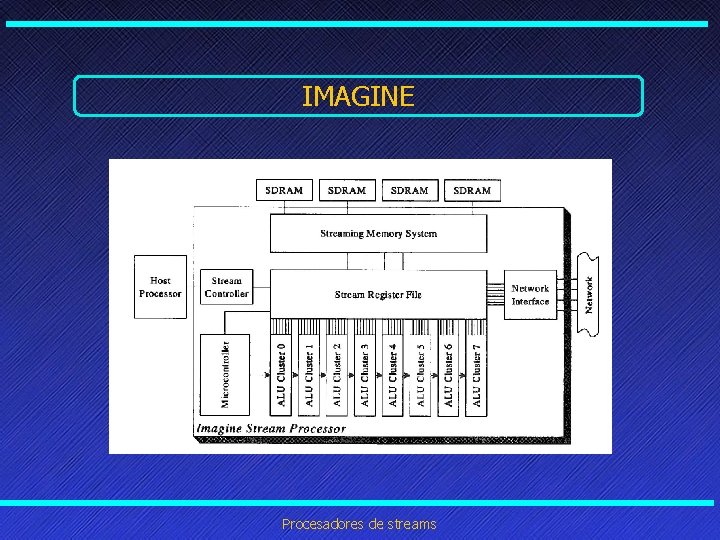

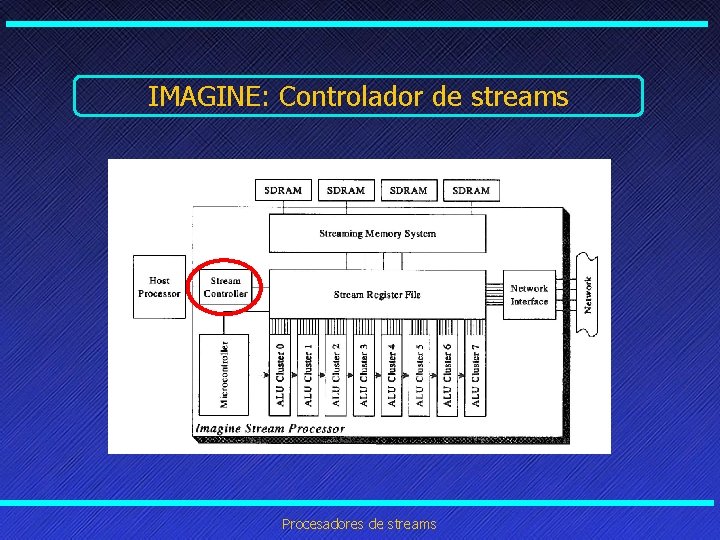

IMAGINE Procesadores de streams

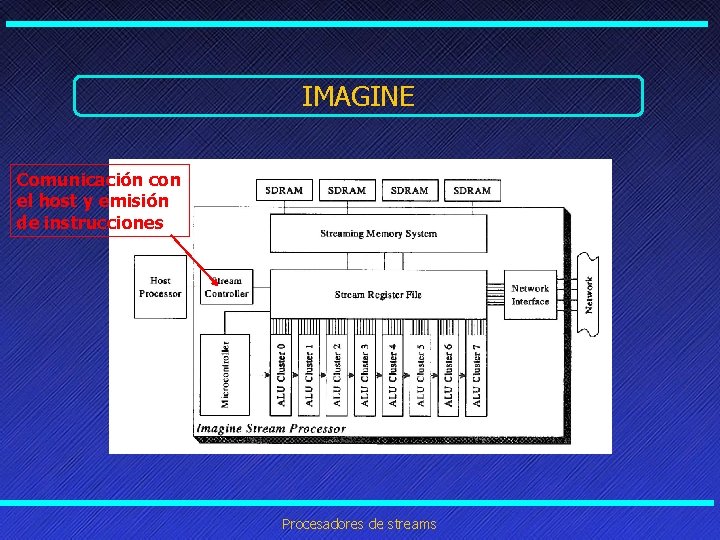

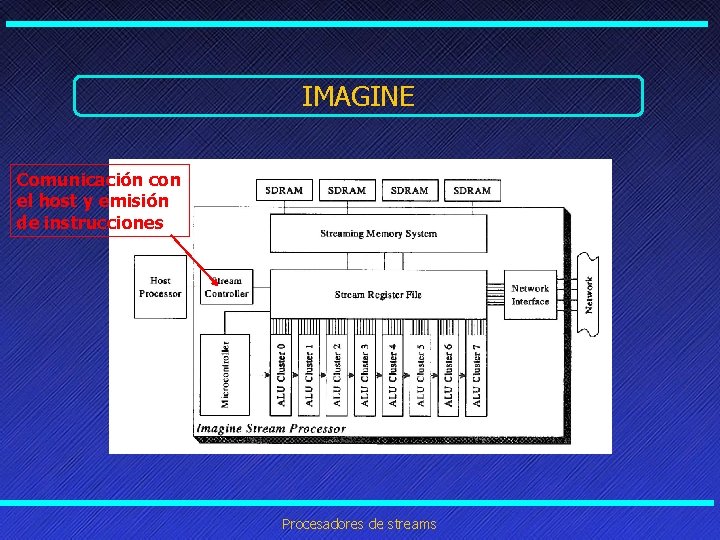

IMAGINE Comunicación con el host y emisión de instrucciones Procesadores de streams

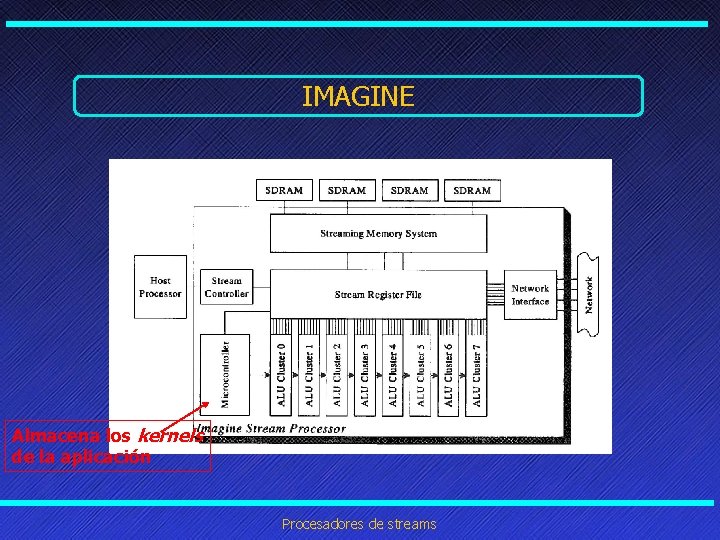

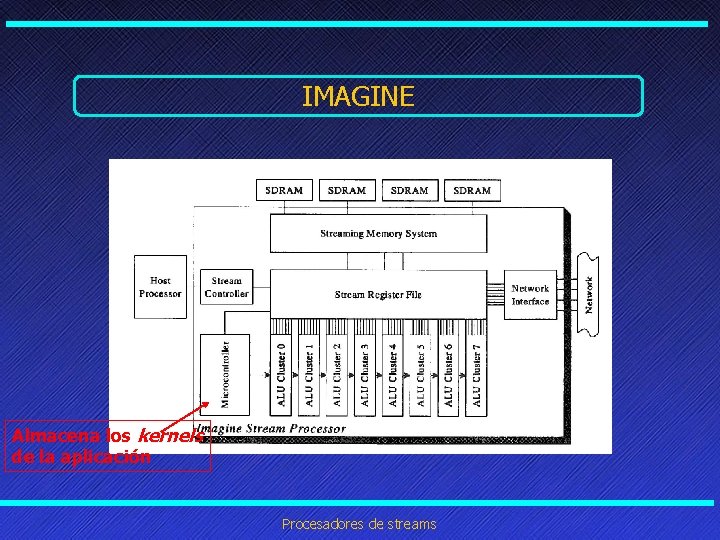

IMAGINE Almacena los kernels de la aplicación Procesadores de streams

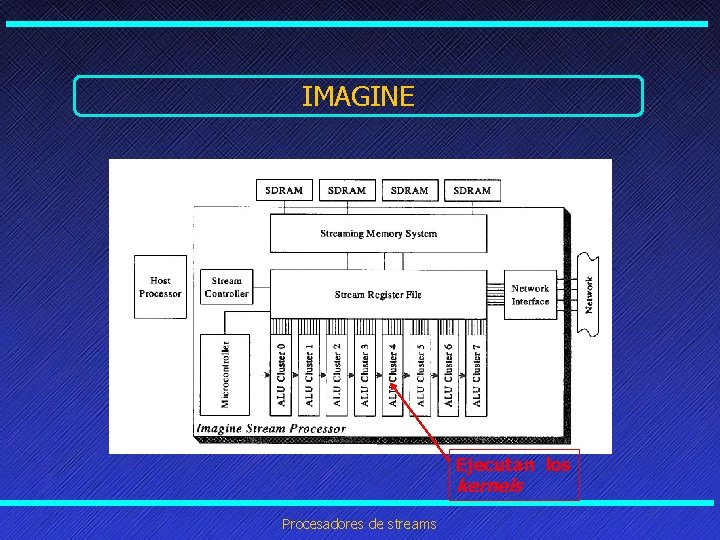

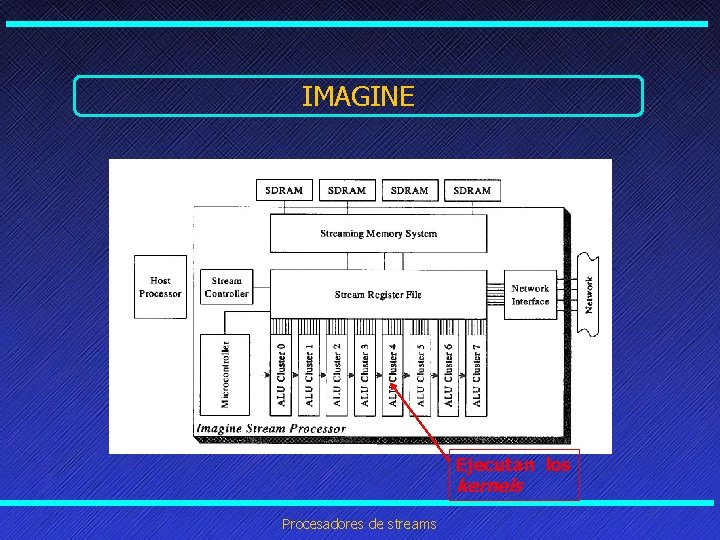

IMAGINE Ejecutan los kernels Procesadores de streams

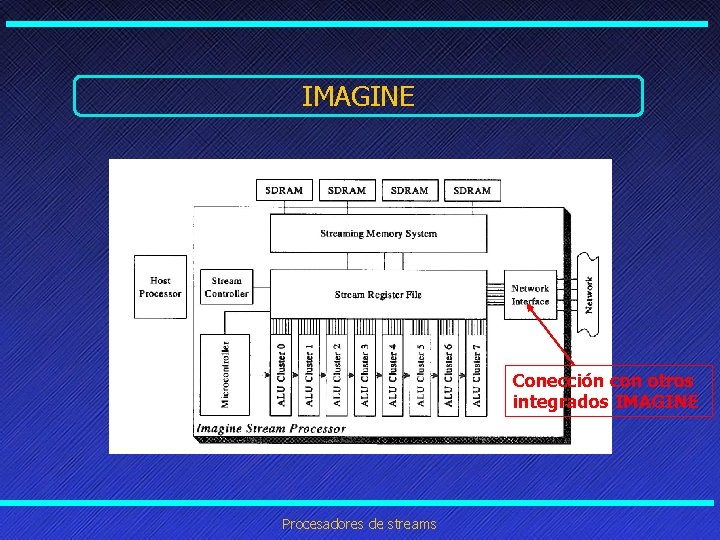

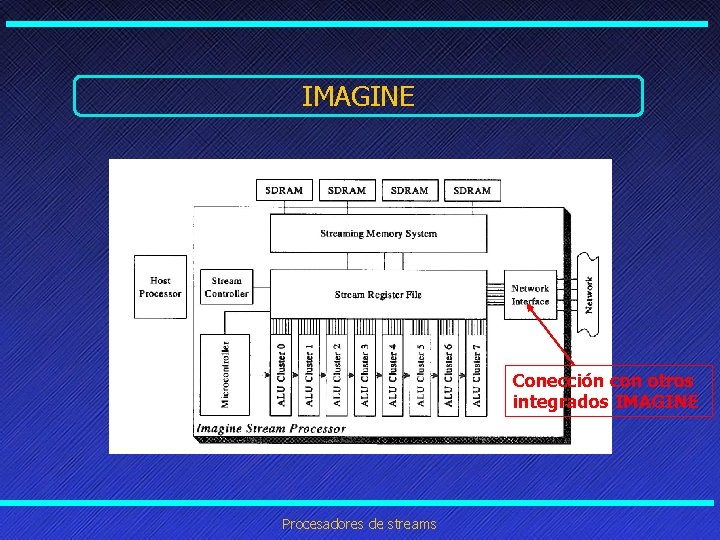

IMAGINE Conección con otros integrados IMAGINE Procesadores de streams

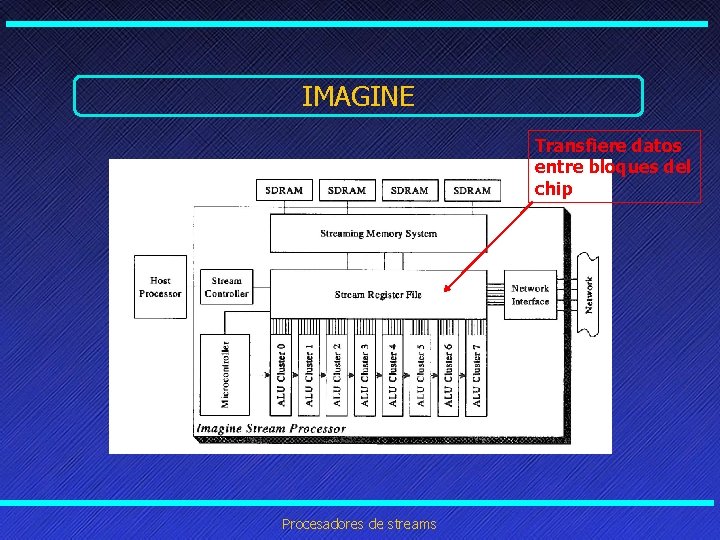

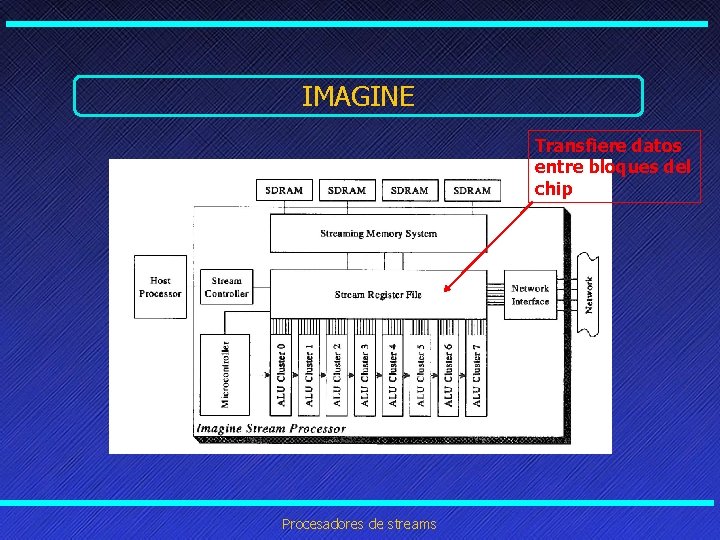

IMAGINE Transfiere datos entre bloques del chip Procesadores de streams

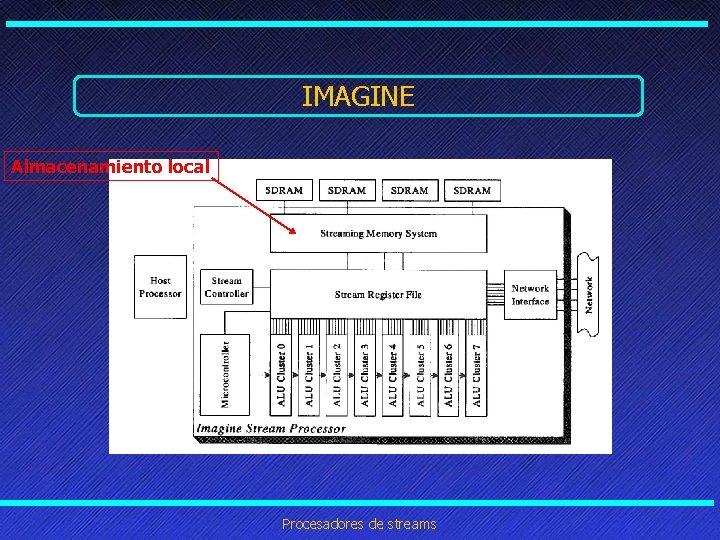

IMAGINE Almacenamiento local Procesadores de streams

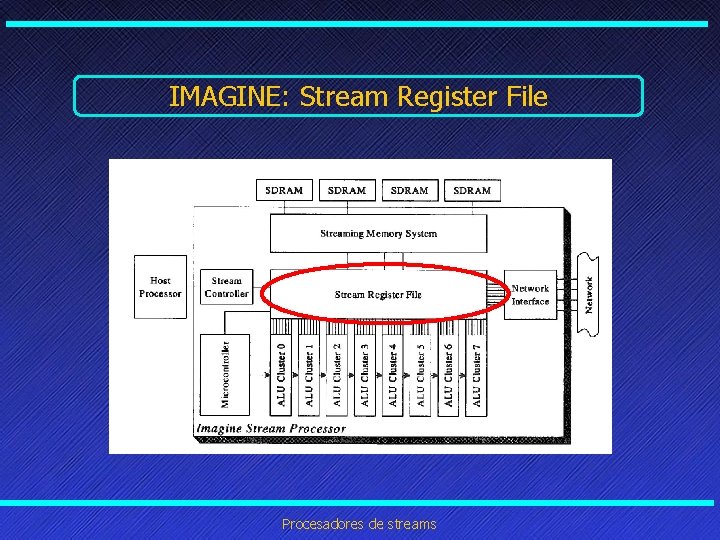

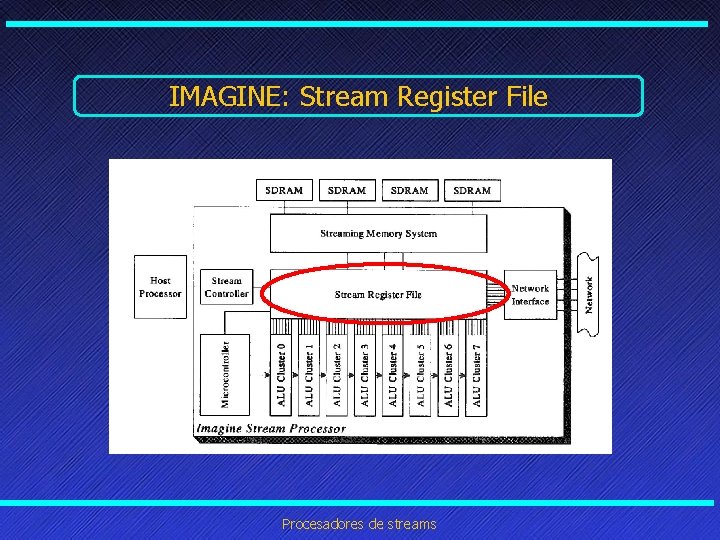

IMAGINE: Stream Register File Procesadores de streams

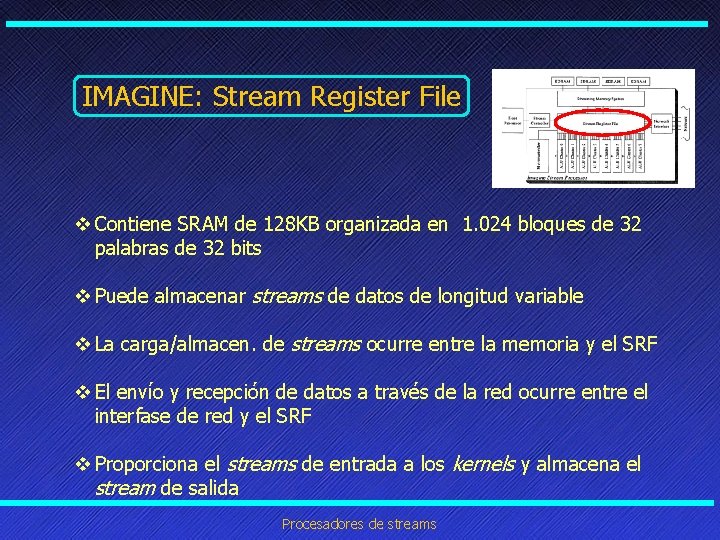

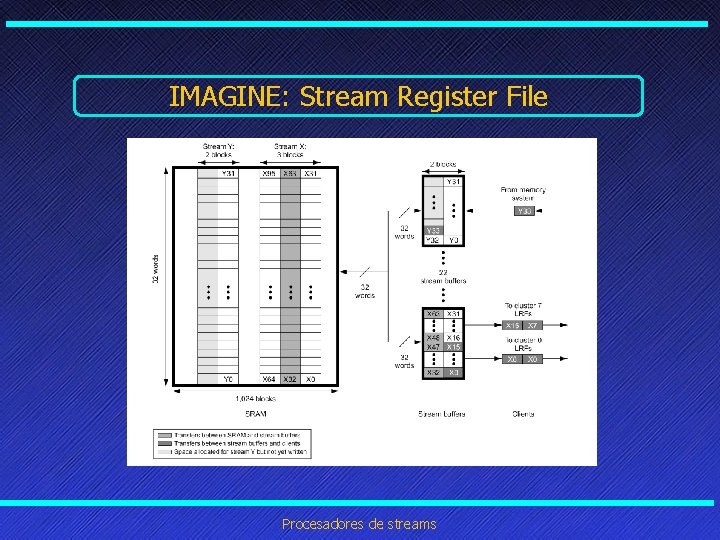

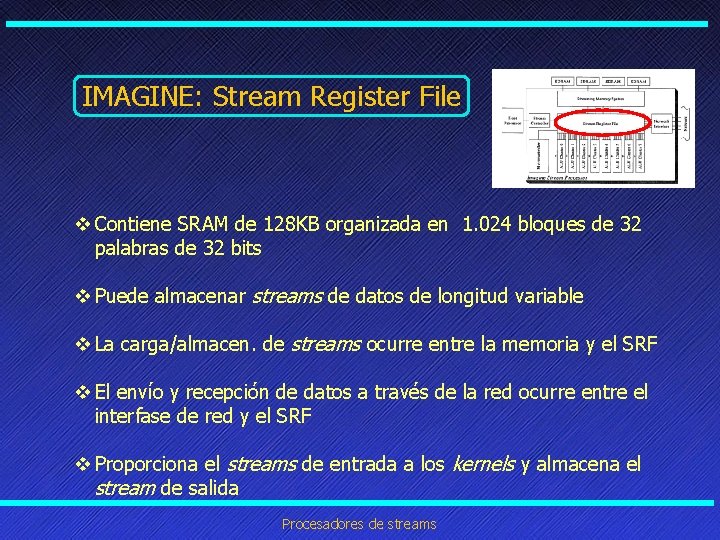

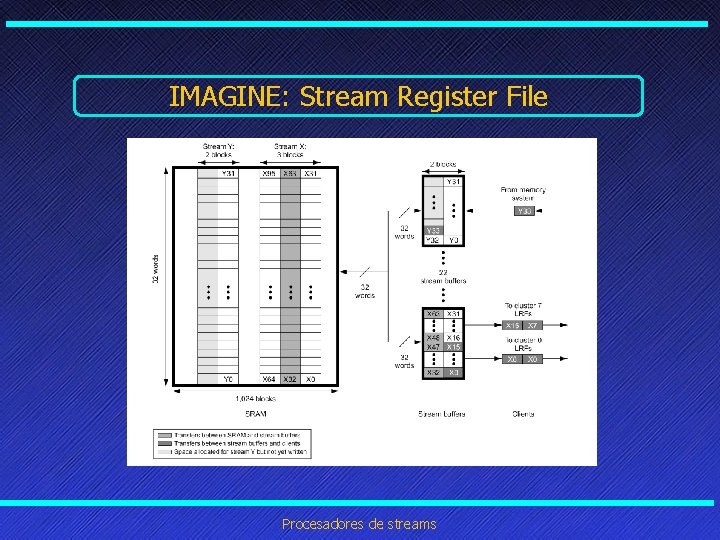

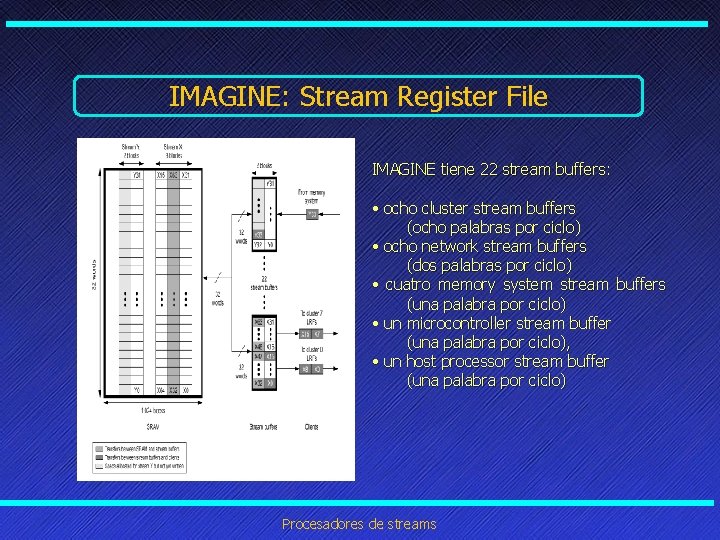

IMAGINE: Stream Register File v Contiene SRAM de 128 KB organizada en 1. 024 bloques de 32 palabras de 32 bits v Puede almacenar streams de datos de longitud variable v La carga/almacen. de streams ocurre entre la memoria y el SRF v El envío y recepción de datos a través de la red ocurre entre el interfase de red y el SRF v Proporciona el streams de entrada a los kernels y almacena el stream de salida Procesadores de streams

IMAGINE: Stream Register File Procesadores de streams

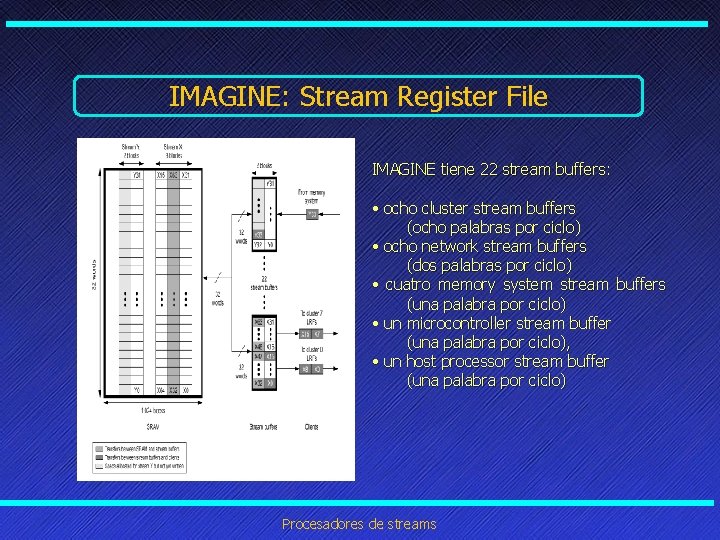

IMAGINE: Stream Register File IMAGINE tiene 22 stream buffers: • ocho cluster stream buffers (ocho palabras por ciclo) • ocho network stream buffers (dos palabras por ciclo) • cuatro memory system stream buffers (una palabra por ciclo) • un microcontroller stream buffer (una palabra por ciclo), • un host processor stream buffer (una palabra por ciclo) Procesadores de streams

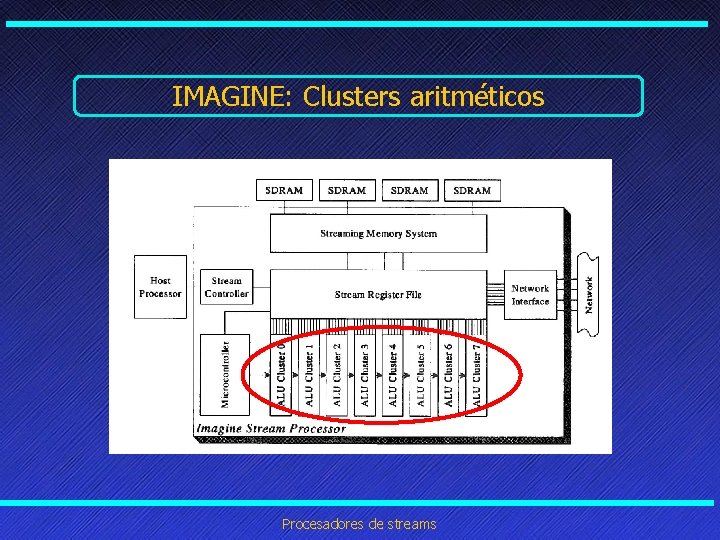

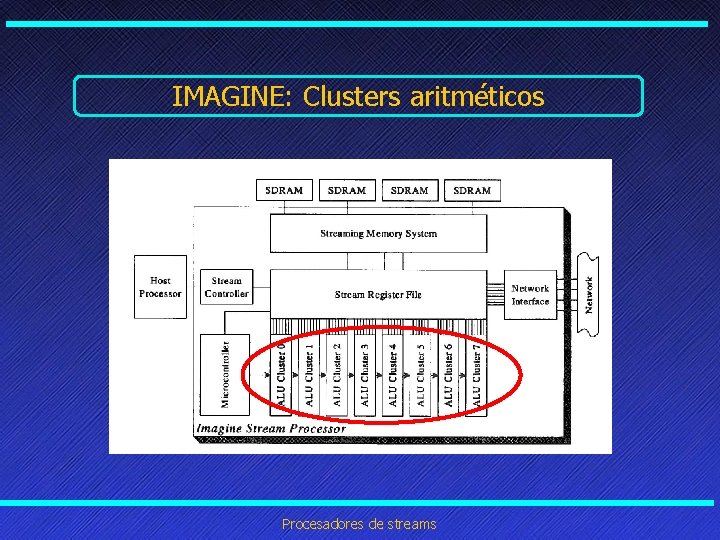

IMAGINE: Clusters aritméticos Procesadores de streams

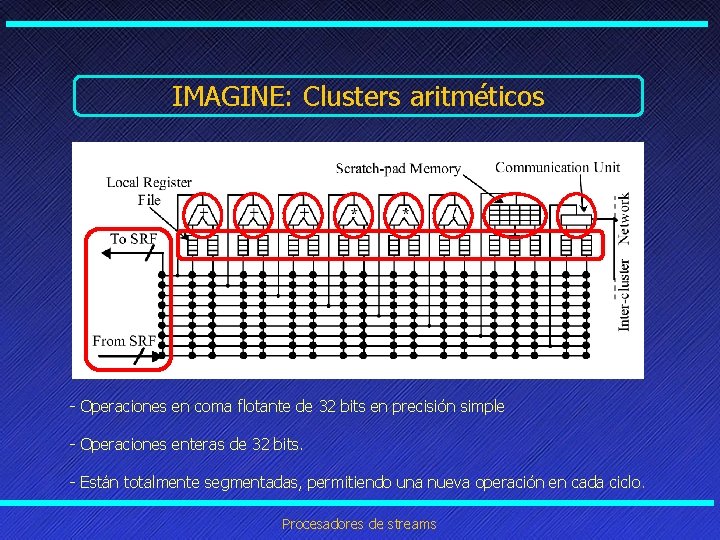

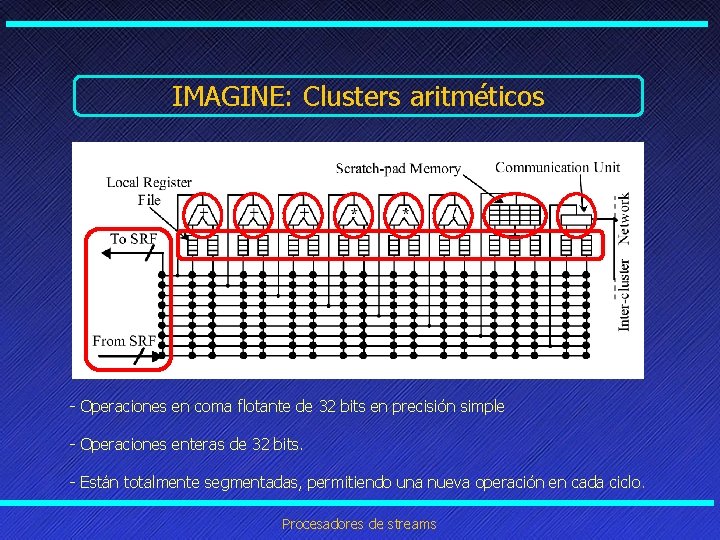

IMAGINE: Clusters aritméticos - Operaciones en coma flotante de 32 bits en precisión simple - Operaciones enteras de 32 bits. - Están totalmente segmentadas, permitiendo una nueva operación en cada ciclo. Procesadores de streams

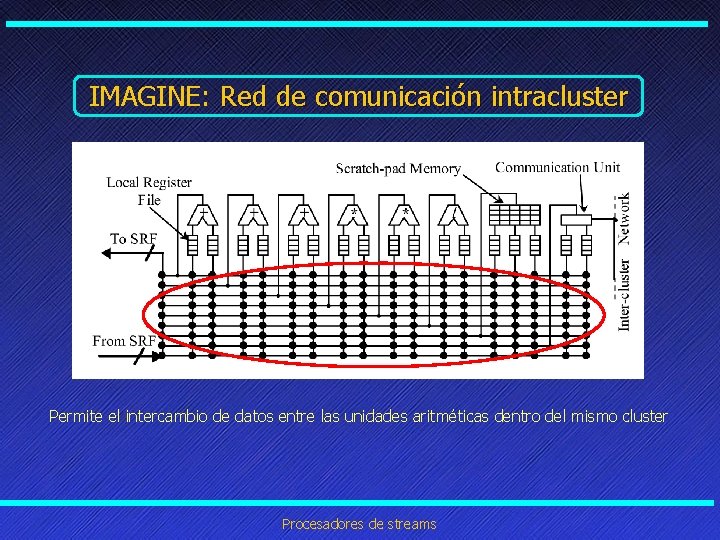

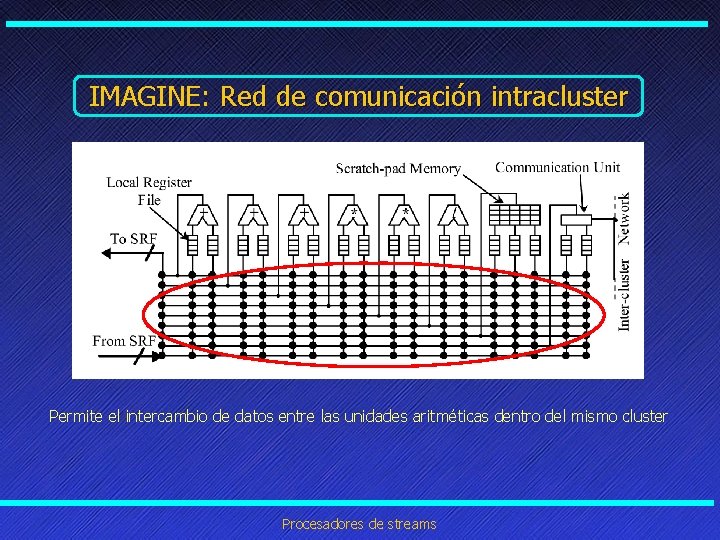

IMAGINE: Red de comunicación intracluster Permite el intercambio de datos entre las unidades aritméticas dentro del mismo cluster Procesadores de streams

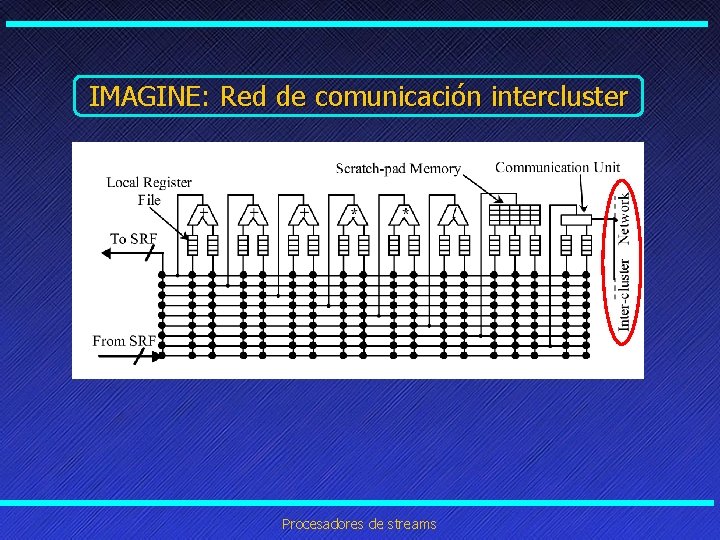

IMAGINE: Red de comunicación intercluster Procesadores de streams

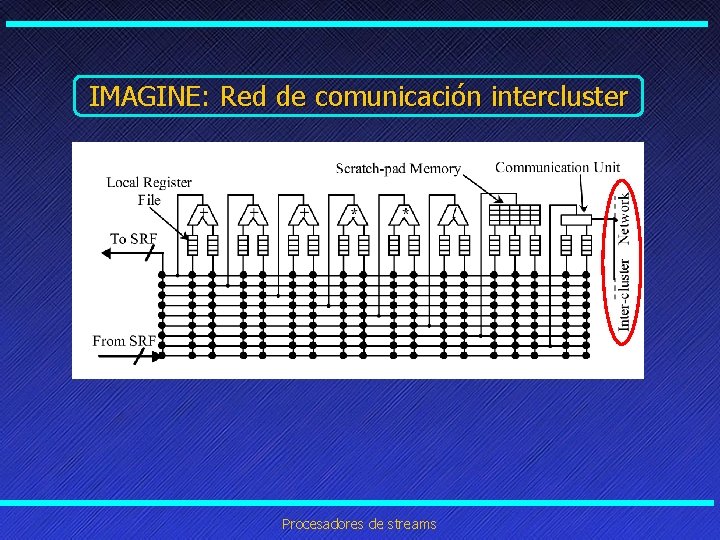

IMAGINE: Red de comunicación intercluster v La unidad de comunicación facilita el intercambio de datos entre clusters v La unidad de comunicación puede enviar una palabra cada ciclo de reloj v El microcontrolador tiene un bus propio para enviar datos a los clusters Procesadores de streams

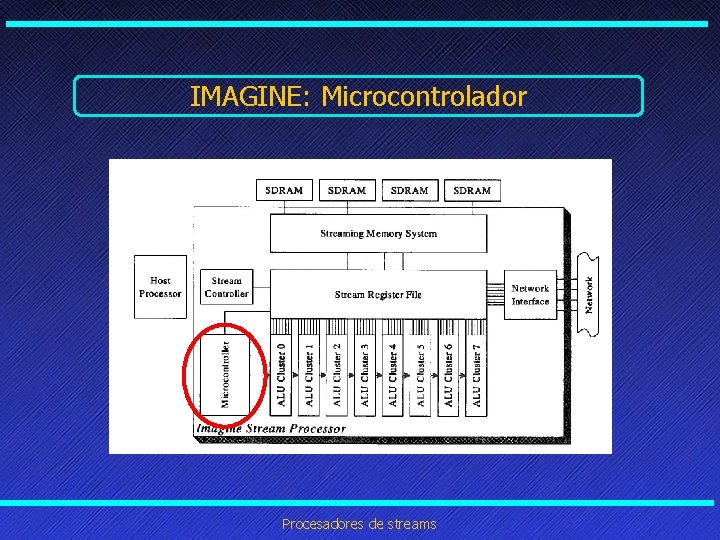

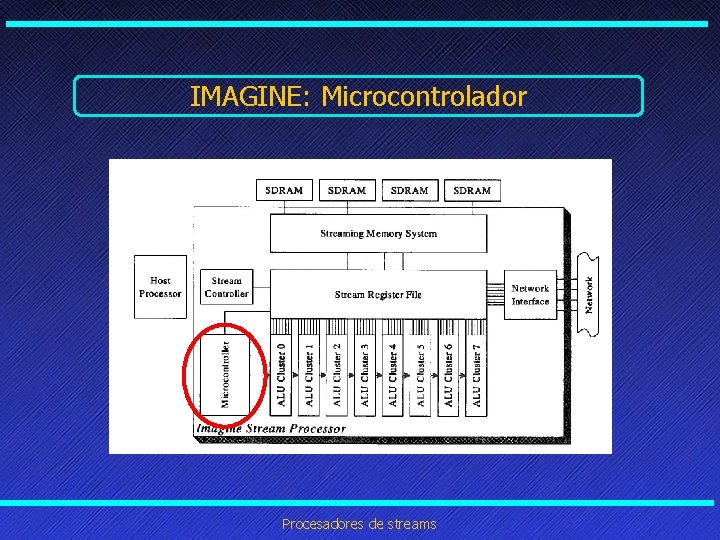

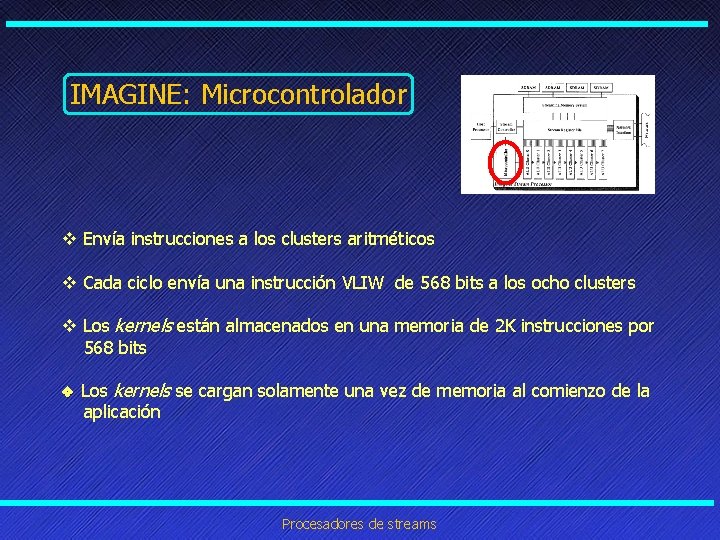

IMAGINE: Microcontrolador Procesadores de streams

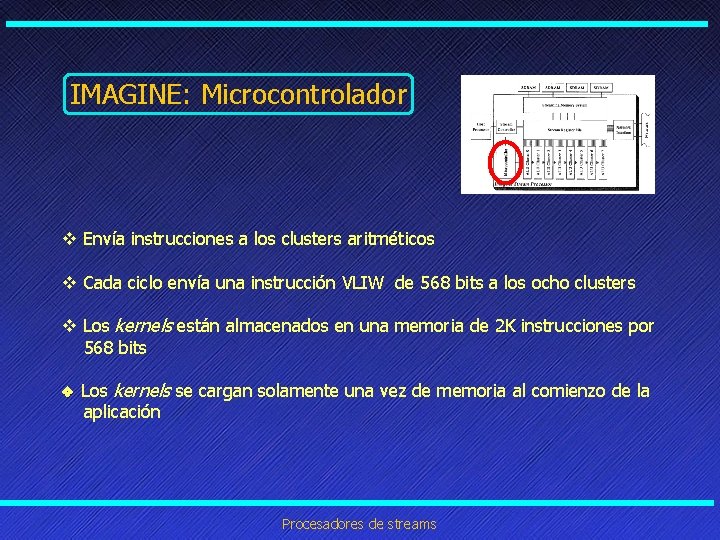

IMAGINE: Microcontrolador v Envía instrucciones a los clusters aritméticos v Cada ciclo envía una instrucción VLIW de 568 bits a los ocho clusters v Los kernels están almacenados en una memoria de 2 K instrucciones por 568 bits v Los kernels se cargan solamente una vez de memoria al comienzo de la aplicación Procesadores de streams

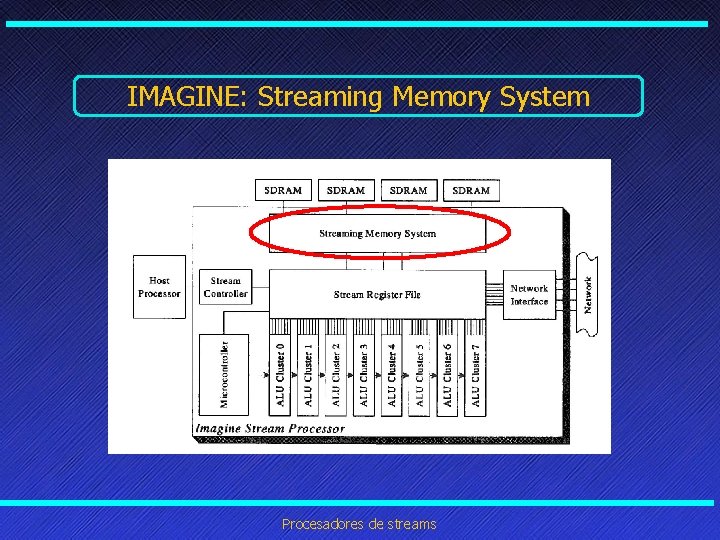

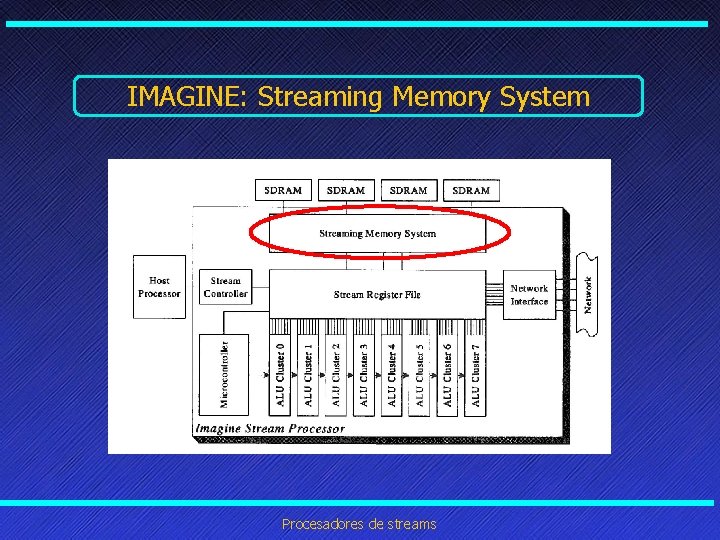

IMAGINE: Streaming Memory System Procesadores de streams

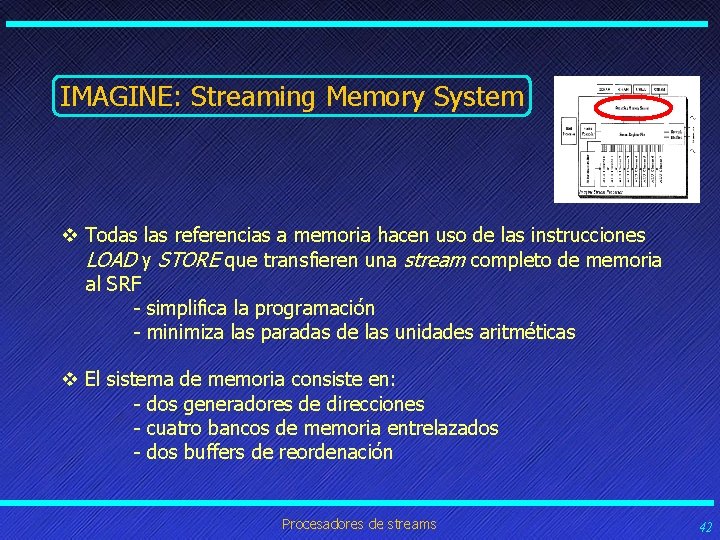

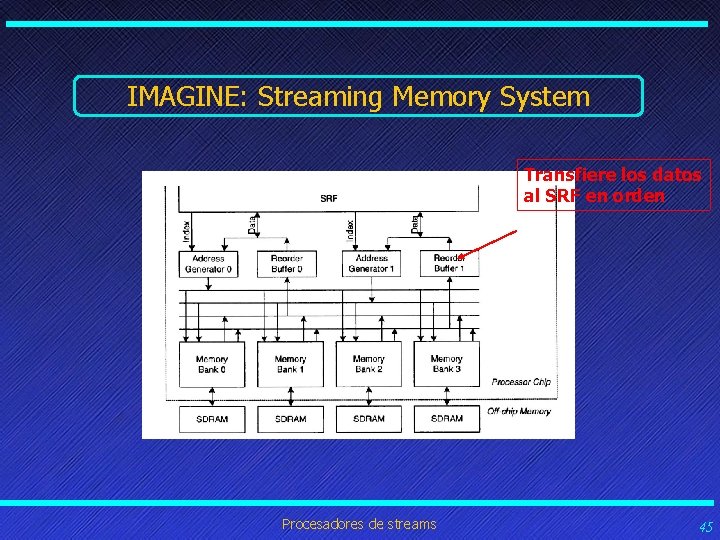

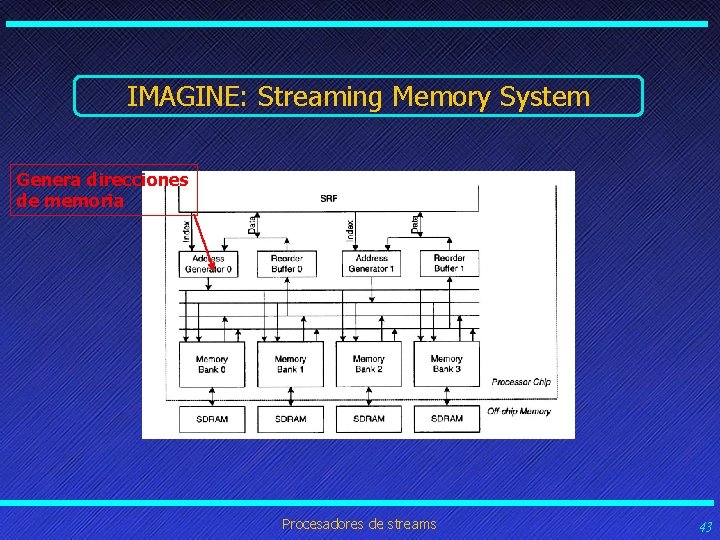

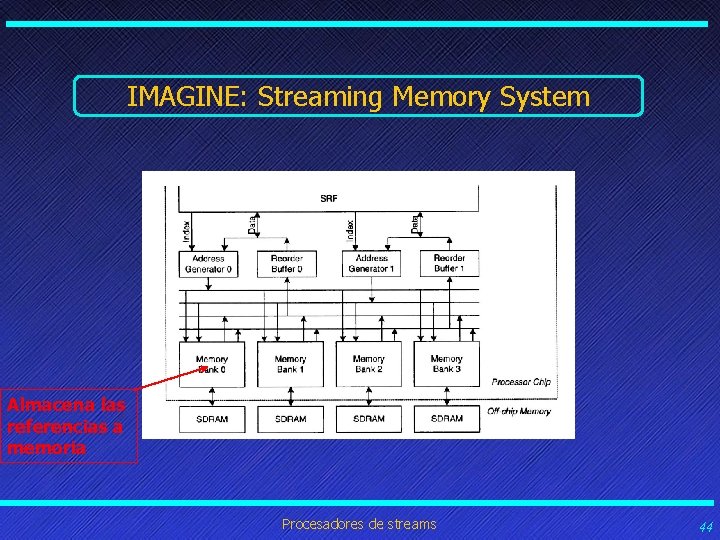

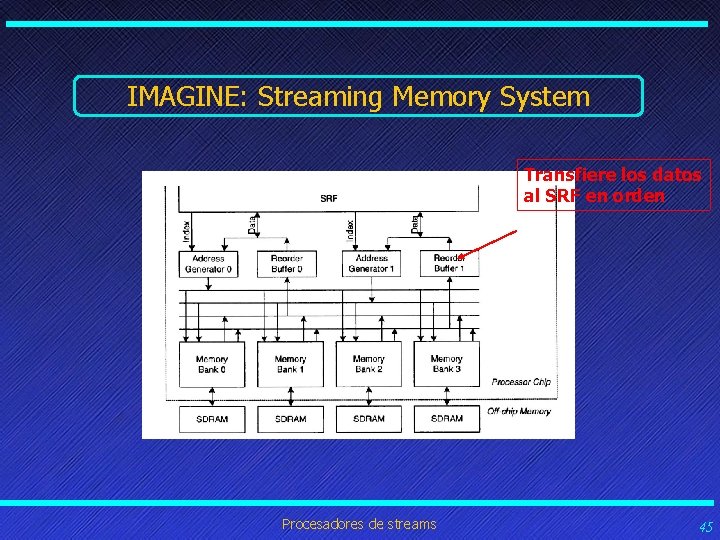

IMAGINE: Streaming Memory System v Todas las referencias a memoria hacen uso de las instrucciones LOAD y STORE que transfieren una stream completo de memoria al SRF - simplifica la programación - minimiza las paradas de las unidades aritméticas v El sistema de memoria consiste en: - dos generadores de direcciones - cuatro bancos de memoria entrelazados - dos buffers de reordenación Procesadores de streams 42

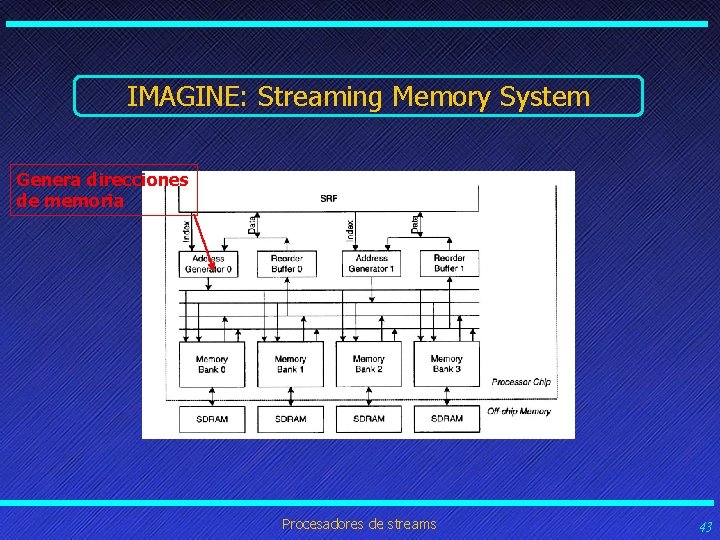

IMAGINE: Streaming Memory System Genera direcciones de memoria Procesadores de streams 43

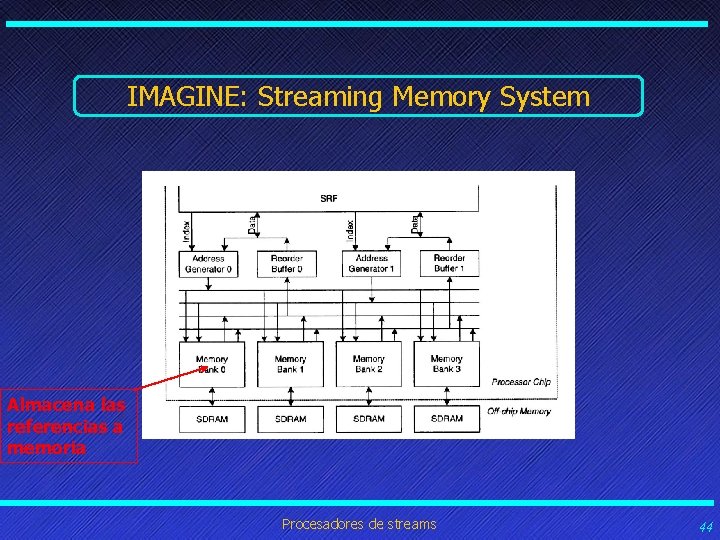

IMAGINE: Streaming Memory System Almacena las referencias a memoria Procesadores de streams 44

IMAGINE: Streaming Memory System Transfiere los datos al SRF en orden Procesadores de streams 45

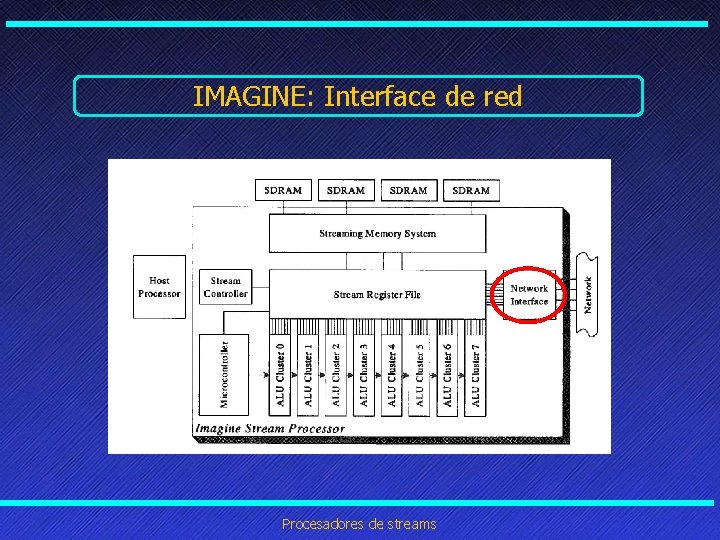

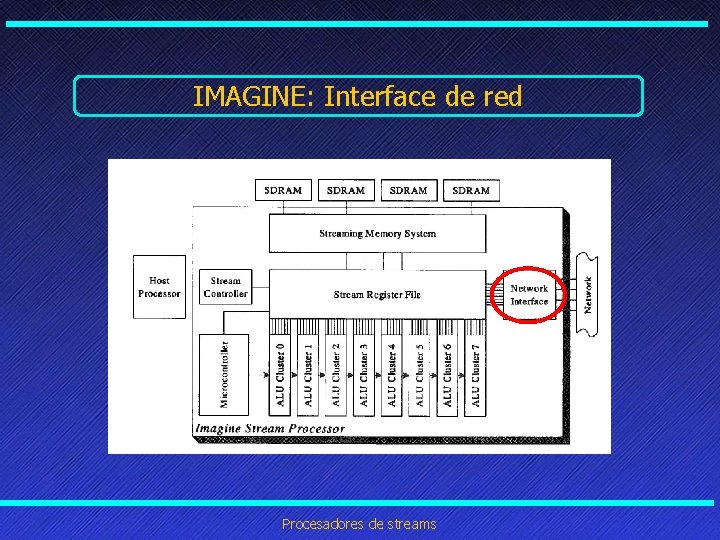

IMAGINE: Interface de red Procesadores de streams

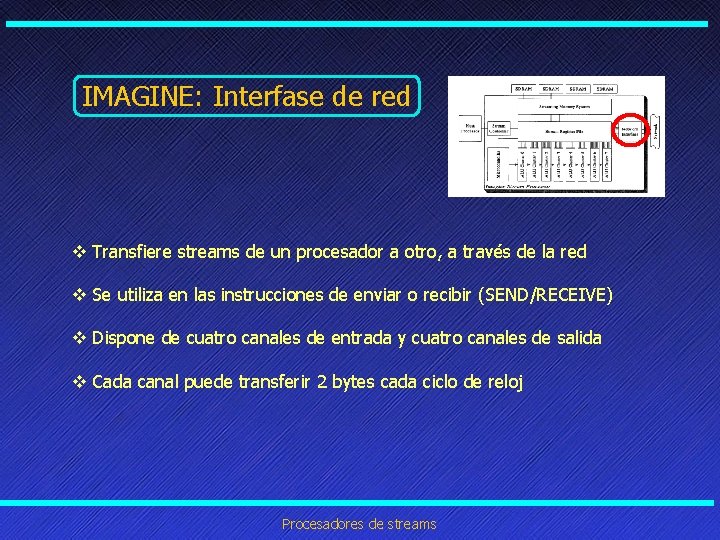

IMAGINE: Interfase de red v Transfiere streams de un procesador a otro, a través de la red v Se utiliza en las instrucciones de enviar o recibir (SEND/RECEIVE) v Dispone de cuatro canales de entrada y cuatro canales de salida v Cada canal puede transferir 2 bytes cada ciclo de reloj Procesadores de streams

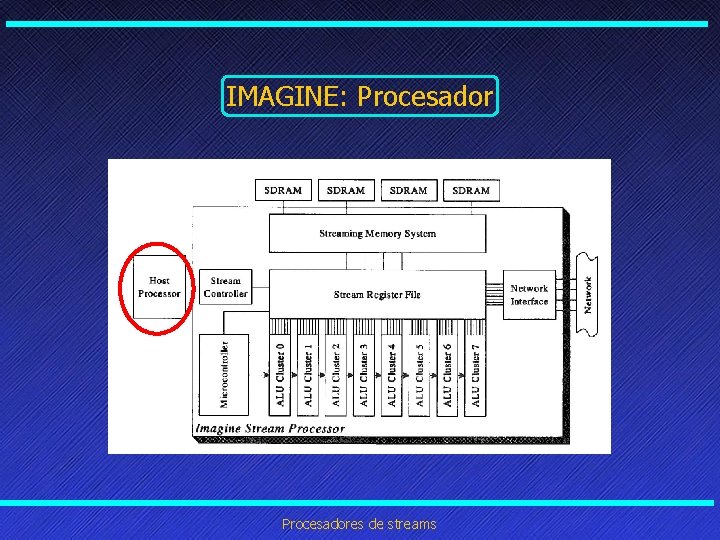

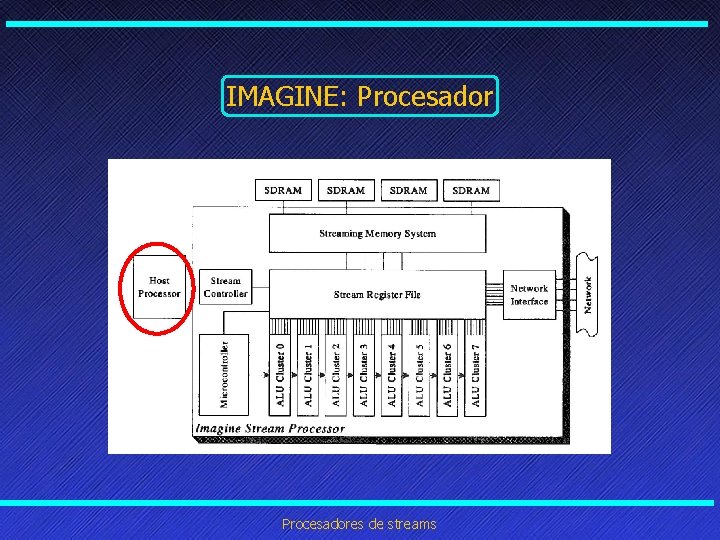

IMAGINE: Procesadores de streams

IMAGINE: Procesador v Un procesador externo ejecuta el programa y transfiere las instrucciones que operan con streams al IMAGINE a través del controlador interno de streams. Procesadores de streams

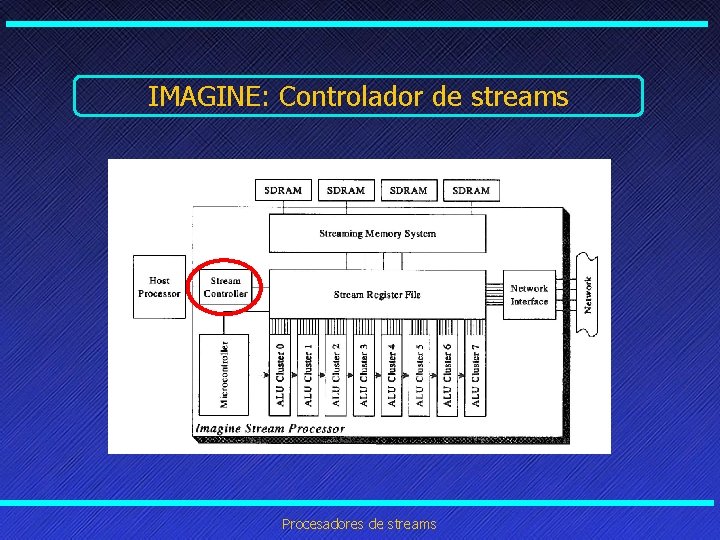

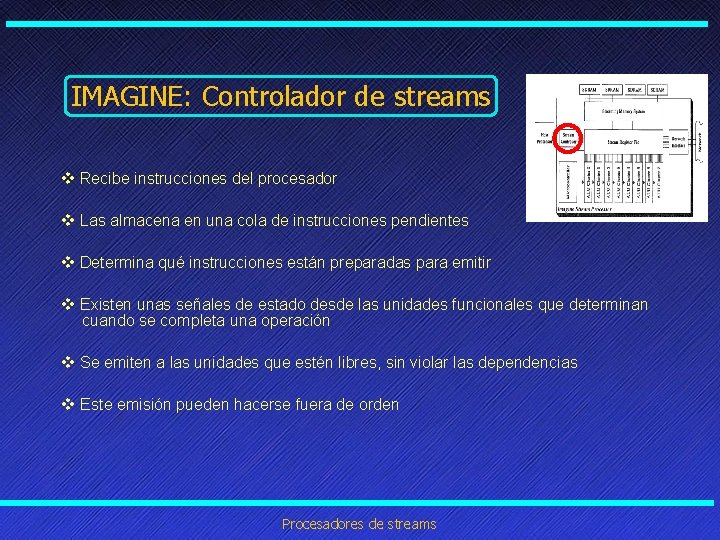

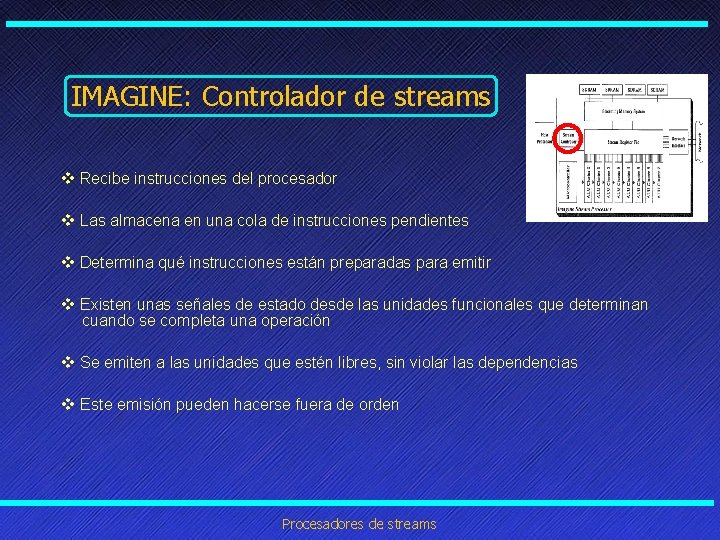

IMAGINE: Controlador de streams Procesadores de streams

IMAGINE: Controlador de streams v Recibe instrucciones del procesador v Las almacena en una cola de instrucciones pendientes v Determina qué instrucciones están preparadas para emitir v Existen unas señales de estado desde las unidades funcionales que determinan cuando se completa una operación v Se emiten a las unidades que estén libres, sin violar las dependencias v Este emisión pueden hacerse fuera de orden Procesadores de streams

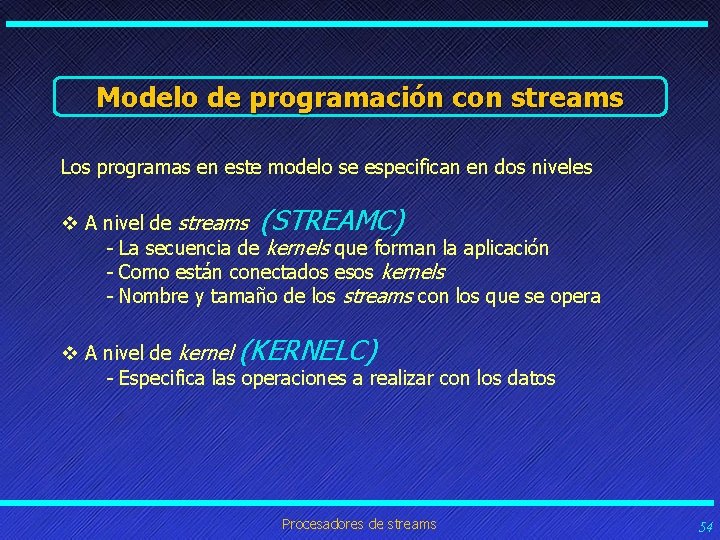

Modelo de programación con streams Los programas en este modelo se especifican en dos niveles v A nivel de streams - La secuencia de kernels que forman la aplicación - Como están conectados esos kernels - Nombre y tamaño de los streams con los que se opera v A nivel de kernel - Especifica las operaciones a realizar con los datos Procesadores de streams 52

Modelo de programación con streams Los programas en este modelo se especifican en dos niveles v A nivel de streams (STREAMC) - La secuencia de kernels que forman la aplicación - Como están conectados esos kernels - Nombre y tamaño de los streams con los que se opera v A nivel de kernel - Especifica las operaciones a realizar con los datos Procesadores de streams 53

Modelo de programación con streams Los programas en este modelo se especifican en dos niveles v A nivel de streams (STREAMC) - La secuencia de kernels que forman la aplicación - Como están conectados esos kernels - Nombre y tamaño de los streams con los que se opera v A nivel de kernel (KERNELC) - Especifica las operaciones a realizar con los datos Procesadores de streams 54

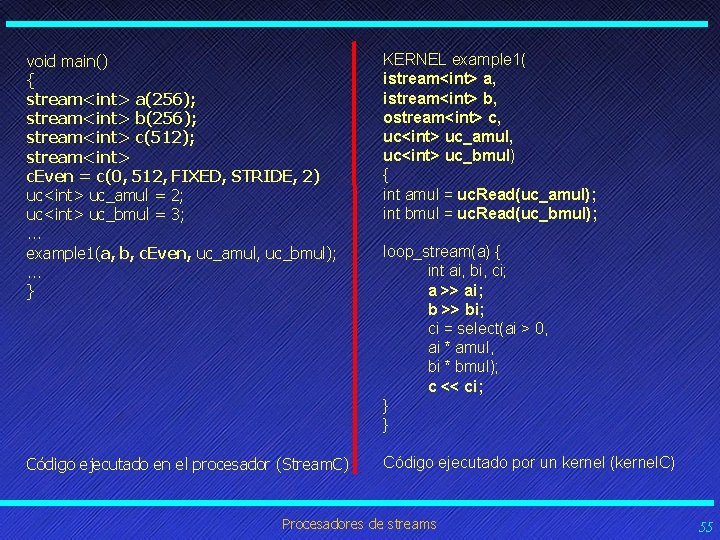

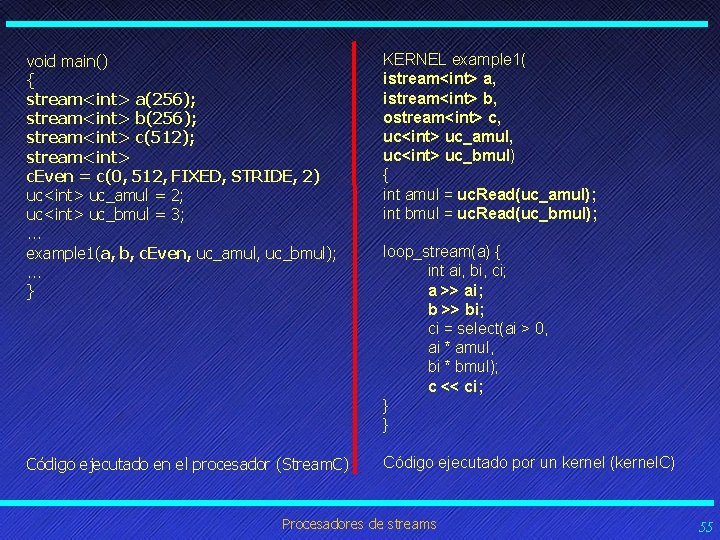

void main() { stream<int> a(256); stream<int> b(256); stream<int> c(512); stream<int> c. Even = c(0, 512, FIXED, STRIDE, 2) uc<int> uc_amul = 2; uc<int> uc_bmul = 3; . . . example 1(a, b, c. Even, uc_amul, uc_bmul); . . . } KERNEL example 1( istream<int> a, istream<int> b, ostream<int> c, uc<int> uc_amul, uc<int> uc_bmul) { int amul = uc. Read(uc_amul); int bmul = uc. Read(uc_bmul); Código ejecutado en el procesador (Stream. C) Código ejecutado por un kernel (kernel. C) loop_stream(a) { int ai, bi, ci; a >> ai; b >> bi; ci = select(ai > 0, ai * amul, bi * bmul); c << ci; } } Procesadores de streams 55

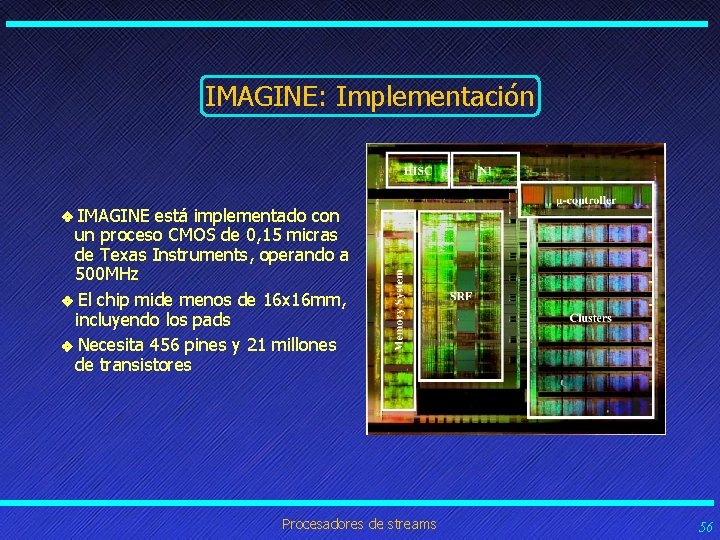

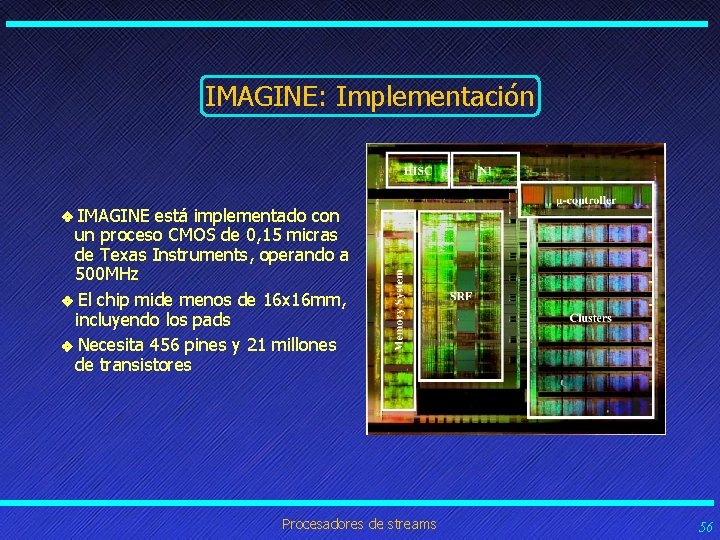

IMAGINE: Implementación v IMAGINE está implementado con un proceso CMOS de 0, 15 micras de Texas Instruments, operando a 500 MHz v El chip mide menos de 16 x 16 mm, incluyendo los pads v Necesita 456 pines y 21 millones de transistores Procesadores de streams 56

Merrimac Bill Dally Universidad de Stanford Procesadores de streams

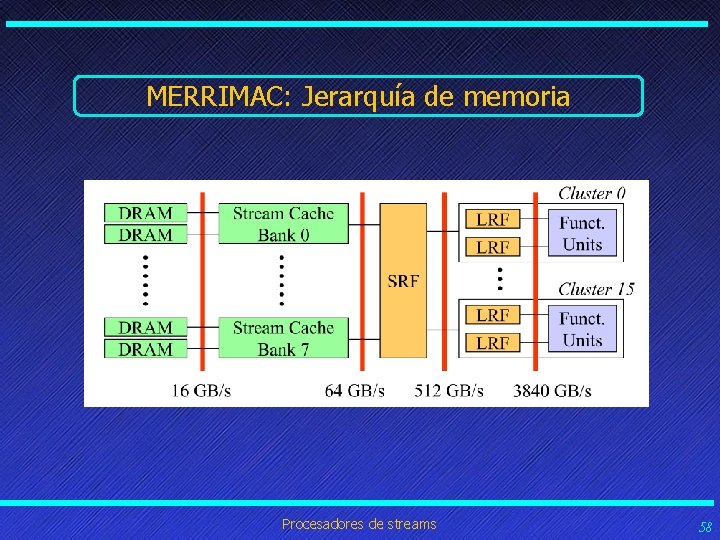

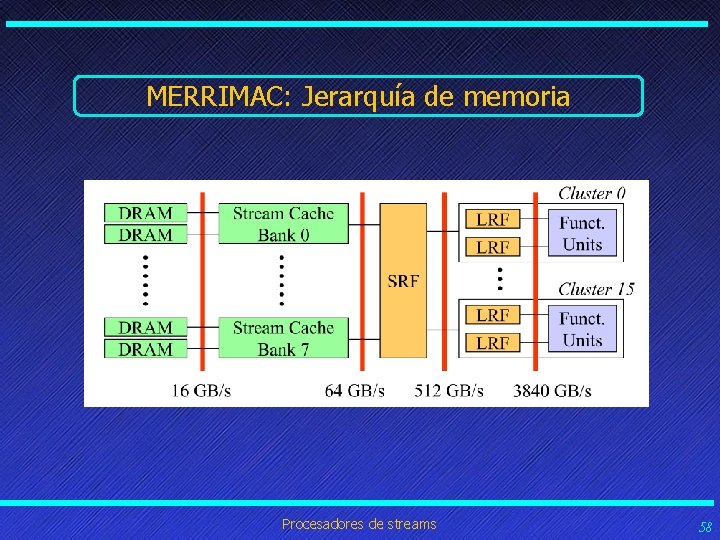

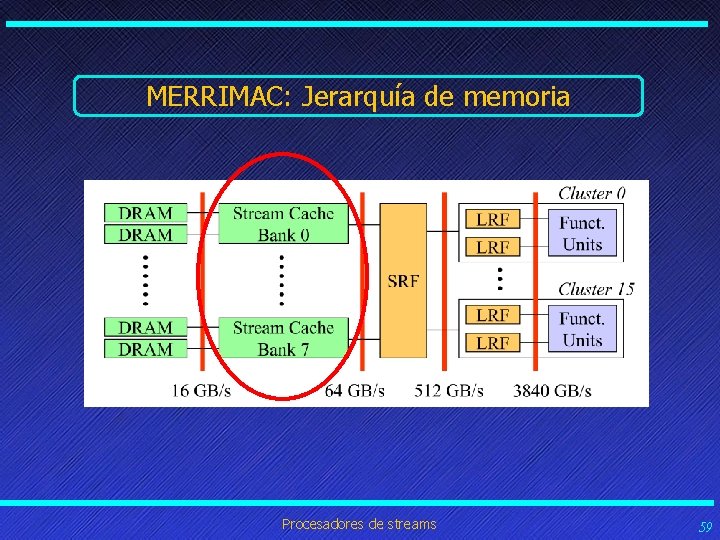

MERRIMAC: Jerarquía de memoria Procesadores de streams 58

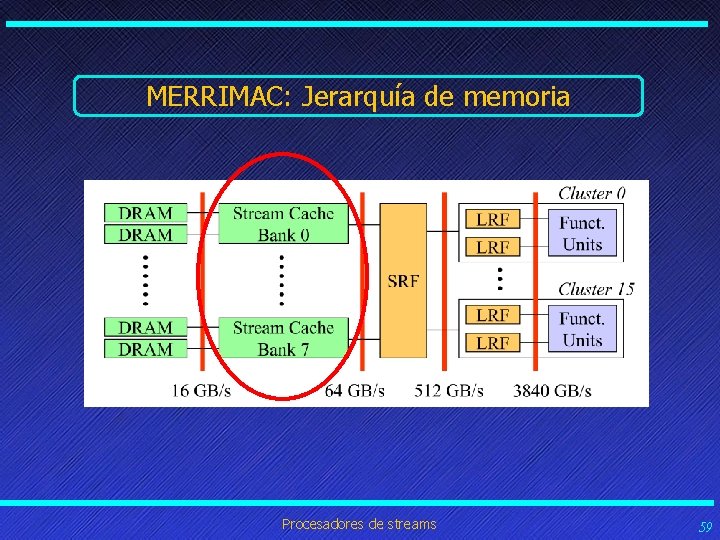

MERRIMAC: Jerarquía de memoria Procesadores de streams 59

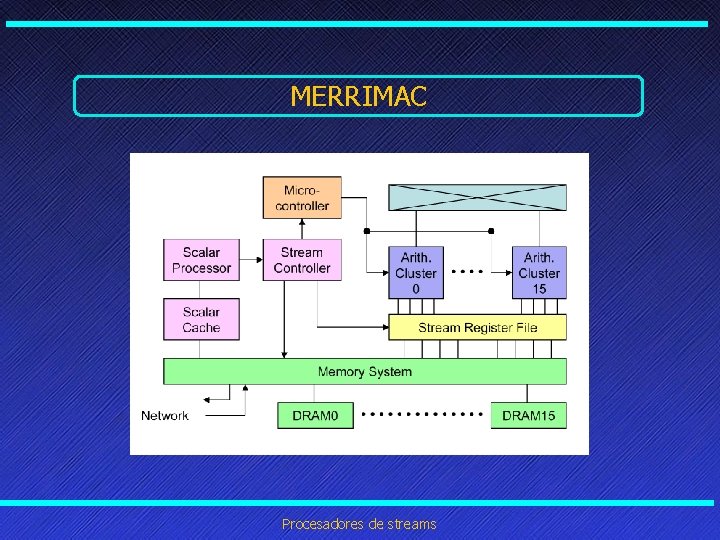

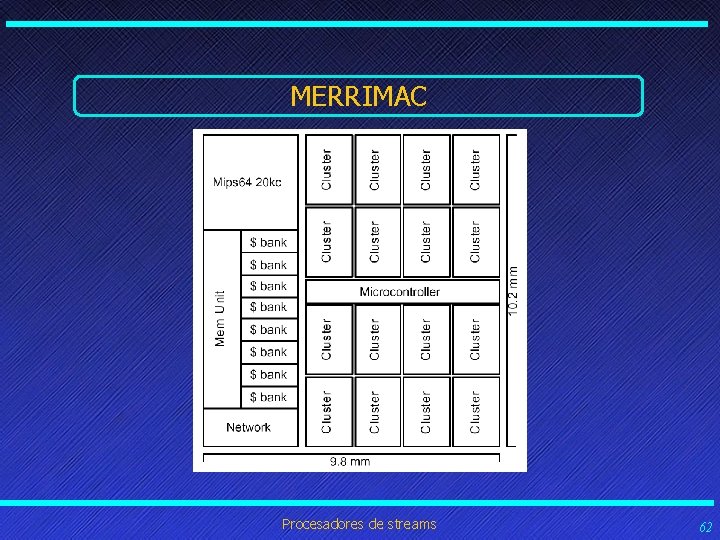

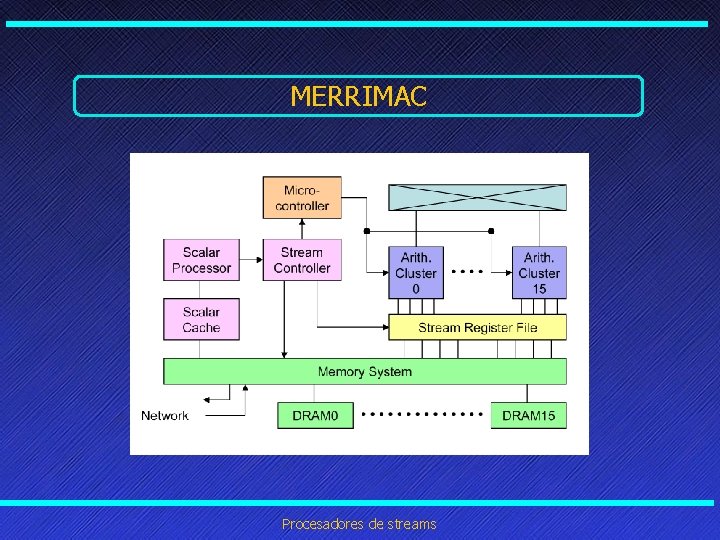

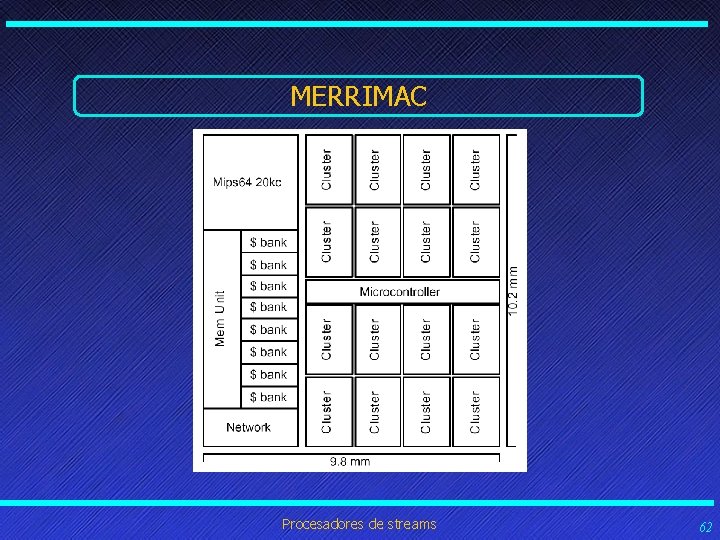

MERRIMAC Procesadores de streams

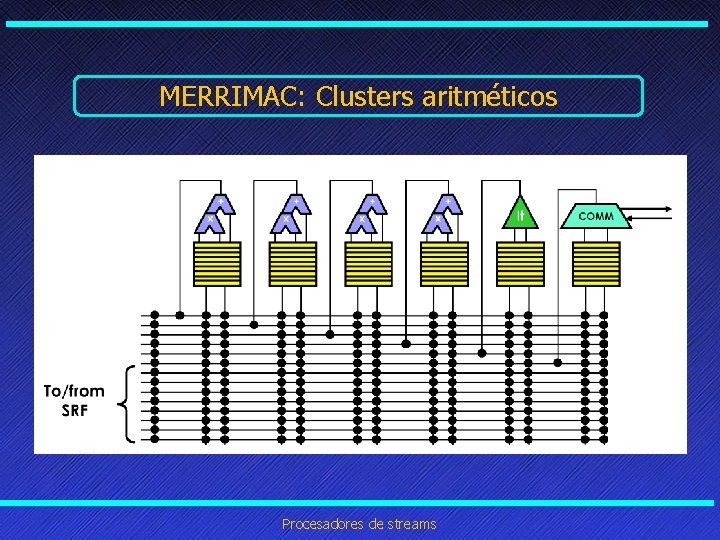

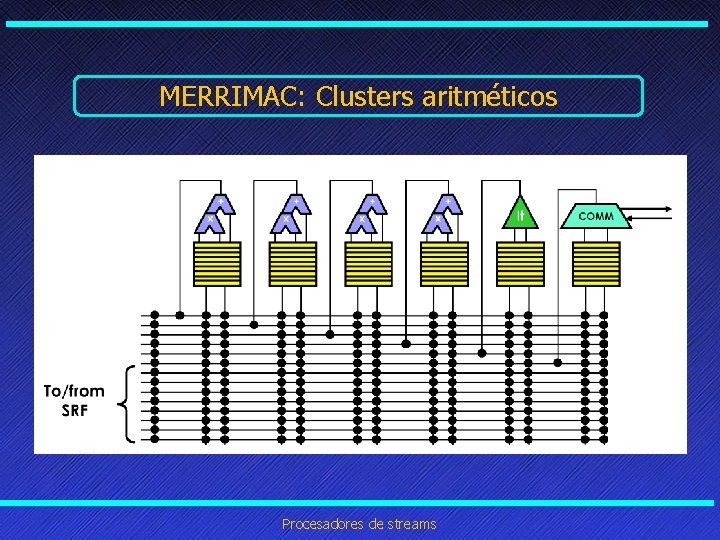

MERRIMAC: Clusters aritméticos Procesadores de streams

MERRIMAC Procesadores de streams 62

Diseño de microprocesadores para multimedia Procesadores de streams Pedro Hernández Fernández Antonio Núñez 8 agosto 2004 Procesadores de streams