DirectMapped Caches Simplest Design Each memory line has

- Slides: 16

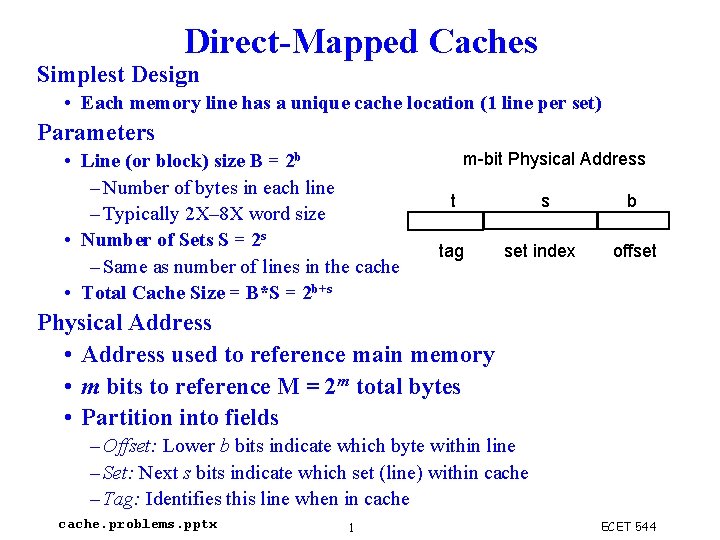

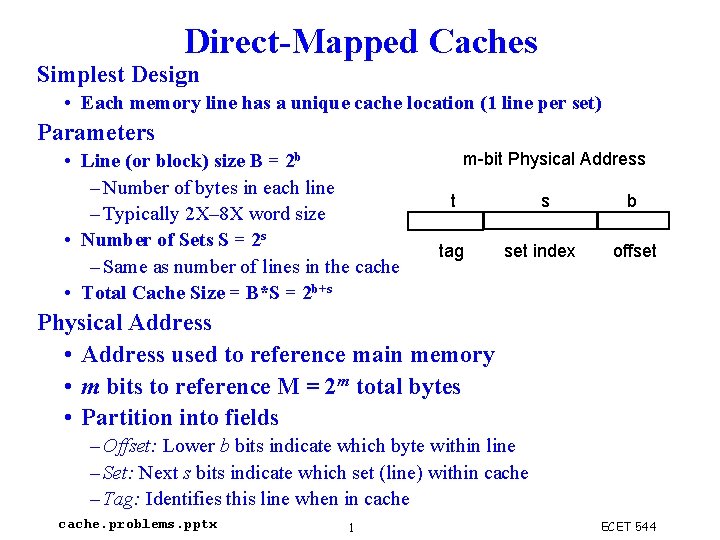

Direct-Mapped Caches Simplest Design • Each memory line has a unique cache location (1 line per set) Parameters • Line (or block) size B = 2 b – Number of bytes in each line – Typically 2 X– 8 X word size • Number of Sets S = 2 s – Same as number of lines in the cache • Total Cache Size = B*S = 2 b+s m-bit Physical Address t tag s set index b offset Physical Address • Address used to reference main memory • m bits to reference M = 2 m total bytes • Partition into fields – Offset: Lower b bits indicate which byte within line – Set: Next s bits indicate which set (line) within cache – Tag: Identifies this line when in cache. problems. pptx 1 ECET 544

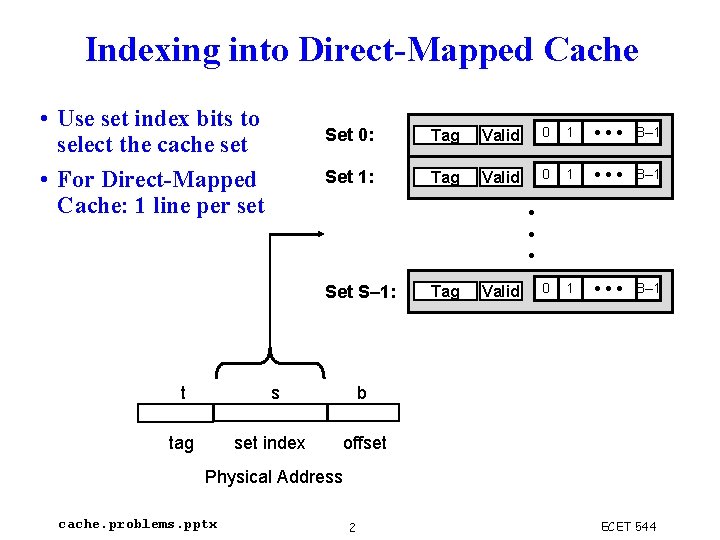

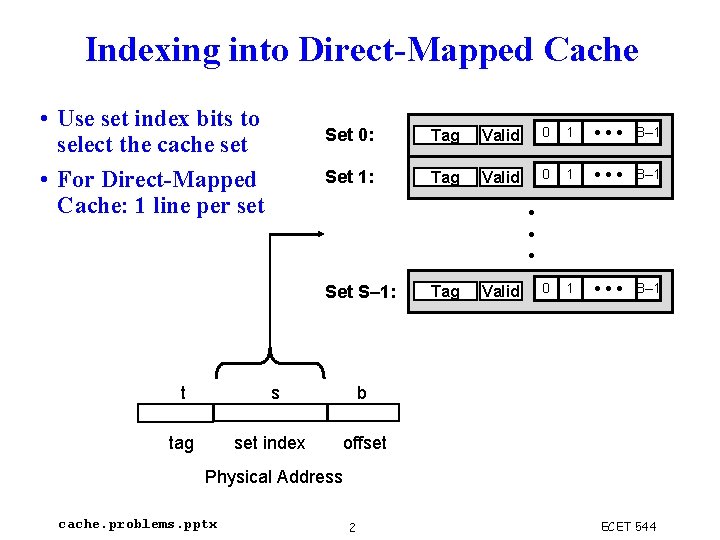

Indexing into Direct-Mapped Cache • Use set index bits to select the cache set • For Direct-Mapped Cache: 1 line per set Set 0: Tag Valid 0 1 • • • B– 1 Set 1: Tag Valid 0 1 • • • B– 1 • • • Set S– 1: t s tag set index Tag Valid b offset Physical Address cache. problems. pptx 2 ECET 544

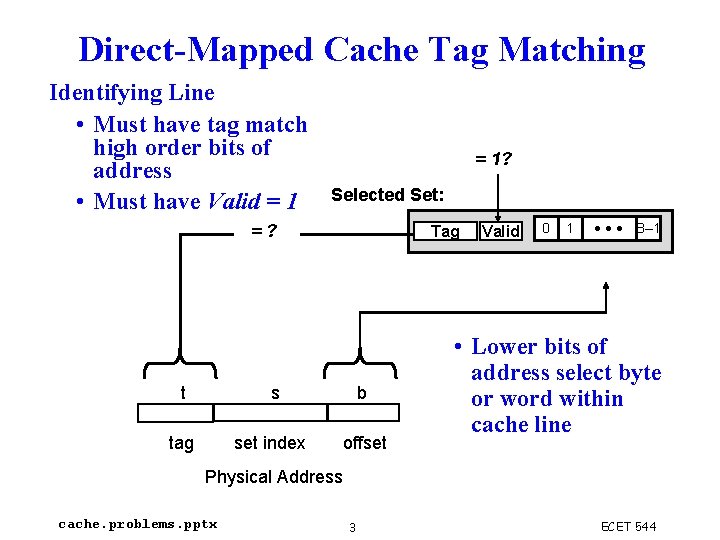

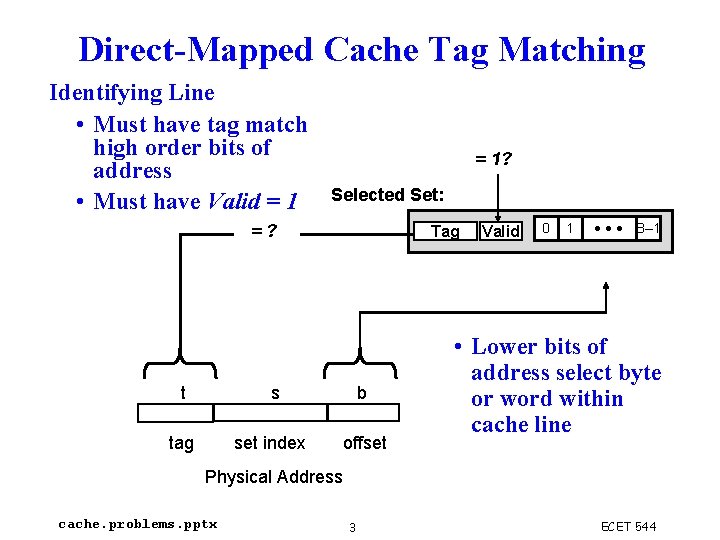

Direct-Mapped Cache Tag Matching Identifying Line • Must have tag match high order bits of address • Must have Valid = 1? Selected Set: =? t Tag s tag set index b offset Valid 0 1 • • • B– 1 • Lower bits of address select byte or word within cache line Physical Address cache. problems. pptx 3 ECET 544

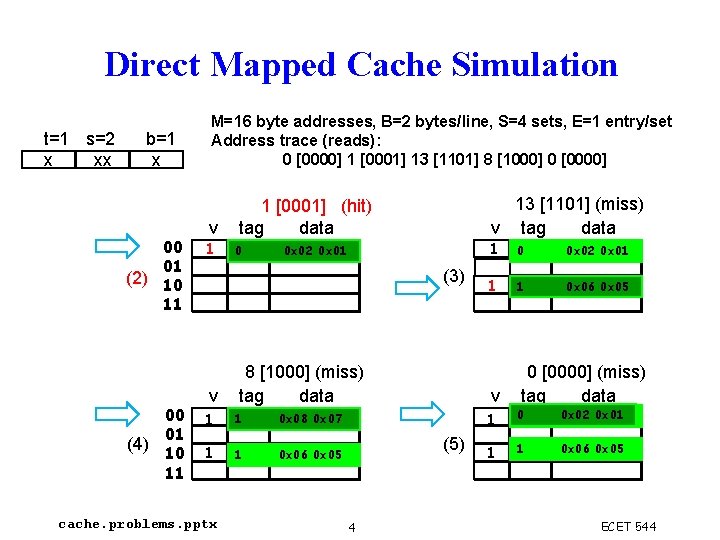

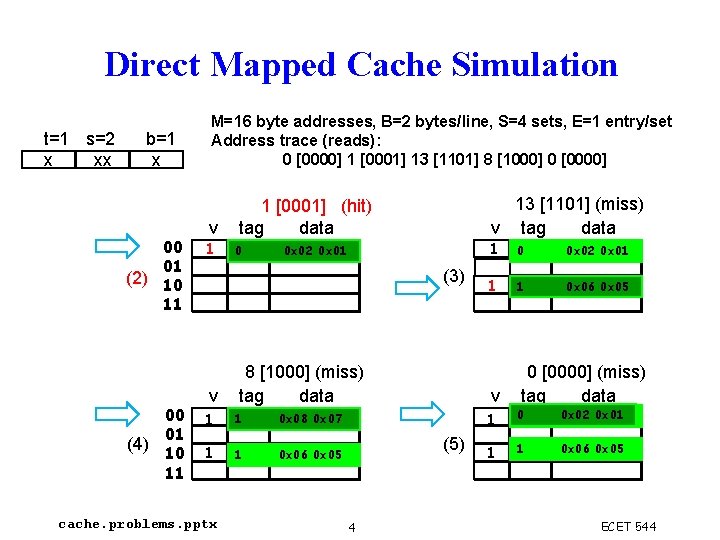

Direct Mapped Cache Simulation t=1 s=2 x xx b=1 x 00 01 (1) 10 (2) 11 00 01 (4) 10 11 M=16 byte addresses, B=2 bytes/line, S=4 sets, E=1 entry/set Address trace (reads): 0 [0000] 1 [0001] 13 [1101] 8 [1000] 0 [0000] v 1 13 [1101] (miss) v tag data 01 [0000] [0001] (miss) (hit) tag data 00 m[1] m[0] 0 x 02 0 x 01 (3) v 8 [1000] (miss) tag data 1 1 1 X 01 m[9] m[8] 0 x 08 0 x 02 0 x 07 0 x 01 1 1 0 x 06 0 x 05 cache. problems. pptx 00 m[1] m[0] 0 x 02 0 x 01 1 11 m[13] m[12] 0 x 06 0 x 05 v (5) 4 11 0 [0000] (miss) tag data 1 1 0 10 X 0 x 02 0 x 08 0 x 01 0 x 07 m[1] m[0] 1 11 0 x 06 0 x 05 m[13] m[12] ECET 544

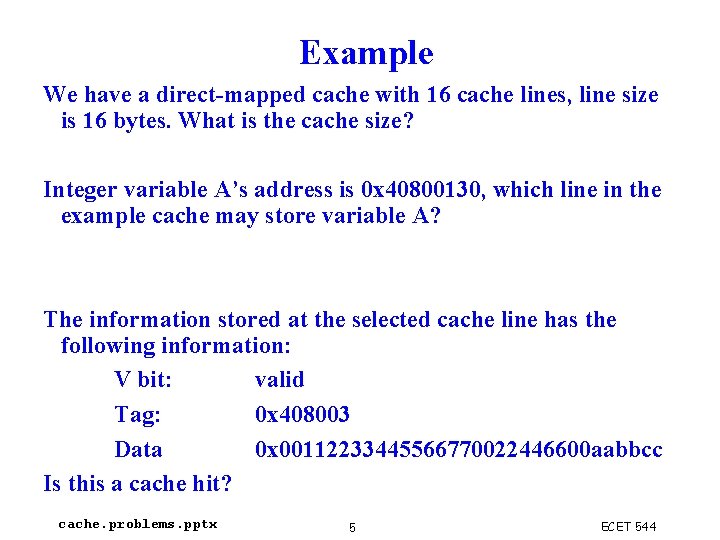

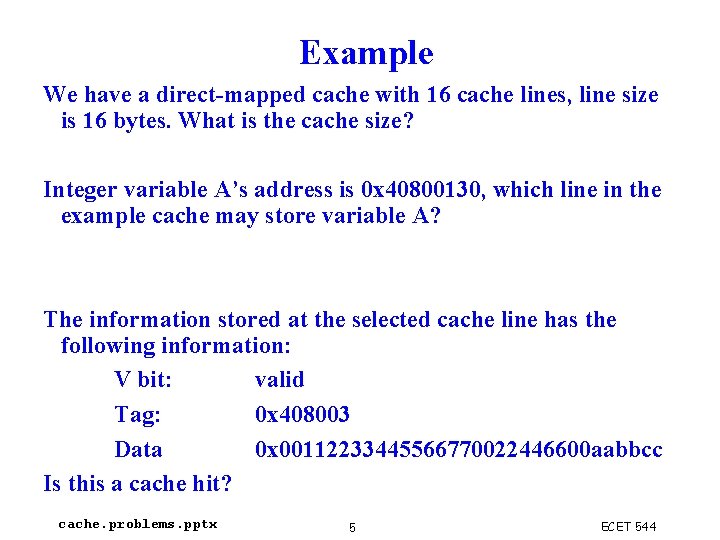

Example We have a direct-mapped cache with 16 cache lines, line size is 16 bytes. What is the cache size? Integer variable A’s address is 0 x 40800130, which line in the example cache may store variable A? The information stored at the selected cache line has the following information: V bit: valid Tag: 0 x 408003 Data 0 x 00112233445566770022446600 aabbcc Is this a cache hit? cache. problems. pptx 5 ECET 544

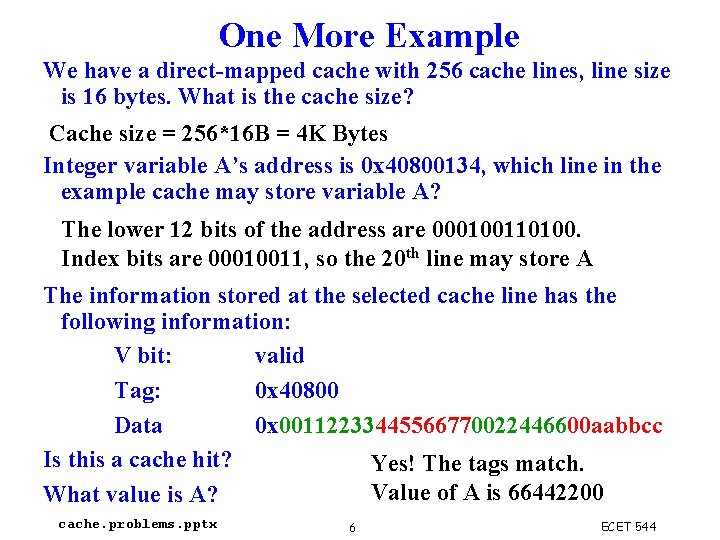

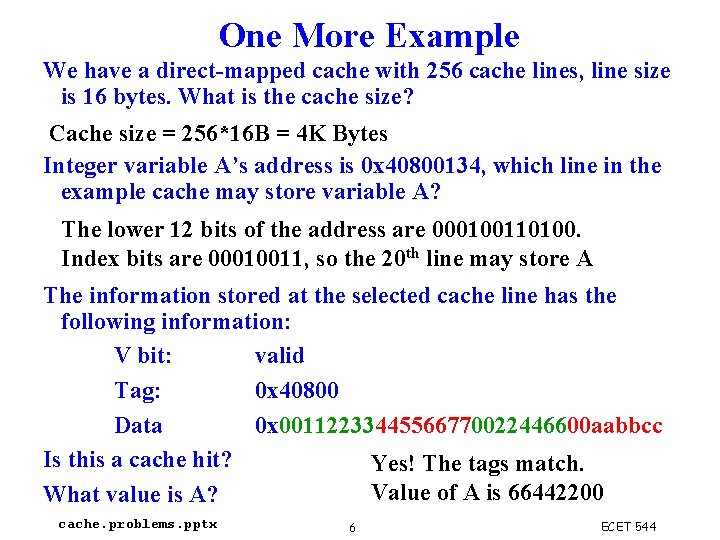

One More Example We have a direct-mapped cache with 256 cache lines, line size is 16 bytes. What is the cache size? Cache size = 256*16 B = 4 K Bytes Integer variable A’s address is 0 x 40800134, which line in the example cache may store variable A? The lower 12 bits of the address are 000100110100. Index bits are 00010011, so the 20 th line may store A The information stored at the selected cache line has the following information: V bit: valid Tag: 0 x 40800 Data 0 x 00112233445566770022446600 aabbcc Is this a cache hit? Yes! The tags match. Value of A is 66442200 What value is A? cache. problems. pptx 6 ECET 544

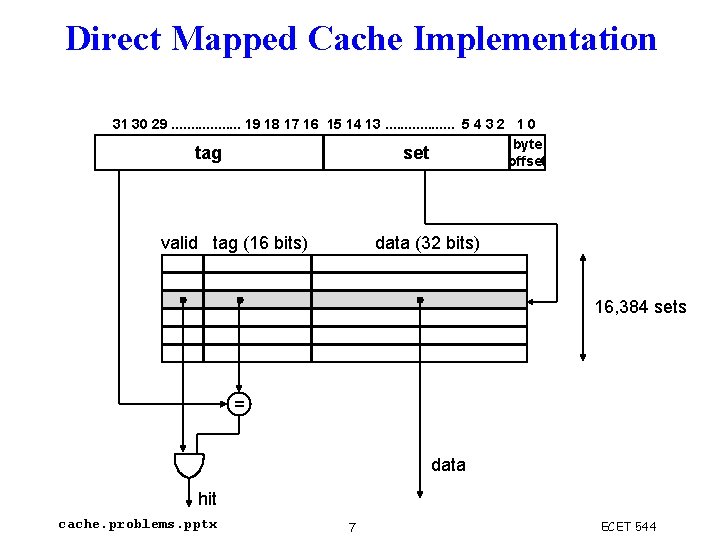

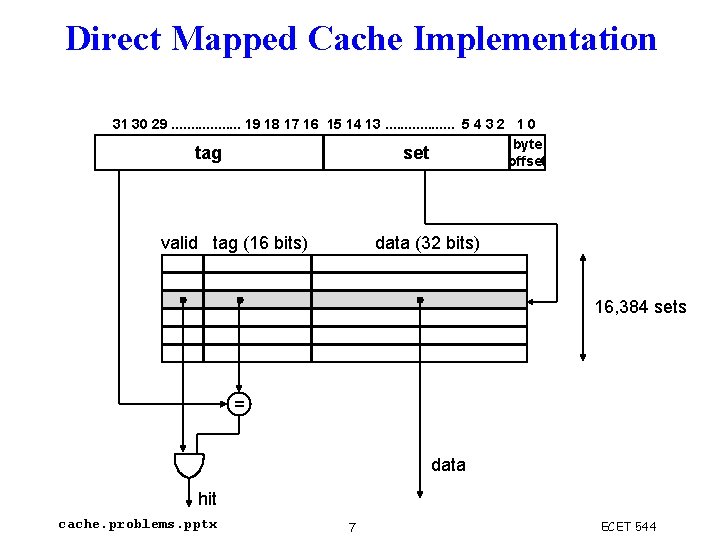

Direct Mapped Cache Implementation 31 30 29. . . . 19 18 17 16 15 14 13. . . . 5 4 3 2 1 0 byte tag set offset valid tag (16 bits) data (32 bits) 16, 384 sets = data hit cache. problems. pptx 7 ECET 544

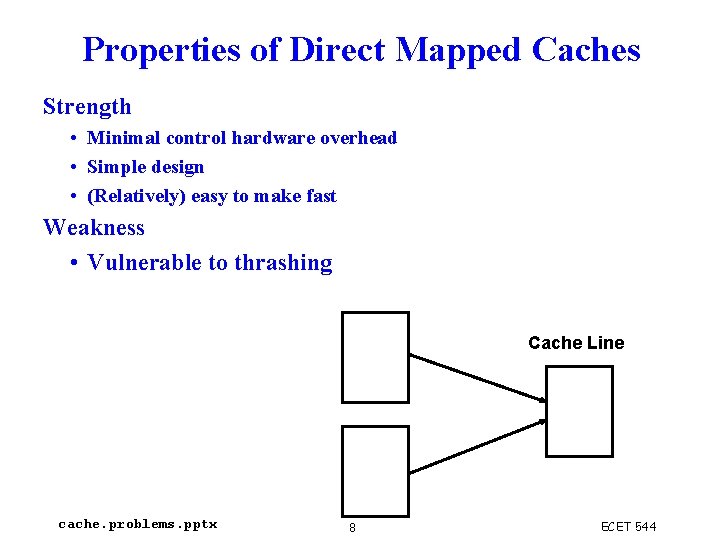

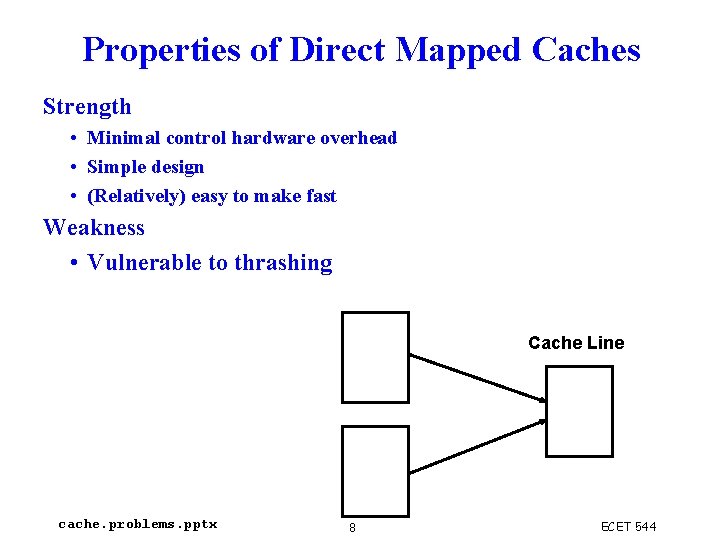

Properties of Direct Mapped Caches Strength • Minimal control hardware overhead • Simple design • (Relatively) easy to make fast Weakness • Vulnerable to thrashing Cache Line cache. problems. pptx 8 ECET 544

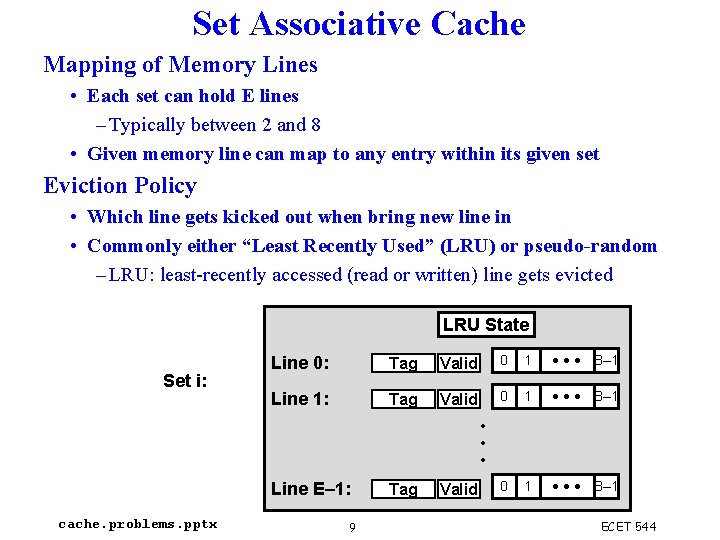

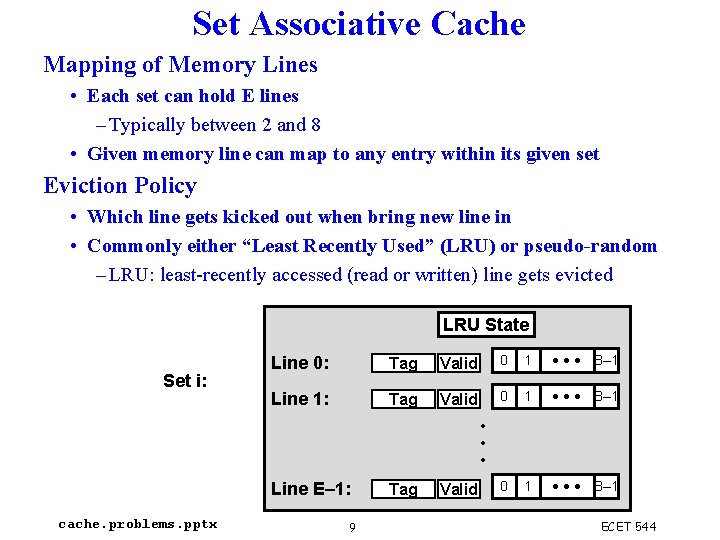

Set Associative Cache Mapping of Memory Lines • Each set can hold E lines – Typically between 2 and 8 • Given memory line can map to any entry within its given set Eviction Policy • Which line gets kicked out when bring new line in • Commonly either “Least Recently Used” (LRU) or pseudo-random – LRU: least-recently accessed (read or written) line gets evicted LRU State Set i: Line 0: Tag Valid 0 1 • • • B– 1 Line 1: Tag Valid 0 1 • • • B– 1 • • • Line E– 1: cache. problems. pptx 9 Tag Valid ECET 544

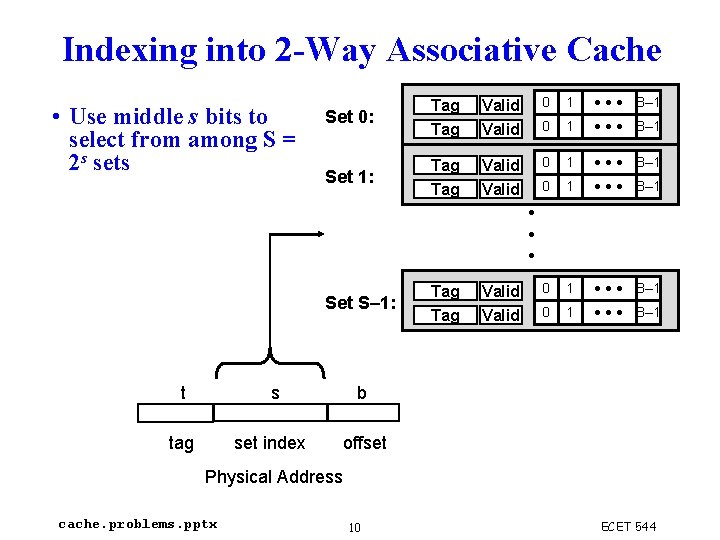

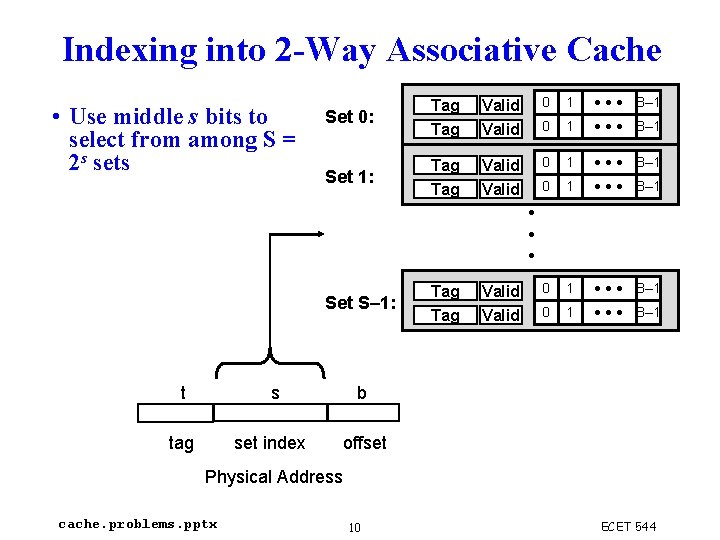

Indexing into 2 -Way Associative Cache • Use middle s bits to select from among S = 2 s sets Set 0: Tag Valid 0 1 Set 1: Tag Valid 0 1 0 1 • • • B– 1 • • • B– 1 • • • Set S– 1: t s tag set index Tag Valid B– 1 b offset Physical Address cache. problems. pptx 10 ECET 544

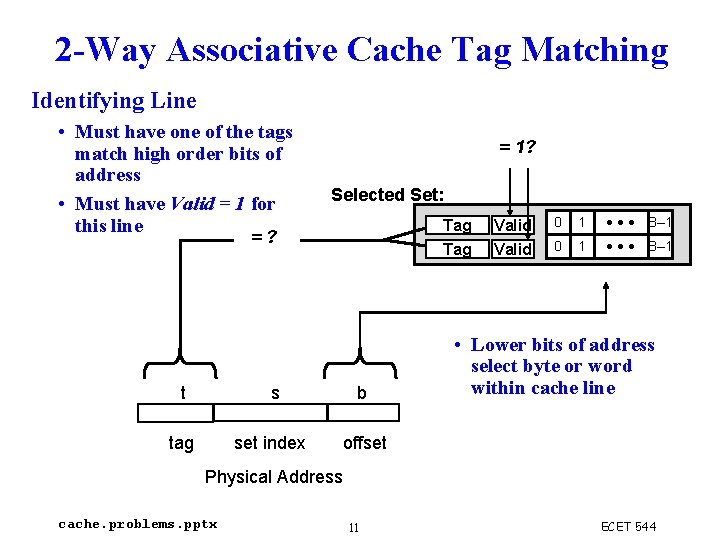

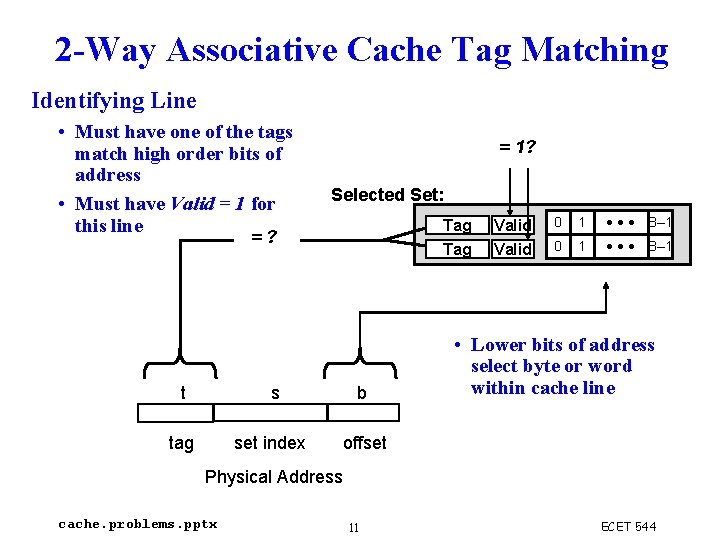

2 -Way Associative Cache Tag Matching Identifying Line • Must have one of the tags match high order bits of address • Must have Valid = 1 for this line = 1? Selected Set: Tag =? t s tag set index b Valid 0 1 • • • B– 1 • Lower bits of address select byte or word within cache line offset Physical Address cache. problems. pptx 11 ECET 544

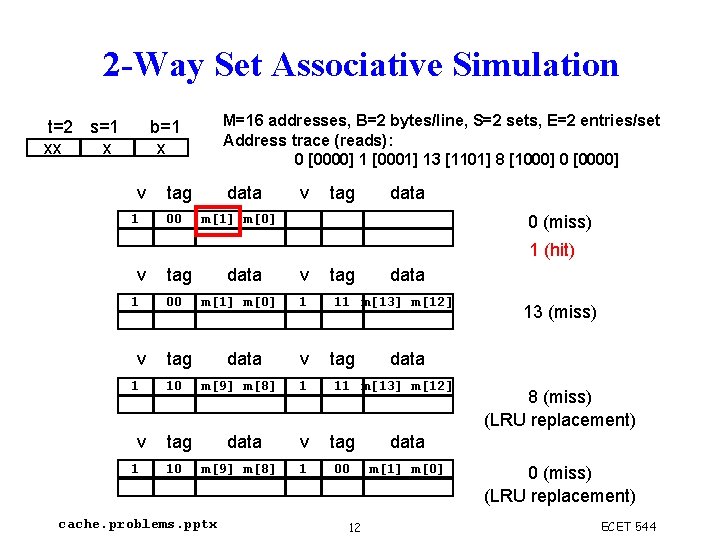

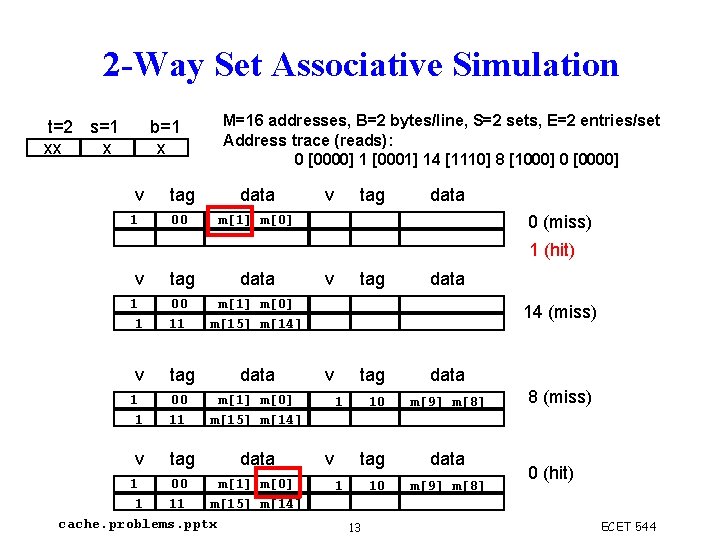

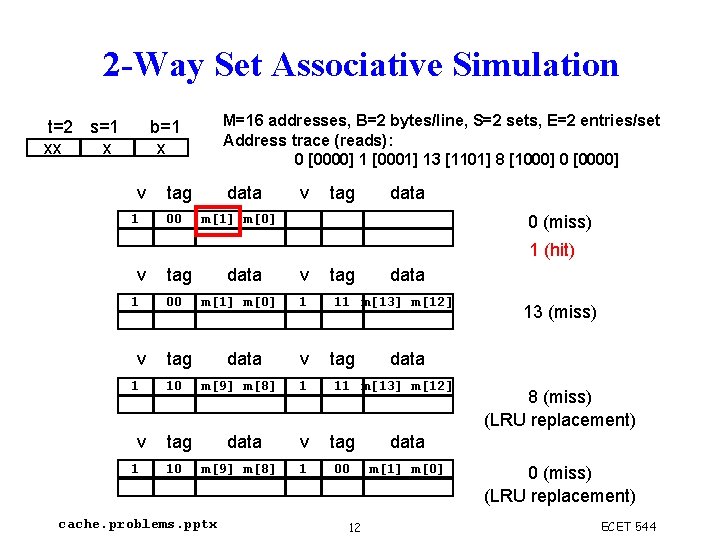

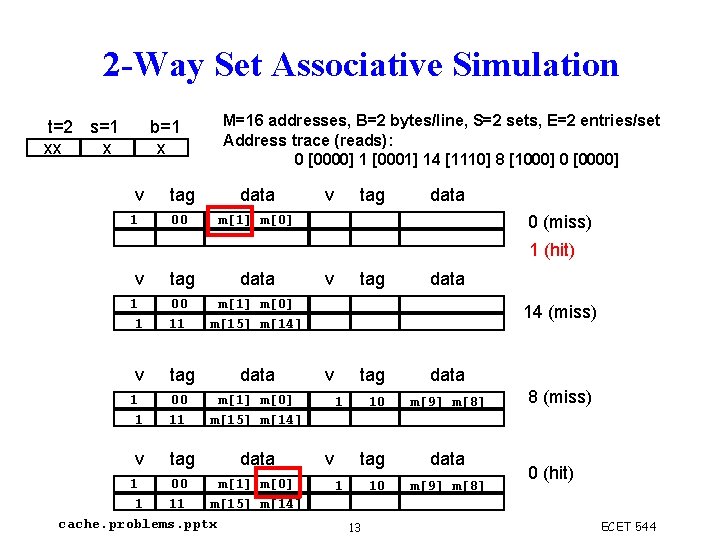

2 -Way Set Associative Simulation t=2 s=1 xx x M=16 addresses, B=2 bytes/line, S=2 sets, E=2 entries/set Address trace (reads): 0 [0000] 1 [0001] 13 [1101] 8 [1000] 0 [0000] b=1 x v 1 tag 00 data v tag data 0 (miss) m[1] m[0] 1 (hit) v 1 v 1 tag 00 data v tag m[1] m[0] 1 11 m[13] m[12] data v tag m[9] m[8] 1 11 m[13] m[12] data v tag data m[9] m[8] 1 00 m[1] m[0] tag 10 cache. problems. pptx 12 data 13 (miss) data 8 (miss) (LRU replacement) 0 (miss) (LRU replacement) ECET 544

2 -Way Set Associative Simulation t=2 s=1 xx x b=1 x v 1 M=16 addresses, B=2 bytes/line, S=2 sets, E=2 entries/set Address trace (reads): 0 [0000] 1 [0001] 14 [1110] 8 [1000] 0 [0000] tag data 00 m[1] m[0] v tag data 0 (miss) 1 (hit) v tag data 1 1 00 11 m[1] m[0] m[15] m[14] v tag data 1 00 m[1] m[0] 1 11 m[15] m[14] cache. problems. pptx v tag data 14 (miss) v tag 1 v 10 tag 1 10 13 data m[9] m[8] 8 (miss) 0 (hit) ECET 544

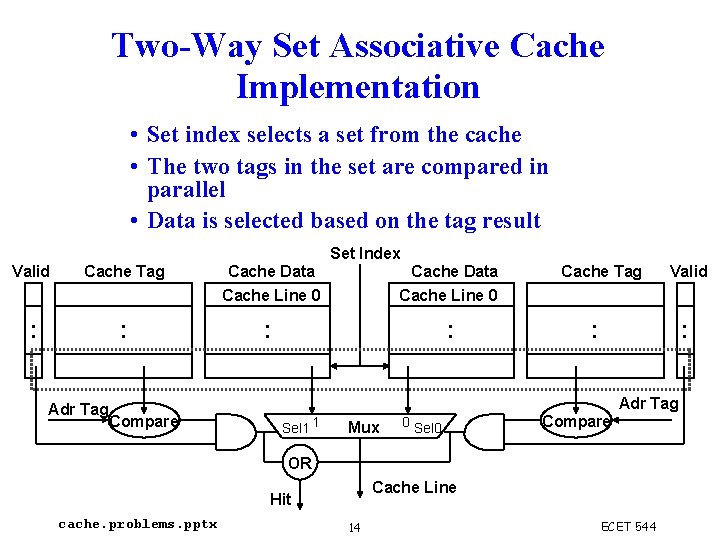

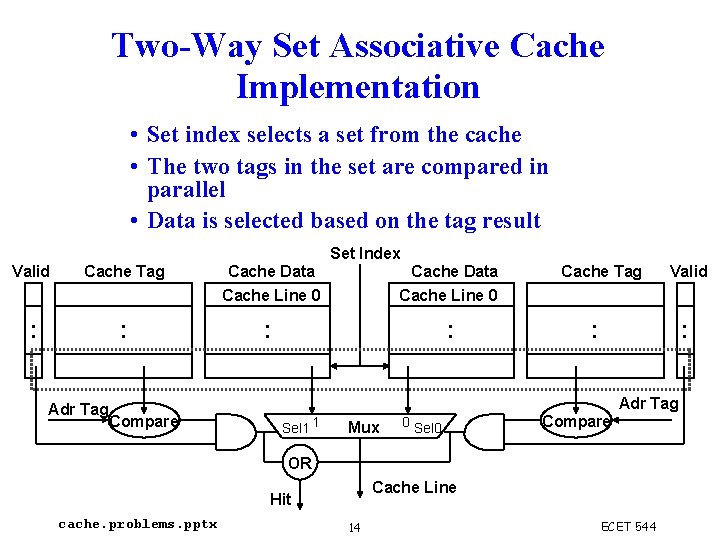

Two-Way Set Associative Cache Implementation • Set index selects a set from the cache • The two tags in the set are compared in parallel • Data is selected based on the tag result Set Index Valid Cache Tag : : Adr Tag Cache Data Cache Line 0 : : Cache Tag Valid : : Adr Tag Compare Sel 1 1 Mux 0 Sel 0 Compare OR Cache Line Hit cache. problems. pptx 14 ECET 544

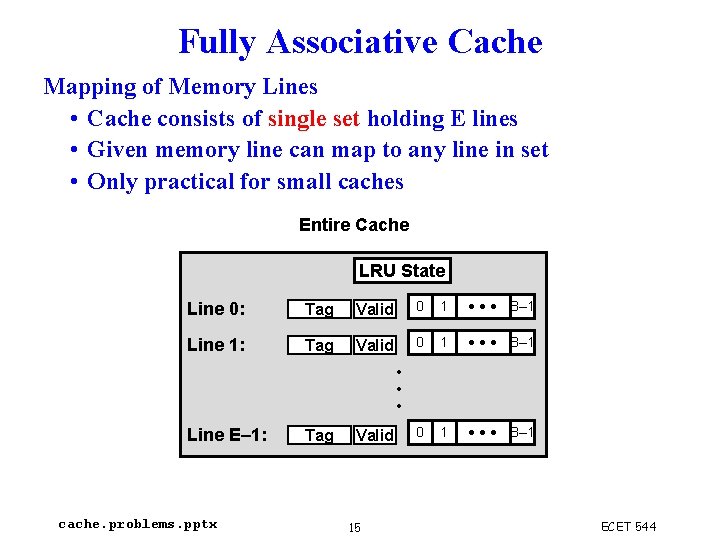

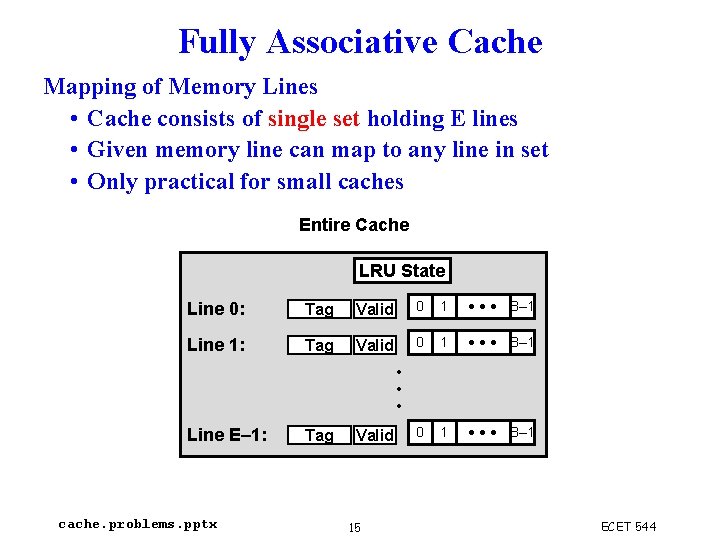

Fully Associative Cache Mapping of Memory Lines • Cache consists of single set holding E lines • Given memory line can map to any line in set • Only practical for small caches Entire Cache LRU State Line 0: Tag Valid 0 1 • • • B– 1 Line 1: Tag Valid 0 1 • • • B– 1 • • • Line E– 1: cache. problems. pptx Tag Valid 15 ECET 544

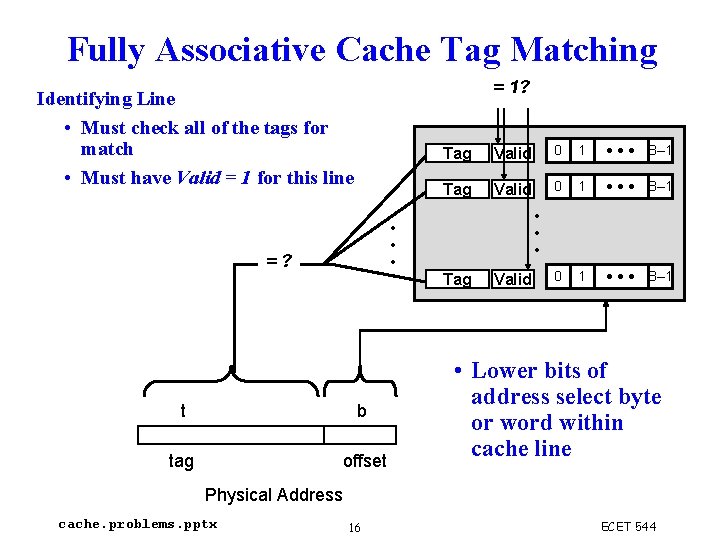

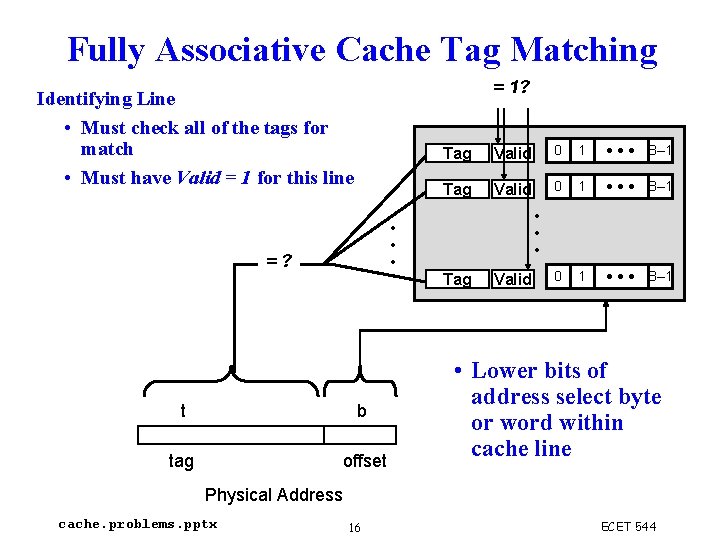

Fully Associative Cache Tag Matching = 1? Identifying Line • Must check all of the tags for match • Must have Valid = 1 for this line Tag Valid 0 1 • • • B– 1 • • • =? Tag t b tag offset Valid • Lower bits of address select byte or word within cache line Physical Address cache. problems. pptx 16 ECET 544