Direct Memory Access Presentation by Leena Jacob To

Direct Memory Access Presentation by Leena Jacob

To be tackled l l The basic computer Improvements made to the basic computer l l Interrupt handler DMA Controller in BF 533 Example code that demonstrates setting up the DMA

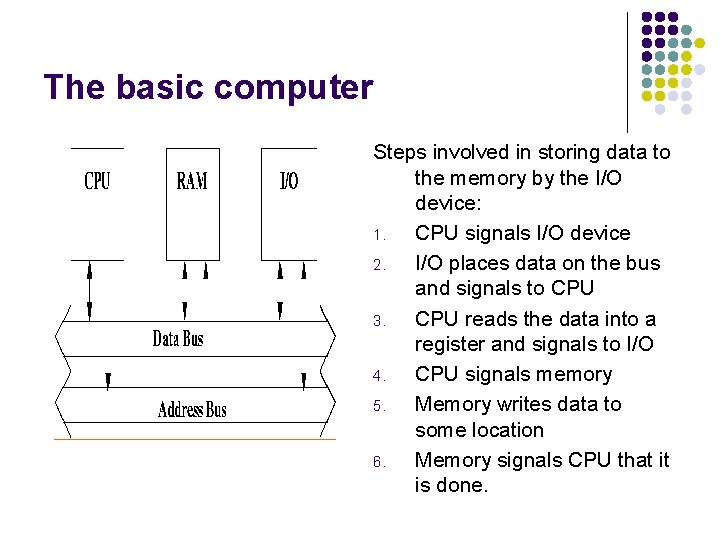

The basic computer Steps involved in storing data to the memory by the I/O device: 1. CPU signals I/O device 2. I/O places data on the bus and signals to CPU 3. CPU reads the data into a register and signals to I/O 4. CPU signals memory 5. Memory writes data to some location 6. Memory signals CPU that it is done.

Deficiencies of CPU I/O l No other useful CPU operations can be accomplished while waiting for I/O l Early I/O devices were very slow, thus compounding the problem 4

Interrupt Improvements l l l The better option is for the I/O device to interrupt the processor with an interrupt signal whenever it is ready with a data. CPU can then service the interrupt and get back to whatever it was doing before. This requires an interrupt handler. 5

Direct Memory Channel Improvement l l l Interrupt processing requires explicit op-code cycles to perform I/O transfers Next improvement is a separate peripheral module to perform direct memory access (DMA). It is also the bus arbitrator. There can only be one user of the data bus so processor must wait if DMA is transferring data. DMA controller tells the processor when the DMA has completed the transfer. 6

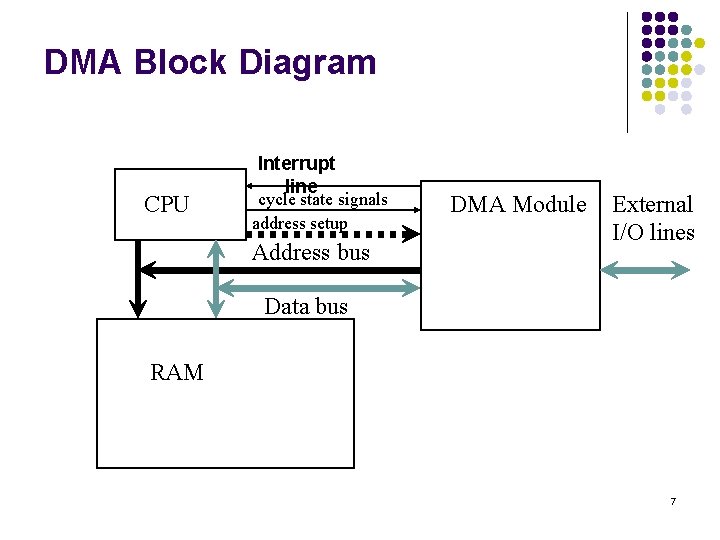

DMA Block Diagram CPU Interrupt line cycle state signals address setup Address bus DMA Module External I/O lines Data bus RAM 7

Sharing of the op-code cycles l Op-code cycles have two distinct parts: 1. One part involves RAM access Read the OP code from program memory (fetch) l Read/write data from/to data RAM addresses (decode and writeback) Second part involves only CPU operations (execute) l Perform data manipulation using CPU registers as source(s) and destination(s) of data l 2. l DMA device performs RAM access during this second portion of the op-code cycle 8

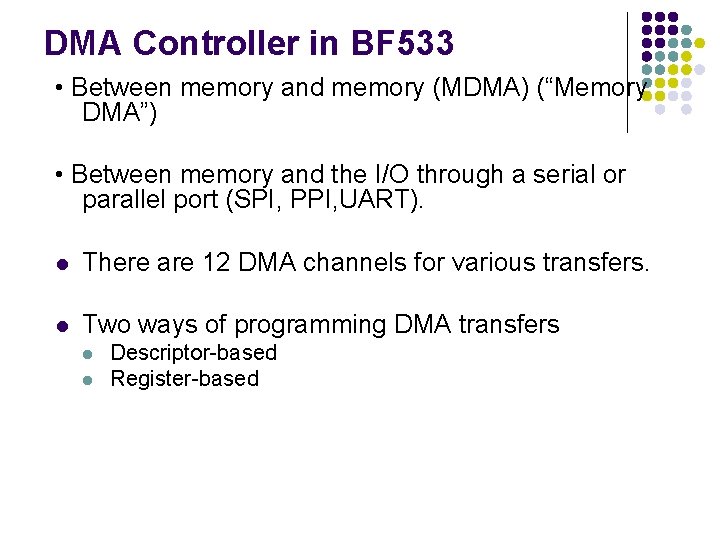

DMA Controller in BF 533 • Between memory and memory (MDMA) (“Memory DMA”) • Between memory and the I/O through a serial or parallel port (SPI, PPI, UART). l There are 12 DMA channels for various transfers. l Two ways of programming DMA transfers l l Descriptor-based Register-based

Descriptor-based DMA l l l Descriptor-based DMA transfers require a set of parameters stored within memory to initiate a DMA sequence. This sort of transfer allows the chaining together of multiple DMA sequences. In descriptor-based DMA operations, a DMA channel can be programmed to automatically set up and start another DMA transfer after the current sequence completes.

Register-based DMA l l Register-based DMA allows the processor to directly program DMA control registers to initiate a DMA transfer. On completion, the control registers may be automatically updated with their original setup values for continuous transfer, if needed.

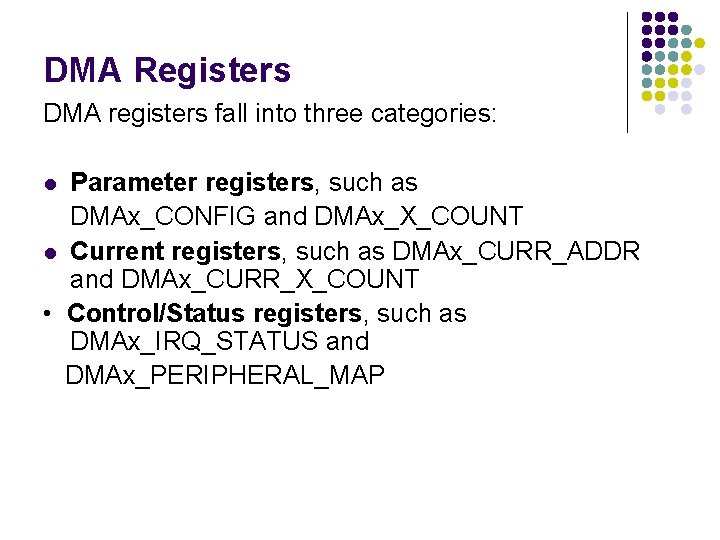

DMA Registers DMA registers fall into three categories: Parameter registers, such as DMAx_CONFIG and DMAx_X_COUNT l Current registers, such as DMAx_CURR_ADDR and DMAx_CURR_X_COUNT • Control/Status registers, such as DMAx_IRQ_STATUS and DMAx_PERIPHERAL_MAP l

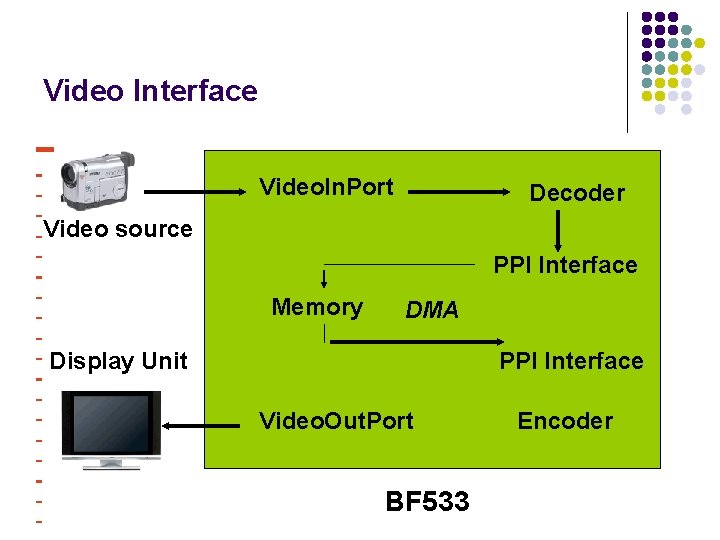

Video Interface Video. In. Port Decoder Video source PPI Interface Memory DMA Display Unit PPI Interface Video. Out. Port BF 533 Encoder

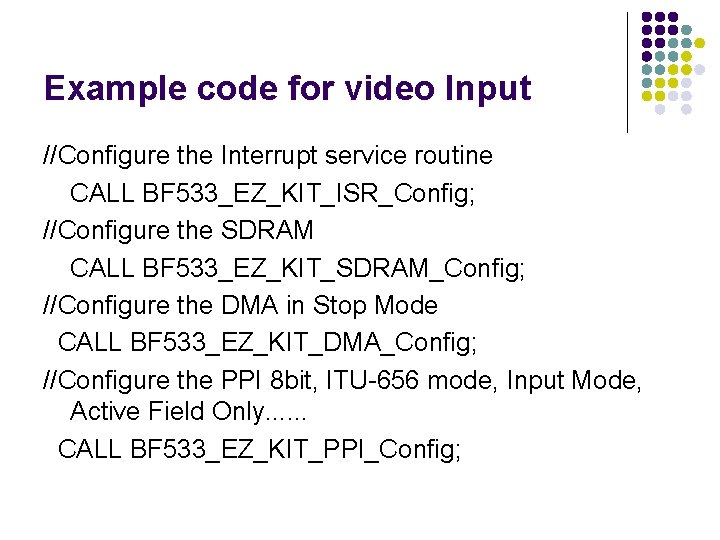

Example code for video Input //Configure the Interrupt service routine CALL BF 533_EZ_KIT_ISR_Config; //Configure the SDRAM CALL BF 533_EZ_KIT_SDRAM_Config; //Configure the DMA in Stop Mode CALL BF 533_EZ_KIT_DMA_Config; //Configure the PPI 8 bit, ITU-656 mode, Input Mode, Active Field Only. . . CALL BF 533_EZ_KIT_PPI_Config;

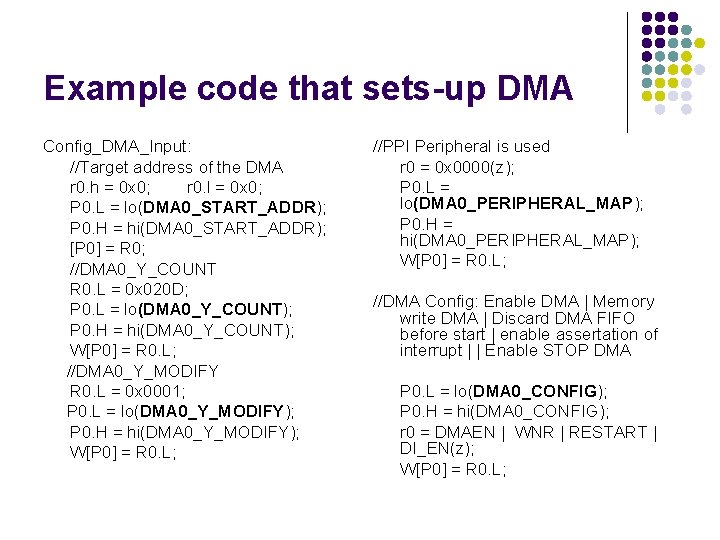

Example code that sets-up DMA Config_DMA_Input: //Target address of the DMA r 0. h = 0 x 0; r 0. l = 0 x 0; P 0. L = lo(DMA 0_START_ADDR); P 0. H = hi(DMA 0_START_ADDR); [P 0] = R 0; //DMA 0_Y_COUNT R 0. L = 0 x 020 D; P 0. L = lo(DMA 0_Y_COUNT); P 0. H = hi(DMA 0_Y_COUNT); W[P 0] = R 0. L; //DMA 0_Y_MODIFY R 0. L = 0 x 0001; P 0. L = lo(DMA 0_Y_MODIFY); P 0. H = hi(DMA 0_Y_MODIFY); W[P 0] = R 0. L; //PPI Peripheral is used r 0 = 0 x 0000(z); P 0. L = lo(DMA 0_PERIPHERAL_MAP); P 0. H = hi(DMA 0_PERIPHERAL_MAP); W[P 0] = R 0. L; //DMA Config: Enable DMA | Memory write DMA | Discard DMA FIFO before start | enable assertation of interrupt | | Enable STOP DMA P 0. L = lo(DMA 0_CONFIG); P 0. H = hi(DMA 0_CONFIG); r 0 = DMAEN | WNR | RESTART | DI_EN(z); W[P 0] = R 0. L;

Interrupt service routine //clear DMA interrupt P 0. L = lo(DMA 0_IRQ_STATUS); P 0. H = hi(DMA 0_IRQ_STATUS); R 0. L = W[P 0]; BITSET(R 0, 0); W[P 0] = R 0. L;

Tackled today l l The basic computer Improvements made to the basic computer l l l Interrupt handler DMA Controller in BF 533 Example code that demonstrates setting up the DMA Importance of DMA transfers in DSP algorithms

References l l l http: //engr. smu. edu/~levine/ee 8304/4 Analog Device’s BF 533 hardware manual http: //www. technology. niagarac. on. ca/courses/comp 530/DMANotes. htm

- Slides: 18