Dijital Elektronik Bipolar Teknii ile Gerekletirilen Saysal Kap

Dijital Elektronik Bipolar Tekniği ile Gerçekleştirilen Sayısal Kapı Aileleri

İçerik • Bipolar Transistörlü Evirici – Geçiş Eğrisi – Lojik Seviye Diyagramı – Çıkış Yelpazesi • TTL Ailesi (Transistör-Transistör Lojik) – Basit TTL Eviricinin Çıkış Yelpazesi – TTL VE-DEĞİL Kapısı • Giriş Transistörü • Totem-Pole Çıkış Katı – – Schottky Kenetlemeli TTL Kapıları Düşük Güçlü Schottky Kenetlemeli TTL Ailesi TTL VEYA-DEĞİL Kapısı TTL VE-KAPISI • ECL Ailesi (Emiter Bağlamalı Lojik) – ECL VEYA-VEYA DEĞİL Kapısı • I 2 Ailesi – Standart I 2 Ailesi

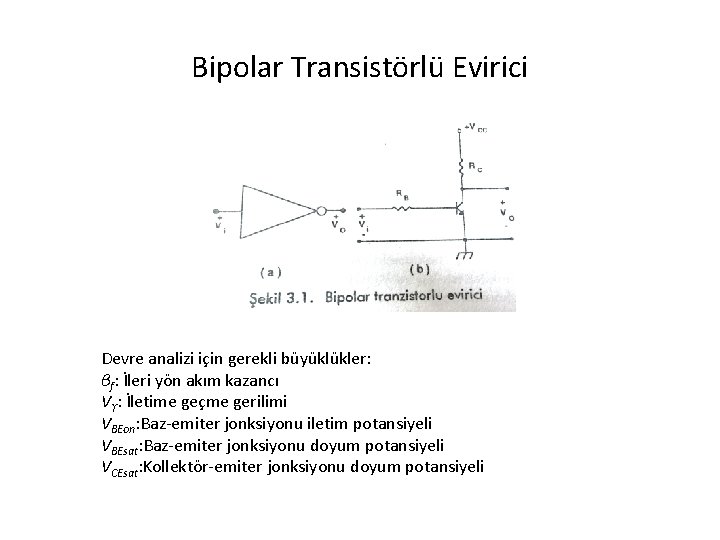

Bipolar Transistörlü Evirici Devre analizi için gerekli büyüklükler: βf: İleri yön akım kazancı Vϒ: İletime geçme gerilimi VBEon: Baz-emiter jonksiyonu iletim potansiyeli VBEsat: Baz-emiter jonksiyonu doyum potansiyeli VCEsat: Kollektör-emiter jonksiyonu doyum potansiyeli

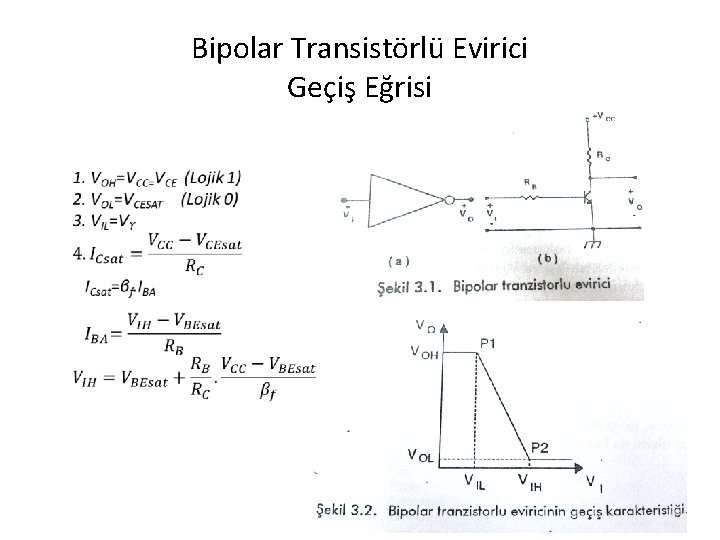

Bipolar Transistörlü Evirici Geçiş Eğrisi

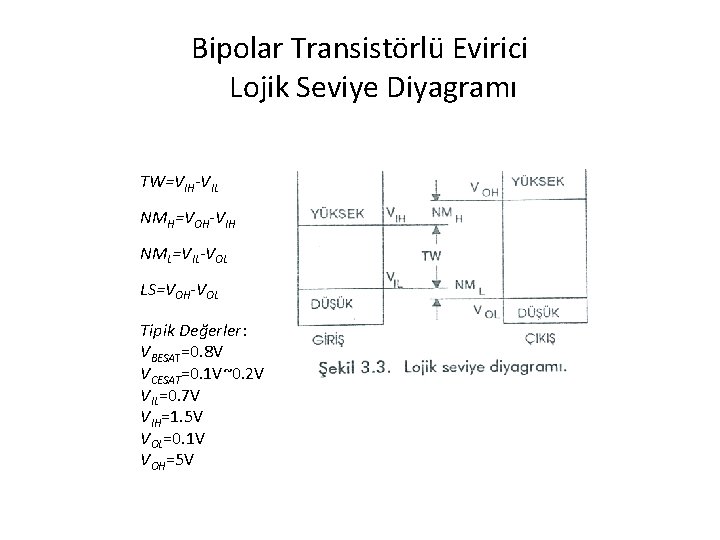

Bipolar Transistörlü Evirici Lojik Seviye Diyagramı TW=VIH-VIL NMH=VOH-VIH NML=VIL-VOL LS=VOH-VOL Tipik Değerler: VBESAT=0. 8 V VCESAT=0. 1 V~0. 2 V VIL=0. 7 V VIH=1. 5 V VOL=0. 1 V VOH=5 V

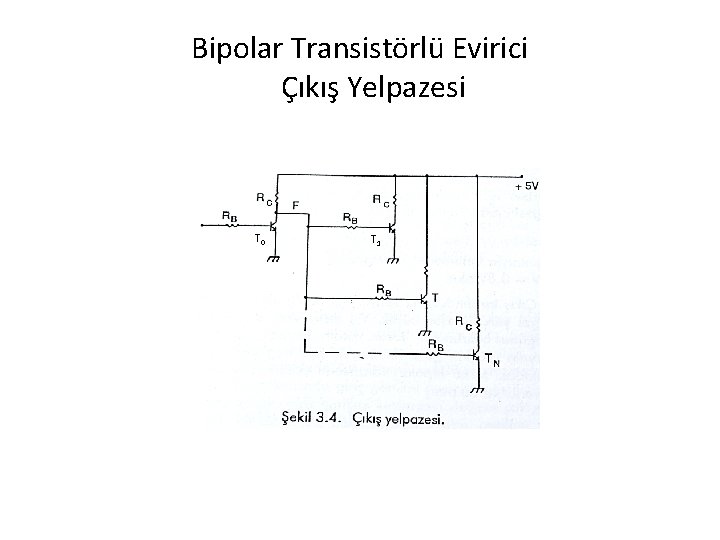

Bipolar Transistörlü Evirici Çıkış Yelpazesi T 0 T 1

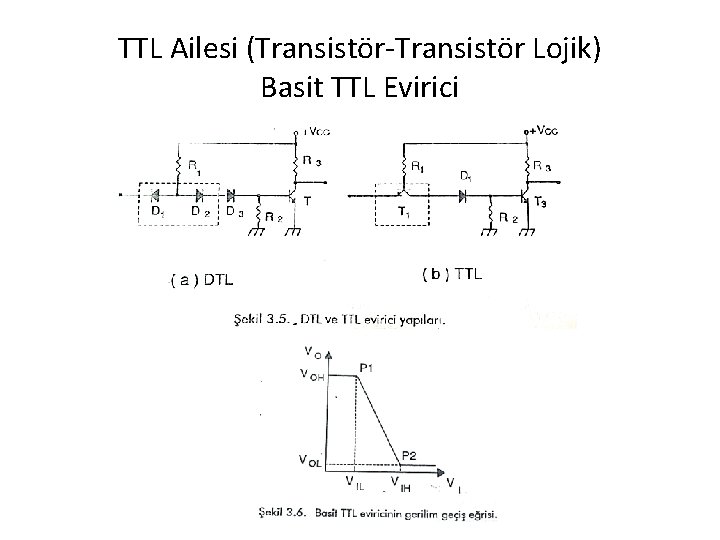

TTL Ailesi (Transistör-Transistör Lojik) Basit TTL Evirici

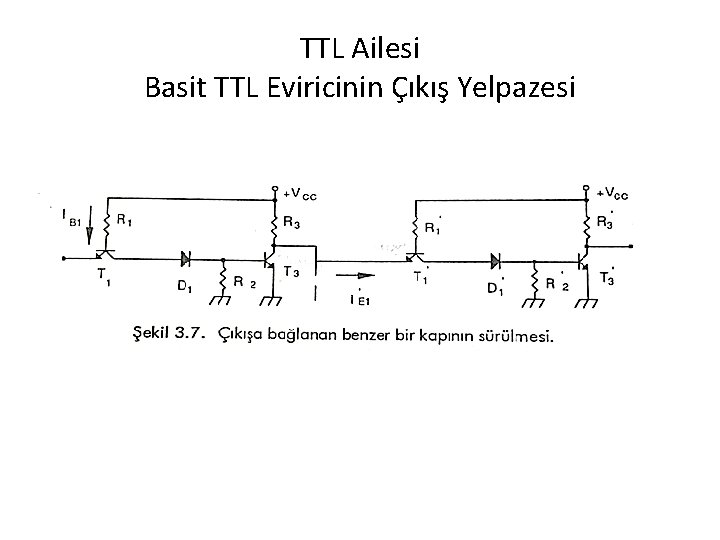

TTL Ailesi Basit TTL Eviricinin Çıkış Yelpazesi

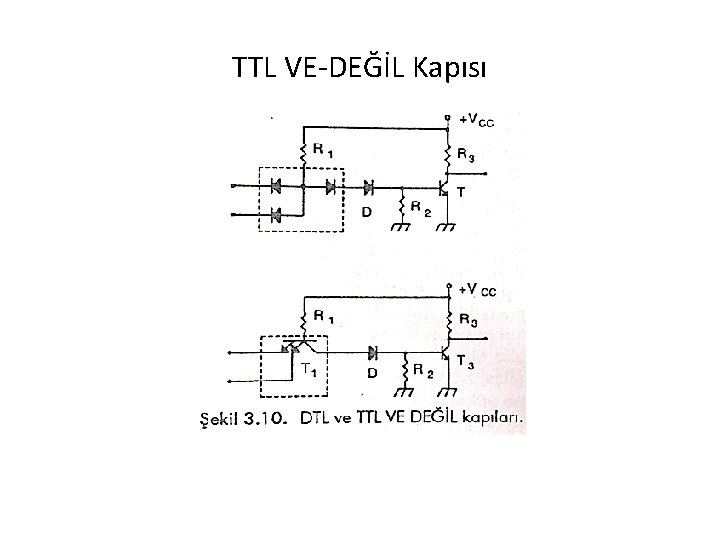

TTL VE-DEĞİL Kapısı

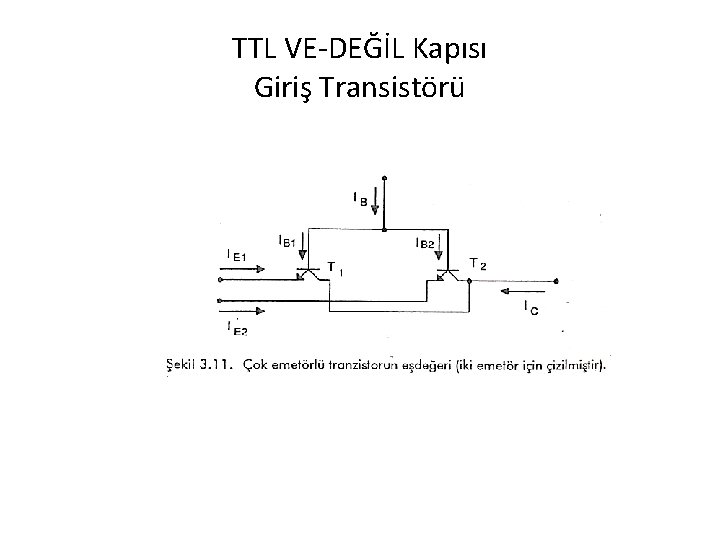

TTL VE-DEĞİL Kapısı Giriş Transistörü

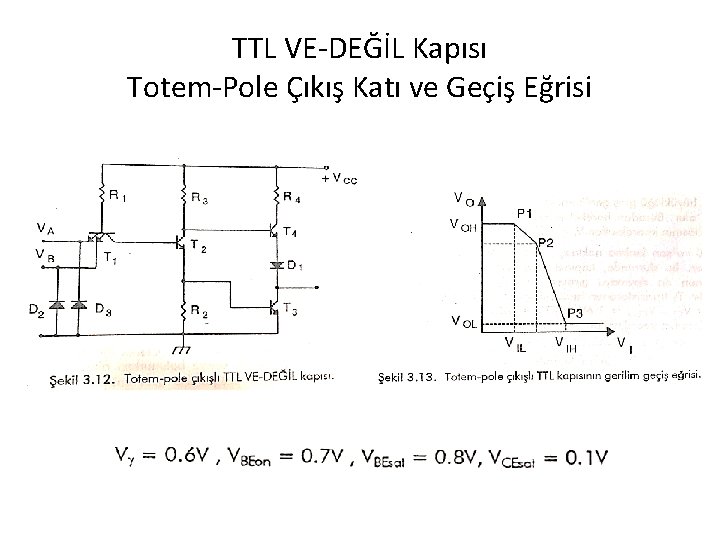

TTL VE-DEĞİL Kapısı Totem-Pole Çıkış Katı ve Geçiş Eğrisi

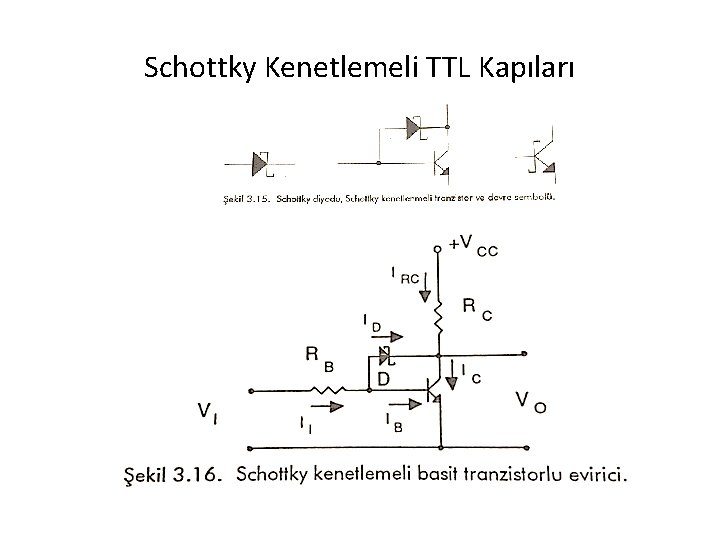

Schottky Kenetlemeli TTL Kapıları

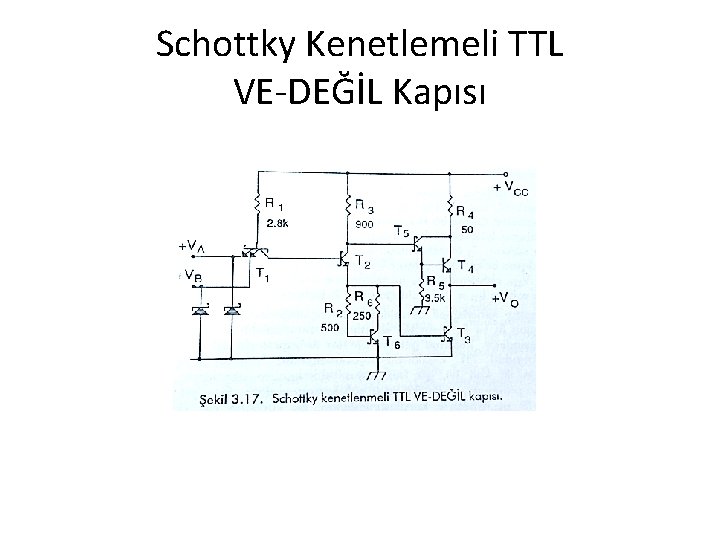

Schottky Kenetlemeli TTL VE-DEĞİL Kapısı

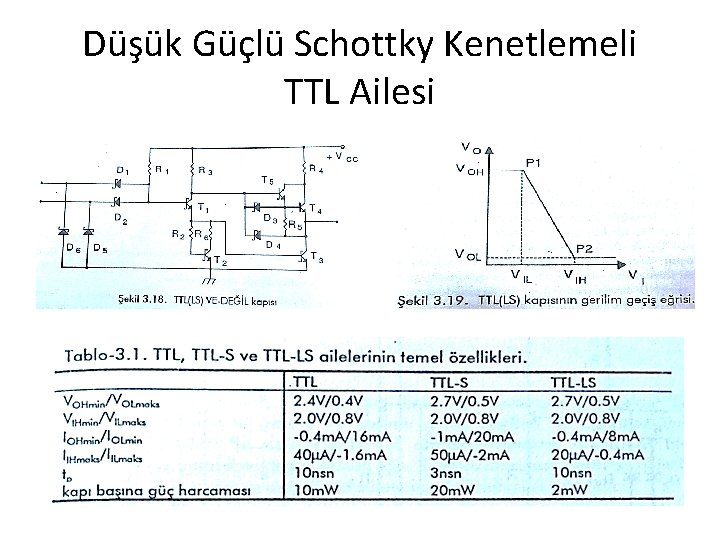

Düşük Güçlü Schottky Kenetlemeli TTL Ailesi

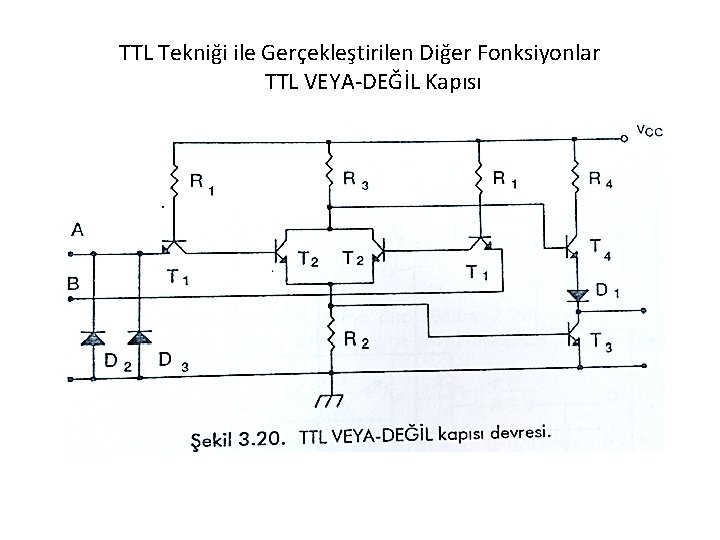

TTL Tekniği ile Gerçekleştirilen Diğer Fonksiyonlar TTL VEYA-DEĞİL Kapısı

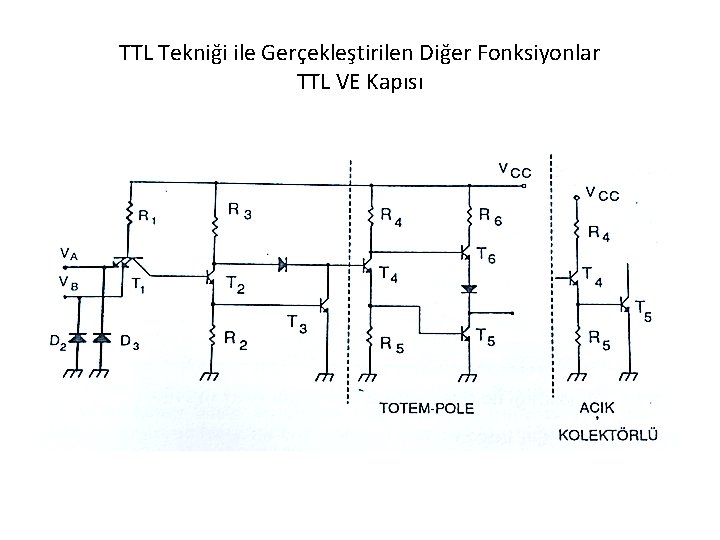

TTL Tekniği ile Gerçekleştirilen Diğer Fonksiyonlar TTL VE Kapısı

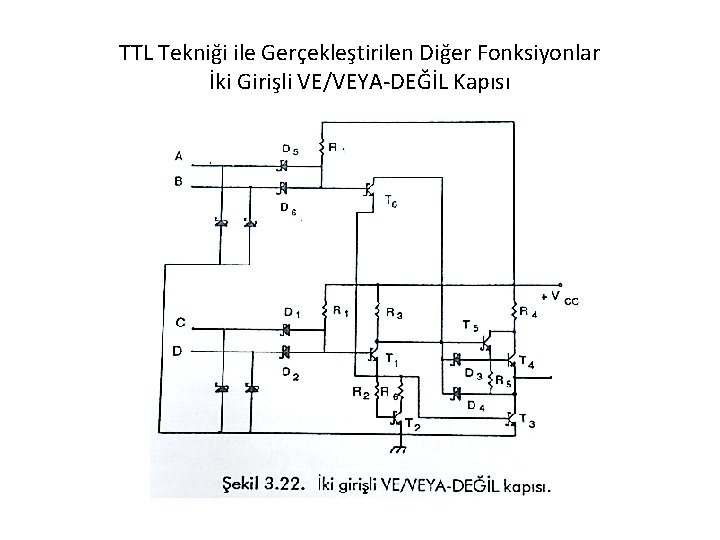

TTL Tekniği ile Gerçekleştirilen Diğer Fonksiyonlar İki Girişli VE/VEYA-DEĞİL Kapısı

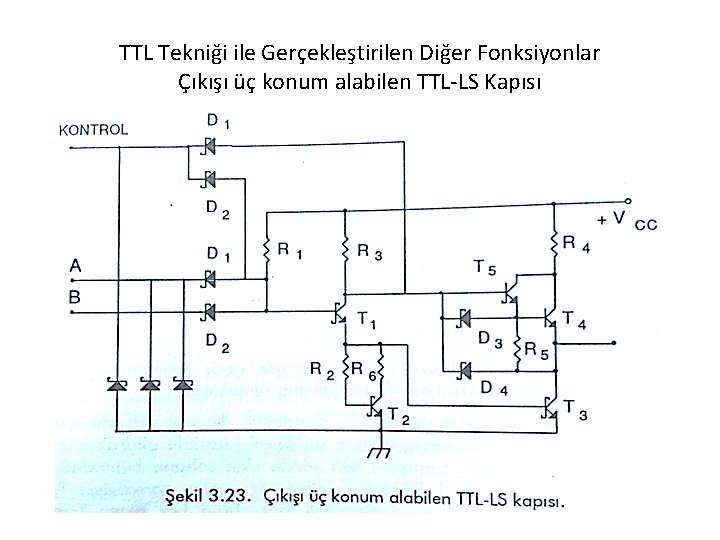

TTL Tekniği ile Gerçekleştirilen Diğer Fonksiyonlar Çıkışı üç konum alabilen TTL-LS Kapısı

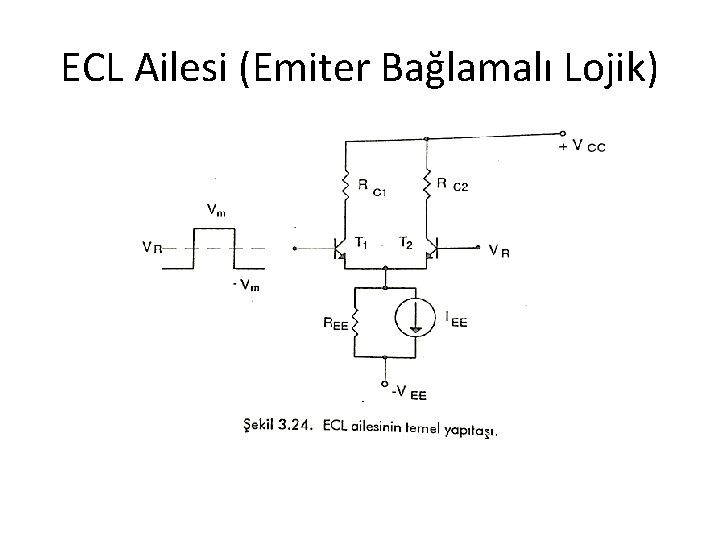

ECL Ailesi (Emiter Bağlamalı Lojik)

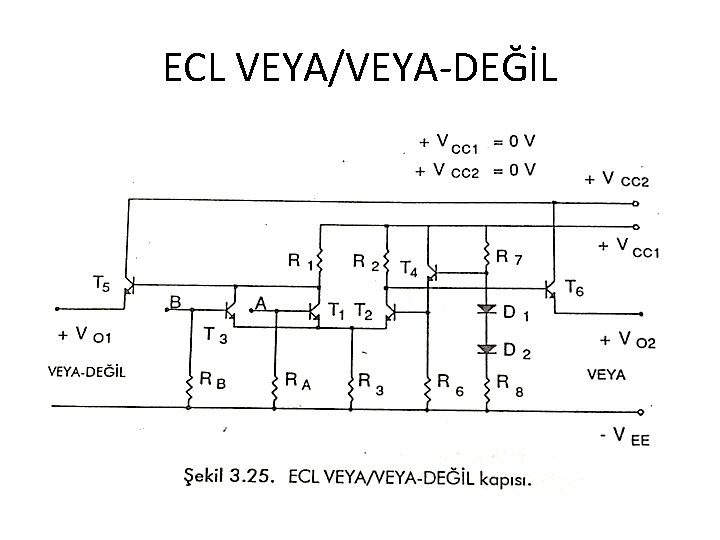

ECL VEYA/VEYA-DEĞİL

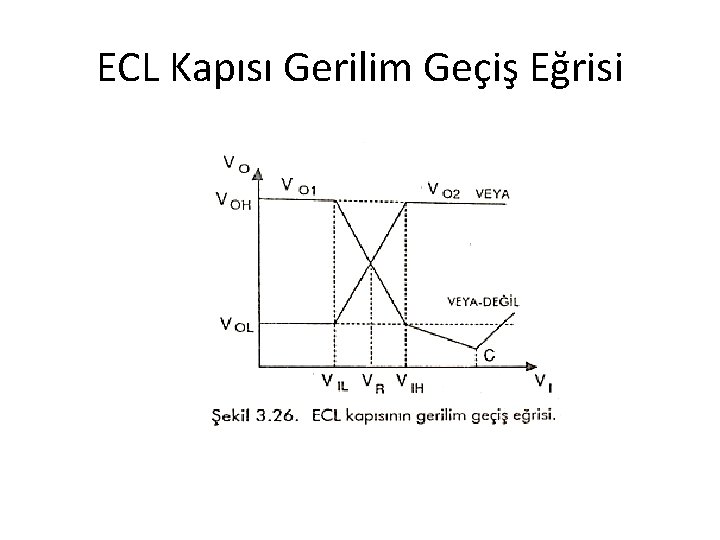

ECL Kapısı Gerilim Geçiş Eğrisi

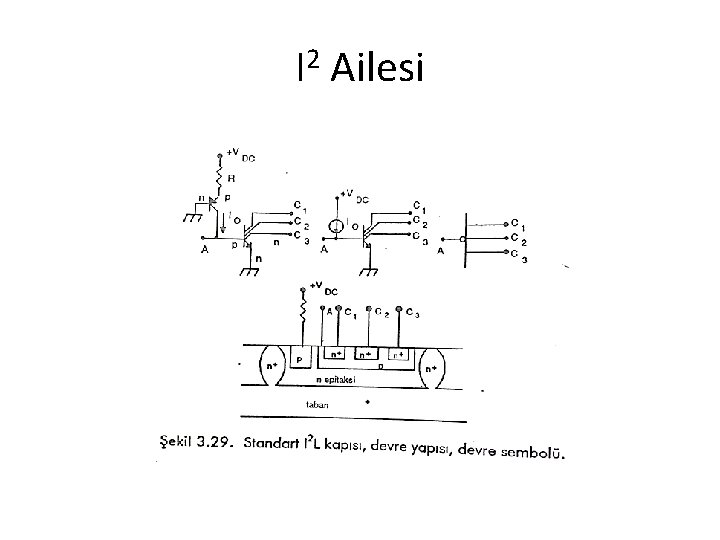

I 2 Ailesi

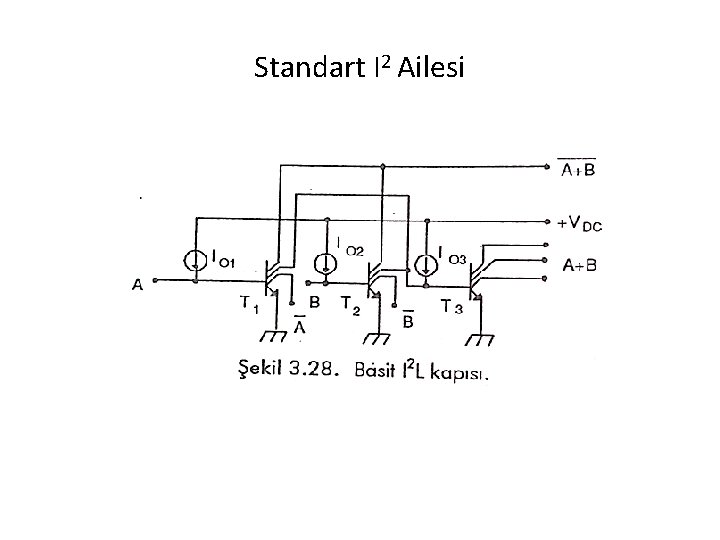

Standart I 2 Ailesi

- Slides: 23