Digitalna obrada signala u FPGA Raunarska aritmetika Raunarska

Digitalna obrada signala u FPGA Računarska aritmetika

Računarska aritmetika • Dva fundamentalna projektna principa RA – Predstavljanje brojeva – Implementacija algebarskih operacija • FPGA obezbeđuju raznovrsnost implementacija RA za željeni DOS algoritam, nasuprot PDSP sa fiksiranim MAC jezgrom. Izborom pogodne bitske širine, moguće su značajne uštede

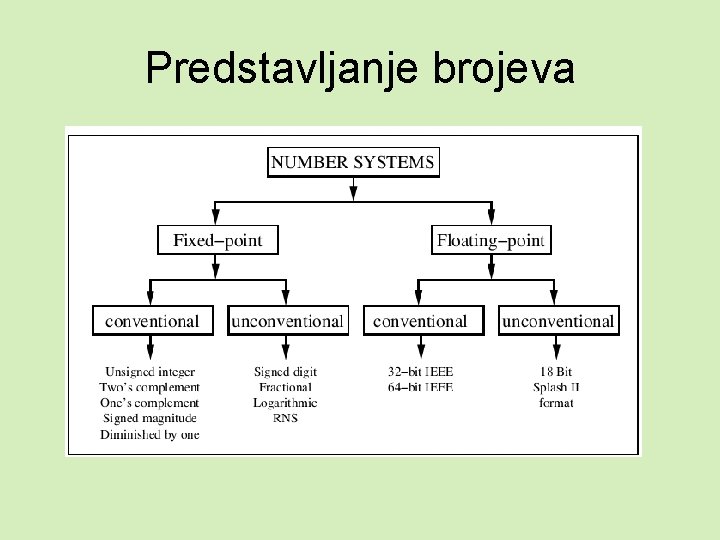

Predstavljanje brojeva • Što ranije na početku projektovanja valjalo bi izabrati između predstavljanje brojeva sa fiksnom ili pokretnom tačkom. • Uopšteno, implementacije sa fiksnom tačkom su brže i jeftinije, dok implementacije sa pokretnom tačkom imaju širi dinamički opseg i nema potrebe za skaliranjem što je dobro za komplikovane algoritme.

Predstavljanje brojeva

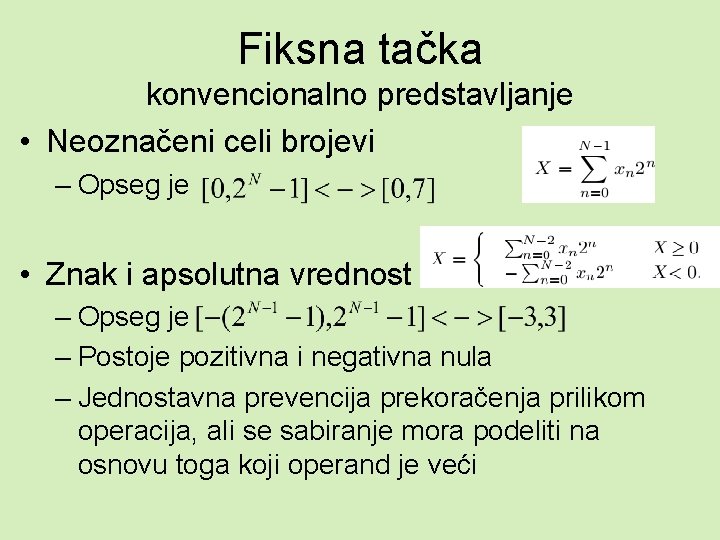

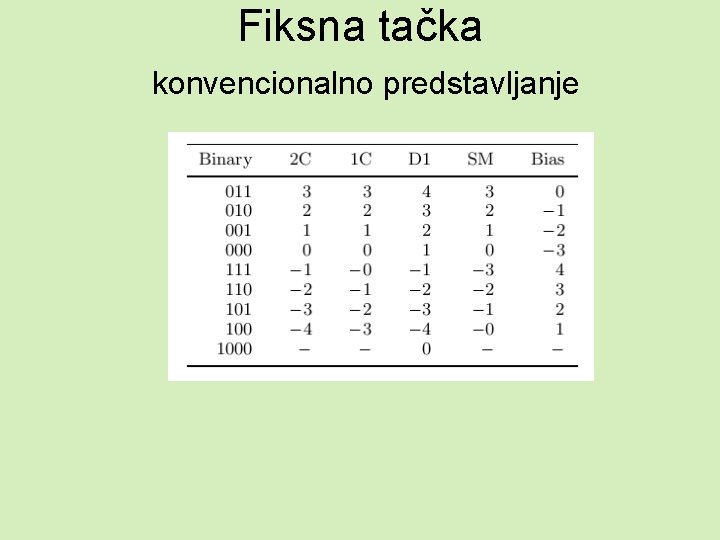

Fiksna tačka konvencionalno predstavljanje • Neoznačeni celi brojevi – Opseg je • Znak i apsolutna vrednost – Opseg je – Postoje pozitivna i negativna nula – Jednostavna prevencija prekoračenja prilikom operacija, ali se sabiranje mora podeliti na osnovu toga koji operand je veći

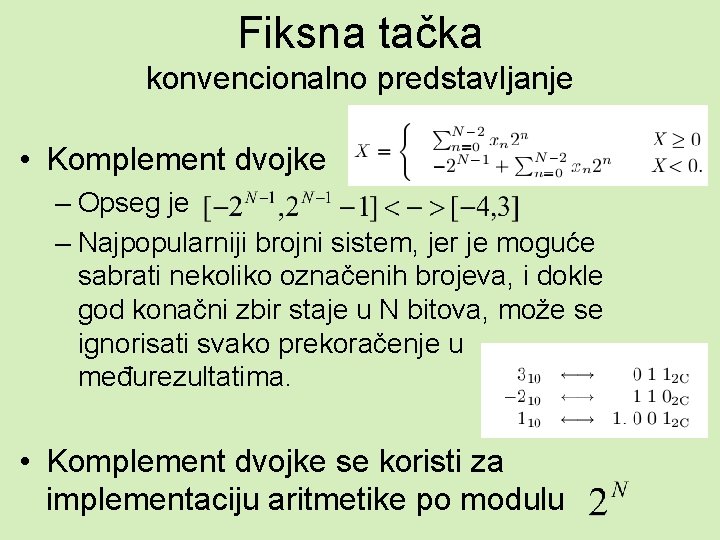

Fiksna tačka konvencionalno predstavljanje • Komplement dvojke – Opseg je – Najpopularniji brojni sistem, jer je moguće sabrati nekoliko označenih brojeva, i dokle god konačni zbir staje u N bitova, može se ignorisati svako prekoračenje u međurezultatima. • Komplement dvojke se koristi za implementaciju aritmetike po modulu

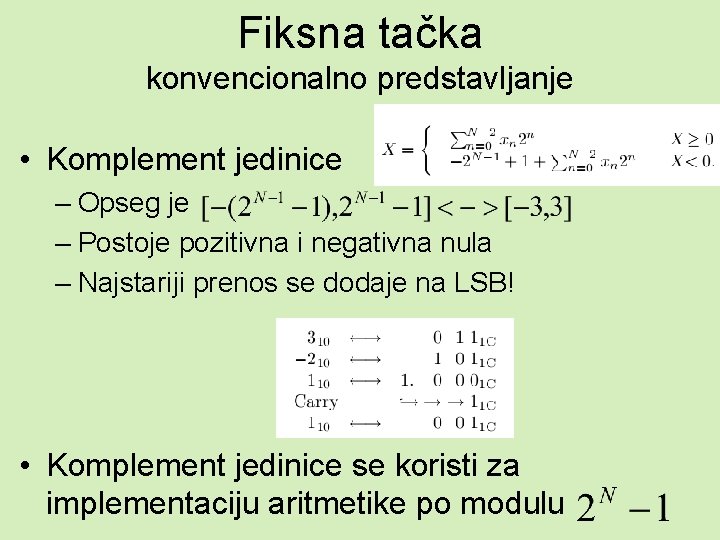

Fiksna tačka konvencionalno predstavljanje • Komplement jedinice – Opseg je – Postoje pozitivna i negativna nula – Najstariji prenos se dodaje na LSB! • Komplement jedinice se koristi za implementaciju aritmetike po modulu

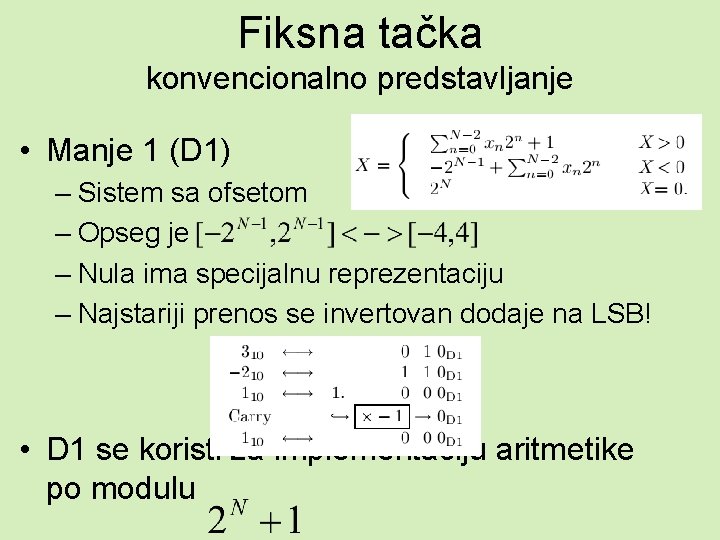

Fiksna tačka konvencionalno predstavljanje • Manje 1 (D 1) – Sistem sa ofsetom – Opseg je – Nula ima specijalnu reprezentaciju – Najstariji prenos se invertovan dodaje na LSB! • D 1 se koristi za implementaciju aritmetike po modulu

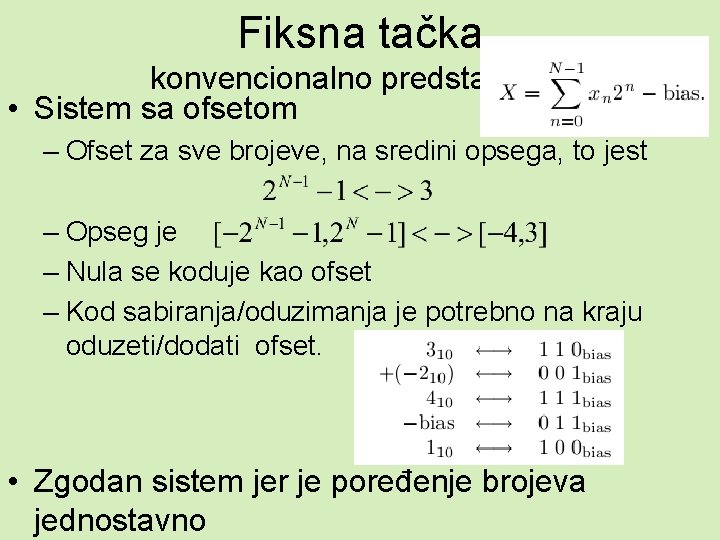

Fiksna tačka konvencionalno predstavljanje • Sistem sa ofsetom – Ofset za sve brojeve, na sredini opsega, to jest – Opseg je – Nula se koduje kao ofset – Kod sabiranja/oduzimanja je potrebno na kraju oduzeti/dodati ofset. • Zgodan sistem jer je poređenje brojeva jednostavno

Fiksna tačka konvencionalno predstavljanje

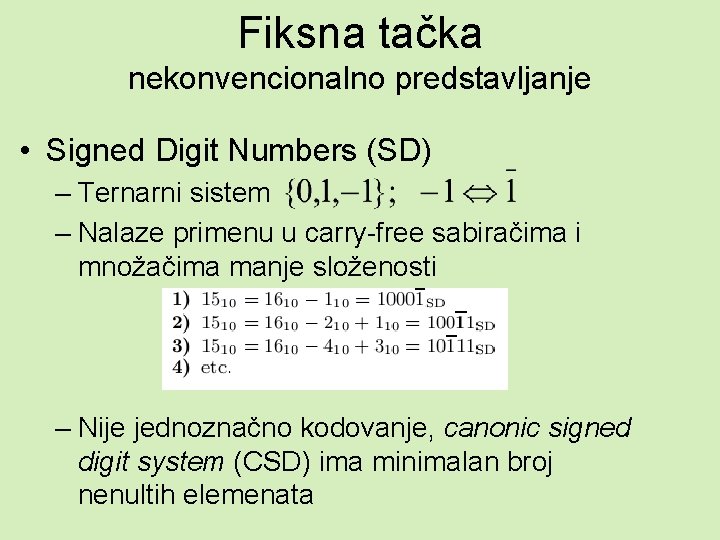

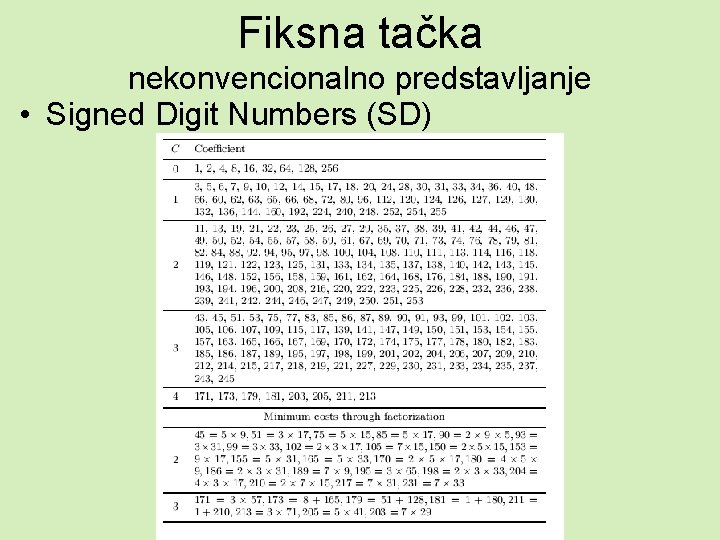

Fiksna tačka nekonvencionalno predstavljanje • Signed Digit Numbers (SD) – Ternarni sistem – Nalaze primenu u carry-free sabiračima i množačima manje složenosti – Nije jednoznačno kodovanje, canonic signed digit system (CSD) ima minimalan broj nenultih elemenata

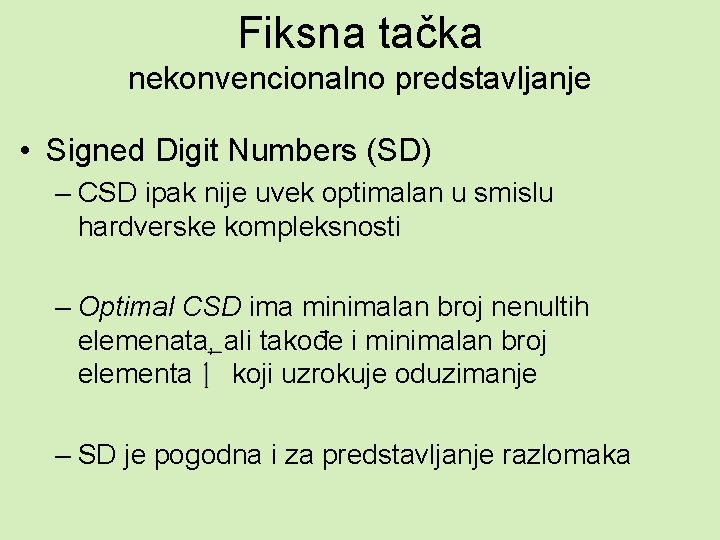

Fiksna tačka nekonvencionalno predstavljanje • Signed Digit Numbers (SD) – CSD ipak nije uvek optimalan u smislu hardverske kompleksnosti – Optimal CSD ima minimalan broj nenultih elemenata, ali takođe i minimalan broj elementa koji uzrokuje oduzimanje – SD je pogodna i za predstavljanje razlomaka

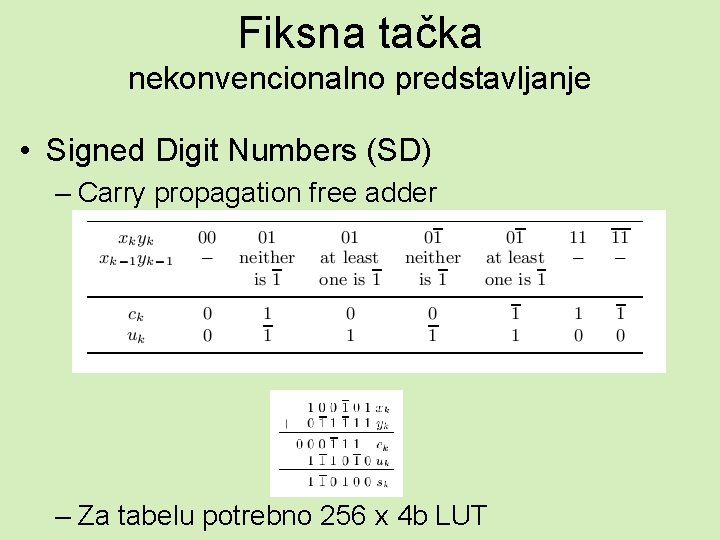

Fiksna tačka nekonvencionalno predstavljanje • Signed Digit Numbers (SD) – Carry propagation free adder – Za tabelu potrebno 256 x 4 b LUT

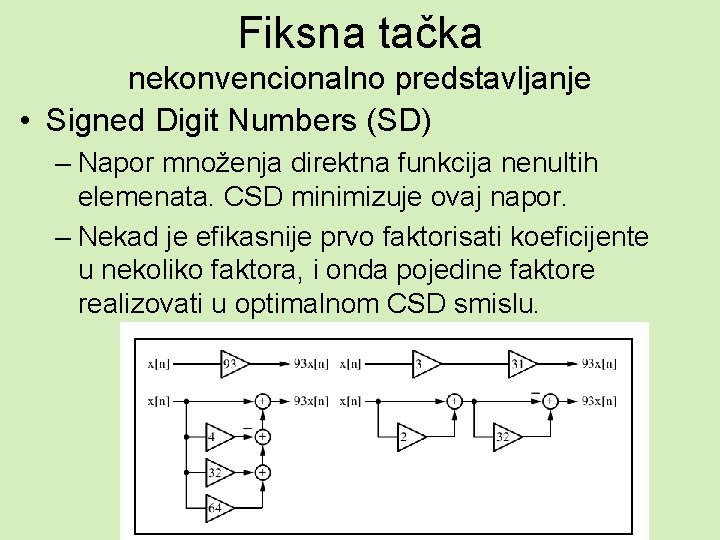

Fiksna tačka nekonvencionalno predstavljanje • Signed Digit Numbers (SD) – Napor množenja direktna funkcija nenultih elemenata. CSD minimizuje ovaj napor. – Nekad je efikasnije prvo faktorisati koeficijente u nekoliko faktora, i onda pojedine faktore realizovati u optimalnom CSD smislu.

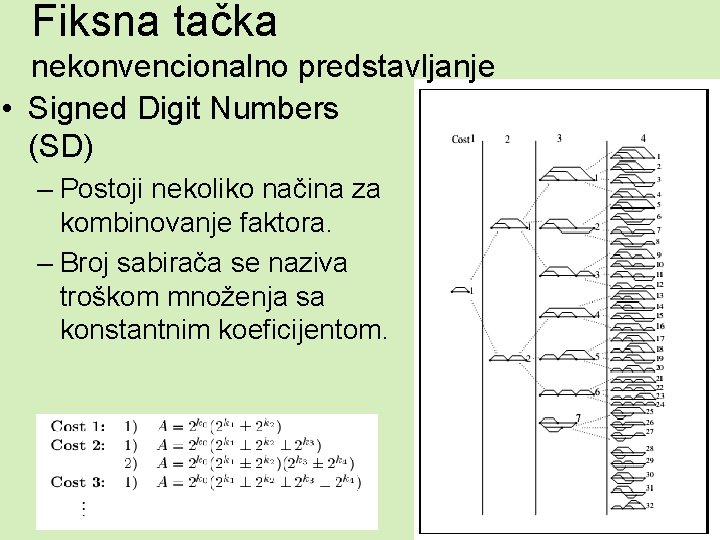

Fiksna tačka nekonvencionalno predstavljanje • Signed Digit Numbers (SD) – Postoji nekoliko načina za kombinovanje faktora. – Broj sabirača se naziva troškom množenja sa konstantnim koeficijentom.

Fiksna tačka nekonvencionalno predstavljanje • Signed Digit Numbers (SD)

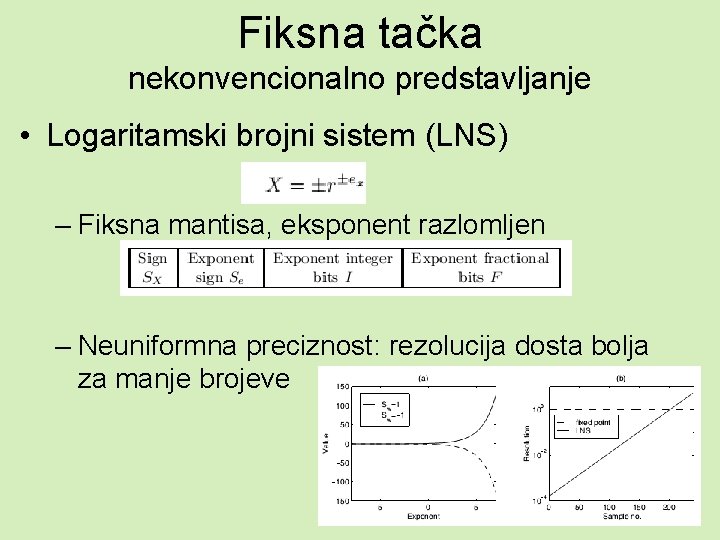

Fiksna tačka nekonvencionalno predstavljanje • Logaritamski brojni sistem (LNS) – Fiksna mantisa, eksponent razlomljen – Neuniformna preciznost: rezolucija dosta bolja za manje brojeve

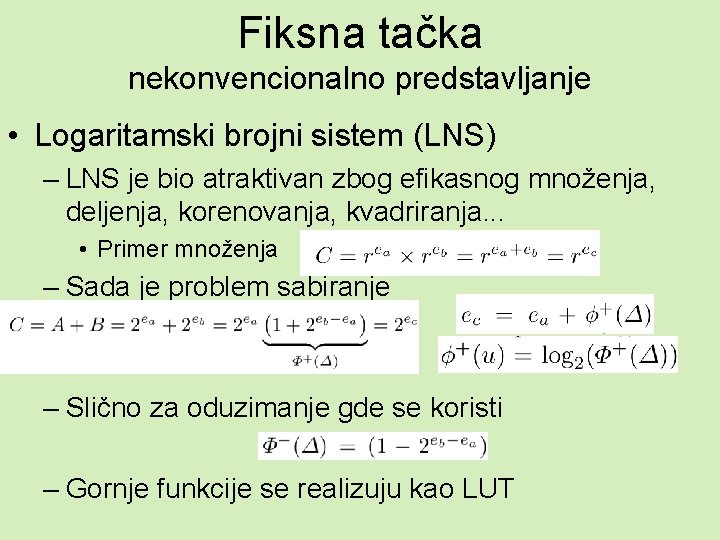

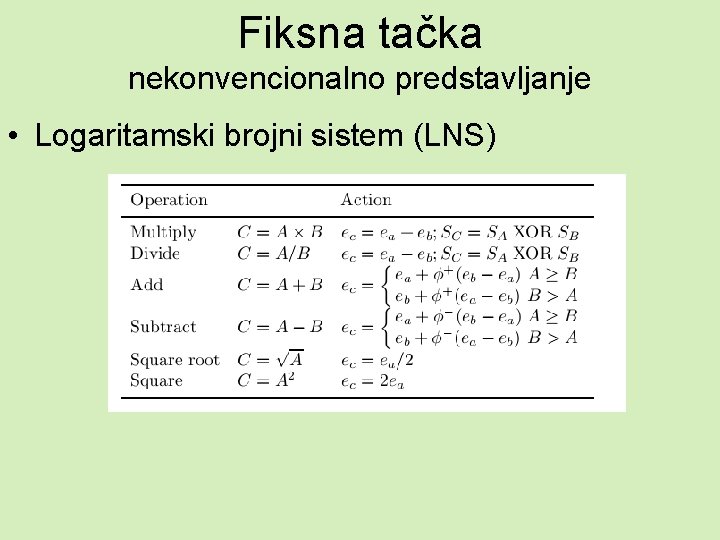

Fiksna tačka nekonvencionalno predstavljanje • Logaritamski brojni sistem (LNS) – LNS je bio atraktivan zbog efikasnog množenja, deljenja, korenovanja, kvadriranja. . . • Primer množenja – Sada je problem sabiranje – Slično za oduzimanje gde se koristi – Gornje funkcije se realizuju kao LUT

Fiksna tačka nekonvencionalno predstavljanje • Logaritamski brojni sistem (LNS)

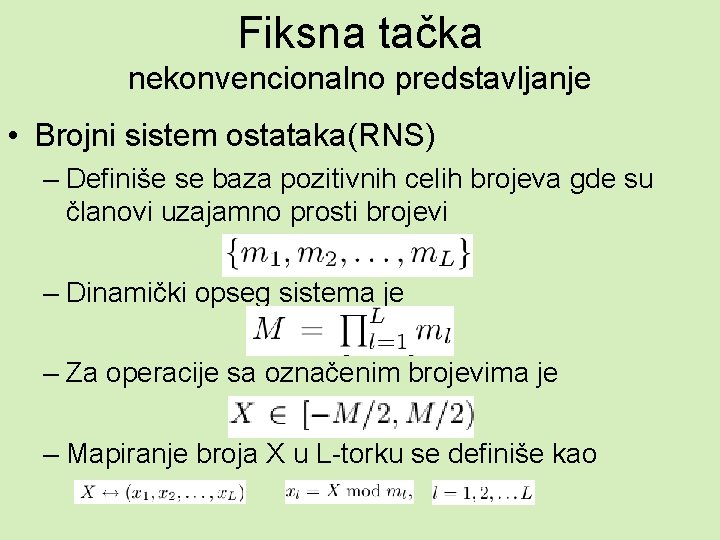

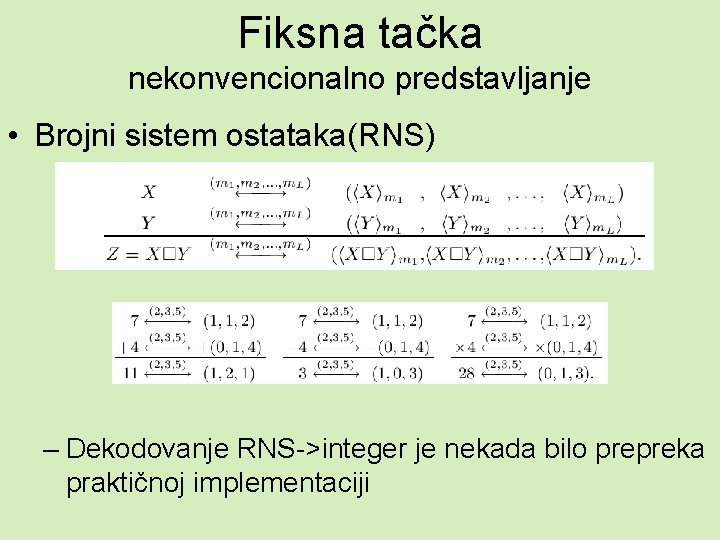

Fiksna tačka nekonvencionalno predstavljanje • Brojni sistem ostataka(RNS) – Definiše se baza pozitivnih celih brojeva gde su članovi uzajamno prosti brojevi – Dinamički opseg sistema je – Za operacije sa označenim brojevima je – Mapiranje broja X u L-torku se definiše kao

Fiksna tačka nekonvencionalno predstavljanje • Brojni sistem ostataka(RNS) – Dekodovanje RNS->integer je nekada bilo prepreka praktičnoj implementaciji

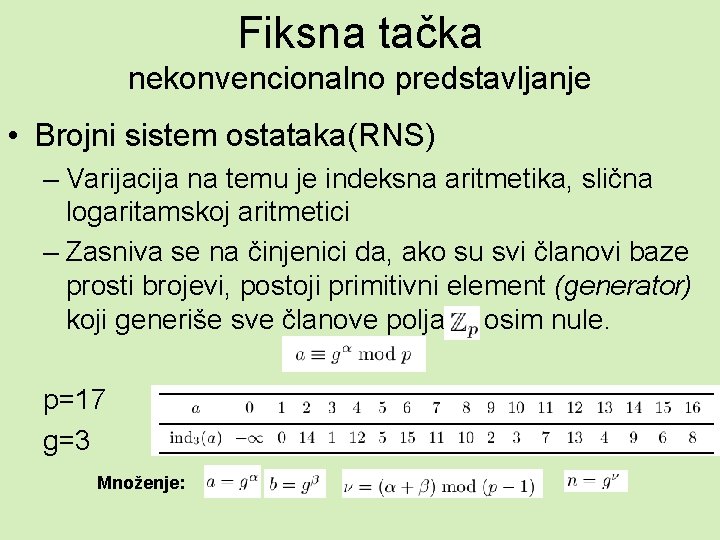

Fiksna tačka nekonvencionalno predstavljanje • Brojni sistem ostataka(RNS) – Varijacija na temu je indeksna aritmetika, slična logaritamskoj aritmetici – Zasniva se na činjenici da, ako su svi članovi baze prosti brojevi, postoji primitivni element (generator) koji generiše sve članove polja osim nule. p=17 g=3 Množenje:

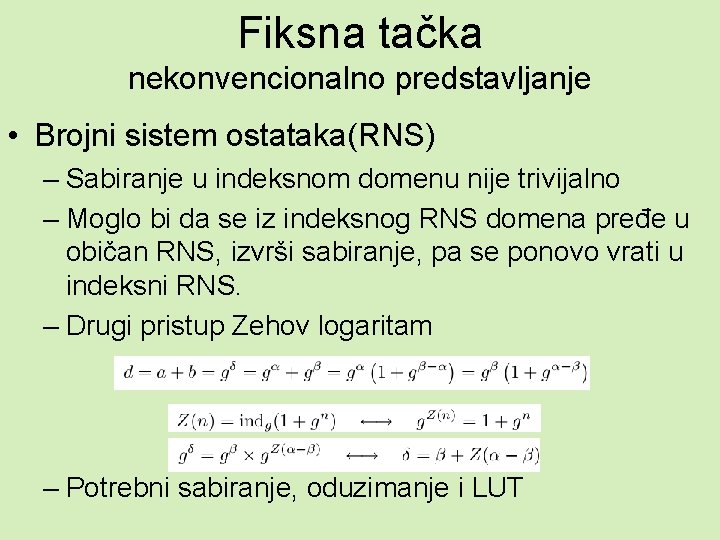

Fiksna tačka nekonvencionalno predstavljanje • Brojni sistem ostataka(RNS) – Sabiranje u indeksnom domenu nije trivijalno – Moglo bi da se iz indeksnog RNS domena pređe u običan RNS, izvrši sabiranje, pa se ponovo vrati u indeksni RNS. – Drugi pristup Zehov logaritam – Potrebni sabiranje, oduzimanje i LUT

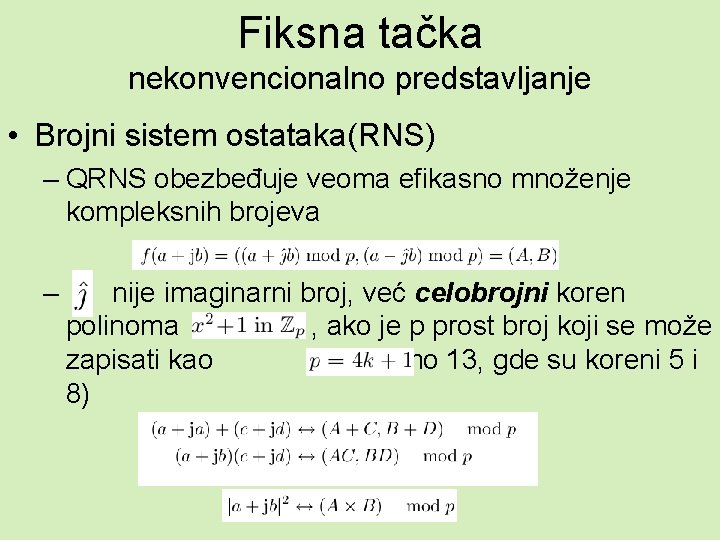

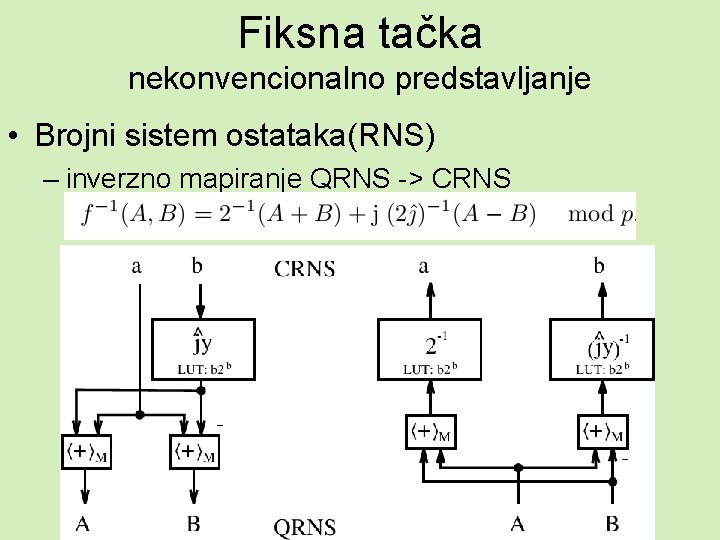

Fiksna tačka nekonvencionalno predstavljanje • Brojni sistem ostataka(RNS) – QRNS obezbeđuje veoma efikasno množenje kompleksnih brojeva – nije imaginarni broj, već celobrojni koren polinoma , ako je p prost broj koji se može zapisati kao (recimo 13, gde su koreni 5 i 8)

Fiksna tačka nekonvencionalno predstavljanje • Brojni sistem ostataka(RNS) – inverzno mapiranje QRNS -> CRNS

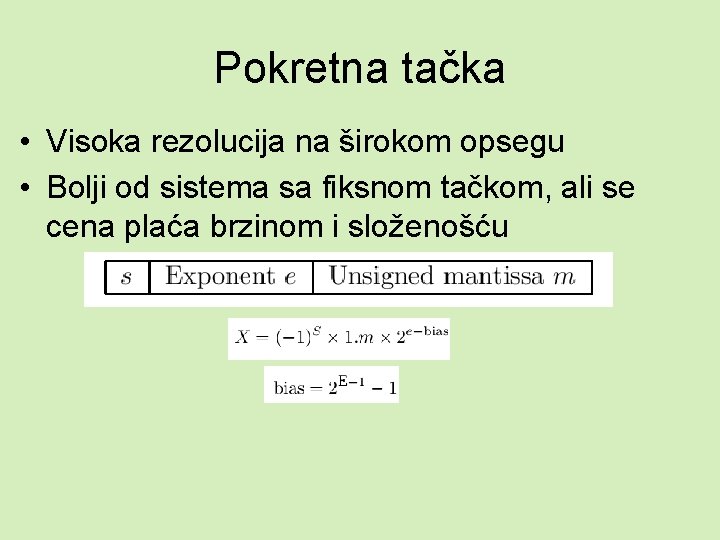

Pokretna tačka • Visoka rezolucija na širokom opsegu • Bolji od sistema sa fiksnom tačkom, ali se cena plaća brzinom i složenošću

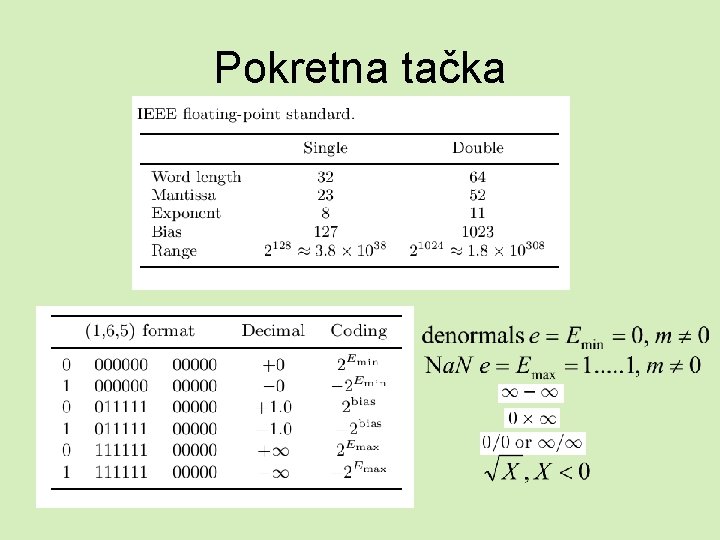

Pokretna tačka

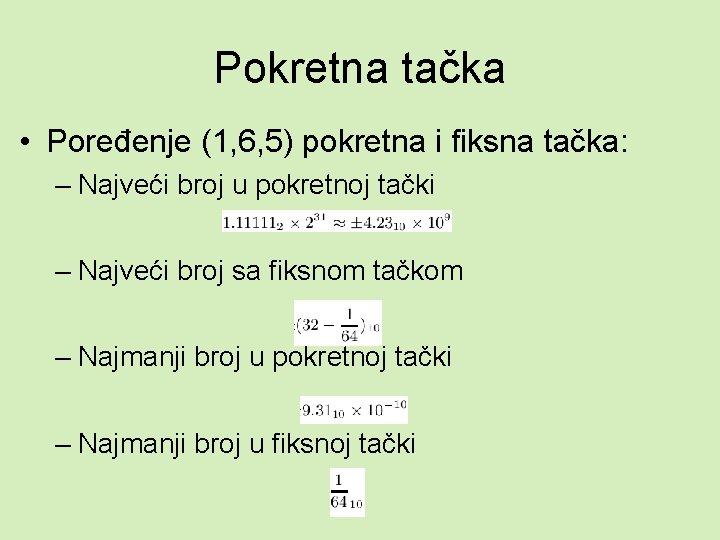

Pokretna tačka • Poređenje (1, 6, 5) pokretna i fiksna tačka: – Najveći broj u pokretnoj tački – Najveći broj sa fiksnom tačkom – Najmanji broj u pokretnoj tački – Najmanji broj u fiksnoj tački

Pokretna tačka • Već implementacija sa 32 bita zahteva 24 x 24 množač • FPGA dozvoljava dizajn sa određenijim dinamičkim opsegom (širina eksponenta) i preciznošću (širina mantise) • Stoga se obično definiše poseban format. • SPLASH-2 (1, 10, 7) koristi 18 bitni format, jer je zgodno da se preko magistrale od 36 bita prenose dva operanda paralelno. Dinamički opseg je

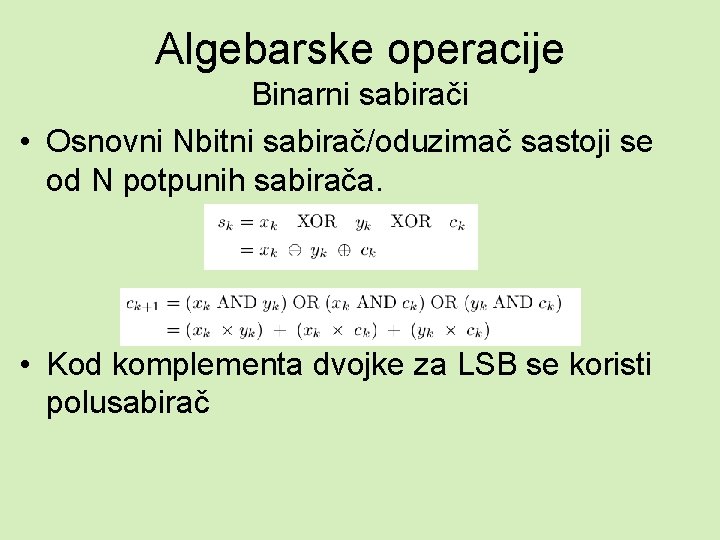

Algebarske operacije Binarni sabirači • Osnovni Nbitni sabirač/oduzimač sastoji se od N potpunih sabirača. • Kod komplementa dvojke za LSB se koristi polusabirač

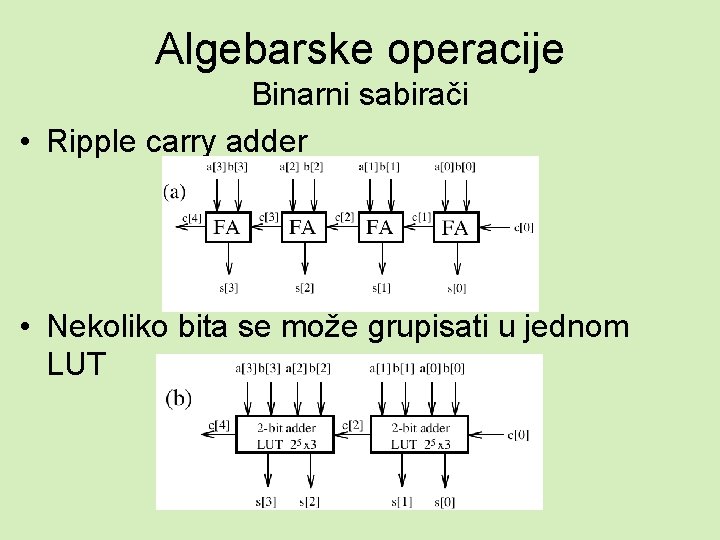

Algebarske operacije Binarni sabirači • Ripple carry adder • Nekoliko bita se može grupisati u jednom LUT

Algebarske operacije Binarni sabirači • Ripple carry adder – Najveće kašnjenje potiče od propagacije prenosa kroz sve blokove – Razvijene su tehnike za smanjenje ovog kašnjenja – Nemaju smisla u modernim FPGA jer u njima postoji interna brza logika za prenos, red veličine brža od kašnjenja kroz LUT

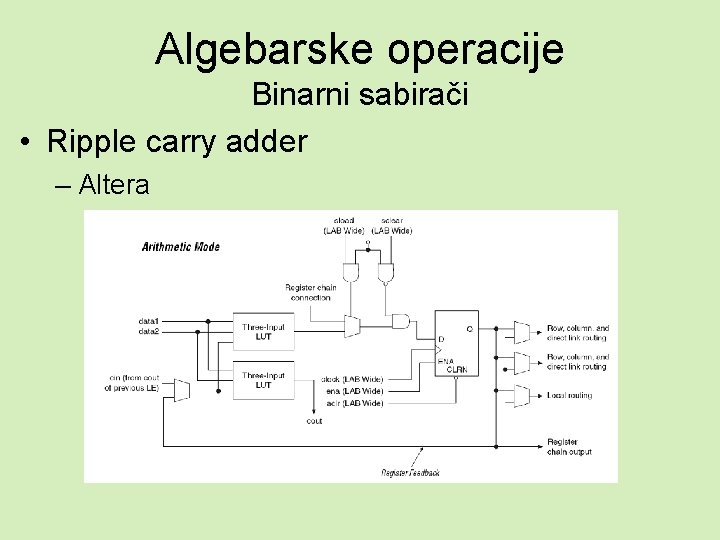

Algebarske operacije Binarni sabirači • Ripple carry adder – Altera

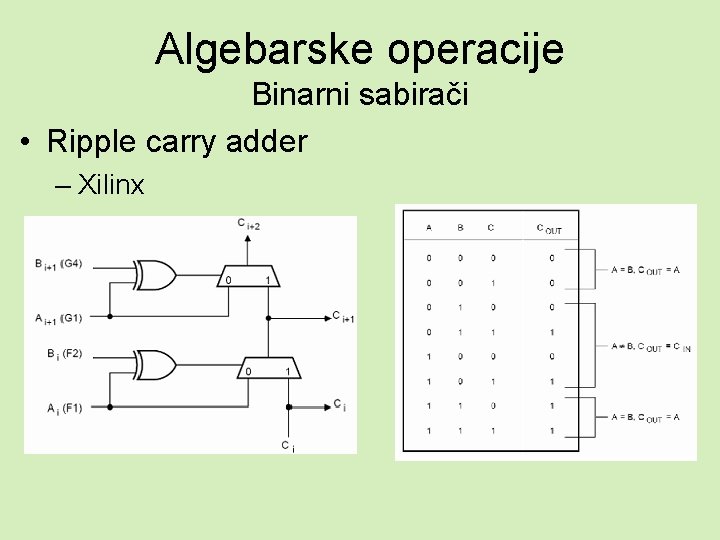

Algebarske operacije Binarni sabirači • Ripple carry adder – Xilinx

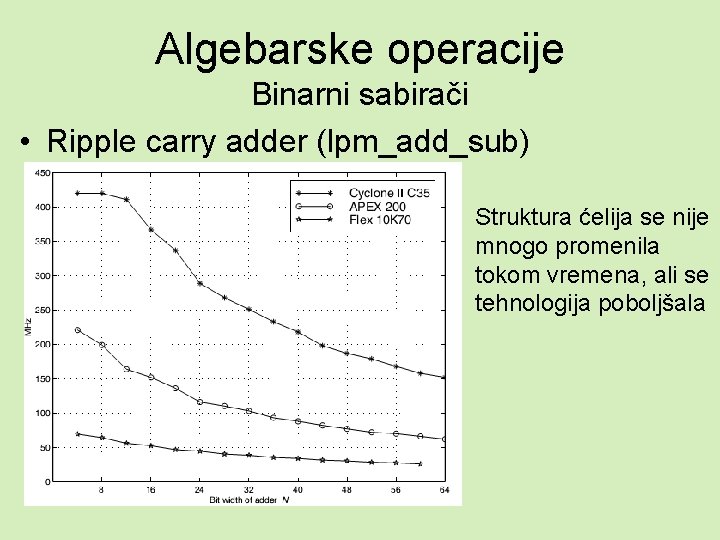

Algebarske operacije Binarni sabirači • Ripple carry adder (lpm_add_sub) Struktura ćelija se nije mnogo promenila tokom vremena, ali se tehnologija poboljšala

Algebarske operacije Binarni sabirači • Protočni (pipelined) sabirači – Protočnost se intenzivno koristi u DOS. – Tipično MAC u PDPS ima četiri stepena • • Dekodovanje komande Učitavanje operanada Množenje i pamćenje proizvoda Sabiranje proizvoda • Ovaj princip se primenjuje u FPGA, uz gotovo nikakvo povećanje resursa, jer LE sadrži i FF koji se inače ne koristi.

Algebarske operacije Binarni sabirači • Protočni (pipelined) sabirači – Aritmetička operacija se deli na male primitivne operacije, prenos i međuvrednosti se pamte u registrima, i računanje nastavlja u sledećem ciklusu. – Pitanje je na koliko nivoa podeliti sabirač? – Najekonomičnije je iskoristiti jedan LAB sa xy LE za jedan nivo. Jedan LE se mora koristi za prenos, osim na MSB delu

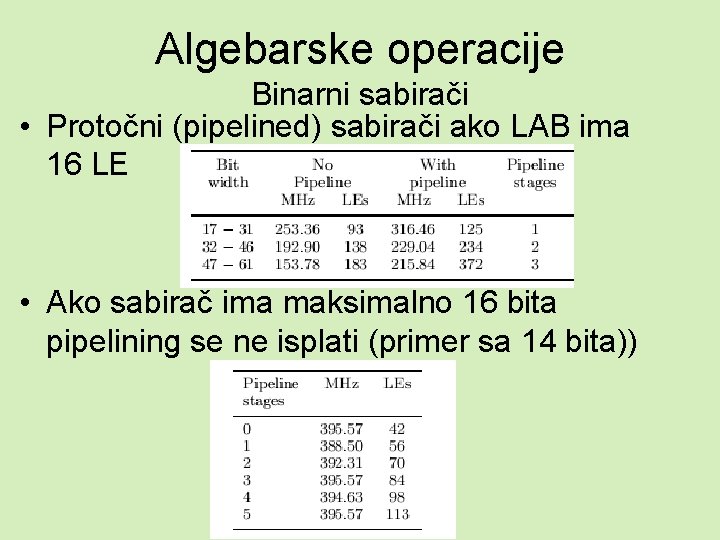

Algebarske operacije Binarni sabirači • Protočni (pipelined) sabirači ako LAB ima 16 LE • Ako sabirač ima maksimalno 16 bita pipelining se ne isplati (primer sa 14 bita))

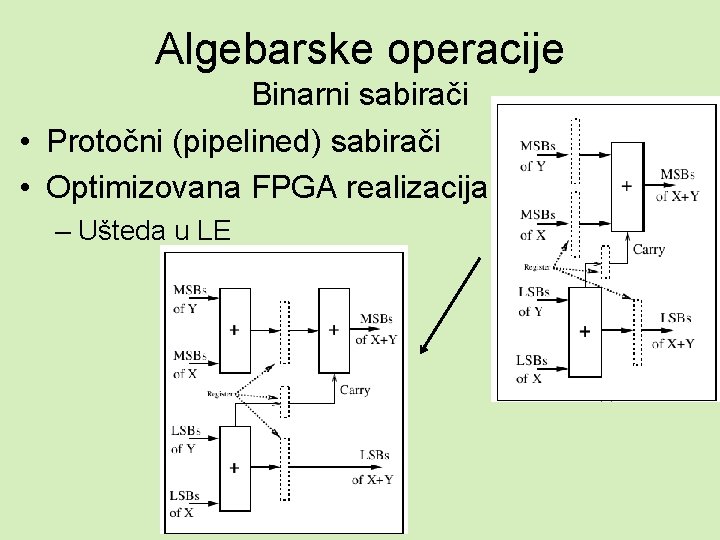

Algebarske operacije Binarni sabirači • Protočni (pipelined) sabirači • Optimizovana FPGA realizacija – Ušteda u LE

Algebarske operacije Sabirači po modulu • Najvažniji gradivni blokovi u RNS dizajnima. Koriste se i za sabiranje i (u indeksnom domenu) množenje.

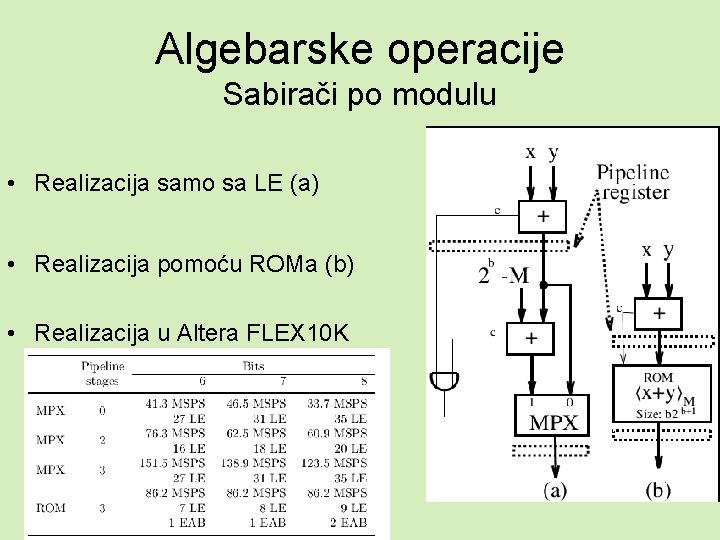

Algebarske operacije Sabirači po modulu • Realizacija samo sa LE (a) • Realizacija pomoću ROMa (b) • Realizacija u Altera FLEX 10 K

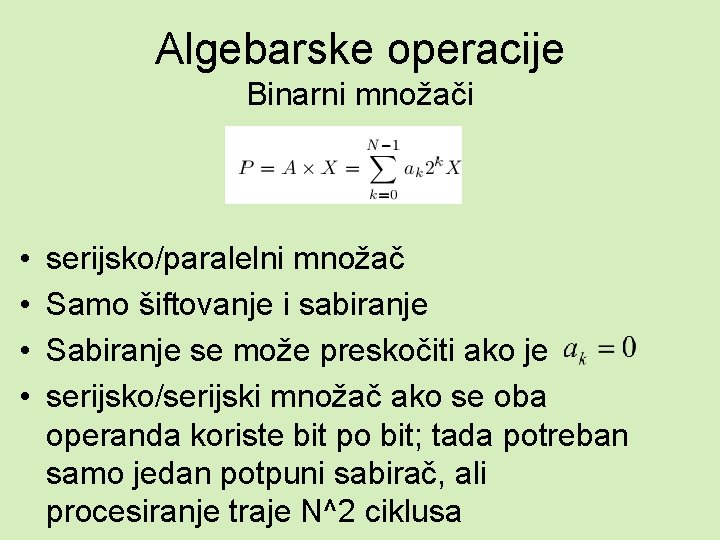

Algebarske operacije Binarni množači • • serijsko/paralelni množač Samo šiftovanje i sabiranje Sabiranje se može preskočiti ako je serijsko/serijski množač ako se oba operanda koriste bit po bit; tada potreban samo jedan potpuni sabirač, ali procesiranje traje N^2 ciklusa

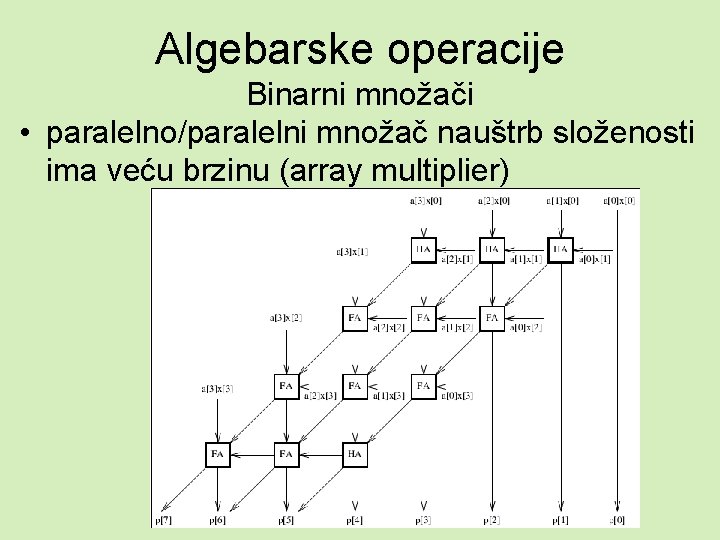

Algebarske operacije Binarni množači • paralelno/paralelni množač nauštrb složenosti ima veću brzinu (array multiplier)

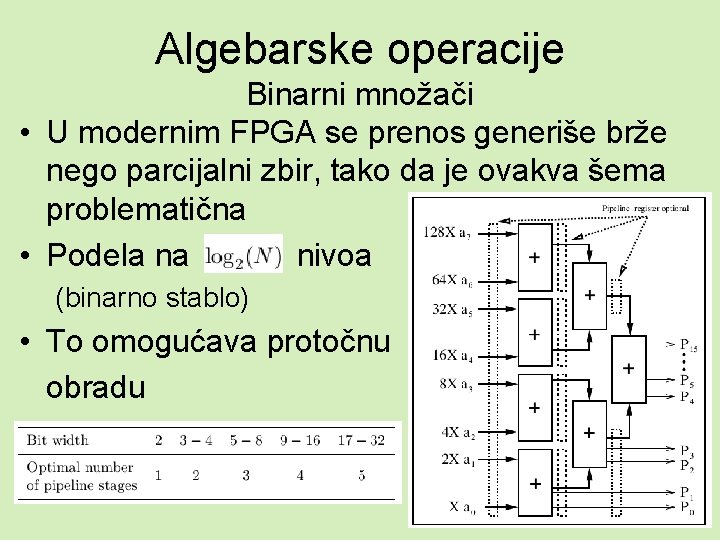

Algebarske operacije Binarni množači • U modernim FPGA se prenos generiše brže nego parcijalni zbir, tako da je ovakva šema problematična • Podela na nivoa (binarno stablo) • To omogućava protočnu obradu

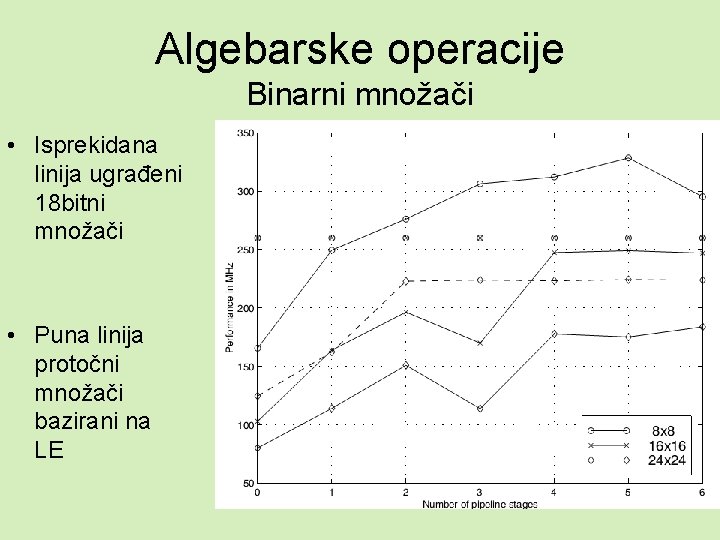

Algebarske operacije Binarni množači • Isprekidana linija ugrađeni 18 bitni množači • Puna linija protočni množači bazirani na LE

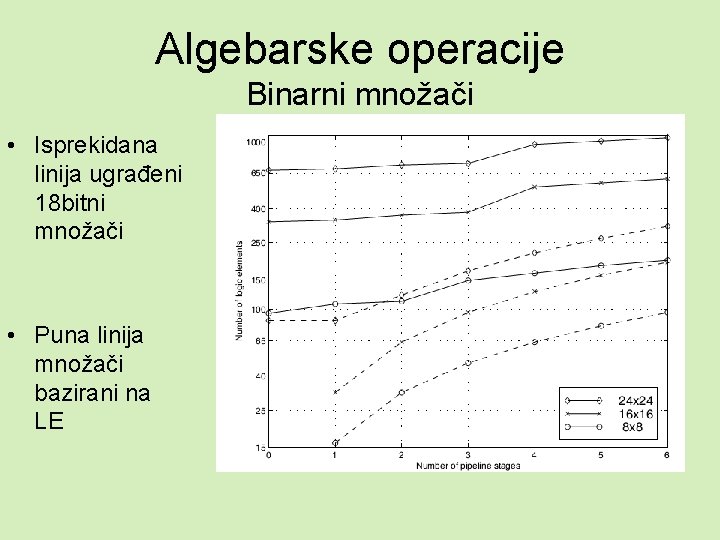

Algebarske operacije Binarni množači • Isprekidana linija ugrađeni 18 bitni množači • Puna linija množači bazirani na LE

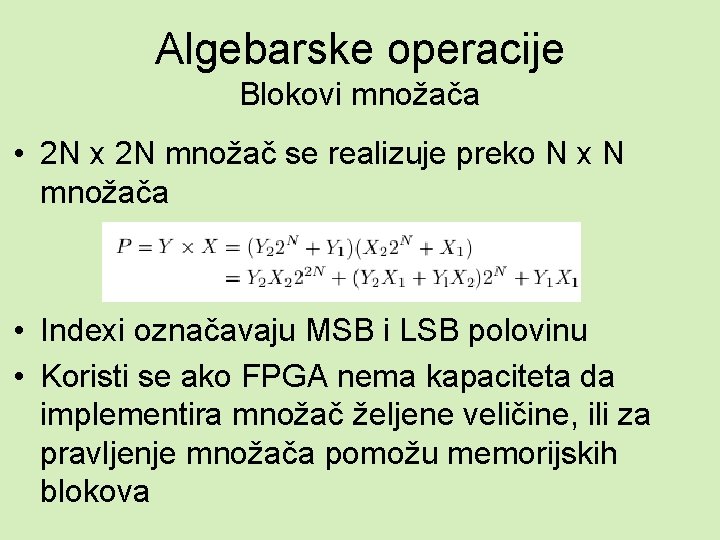

Algebarske operacije Blokovi množača • 2 N x 2 N množač se realizuje preko N x N množača • Indexi označavaju MSB i LSB polovinu • Koristi se ako FPGA nema kapaciteta da implementira množač željene veličine, ili za pravljenje množača pomožu memorijskih blokova

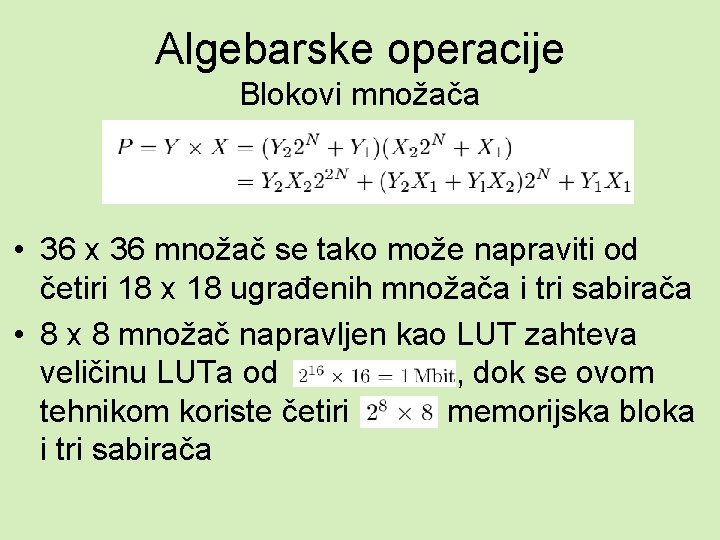

Algebarske operacije Blokovi množača • 36 x 36 množač se tako može napraviti od četiri 18 x 18 ugrađenih množača i tri sabirača • 8 x 8 množač napravljen kao LUT zahteva veličinu LUTa od , dok se ovom tehnikom koriste četiri memorijska bloka i tri sabirača

Algebarske operacije Blokovi množača • Implementacija pomoću memorija je bolja jer se a) smanjuje broj korišćenih LE b) manje se koriste resursi za rutiranje • Broj ugrađenih množača je obično mali, tako da LUT bazirani množači obezbeđuju povećanje broja brzih množača.

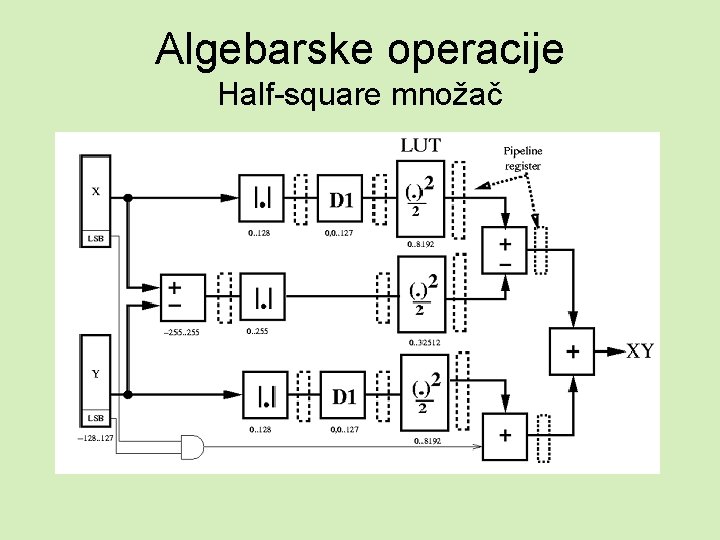

Algebarske operacije Half-square množač • Memorijski zahtevi kod LUT baziranih množača mogu se smanjiti i smanjenjem broja bita u ulaznom domenu • Ako se smanji broj bita na ulazu za 1, veličina LUTa se smanjuje za pola • Koristi se kvadriranje, jer je tabela za kvadriranje veličine svega

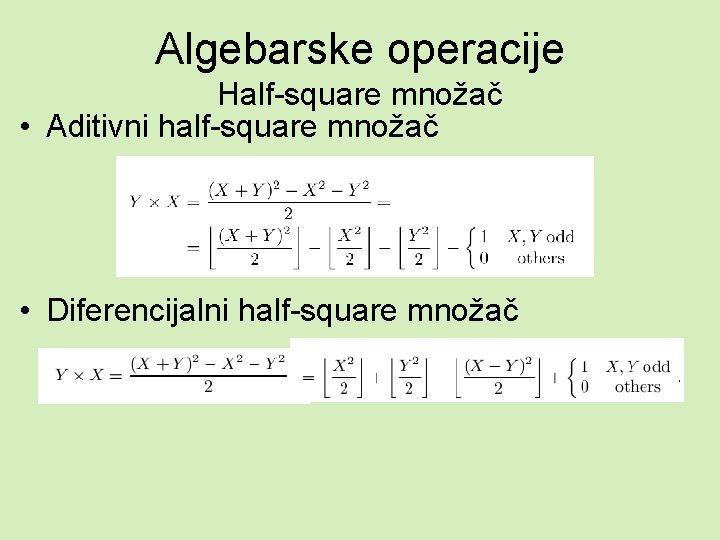

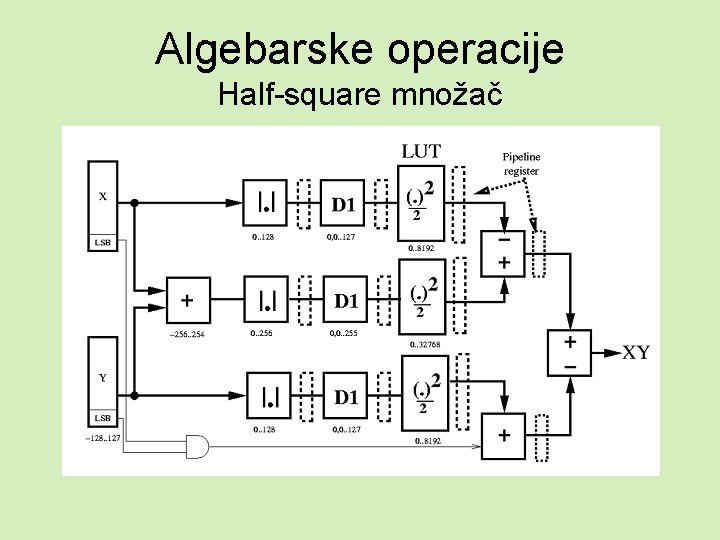

Algebarske operacije Half-square množač • Aditivni half-square množač • Diferencijalni half-square množač

Algebarske operacije Half-square množač

Algebarske operacije Half-square množač

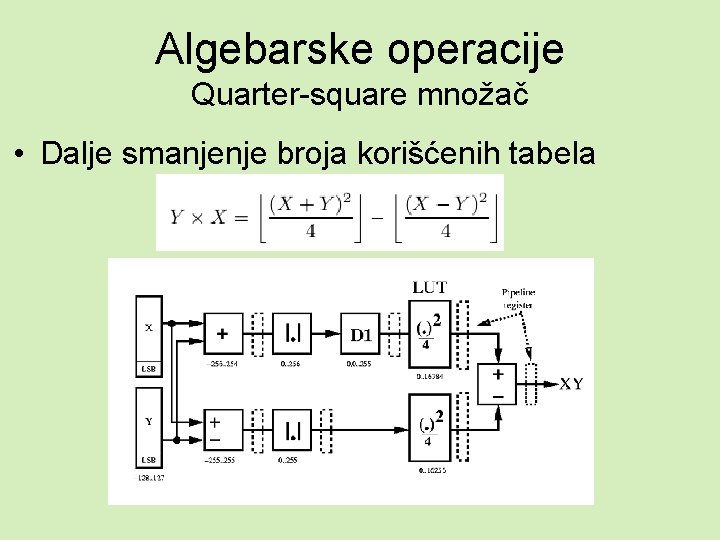

Algebarske operacije Quarter-square množač • Dalje smanjenje broja korišćenih tabela

- Slides: 54