Digital Systems Design VHDL in Bluetooth Baseband Module

Digital Systems Design VHDL in Bluetooth Baseband Module by Marc A. Mackey

Formal Definitions ¡ Baseband - A transmission medium through which digital signals are sent without frequency shifting. In general, only one communication channel is available at any given time. (eg. Ethernet) ¡ Bluetooth - is a short-range radio communication system that is intended to create ad-hoc wireless connectivity between portable and/or fixed electronic devices. (eg. computers, cellular phones, printers, and digital cameras)

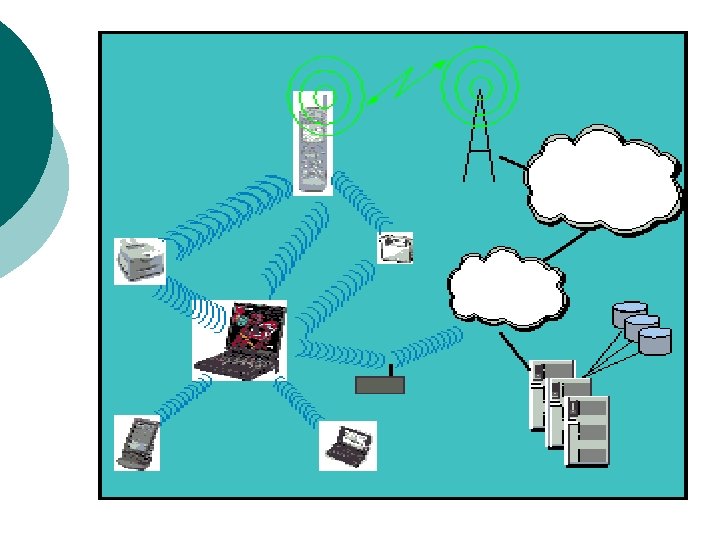

Formal Descriptions ¡ ¡ The Bluetooth system is designed to manage a small number of low-cost point-to-(multi)point communication links over a distance of up to 10 meters with a transmit power of less than 1 m. W. It operates in the globally available unlicensed ISM (industrial, scientific, medical) frequency band at 2. 4 GHz and applies frequency hopping for transmitting data at a symbol rate of 1 Ms/s over the air. Using a combination of circuit and packet switching, Bluetooth can establish up to three 64 kb/s synchronous (voice) channels or an asynchronous (data) channel supporting data rates of maximal 723 kb/s asymmetric or 433 kb/s symmetric.

Nokia 3600 (Calista GSM Model)

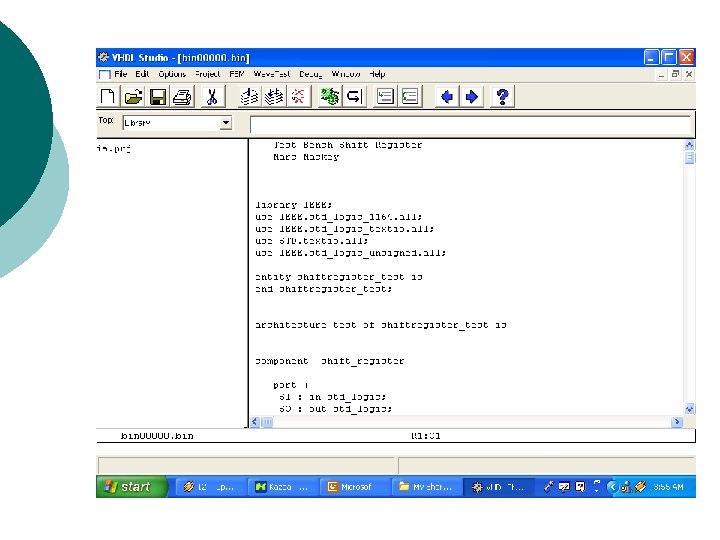

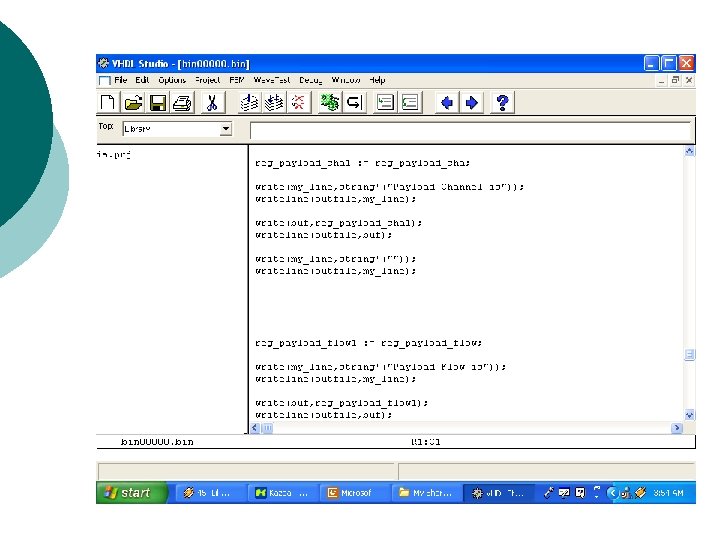

VHDL assignment to components ¡ The Bluetooth baseband hardware components have to be implemented using VHDL as the description language. However, in the design of the Bluetooth baseband core thirteen components are needed in the independent simulation environment for VHDL designs. This will enable us to generate test vectors for the VHDL test benches.

Basic Components of Baseband Core ¡ ¡ ¡ ¡ RF interface LMP interface (a CPU may be) Hop selection controller ACL & SCO link controller HEC and FEC controllers Access code correlator Data whitening (Scrambling) Encryption Authentication Audio Interface Clock recovery and synchronization Channel Control Machine RX/TX buffers and registers

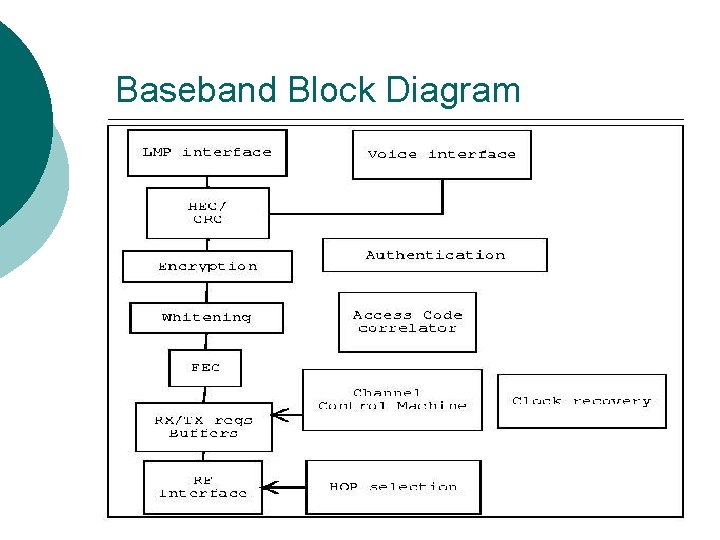

Baseband Block Diagram

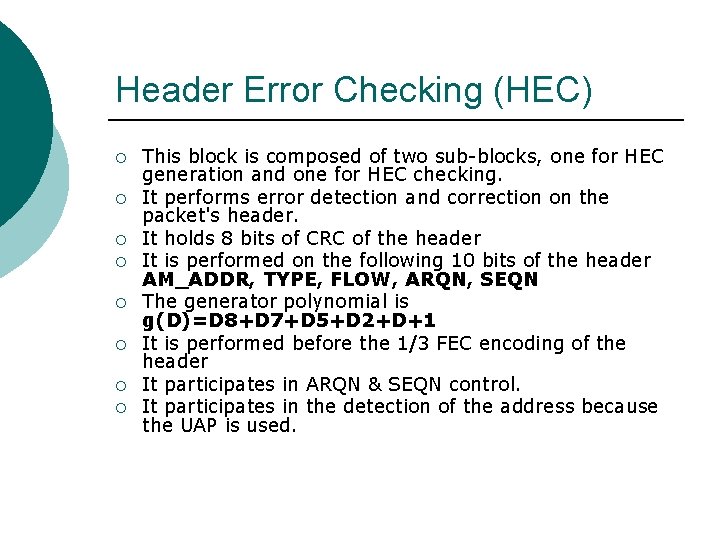

Header Error Checking (HEC) ¡ ¡ ¡ ¡ This block is composed of two sub-blocks, one for HEC generation and one for HEC checking. It performs error detection and correction on the packet's header. It holds 8 bits of CRC of the header It is performed on the following 10 bits of the header AM_ADDR, TYPE, FLOW, ARQN, SEQN The generator polynomial is g(D)=D 8+D 7+D 5+D 2+D+1 It is performed before the 1/3 FEC encoding of the header It participates in ARQN & SEQN control. It participates in the detection of the address because the UAP is used.

Header Error Checking (cont’d) ¡ ¡ ¡ The shift register is preloaded with the slave upper address part (UAP) in Master page response state. The shift register is preloaded with the UAP of the master device. LSB bits of the header are entered first. The LSB of UAP goes to the left-most shifter register element In the checking the shift register is initialized as before and HEC is performed on the header

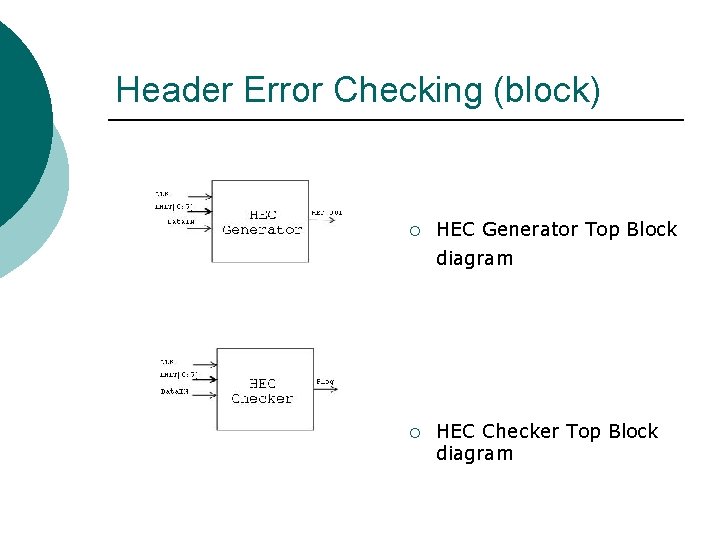

Header Error Checking (block) ¡ HEC Generator Top Block diagram ¡ HEC Checker Top Block diagram

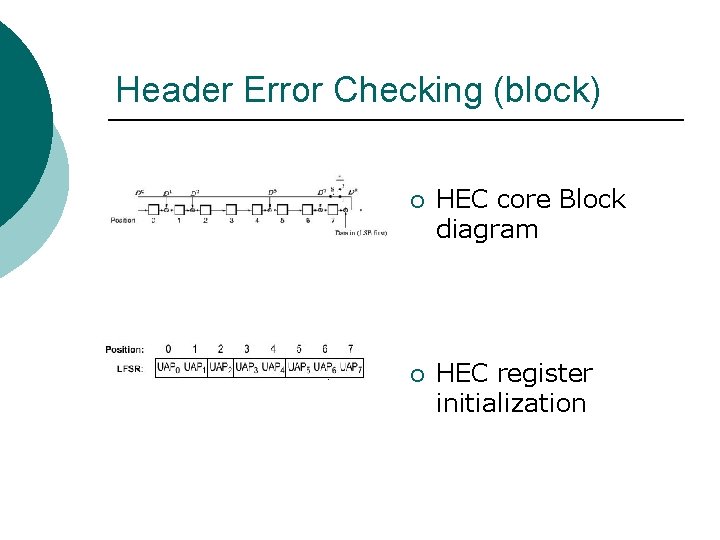

Header Error Checking (block) ¡ HEC core Block diagram ¡ HEC register initialization

CRC ¡ ¡ ¡ ¡ ¡ This block is composed of two sub-blocks, one for CRC generation and one for CRC checking. It performs error detection and correction on the packet's payload. It holds 16 bits of CRC of the payload The generator polynomial is (CRC-CCITT) g(D)=D 16+D 12+D 5+1 It participates in ARQN & SEQN control. It is not performed on all types of packets. CRC is performed on the following ACL links packets DM 1, DH 1, DM 1, DH 3, DM 5, DH 5 CRC is performed on the data part of the DV SCO link packets only CRC is performed on FHS packets CRC is done before any possible FEC encoding.

CRC ¡ ¡ ¡ ¡ It participates in the detection of the address because the UAP is used. The shift register is preloaded with the slave upper address part (UAP) in Master page response state FHS packet. The shift register is preloaded with the default check initialization (DCI) which is 0 x 00 in the FHS packets sent in inquiry response. The shift register is preloaded with the UAP of the master device. Since the UAP and DCI are 8 bit values, they are loaded into the 8 least significant (left-most) and other bits are set to zero The CRC code is appended to the information. In the checking the shift register is initialized as before and CRC is performed on the header

CRC ¡ ¡ ¡ LSB bits of the data are entered first. The data bits are shifted into the LFSR and when they are finished the Switsh (S shown in the figure) passes zeros to the LFSR. The CRC and HEC blocks are very similar except that HEC must be done in all packets and it is 8 bits while CRC is done on some packets and is 16 -bit

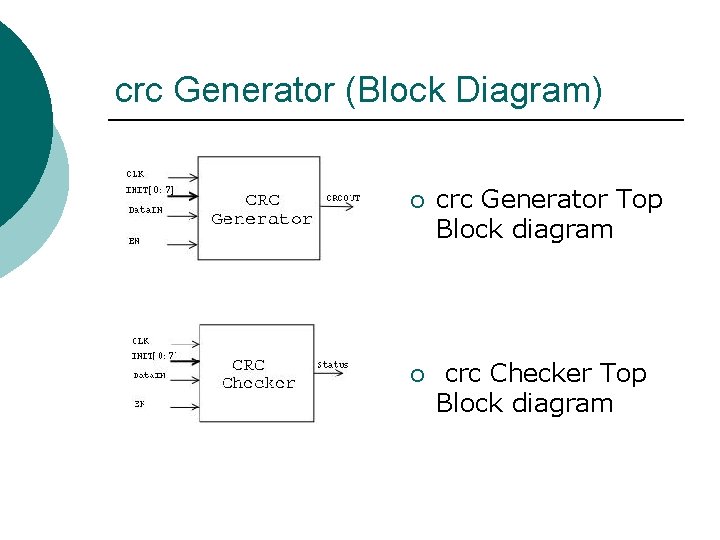

crc Generator (Block Diagram) ¡ crc Generator Top Block diagram ¡ crc Checker Top Block diagram

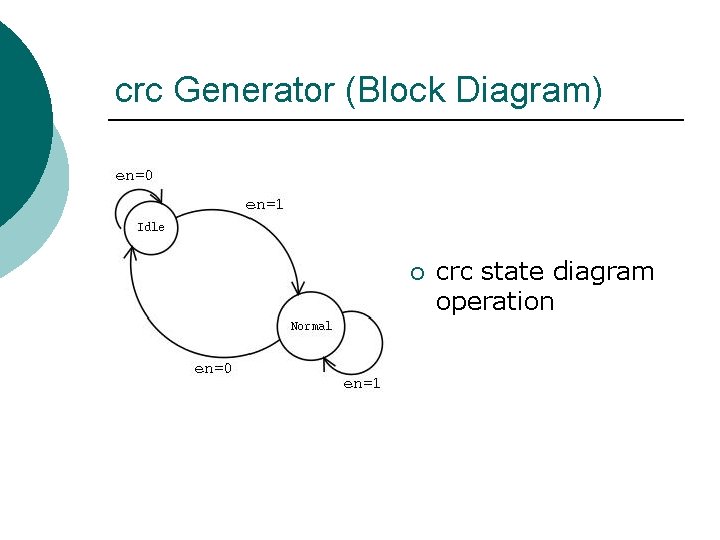

crc Generator (Block Diagram) ¡ crc state diagram operation

crc Generator (Block Diagram) ¡ crc register initialization ¡ crc core Block diagram

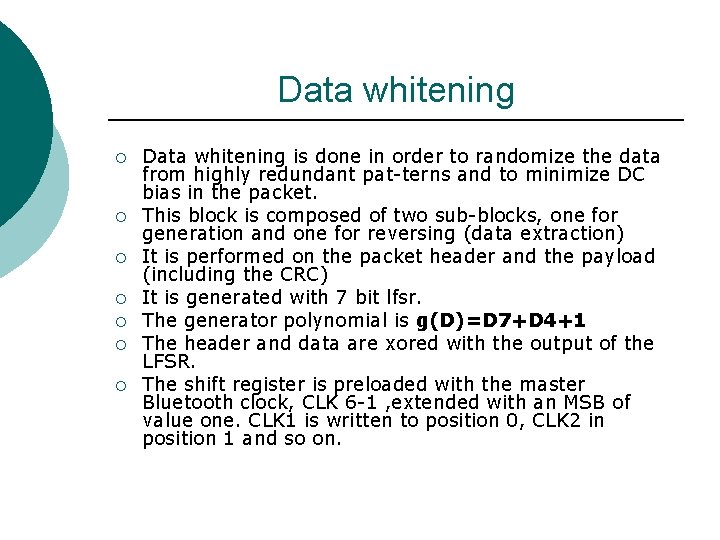

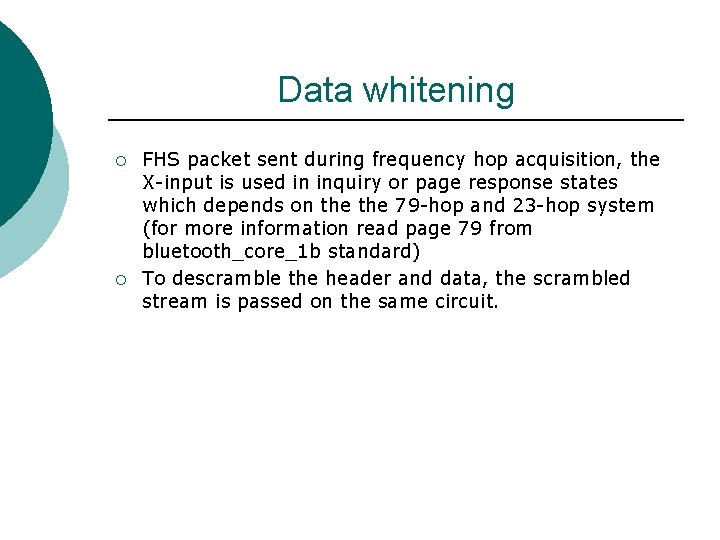

Data whitening ¡ ¡ ¡ ¡ Data whitening is done in order to randomize the data from highly redundant pat-terns and to minimize DC bias in the packet. This block is composed of two sub-blocks, one for generation and one for reversing (data extraction) It is performed on the packet header and the payload (including the CRC) It is generated with 7 bit lfsr. The generator polynomial is g(D)=D 7+D 4+1 The header and data are xored with the output of the LFSR. The shift register is preloaded with the master Bluetooth clock, CLK 6 -1 , extended with an MSB of value one. CLK 1 is written to position 0, CLK 2 in position 1 and so on.

Data whitening ¡ ¡ FHS packet sent during frequency hop acquisition, the X-input is used in inquiry or page response states which depends on the 79 -hop and 23 -hop system (for more information read page 79 from bluetooth_core_1 b standard) To descramble the header and data, the scrambled stream is passed on the same circuit.

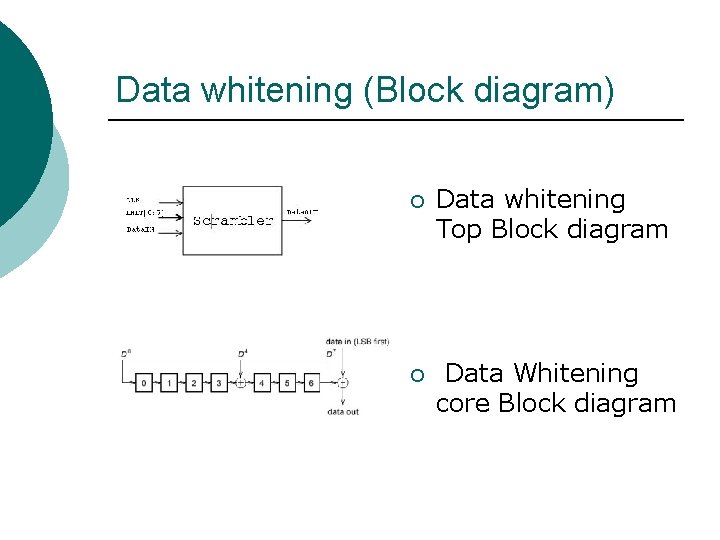

Data whitening (Block diagram) ¡ Data whitening Top Block diagram ¡ Data Whitening core Block diagram

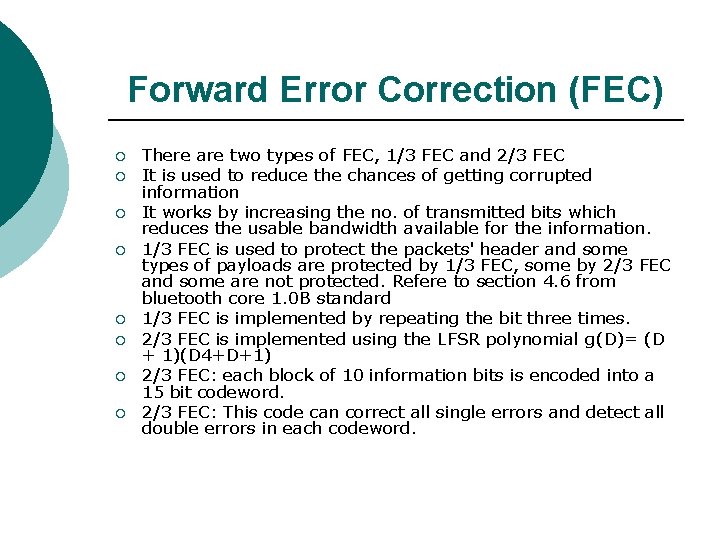

Forward Error Correction (FEC) ¡ ¡ ¡ ¡ There are two types of FEC, 1/3 FEC and 2/3 FEC It is used to reduce the chances of getting corrupted information It works by increasing the no. of transmitted bits which reduces the usable bandwidth available for the information. 1/3 FEC is used to protect the packets' header and some types of payloads are protected by 1/3 FEC, some by 2/3 FEC and some are not protected. Refere to section 4. 6 from bluetooth core 1. 0 B standard 1/3 FEC is implemented by repeating the bit three times. 2/3 FEC is implemented using the LFSR polynomial g(D)= (D + 1)(D 4+D+1) 2/3 FEC: each block of 10 information bits is encoded into a 15 bit codeword. 2/3 FEC: This code can correct all single errors and detect all double errors in each codeword.

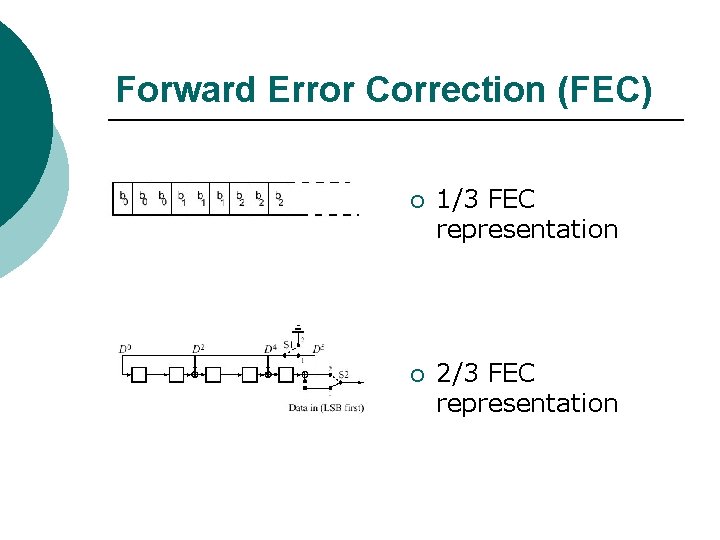

Forward Error Correction (FEC) ¡ 1/3 FEC representation ¡ 2/3 FEC representation

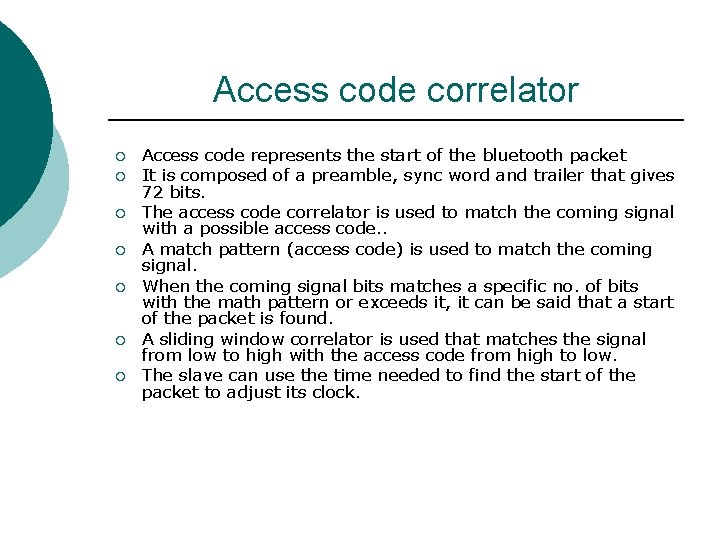

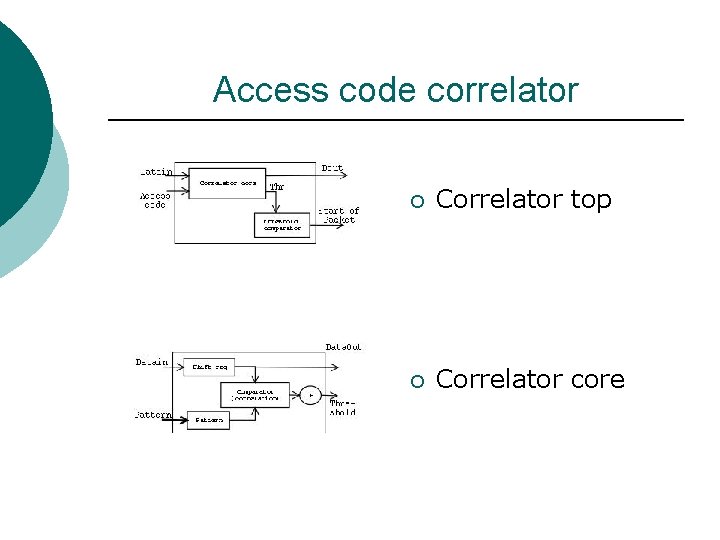

Access code correlator ¡ ¡ ¡ ¡ Access code represents the start of the bluetooth packet It is composed of a preamble, sync word and trailer that gives 72 bits. The access code correlator is used to match the coming signal with a possible access code. . A match pattern (access code) is used to match the coming signal. When the coming signal bits matches a specific no. of bits with the math pattern or exceeds it, it can be said that a start of the packet is found. A sliding window correlator is used that matches the signal from low to high with the access code from high to low. The slave can use the time needed to find the start of the packet to adjust its clock.

Access code correlator ¡ Correlator top ¡ Correlator core

Other Components ¡ ¡ ¡ ¡ ¡ Clock recovery LMP interface Rx/TX registers Hop Selection Voice Interface Link Controller Machine Looking for. . An RF interface between baseband chip and RF chip An LMP interface between the baseband chip and higher level protocols and chips.

Vote of Thanks Jeff Weintraub - Xilinx foundation ¡ San Jose, CA ¡ Jeff. Weintraub@xilinx. com ¡ Luke Trip – Nokia AMS ¡ Melbourne, FL ¡ (Luke. trip@nokia. com) ¡

- Slides: 29