Digital Systems Design 2 VHDL Subprograms Packages and

Digital Systems Design 2 VHDL: Subprograms, Packages, and Libraries Ref. “VHDL Starter’s Guide”, Sudhakar Yalamanchili, Prentice Hall, 1998 Veton Këpuska

Subprograms, Packages, and Libraries u For large projects mechanisms that allow for: Structuring of programs, n Reusing of software modules, and n Managing software complexity, are needed: 1. Functions, 2. Procedures, 3. Packages, and 4. Libraries. n 10/3/2020 Veton Këpuska 2

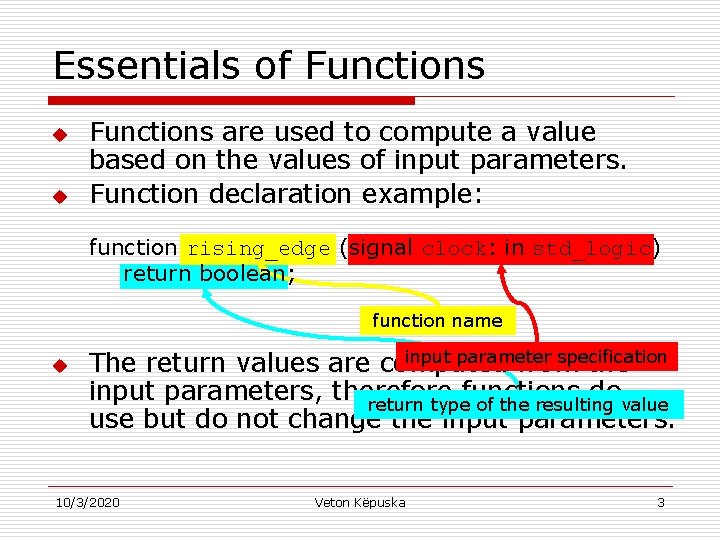

Essentials of Functions u u Functions are used to compute a value based on the values of input parameters. Function declaration example: function rising_edge (signal clock: in std_logic) return boolean; function name u input parameter specification The return values are computed from the input parameters, therefore functions do return type of the resulting value use but do not change the input parameters. 10/3/2020 Veton Këpuska 3

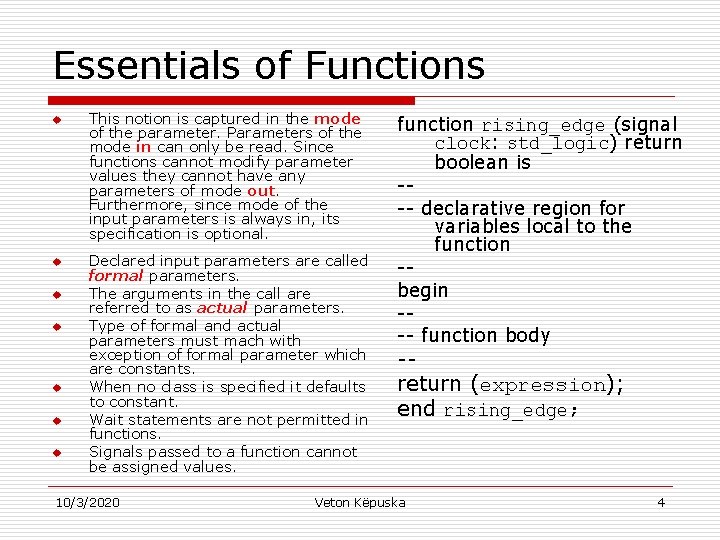

Essentials of Functions u u u u This notion is captured in the mode of the parameter. Parameters of the mode in can only be read. Since functions cannot modify parameter values they cannot have any parameters of mode out. Furthermore, since mode of the input parameters is always in, its specification is optional. Declared input parameters are called formal parameters. The arguments in the call are referred to as actual parameters. Type of formal and actual parameters must mach with exception of formal parameter which are constants. When no class is specified it defaults to constant. Wait statements are not permitted in functions. Signals passed to a function cannot be assigned values. 10/3/2020 function rising_edge (signal clock: std_logic) return boolean is --- declarative region for variables local to the function -begin --- function body -return (expression); end rising_edge; Veton Këpuska 4

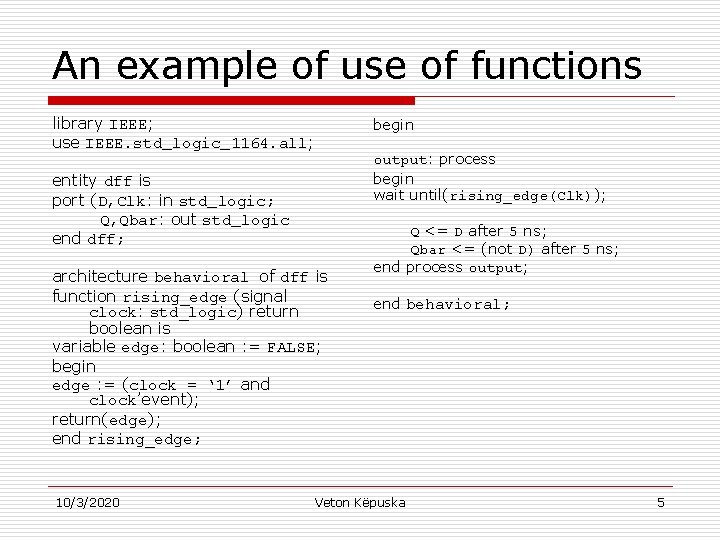

An example of use of functions library IEEE; use IEEE. std_logic_1164. all; begin output: process begin wait until(rising_edge(Clk)); entity dff is port (D, Clk: in std_logic; Q, Qbar: out std_logic end dff; architecture behavioral of dff is function rising_edge (signal clock: std_logic) return boolean is variable edge: boolean : = FALSE; begin edge : = (clock = ‘ 1’ and clock’event); return(edge); end rising_edge; 10/3/2020 Q <= D after 5 ns; Qbar <= (not D) after 5 ns; end process output; end behavioral; Veton Këpuska 5

Type conversion u u Consider the VHDL type bit_vector and IEEE 1164 type std_logic_vector. to_stdlogicvector() is function defined in std_logic_1164. vhd package that can be used to convert signals from bit_vector type to std_logic_vector. Conversely one may need to convert from std_logic_vector to bit_vector. An implementation of this function is depicted in the following VHDL code. Conversion tools are typically provided in libraries (e. g. , std_logic_arith. vhd). 10/3/2020 function to_bitvector (svalue: std_logic_vector) return bit_vector is variable outvalue: bit_vector(svalue’length-1 downto 0); begin --- scan all elements of the array -for i in svalue’range loop case svalue(i) is when ‘ 0’ => outvalue(i) : = ‘ 0’; when ‘ 1’ => outvalue(i) : = ‘ 1’; when others => outvalue(i) : = ‘ 0’; end case; end loop; return(outvalue); end to_bitvector; Veton Këpuska 6

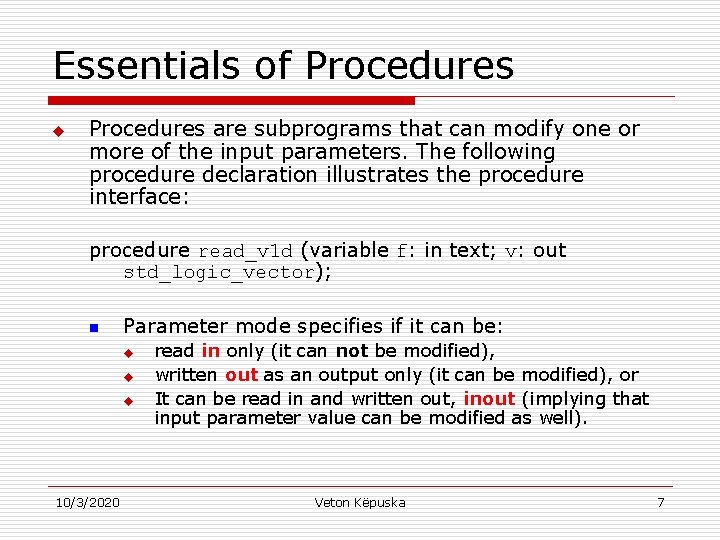

Essentials of Procedures u Procedures are subprograms that can modify one or more of the input parameters. The following procedure declaration illustrates the procedure interface: procedure read_v 1 d (variable f: in text; v: out std_logic_vector); n Parameter mode specifies if it can be: u u u 10/3/2020 read in only (it can not be modified), written out as an output only (it can be modified), or It can be read in and written out, inout (implying that input parameter value can be modified as well). Veton Këpuska 7

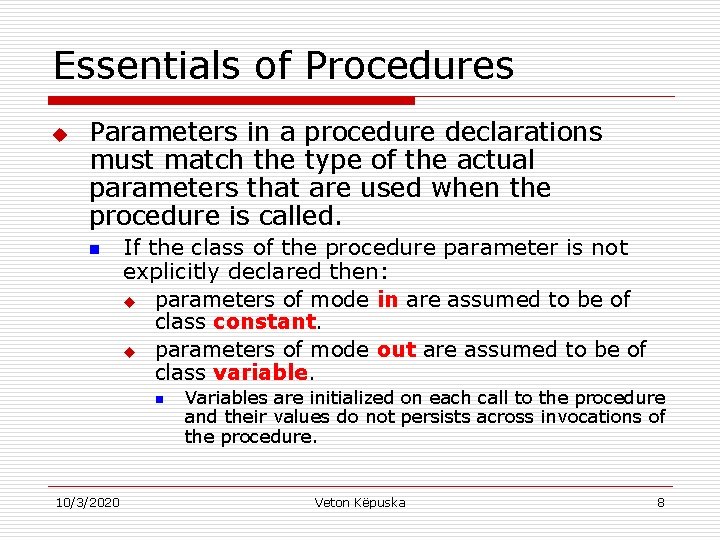

Essentials of Procedures u Parameters in a procedure declarations must match the type of the actual parameters that are used when the procedure is called. n If the class of the procedure parameter is not explicitly declared then: u parameters of mode in are assumed to be of class constant. u parameters of mode out are assumed to be of class variable. n 10/3/2020 Variables are initialized on each call to the procedure and their values do not persists across invocations of the procedure. Veton Këpuska 8

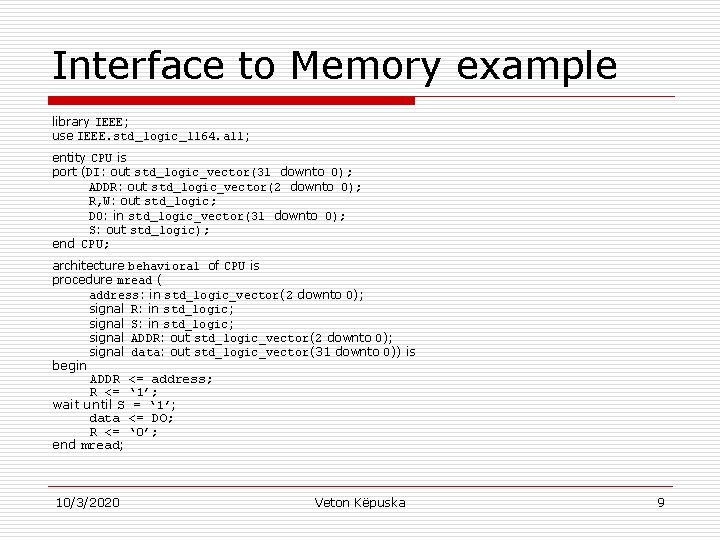

Interface to Memory example library IEEE; use IEEE. std_logic_1164. all; entity CPU is port (DI: out std_logic_vector(31 downto 0); ADDR: out std_logic_vector(2 downto 0); R, W: out std_logic; DO: in std_logic_vector(31 downto 0); S: out std_logic); end CPU; architecture behavioral of CPU is procedure mread ( address: in std_logic_vector(2 downto 0); signal R: in std_logic; signal S: in std_logic; signal ADDR: out std_logic_vector(2 downto 0); signal data: out std_logic_vector(31 downto 0)) is begin ADDR <= address; R <= ‘ 1’; wait until S = ‘ 1’; data <= DO; R <= ‘ 0’; end mread; 10/3/2020 Veton Këpuska 9

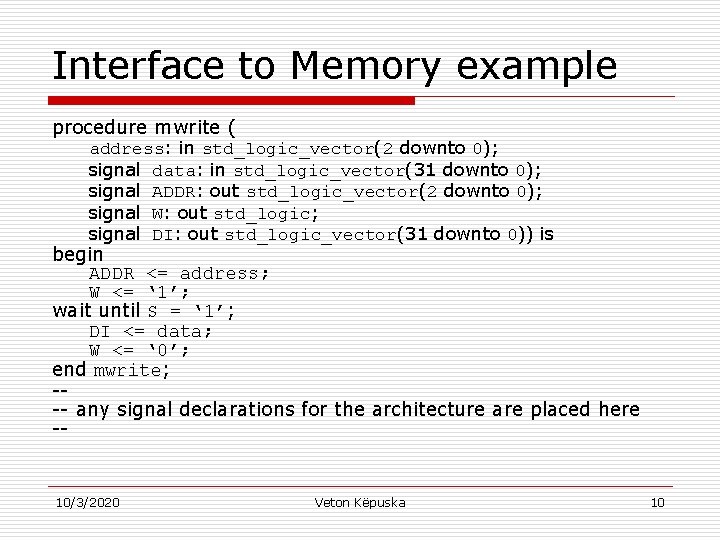

Interface to Memory example procedure mwrite ( address: in std_logic_vector(2 downto 0); signal data: in std_logic_vector(31 downto 0); signal ADDR: out std_logic_vector(2 downto 0); signal W: out std_logic; signal DI: out std_logic_vector(31 downto 0)) is begin ADDR <= address; W <= ‘ 1’; wait until S = ‘ 1’; DI <= data; W <= ‘ 0’; end mwrite; --- any signal declarations for the architecture are placed here -- 10/3/2020 Veton Këpuska 10

Interface to Memory example begin --- CPU behavioral description here -process begin --- behavioral description -end process; end behavioral; 10/3/2020 Veton Këpuska 11

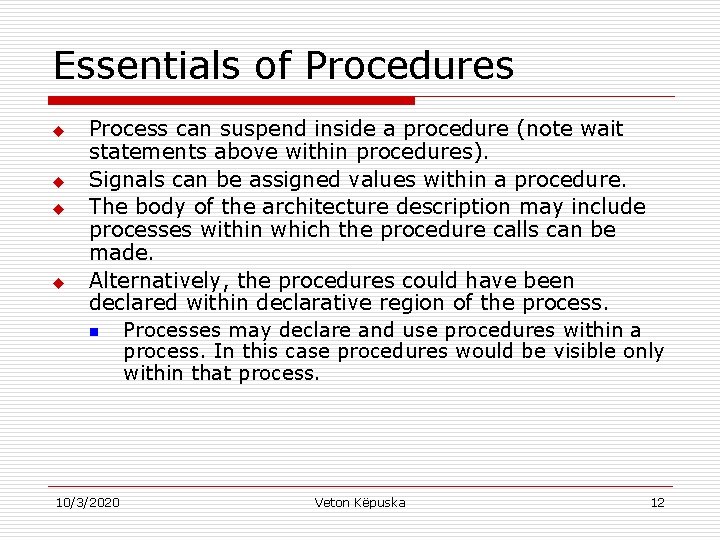

Essentials of Procedures u u Process can suspend inside a procedure (note wait statements above within procedures). Signals can be assigned values within a procedure. The body of the architecture description may include processes within which the procedure calls can be made. Alternatively, the procedures could have been declared within declarative region of the process. n Processes may declare and use procedures within a process. In this case procedures would be visible only within that process. 10/3/2020 Veton Këpuska 12

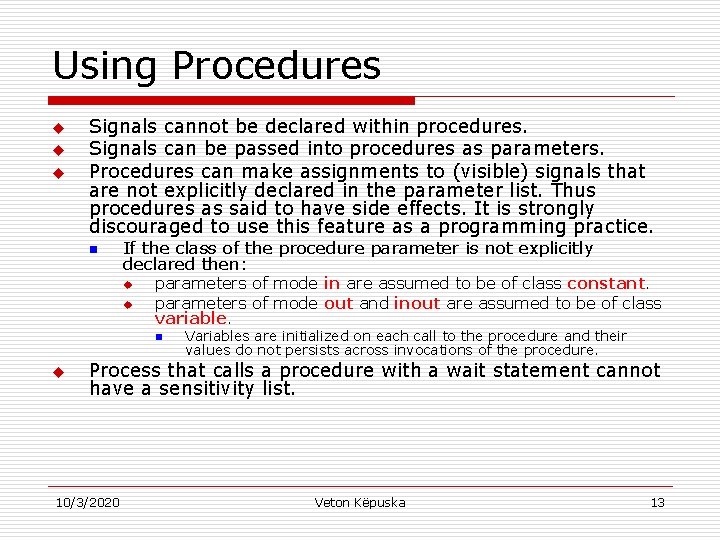

Using Procedures u u u Signals cannot be declared within procedures. Signals can be passed into procedures as parameters. Procedures can make assignments to (visible) signals that are not explicitly declared in the parameter list. Thus procedures as said to have side effects. It is strongly discouraged to use this feature as a programming practice. n If the class of the procedure parameter is not explicitly declared then: u u parameters of mode in are assumed to be of class constant. parameters of mode out and inout are assumed to be of class variable. n u Variables are initialized on each call to the procedure and their values do not persists across invocations of the procedure. Process that calls a procedure with a wait statement cannot have a sensitivity list. 10/3/2020 Veton Këpuska 13

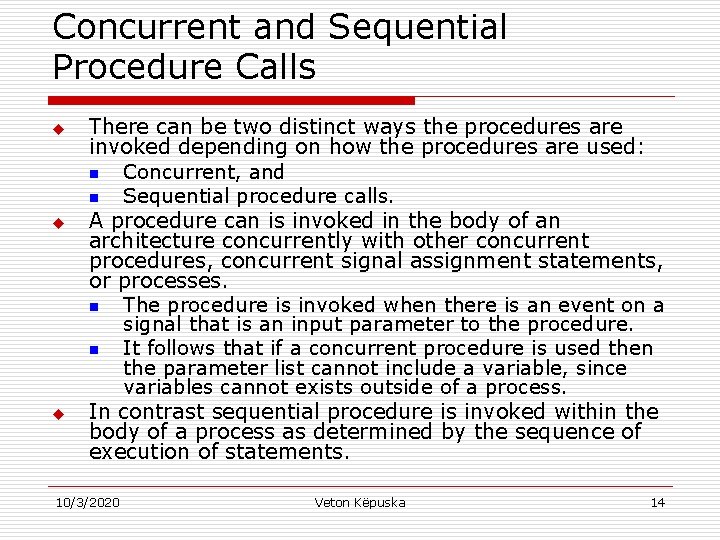

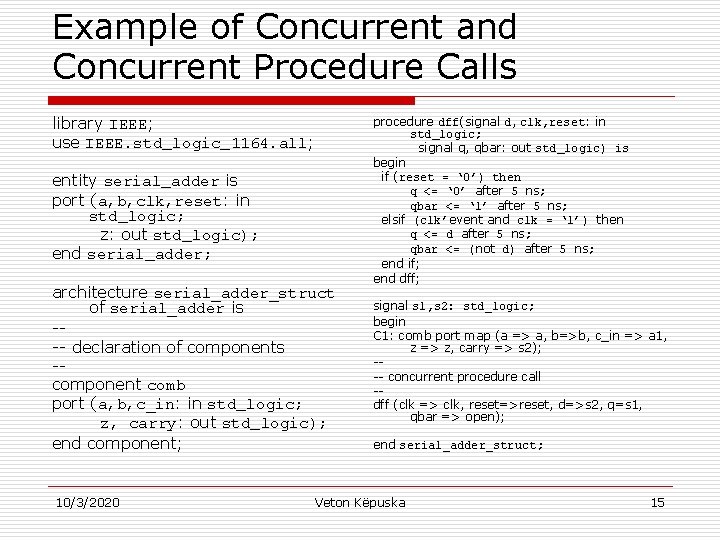

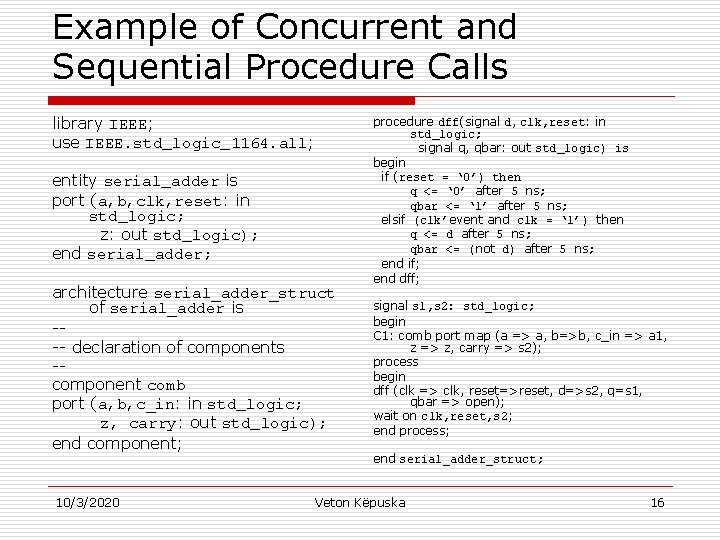

Concurrent and Sequential Procedure Calls u u u There can be two distinct ways the procedures are invoked depending on how the procedures are used: n Concurrent, and n Sequential procedure calls. A procedure can is invoked in the body of an architecture concurrently with other concurrent procedures, concurrent signal assignment statements, or processes. n The procedure is invoked when there is an event on a signal that is an input parameter to the procedure. n It follows that if a concurrent procedure is used then the parameter list cannot include a variable, since variables cannot exists outside of a process. In contrast sequential procedure is invoked within the body of a process as determined by the sequence of execution of statements. 10/3/2020 Veton Këpuska 14

Example of Concurrent and Concurrent Procedure Calls library IEEE; use IEEE. std_logic_1164. all; entity serial_adder is port (a, b, clk, reset: in std_logic; z: out std_logic); end serial_adder; architecture serial_adder_struct of serial_adder is --- declaration of components -component comb port (a, b, c_in: in std_logic; z, carry: out std_logic); end component; 10/3/2020 procedure dff(signal d, clk, reset: in std_logic; signal q, qbar: out std_logic) is begin if (reset = ‘ 0’) then q <= ‘ 0’ after 5 ns; qbar <= ‘ 1’ after 5 ns; elsif (clk’event and clk = ‘ 1’) then q <= d after 5 ns; qbar <= (not d) after 5 ns; end if; end dff; signal s 1, s 2: std_logic; begin C 1: comb port map (a => a, b=>b, c_in => a 1, z => z, carry => s 2); --- concurrent procedure call -dff (clk => clk, reset=>reset, d=>s 2, q=s 1, qbar => open); end serial_adder_struct; Veton Këpuska 15

Example of Concurrent and Sequential Procedure Calls library IEEE; use IEEE. std_logic_1164. all; entity serial_adder is port (a, b, clk, reset: in std_logic; z: out std_logic); end serial_adder; architecture serial_adder_struct of serial_adder is --- declaration of components -component comb port (a, b, c_in: in std_logic; z, carry: out std_logic); end component; 10/3/2020 procedure dff(signal d, clk, reset: in std_logic; signal q, qbar: out std_logic) is begin if (reset = ‘ 0’) then q <= ‘ 0’ after 5 ns; qbar <= ‘ 1’ after 5 ns; elsif (clk’event and clk = ‘ 1’) then q <= d after 5 ns; qbar <= (not d) after 5 ns; end if; end dff; signal s 1, s 2: std_logic; begin C 1: comb port map (a => a, b=>b, c_in => a 1, z => z, carry => s 2); process begin dff (clk => clk, reset=>reset, d=>s 2, q=s 1, qbar => open); wait on clk, reset, s 2; end process; end serial_adder_struct; Veton Këpuska 16

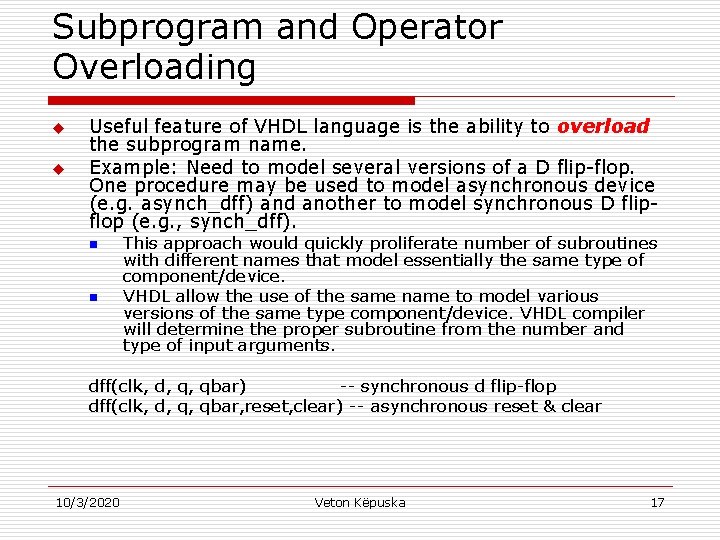

Subprogram and Operator Overloading u u Useful feature of VHDL language is the ability to overload the subprogram name. Example: Need to model several versions of a D flip-flop. One procedure may be used to model asynchronous device (e. g. asynch_dff) and another to model synchronous D flipflop (e. g. , synch_dff). n n This approach would quickly proliferate number of subroutines with different names that model essentially the same type of component/device. VHDL allow the use of the same name to model various versions of the same type component/device. VHDL compiler will determine the proper subroutine from the number and type of input arguments. dff(clk, d, q, qbar) -- synchronous d flip-flop dff(clk, d, q, qbar, reset, clear) -- asynchronous reset & clear 10/3/2020 Veton Këpuska 17

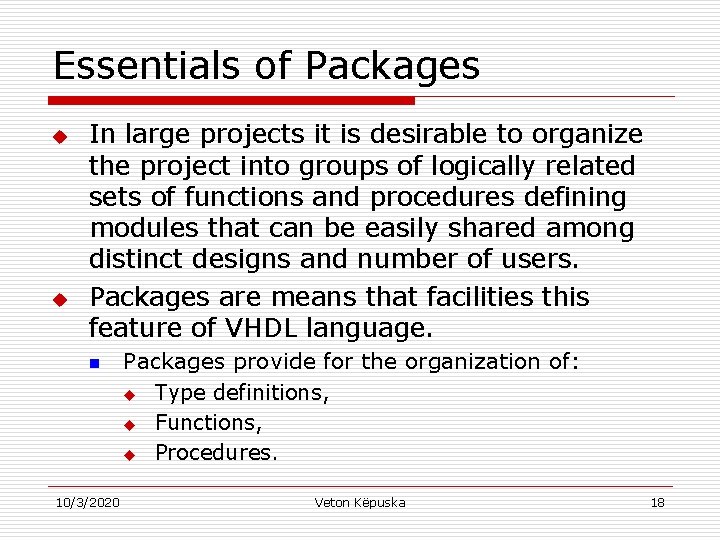

Essentials of Packages u u In large projects it is desirable to organize the project into groups of logically related sets of functions and procedures defining modules that can be easily shared among distinct designs and number of users. Packages are means that facilities this feature of VHDL language. n 10/3/2020 Packages provide for the organization of: u Type definitions, u Functions, u Procedures. Veton Këpuska 18

Essentials of Packages u To gain an intution for the constructs used in building packages it is instructive to consider how the code modules may be reused across projects. n n 10/3/2020 What is a minimal information required in order to make users of a package aware of the utilities that it provides? Package Declaration – it is interface or specification of the services that a package provides. Veton Këpuska 19

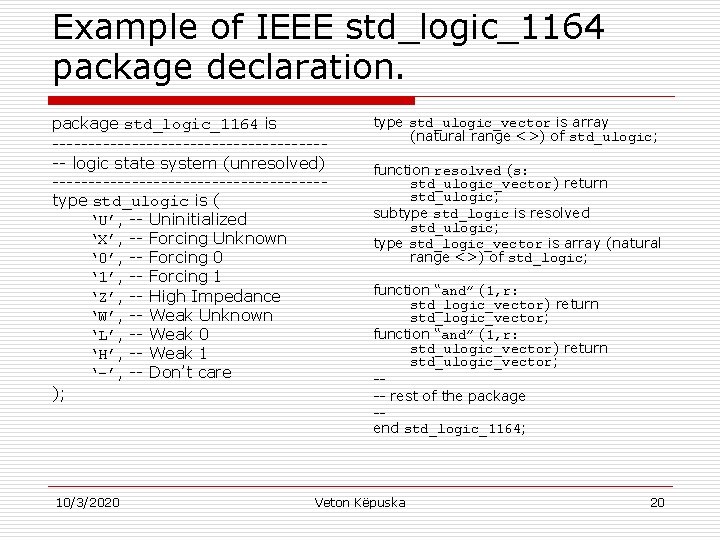

Example of IEEE std_logic_1164 package declaration. package std_logic_1164 is -------------------- logic state system (unresolved) -------------------type std_ulogic is ( ‘U’, -- Uninitialized ‘X’, -- Forcing Unknown ‘ 0’, -- Forcing 0 ‘ 1’, -- Forcing 1 ‘Z’, -- High Impedance ‘W’, -- Weak Unknown ‘L’, -- Weak 0 ‘H’, -- Weak 1 ‘-’, -- Don’t care ); 10/3/2020 type std_ulogic_vector is array (natural range <>) of std_ulogic; function resolved (s: std_ulogic_vector) return std_ulogic; subtype std_logic is resolved std_ulogic; type std_logic_vector is array (natural range <>) of std_logic; function “and” (1, r: std_logic_vector) return std_logic_vector; function “and” (1, r: std_ulogic_vector) return std_ulogic_vector; --- rest of the package -end std_logic_1164; Veton Këpuska 20

Essentials of Packages u u If a package is being constructed that used types, procedures, or functions from another package, then access ot this package must be provided via library and use clauses. After defining the content of the package (via package declaration) the VHDL code that implements these functions and procedures must be supplied. n 10/3/2020 This implementation is contained in the package body. Veton Këpuska 21

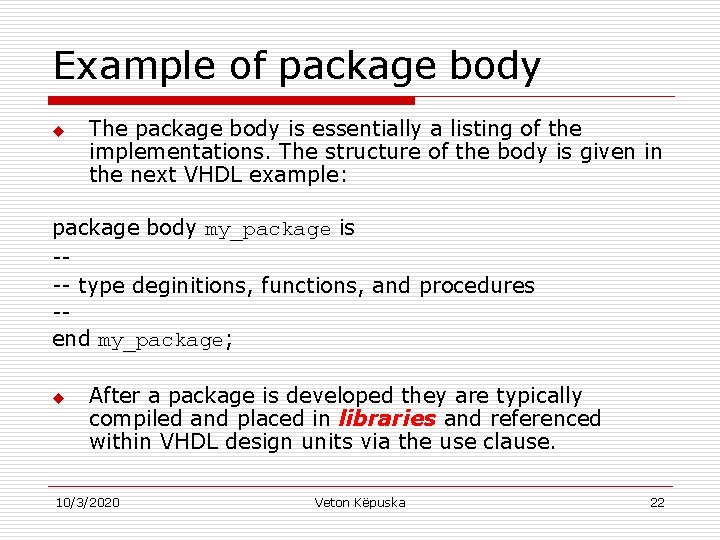

Example of package body u The package body is essentially a listing of the implementations. The structure of the body is given in the next VHDL example: package body my_package is --- type deginitions, functions, and procedures -end my_package; u After a package is developed they are typically compiled and placed in libraries and referenced within VHDL design units via the use clause. 10/3/2020 Veton Këpuska 22

Essentials of Libraries u u u Each design unit; entity-architecture pair, package body, is compiled and placed in a design library. Libraries are implemented as directories and are referenced by their logical name. This logical name maps to a physical path to the corresponding directory. The libraries must be declared when needed to be used: library logical-library-name-1, logical-library-name-2, …; u Libraries STD and WORK are implicitly declared (e. g. , user declared programs do not need to declare them). n n 10/3/2020 STD library contains standard packages provided with VHDL distributions. WORK library refers to working directory which can be set within the simulation environment. Veton Këpuska 23

Essentials of Libraries u u If programs were to access functions in a design unit that was stored in other libraries, e. g. , IEEE, then this library must be declared at the start of the program. Once a library has been declared all of the functions, procedures, and type declarations of a package in the library can be made accessible to a VHDL model through the use clause: library IEEE; use IEEE. std_logic_1164. all; u The second statement makes all of the type definitions, functions, and procedures defined in the package std_logic_1164. vhd visible to the VHDL model. A second form of the use clause can be used when only a specific item, such as function called my_func, in the package is to be made visible: use IEEE. std_logic_1164. my_func; 10/3/2020 Veton Këpuska 24

Essentials of Libraries u Important note. Visibility of the library must be established for each design unit separately. It is not enough to have library declared on top of a file if that file contains more than one design unit. 10/3/2020 Veton Këpuska 25

- Slides: 25